LP38852 1.5A Fast-Response High-Accuracy Adjustable LDO Linear Regulator

with Enable and Soft-Start

Literature Number: SNVS482D

LP38852 1.5A Fast-Response High-Accuracy LDO Linear Regulator with

# LP38852

# 1.5A Fast-Response High-Accuracy Adjustable LDO Linear Regulator with Enable and Soft-Start

### **General Description**

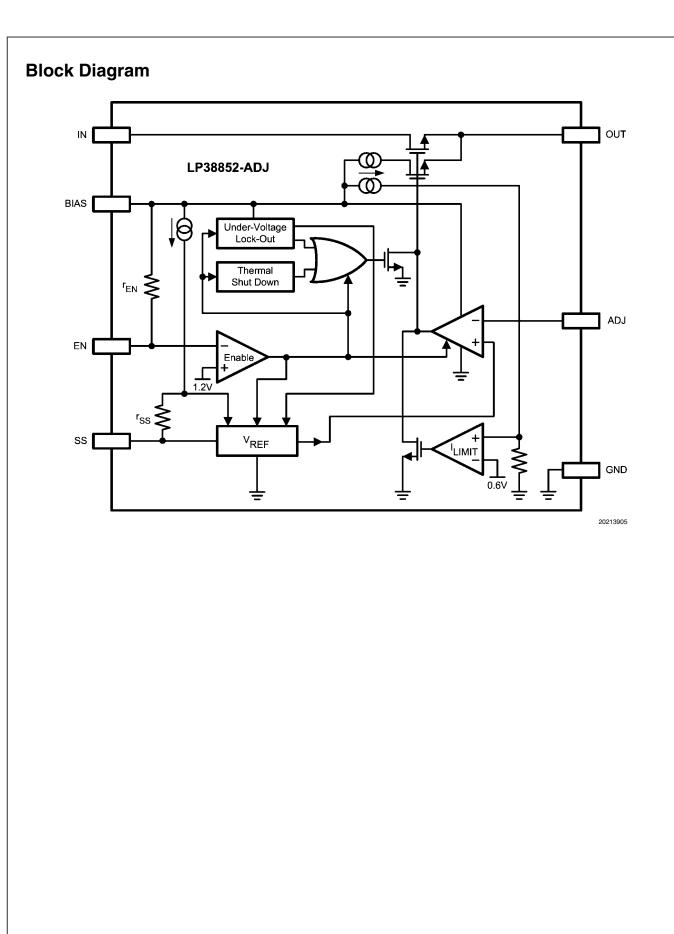

The LP38852-ADJ is a high current, fast response regulator which can maintain output voltage regulation with extremely low input to output voltage drop. Fabricated on a CMOS process, the device operates from two input voltages:  $V_{BIAS}$  provides voltage to drive the gate of the N-MOS power transistor, while  $V_{IN}$  is the input voltage which supplies power to the load. The use of an external bias rail allows the part to operate from ultra low  $V_{IN}$  voltages. Unlike bipolar regulators, the CMOS architecture consumes extremely low quiescent current at any output load current. The use of an N-MOS power transistor results in wide bandwidth, yet minimum external capacitance is required to maintain loop stability.

The fast transient response of this device makes it suitable for use in powering DSP, Microcontroller Core voltages and Switch Mode Power Supply post regulators. The part is available in the TO-220 and TO-263 7-pin packages.

Dropout Voltage: 130 mV (typical) at 1.5A load current.

Low Ground Pin Current: 10 mA (typical) at 1.5A load current.

Soft-Start: Programmable Soft-Start time.

**Precision ADJ Voltage:**  $\pm 1.5\%$  for T<sub>J</sub> = 25°C, and  $\pm 2.0\%$  for 0°C  $\leq$  T<sub>J</sub>  $\leq$  +125°C, across all line and load conditions

### Features

- Adjustable V<sub>OUT</sub> range of 0.80V to 1.8V

- Wide V<sub>BIAS</sub> Supply operating range of 3.0V to 5.5V

- Stable with 10µF Ceramic capacitors

- Dropout voltage of 130 mV (typical) at 1.5A load current

- Precision Output Voltage across all line and load

- conditions: ---  $\pm 1.5\% V_{ADJ}$  for T<sub>J</sub> = 25°C

- $= \pm 1.5\% V_{ADJ} \text{ for } 0^{\circ} \text{ C} \leq T \leq 11$

- $= \pm 2.0\% V_{ADJ}$  for  $0^{\circ}C \le T_{J} \le \pm 125^{\circ}C$

- $= \pm 3.0\% V_{ADJ}$  for  $-40^{\circ}C \le T_{J} \le +125^{\circ}C$

- Over-Temperature and Over-Current protection

- Available in 8 lead PSOP, 7 lead TO-220 and 7 lead TO-263 packages

- -40°C to +125°C Operating Junction Temperature Range

### Applications

- ASIC Power Supplies In:

Desktops, Notebooks, and Graphics Cards, Servers

- Gaming Set Top Boxes, Printers and Copiers

Server Core and I/O Supplies

- DSP and FPGA Power Supplies

- SMPS Post-Regulator

© 2011 Texas Instruments Incorporated 202139

**Enable and Soft-Stari**

#### oring Information \_

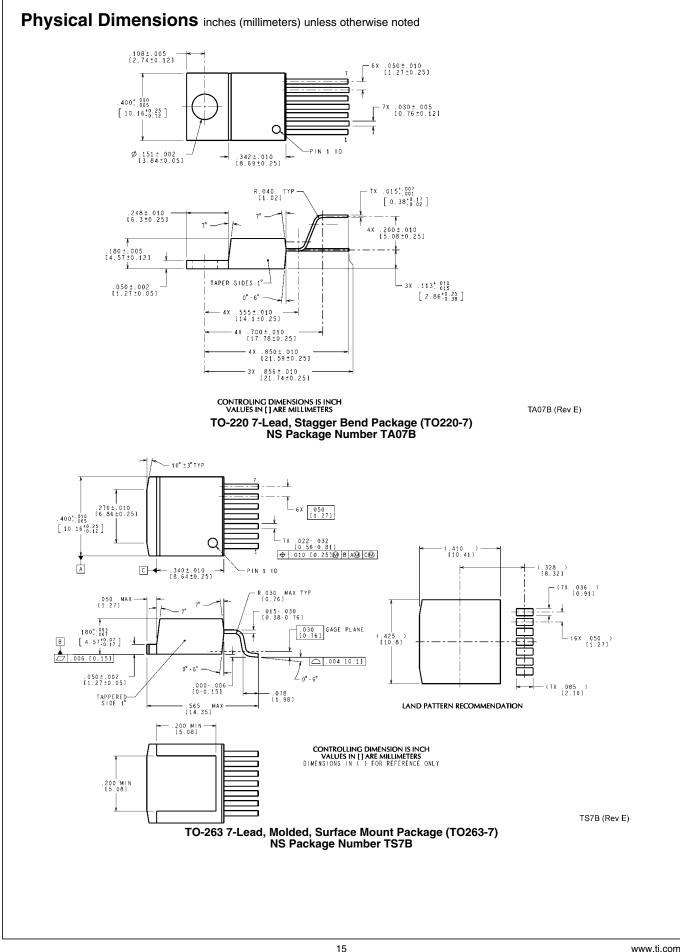

| V <sub>OUT</sub> | Order Number   | Package Type                                | Package Drawing | Supplied As           |

|------------------|----------------|---------------------------------------------|-----------------|-----------------------|

|                  | LP38852S-ADJ   | TO263-7                                     | TS7B            | Rail of 45            |

|                  | LP38852SX-ADJ  | TO263-7                                     | TS7B            | Tape and Reel of 500  |

| ADJ              | LP38852T-ADJ   | TO263-7      TS7B        TO220-7      TA07B | Rail of 45      |                       |

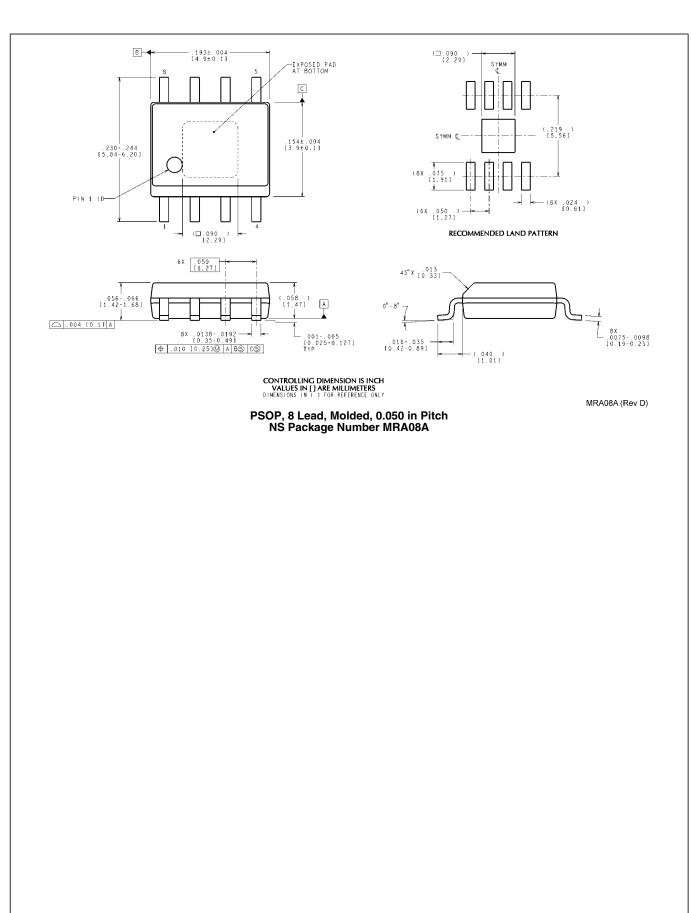

|                  | LP38852MR-ADJ  | PSOP-8                                      | MRA08A          | Rail of 95            |

|                  | LP38852MRX-ADJ | PSOP-8                                      | MRA08A          | Tape and Reel of 2500 |

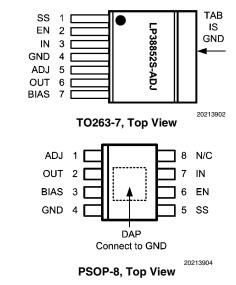

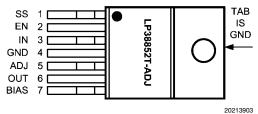

## **Connection Diagrams**

TO220-7, Top View

## **Pin Descriptions**

| TO220–7<br>Pin # | TO263–7<br>Pin # |     |      |                                                                                                                                                                                                          |  | Pin Description |

|------------------|------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------|

| 1                | 1                | 5   | SS   | Soft-Start capacitor connection. Used to slow the rise time of $V_{\text{OUT}}$ at turn-on.                                                                                                              |  |                 |

| 2                | 2                | 6   | EN   | Device Enable, High = On, Low = Off.                                                                                                                                                                     |  |                 |

| 3                | 3                | 7   | IN   | The unregulated voltage input                                                                                                                                                                            |  |                 |

| 4                | 4                | 4   | GND  | Ground                                                                                                                                                                                                   |  |                 |

| 5                | 5                | 1   | ADJ  | The feedback connection to set the output voltage                                                                                                                                                        |  |                 |

| 6                | 6                | 2   | OUT  | The regulated output voltage                                                                                                                                                                             |  |                 |

| 7                | 7                | 3   | BIAS | The supply for the internal control and reference circuitry.                                                                                                                                             |  |                 |

| -                | -                | 8   | N/C  | No internal connection                                                                                                                                                                                   |  |                 |

| ТАВ              | ТАВ              | -   | ТАВ  | The TAB is a thermal and electrical connection that is physicall<br>attached to the backside of the die, and used as a thermal hear<br>sink connection. See the Application Information section for deta |  |                 |

| -                | -                | DAP | DAP  | The DAP is a thermal connection only that is physically attached<br>the backside of the die, and used as a thermal heat-sink<br>connection. See the Application Information section for details.         |  |                 |

### TO220-7 and TO263-7 Packages

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Storage Temperature Range                    | –65°C to +150°C    |

|----------------------------------------------|--------------------|

| Lead Temperature                             |                    |

| Soldering, 5 seconds                         | 260°C              |

| ESD Rating                                   |                    |

| Human Body Model ( <i>Note 2</i> )           | ±2 kV              |

| Power Dissipation ( <i>Note 3</i> )          | Internally Limited |

| V <sub>IN</sub> Supply Voltage (Survival)    | -0.3V to +6.0V     |

| V <sub>BIAS</sub> Supply Voltage (Survival)  | -0.3V to +6.0V     |

| V <sub>SS</sub> SoftStart Voltage (Survival) | -0.3V to +6.0V     |

|                                              |                    |

I<sub>OUT</sub> Current (Survival) Junction Temperature Internally Limited -40°C to +150°C

## Operating Ratings (Note 1)

| V <sub>IN</sub> Supply Voltage                     | $(V_{OUT} + V_{DO})$ to $V_{BIAS}$ |  |

|----------------------------------------------------|------------------------------------|--|

| V <sub>BIAS</sub> Supply Voltage ( <i>Note 7</i> ) |                                    |  |

| $0.8V \le V_{OUT} \le 1.2V$                        | 3.0V to 5.5V                       |  |

| $1.2V < V_{OUT} \le 1.8V$                          | 4.5V to 5.5V                       |  |

| V <sub>EN</sub> Voltage                            | 0.0V to $V_{\text{BIAS}}$          |  |

| Ι <sub>ουτ</sub>                                   | 0 mA to 1.5A                       |  |

| Junction Temperature Range<br>( <i>Note 3</i> )    | -40°C to +125°C                    |  |

**Electrical Characteristics** Unless otherwise specified:  $V_{OUT} = 0.80V$ ,  $V_{IN} = V_{OUT(NOM)} + 1V$ ,  $V_{BIAS} = 3.0V$ ,  $V_{EN} = V_{BIAS}$ ,  $I_{OUT} = 10$  mA,  $C_{IN} = C_{OUT} = 10 \mu$ F,  $C_{BIAS} = 1 \mu$ F,  $C_{SS} = open$ . Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in **boldface type** apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only.

| Symbol                             | Parameter                                                | Conditions                                                                                                                                                                         | MIN                  | ТҮР                       | MAX                 | Units |  |

|------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|---------------------|-------|--|

|                                    |                                                          | $\begin{split} & V_{OUT(NOM)} + 1V \leq V_IN \leq V_BIAS \leq 4.5V, \\ & See \; (\textit{Note 7}) \\ & 3.0V \leq V_BIAS \leq 5.5V, \\ & 10 \; mA \leq I_OUT \leq 1.5A \end{split}$ | 492.5<br><b>485.</b> | 500. 507.5<br><b>515.</b> |                     |       |  |

| V <sub>ADJ</sub>                   | V <sub>ADJ</sub> Accuracy                                | $V_{OUT(NOM)}+1V \le V_{IN} \le V_{BIAS} \le 4.5V,$<br>See ( <i>Note 7</i> )<br>3.0V \le V_{BIAS} \le 5.5V,<br>10 mA $\le I_{OUT} \le 1.5A,$<br>0°C $\le T_{J} \le +125$ °C        | 490.                 | 500.                      | 510.                | mV    |  |

| V                                  | V Dongo                                                  | $3.0V \le V_{BIAS} \le 5.5V$                                                                                                                                                       | 0.80                 |                           | 1.20                |       |  |

| V <sub>OUT</sub>                   | V <sub>OUT</sub> Range                                   | $4.5V \le V_{BIAS} \le 5.5V$                                                                                                                                                       | 0.80                 |                           | 1.80 V              |       |  |

| $\Delta V_{OUT} / \Delta V_{IN}$   | Line Regulation, V <sub>IN</sub> ( <i>Note 4</i> )       | $V_{OUT(NOM)}$ +1V $\leq V_{IN} \leq V_{BIAS} \leq 4.5V$                                                                                                                           | -                    | 0.04                      | -                   | %/V   |  |

| $\Delta V_{OUT} / \Delta V_{BIAS}$ | Line Regulation, V <sub>BIAS</sub> ( <i>Note 4</i> )     | $3.0V \le V_{BIAS} \le 5.5V$                                                                                                                                                       | -                    | 0.10                      | -                   | %/V   |  |

| $\Delta V_{OUT} / \Delta I_{OUT}$  | Output Voltage Load Regulation ( <i>Note 5</i> )         | 10 mA ≤ I <sub>OUT</sub> ≤ 1.5A                                                                                                                                                    | -                    | 0.2                       | -                   | %/A   |  |

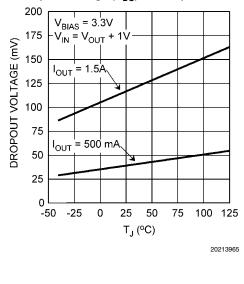

| V <sub>DO</sub>                    | Dropout Voltage (Note 6)                                 | I <sub>OUT</sub> = 1.5A                                                                                                                                                            | -                    | 130                       | 165<br><b>180</b>   | mV    |  |

| I <sub>GND(IN)</sub>               | Quiescent Current Drawn from<br>V <sub>IN</sub> Supply   | $V_{OUT} = 0.80V$<br>$V_{BIAS} = 3.0V$<br>10 mA $\leq I_{OUT} \leq 1.5A$                                                                                                           | -                    | 7.0                       | 8.5<br><b>9.0</b>   | mA    |  |

|                                    |                                                          | $V_{EN} \le 0.5V$                                                                                                                                                                  |                      | 1                         | 100<br><b>300</b>   | μA    |  |

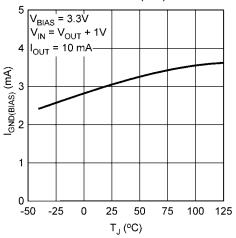

| 1                                  | Quiescent Current Drawn from<br>V <sub>BIAS</sub> Supply | 10 mA ≤ I <sub>OUT</sub> ≤ 1.5A                                                                                                                                                    | -                    | 3.0                       | 3.8<br><b>4.5</b>   | mA    |  |

| I <sub>GND(BIAS)</sub>             |                                                          | V <sub>EN</sub> ≤ 0.5V                                                                                                                                                             |                      | 100                       | 170<br><b>200</b>   | μΑ    |  |

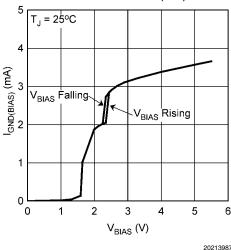

| UVLO                               | Under-Voltage Lock-Out<br>Threshold                      | V <sub>BIAS</sub> rising until device is functional                                                                                                                                | 2.20<br><b>2.00</b>  | 2.45                      | 2.70<br><b>2.90</b> | V     |  |

| UVLO <sub>(HYS)</sub>              | Under-Voltage Lock-Out<br>Hysteresis                     | V <sub>BIAS</sub> falling from UVLO threshold until device is non-functional                                                                                                       | 60<br><b>50</b>      | 150                       | 300<br><b>350</b>   | mV    |  |

| I <sub>SC</sub>                    | Output Short-Circuit Current                             | $V_{IN} = V_{OUT(NOM)} + 1V,$<br>$V_{BIAS} = 3.0V, V_{OUT} = 0.0V$                                                                                                                 | -                    | 4.5                       | -                   | А     |  |

| Symbol               | Parameter                                                              | Conditions                                               | MIN                 | ТҮР  | MAX                 | Units             |  |

|----------------------|------------------------------------------------------------------------|----------------------------------------------------------|---------------------|------|---------------------|-------------------|--|

| Soft-Start           | •                                                                      | · · · · · · · · · · · · · · · · · · ·                    |                     |      |                     |                   |  |

| r <sub>ss</sub>      | Soft-Start internal resistance                                         |                                                          | 11.0                | 13.5 | 16.0                | kΩ                |  |

| t <sub>SS</sub>      | Soft-Start time<br>$t_{SS} = C_{SS} \times r_{SS} \times 5$            | C <sub>SS</sub> = 10 nF                                  | -                   | 675  | -                   | μs                |  |

| nable                | 4                                                                      | •                                                        |                     | •    | •                   | •                 |  |

|                      |                                                                        | $V_{EN} = V_{BIAS}$                                      | -                   | 0.01 | -                   |                   |  |

| I <sub>EN</sub>      | ENABLE pin Current                                                     | V <sub>EN</sub> = 0.0V, V <sub>BIAS</sub> = 5.5V         | -19<br><b>-13</b>   | -30  | -40<br><b>-51</b>   | μΑ                |  |

| V <sub>EN(ON)</sub>  | Enable Voltage Threshold                                               | V <sub>EN</sub> rising until Output = ON                 | 1.00<br><b>0.90</b> | 1.25 | 1.50<br><b>1.55</b> | v                 |  |

| V <sub>EN(HYS)</sub> | Enable Voltage Hysteresis                                              | $V_{EN}$ falling from $V_{EN(ON)}$ until Output = OFF    | 50<br><b>30</b>     | 100  | 150<br><b>200</b>   | mV                |  |

| t <sub>OFF</sub>     | Turn-OFF Delay Time                                                    | R <sub>LOAD</sub> x C <sub>OUT</sub> << t <sub>OFF</sub> | -                   | 20   | -                   |                   |  |

| t <sub>ON</sub>      | Turn-ON Delay Time                                                     | R <sub>LOAD</sub> x C <sub>OUT</sub> << t <sub>ON</sub>  | -                   | 15   | -                   | - μs              |  |

| C Paramete           | ers                                                                    | •                                                        |                     | •    | •                   | •                 |  |

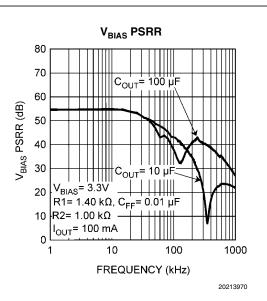

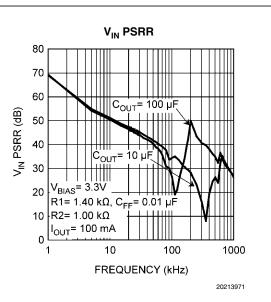

| PSRR                 | Ripple Rejection for V <sub>IN</sub> Input<br>Voltage                  | $V_{IN} = V_{OUT(NOM)} + 1V,$<br>f = 120 Hz              | -                   | 80   | -                   | - dB              |  |

| (V <sub>IN</sub> )   |                                                                        | $V_{IN} = V_{OUT(NOM)} + 1V,$<br>f = 1 kHz               | -                   | 65   | -                   |                   |  |

| PSRR                 | Ripple Rejection for V <sub>BIAS</sub> Voltage                         | $V_{BIAS} = V_{OUT(NOM)} + 3V,$<br>f = 120 Hz            | -                   | 58   | -                   |                   |  |

| (V <sub>BIAS</sub> ) |                                                                        | $V_{BIAS} = V_{OUT(NOM)} + 3V,$<br>f = 1 kHz             | -                   | 58   | -                   |                   |  |

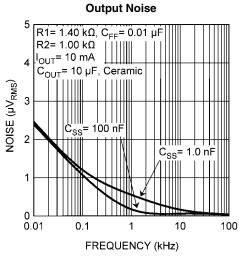

|                      | Output Noise Density                                                   | f = 120 Hz                                               | -                   | 1    | -                   | µV/√Hz            |  |

| e <sub>n</sub>       |                                                                        | BW = 10 Hz – 100 kHz                                     | -                   | 150  | -                   |                   |  |

|                      | Output Noise Voltage                                                   | BW = 300 Hz – 300 kHz                                    | -                   | 90   | -                   | μV <sub>RMS</sub> |  |

| hermal Para          | ameters                                                                | •                                                        |                     |      | •                   | •                 |  |

| $T_{SD}$             | Thermal Shutdown Junction<br>Temperature                               |                                                          | -                   | 160  | -                   | °C                |  |

| T <sub>SD(HYS)</sub> | Thermal Shutdown Hysteresis                                            |                                                          | -                   | 10   | -                   | 1                 |  |

| /                    |                                                                        | TO220-7                                                  | -                   | 60   | -                   |                   |  |

| $\theta_{J-A}$       | Thermal Resistance, Junction to Ambient ( <i>Note 3</i> )              | TO263-7                                                  | -                   | 60   | -                   |                   |  |

|                      |                                                                        | PSOP-8                                                   | -                   | 168  | -                   |                   |  |

|                      | Thermal Desisters and Investigation                                    | TO220-7                                                  | -                   | 3    | -                   | °C/W              |  |

| $\theta_{J-C}$       | Thermal Resistance, Junction to Case ( <i>Note 3</i> , <i>Note 8</i> ) | TO263-7                                                  | -                   | 3    | -                   | ]                 |  |

|                      |                                                                        | PSOP-8                                                   | -                   | 11   | -                   | 7                 |  |

Note 1: Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics.

Note 2: The human body model is a 100 pF capacitor discharged through a 1.5k resistor into each pin. Test method is per JESD22-A114.

**Note 3:** Device power dissipation must be de-rated based on device power dissipation ( $P_D$ ), ambient temperature ( $T_A$ ), and package junction to ambient thermal resistance ( $\theta_{JA}$ ). Additional heat-sinking may be required to ensure that the device junction temperature ( $T_J$ ) does not exceed the maximum operating rating. See the Application Information section for details.

Note 4: Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

**Note 5:** Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from no load to full load. **Note 6:** Dropout voltage is defined the as input to output voltage differential ( $V_{IN} - V_{OUT}$ ) where the input voltage is low enough to cause the output voltage to drop 2% from the nominal value.

Note 7:  $\rm V_{IN}$  cannot exceed either  $\rm V_{BIAS}$  or 4.5V, whichever value is lower.

**Note 8:** For TO-220 and TO-263:  $\theta_{J-C}$  refers to the BOTTOM surface of the package, under the epoxy body, as the 'CASE'. For PSOP-8:  $\theta_{J-C}$  refers to the DAP (aka: Exposed Pad) on BOTTOM surface of the package as the 'CASE'.

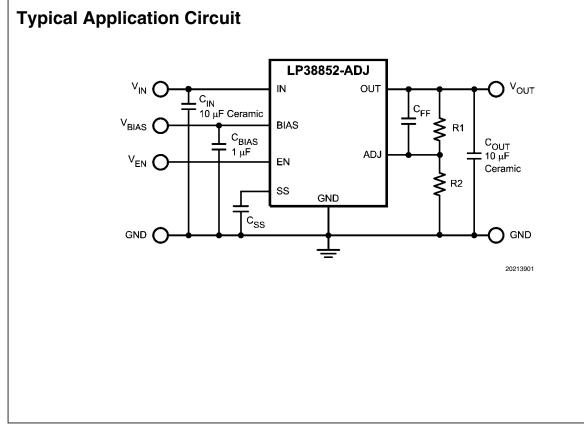

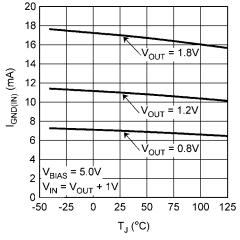

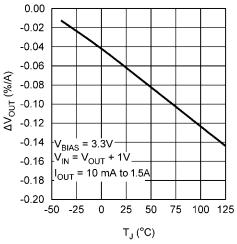

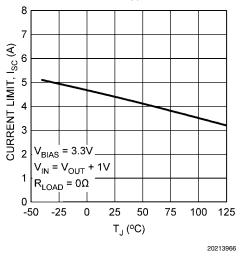

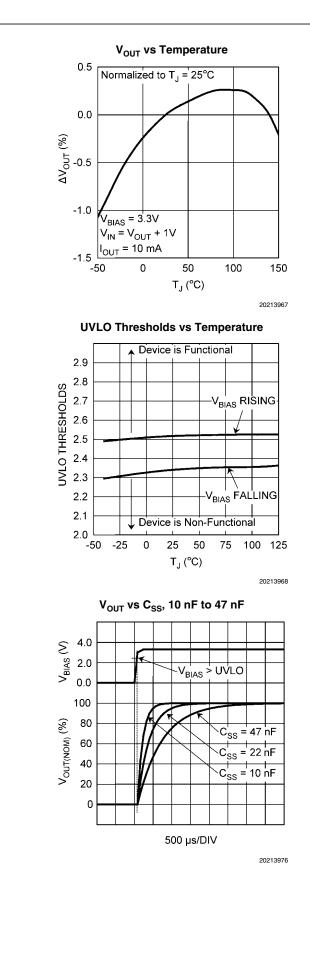

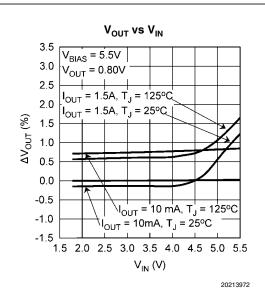

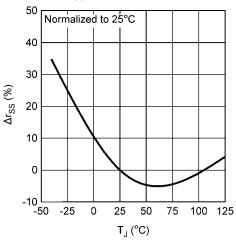

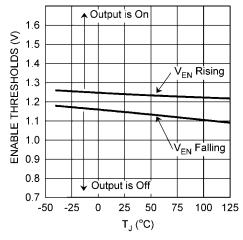

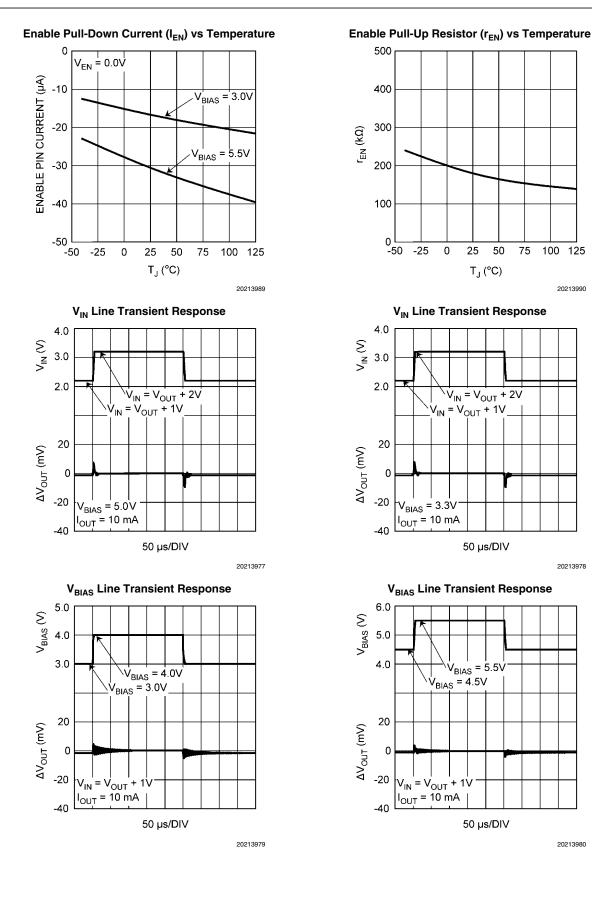

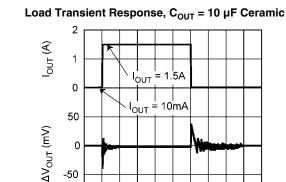

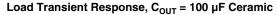

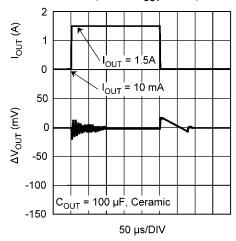

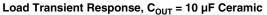

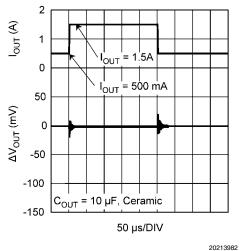

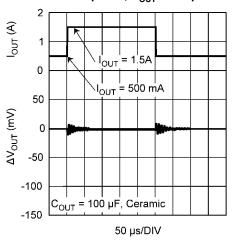

**Typical Performance Characteristics** Refer to the *Typical Application Circuit*. Unless otherwise specified:  $T_J = 25^{\circ}C$ ,  $R1 = 1.40 \text{ k}\Omega$ ,  $R2 = 1.00 \text{ k}\Omega$ ,  $C_{FF} = 0.01 \text{ }\mu\text{F}$ ,  $V_{IN} = V_{OUT(NOM)} + 1V$ ,  $V_{BIAS} = 3.0V$ ,  $I_{OUT} = 10 \text{ }\mu\text{A}$ ,  $C_{IN} = 10 \text{ }\mu\text{F}$  Ceramic,  $C_{OUT} = 10 \text{ }\mu\text{F}$  Ceramic,  $C_{BIAS} = 1 \text{ }\mu\text{F}$  Ceramic,  $C_{SS} = \text{Open}$ .

V<sub>BIAS</sub> Ground Pin Current (I<sub>GND(BIAS)</sub>) vs Temperature

**V**<sub>IN</sub> Ground Pin Current vs Temperature

Dropout Voltage (V<sub>DO</sub>) vs Temperature

LP38852

Load Regulation vs Temperature

Output Current Limit (I<sub>SC</sub>) vs Temperature

Soft-Start r<sub>SS</sub> Variation vs Temperature

20213975

#### Enable Thresholds (V<sub>EN</sub>) vs Temperature

www.ti.com

-50 -100 -150 -150 -150 -150 μF, Ceramic 50 μs/DIV

20213981

20213983

Load Transient Response,  $C_{OUT} = 100 \ \mu F$  Ceramic

20213984

Load Transient Response,  $C_{OUT}$  = 100 µF Tantalum

20213969

LP38852

LP38852

## **Application Information**

### **EXTERNAL CAPACITORS**

To assure regulator stability, input and output capacitors are required as shown in the Typical Application Circuit.

#### **Output Capacitor**

A minimum output capacitance of 10  $\mu F$ , ceramic, is required for stability. The amount of output capacitance can be increased without limit. The output capacitor must be located less than 1 cm from the output pin of the IC and returned to the device ground pin with a clean analog ground.

Only high quality ceramic types such as X5R or X7R should be used, as the Z5U and Y5F types do not provide sufficient capacitance over temperature.

Tantalum capacitors will also provide stable operation across the entire operating temperature range. However, the effects of ESR may provide variations in the output voltage during fast load transients. Using the minimum recommended 10  $\mu$ F ceramic capacitor at the output will allow unlimited capacitance, Tantalum and/or Aluminum, to be added in parallel.

#### Input Capacitor

The input capacitor must be at least 10  $\mu F,$  but can be increased without limit. It's purpose is to provide a low source impedance for the regulator input. A ceramic capacitor, X5R or X7R, is recommended.

Tantalum capacitors may also be used at the input pin. There is no specific ESR limitation on the input capacitor (the lower, the better).

Aluminum electrolytic capacitors can be used, but are not recommended as their ESR increases very quickly at cold temperatures. They are not recommended for any application where the ambient temperature falls below 0°C.

#### **Bias Capacitor**

The capacitor on the bias pin must be at least 1  $\mu$ F, and can be any good quality capacitor (ceramic is recommended).

#### Feed Forward Capacitor, C<sub>FF</sub> (Refer to the Typical Application Circuit)

When using a ceramic capacitor for  $C_{OUT}$ , the typical ESR value will be too small to provide any meaningful positive phase compensation,  $F_z$ , to offset the internal negative phase shifts in the gain loop.

$$F_{Z} = (1 / (2 \times \pi \times C_{OUT} \times ESR))$$

(1)

A capacitor placed across the gain resistor R1 will provide additional phase margin to improve load transient response of the device. This capacitor,  $C_{FF}$ , in parallel with R1, will form a zero in the loop response given by the formula:

$$F_{7} = (1 / (2 \times \pi \times C_{FF} \times R1))$$

(2)

For optimum load transient response select  $\rm C_{FF}$  so the zero frequency,  $\rm F_Z$  falls between 10 kHz and 15 kHz.

$$(C_{FF} = (1 / (2 \times \pi \times R1 \times F_Z)))$$

(3)

The phase lead provided by C<sub>FF</sub> diminishes as the DC gain approaches unity, or V<sub>OUT</sub> approaches V<sub>ADJ</sub>. This is because C<sub>FF</sub> also forms a pole with a frequency of:

$$F_{P} = (1 / (2 \times \pi \times C_{FF} \times (R1 \parallel R2)))$$

(4)

It's important to note that at higher output voltages, where R1 is much larger than R2, the pole and zero are far apart in frequency. At lower output voltages the frequency of the pole and the zero mover closer together. The phase lead provided from C<sub>FF</sub> diminishes quickly as the output voltage is reduced, and has no effect when V<sub>OUT</sub> = V<sub>ADJ</sub>. For this reason, relying on this compensation technique alone is adequate only for higher output voltages. For the LP38852, the practical minimum V<sub>OUT</sub> is 0.8V when a ceramic capacitor is used for C<sub>OUT</sub>.

FIGURE 1. F<sub>ZERO</sub> and F<sub>POLE</sub> vs Gain

#### SETTING THE OUTPUT VOLTAGE (Refer to the Typical Application Circuit)

The output voltage is set using the external resistive divider R1 and R2. The output voltage is given by the formula:

$$V_{OUT} = V_{ADJ} \times \left(1 + \left(\frac{R1}{R2}\right)\right)$$

(5)

The resistors used for R1 and R2 should be high quality, tight tolerance, and with matching temperature coefficients. It is important to remember that, although the value of  $V_{ADJ}$  is guaranteed, the use of low quality resistors for R1 and R2 can easily produce a  $V_{OUT}$  value that is unacceptable.

It is recommended that the values selected for R1 and R2 are such that the parallel value is less than 10 k $\Omega$ . This is to prevent internal parasitic capacitances on the ADJ pin from interfering with the F<sub>z</sub> pole set by R1 and C<sub>FF</sub>.

$$((R1 \times R2) / (R1 + R2)) \le 10 \text{ k}\Omega$$

(6)

Table 1 lists some suggested, best fit, standard ±1% resistor values for R1 and R2, and a standard ±10% capacitor values for C<sub>FF</sub>, for a range of V<sub>OUT</sub> values. Other values of R1, R2, and C<sub>FF</sub> are available that will give similar results.

| ΤА | BL | Е | 1. |

|----|----|---|----|

|    |    |   |    |

| V <sub>OUT</sub> | R1      | R2      | C <sub>FF</sub> | Fz       |

|------------------|---------|---------|-----------------|----------|

| 0.8V             | 1.07 kΩ | 1.78 kΩ | 12 nF           | 12.4 kHz |

| 0.9V             | 1.50 kΩ | 1.87 kΩ | 8.2 nF          | 12.9 kHz |

| 1.0V             | 1.00 kΩ | 1.00 kΩ | 12 nF           | 13.3 kHz |

| 1.1V             | 1.65 kΩ | 1.37 kΩ | 8.2 nF          | 11.8 kHz |

| 1.2V             | 1.40 kΩ | 1.00 kΩ | 10 nF           | 11.4 kHz |

| 1.3V             | 1.15 kΩ | 715 Ω   | 12 nF           | 11.5 kHz |

| 1.4V             | 1.07 kΩ | 590 Ω   | 12 nF           | 12.4 kHz |

| 1.5V             | 2.00 kΩ | 1.00 kΩ | 6.8 nF          | 11.7 kHz |

| 1.6V             | 1.65 kΩ | 750 Ω   | 8.2 nF          | 11.8 kHz |

| 1.7V             | 2.55 kΩ | 1.07 kΩ | 5.6 nF          | 11.1 kHz |

| 1.8V             | 2.94 kΩ | 1.13 kΩ | 4.7 nF          | 11.5 kHz |

Please refer to Application Note AN-1378 for additional information on how resistor tolerances affect the calculated  $\rm V_{OUT}$  value.

#### **INPUT VOLTAGE**

The input voltage (V<sub>IN</sub>) is the high current external voltage rail that will be regulated down to a lower voltage, which is applied to the load. The input voltage must be at least V<sub>OUT</sub> + V<sub>DO</sub>, and no higher than whatever value is used for V<sub>BIAS</sub>.

#### **BIAS VOLTAGE**

The bias voltage (V<sub>BIAS</sub>) is a low current external voltage rail required to bias the control circuitry and provide gate drive for the N-FET pass transistor. When V<sub>OUT</sub> is set to 1.20V, or less, V<sub>BIAS</sub> may be anywhere in the operating range of 3.0V to 5.5V. If V<sub>OUT</sub> is set higher than 1.20V, V<sub>BIAS</sub> must be between 4.5V and 5.5V to ensure proper operation of the device.

#### UNDER VOLTAGE LOCKOUT

The bias voltage is monitored by a circuit which prevents the device from functioning when the bias voltage is below the Under-Voltage Lock-Out (UVLO) threshold of approximately 2.45V.

As the bias voltage rises above the UVLO threshold the device control circuitry becomes active. There is approximately 150 mV of hysteresis built into the UVLO threshold to provide noise immunity.

When the bias voltage is between the UVLO threshold and the Minimum Operating Rating value of 3.0V the device will be functional, but the operating parameters will not be within the guaranteed limits.

#### SUPPLY SEQUENCING

There is no requirement for the order that  $V_{\rm IN}$  or  $V_{\rm BIAS}$  are applied or removed.

One practical limitation is that the Soft-Start circuit starts charging  $C_{SS}$  when both  $V_{BIAS}$  rises above the UVLO threshold and the Enable pin is above the  $V_{EN(ON)}$  threshold. If the application of  $V_{IN}$  is delayed beyond this point the benefits of Soft-Start will be compromised.

In any case, the output voltage cannot be guaranteed until both  $V_{\rm IN}$  and  $V_{\rm BIAS}$  are within the range of guaranteed operating values.

If used in a dual-supply system where the regulator output load is returned to a negative supply, the output pin must be diode clamped to ground. A Schottky diode is recommended for this diode clamp.

www.ti.com

A reverse voltage condition will exist when the voltage at the output pin is higher than the voltage at the input pin. Typically this will happen when V<sub>IN</sub> is abruptly taken low and C<sub>OUT</sub> continues to hold a sufficient charge such that the input to output voltage becomes reversed.

The NMOS pass element, by design, contains no body diode. This means that, as long as the gate of the pass element is not driven, there will not be any reverse current flow through the pass element during a reverse voltage event. The gate of the pass element is not driven when  $V_{\text{BIAS}}$  is below the UVLO threshold, or when the Enable pin is held low.

When  $V_{BIAS}$  is above the UVLO threshold, and the Enable pin is above the  $V_{EN(ON)}$  threshold, the control circuitry is active and will attempt to regulate the output voltage. Since the input voltage is less than the output voltage the control circuit will drive the gate of the pass element to the full  $V_{BIAS}$  potential when the output voltage begins to fall. In this condition, reverse current will flow from the output pin to the input pin , limited only by the  $R_{DS(ON)}$  of the pass element and the output to input voltage differential. Discharging an output capacitor up 1000  $\mu F$  in this manner will not damage the device as the current will rapidly decay. However, continuous reverse current should be avoided.

#### SOFT-START

The LP38852 incorporates a Soft-Start function that reduces the start-up current surge into the output capacitor (C<sub>OUT</sub>) by allowing V<sub>OUT</sub> to rise slowly to the final value. This is accomplished by controlling V<sub>REF</sub> at the SS pin. The soft-start timing capacitor (C<sub>SS</sub>) is internally held to ground until both V<sub>BIAS</sub> rises above the Under-Voltage Lock-Out threshold (ULVO) and the Enable pin is higher than the V<sub>EN(ON)</sub> threshold.

$V_{\mathsf{REF}}$  will rise at an RC rate defined by the internal resistance of the SS pin ( $r_{SS}$ ), and the external capacitor connected to the SS pin. This allows the output voltage to rise in a controlled manner until steady-state regulation is achieved. Typically, five time constants are recommended to assure that the output voltage is sufficiently close to the final steady-state value. During the soft-start time the output current can rise to the built-in current limit.

Soft-Start Time =

$$C_{SS} \times r_{SS} \times 5$$

(7)

Since the  $V_{OUT}$  rise will be exponential, not linear, the in-rush current will peak during the first time constant (T), and  $V_{OUT}$  will require four additional time constants (4T) to reach the final value (5T) .

After achieving normal operation, should either V<sub>BIAS</sub> fall below the ULVO threshold, or the Enable pin fall below the V<sub>EN</sub> (<sub>OFF</sub>) threshold, the device output will be disabled and the Soft-Start capacitor (C<sub>SS</sub>) discharge circuit will become active. The C<sub>SS</sub> discharge circuit will remain active until V<sub>BIAS</sub> falls to 500 mV (typical). When V<sub>BIAS</sub> falls below 500 mV (typical), the C<sub>SS</sub> discharge circuit will cease to function due to a lack of sufficient biasing to the control circuitry.

Since  $V_{REF}$  appears on the SS pin, any leakage through  $C_{SS}$  will cause  $V_{REF}$  to fall, and thus affect  $V_{OUT}$ . A leakage of 50 nA (about 10 MΩ) through  $C_{SS}$  will cause  $V_{OUT}$  to be approximately 0.1% lower than nominal, while a leakage of 500 nA (about 1 MΩ) will cause  $V_{OUT}$  to be approximately 1% lower than nominal. Typical ceramic capacitors will have a factor of 10X difference in leakage between 25°C and 85°C, so the maximum ambient temperature must be included in the capacitor selection process.

Typical C<sub>SS</sub> values will be in the range of 1 nF to 100 nF, providing typical Soft-Start times in the range of 70 µs to 7 ms (5τ). Values less than 1 nF can be used, but the Soft-Start effect will be minimal. Values larger than 100 nF will provide soft-start, but may not be fully discharged if V<sub>BIAS</sub> falls from the UVLVO threshold to less than 500 mV in less than 100 µs.

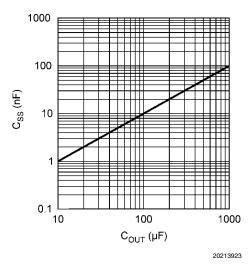

Figure 2 shows the relationship between the  $\rm C_{OUT}$  value and a typical  $\rm C_{SS}$  value.

FIGURE 2. Typical C<sub>SS</sub> vs C<sub>OUT</sub> Values

The  $C_{\rm SS}$  capacitor must be connected to a clean ground path back to the device ground pin. No components, other than  $C_{\rm SS}$ , should be connected to the SS pin, as there could be adverse effects to  $V_{\rm OUT}.$

If the Soft-Start function is not needed the SS pin should be left open, although some minimal capacitance value is always recommended.

#### **ENABLE OPERATION**

The Enable pin (EN) provides a mechanism to enable, or disable, the regulator output stage. The Enable pin has an internal pull-up, through a typical 180 k $\Omega$  resistor, to V<sub>BIAS</sub>.

If the Enable pin is actively driven, pulling the Enable pin above the V<sub>EN</sub> threshold of 1.25V (typical) will turn the regulator output on, while pulling the Enable pin below the V<sub>EN</sub> threshold will turn the regulator output off. There is approximately 100 mV of hysteresis built into the Enable threshold provide noise immunity.

If the Enable function is not needed this pin should be left open, or connected directly to  $V_{BIAS}$ . If the Enable pin is left open, stray capacitance on this pin must be minimized, otherwise the output turn-on will be delayed while the stray capacitance is charged through the internal resistance ( $r_{EN}$ ).

#### POWER DISSIPATION AND HEAT-SINKING

Additional copper area for heat-sinking may be required depending on the maximum device dissipation ( $P_D$ ) and the maximum anticipated ambient temperature ( $T_A$ ) for the device. Under all possible conditions, the junction temperature must be within the range specified under operating conditions.

The total power dissipation of the device is the sum of three different points of dissipation in the device.

The first part is the power that is dissipated in the NMOS pass element, and can be determined with the formula:

$$\mathsf{P}_{\mathsf{D}(\mathsf{PASS})} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{I}_{\mathsf{OUT}} \tag{8}$$

The second part is the power that is dissipated in the bias and control circuitry, and can be determined with the formula:

$$\mathsf{P}_{\mathsf{D}(\mathsf{BIAS})} = \mathsf{V}_{\mathsf{BIAS}} \times \mathsf{I}_{\mathsf{GND}(\mathsf{BIAS})} \tag{9}$$

where  $I_{GND(BIAS)}$  is the portion of the operating ground current of the device that is related to  $V_{BIAS}.$

The third part is the power that is dissipated in portions of the output stage circuitry, and can be determined with the formula:

$$P_{D(IN)} = V_{IN} \times I_{GND(IN)}$$

(10)

where  $I_{\text{GND}(\text{IN})}$  is the portion of the operating ground current of the device that is related to  $V_{\text{IN}}.$

The total power dissipation is then:

$$P_{\rm D} = P_{\rm D(PASS)} + P_{\rm D(BIAS)} + P_{\rm D(IN)}$$

(11)

The maximum allowable junction temperature rise  $(\Delta T_J)$  depends on the maximum anticipated ambient temperature  $(T_A)$  for the application, and the maximum allowable operating junction temperature  $(T_{J(MAX)})$ .

$$\Delta T_{\rm J} = T_{\rm J(MAX)} - T_{\rm A(MAX)} \tag{12}$$

The maximum allowable value for junction to ambient Thermal Resistance,  $\theta_{JA}$ , can be calculated using the formula:

$$\theta_{JA} \le \frac{\Delta T_J}{P_D}$$

(13)

#### Heat-Sinking The TO-220 Package

The TO-220 package has a  $\theta_{JA}$  rating of 60°C/W and a  $\theta_{JC}$  rating of 3°C/W. These ratings are for the package only, no additional heat-sinking, and with no airflow. If the needed  $\theta_{JA}$ , as calculated above, is greater than or equal to 60°C/W then no additional heat-sinking is required since the package can safely dissipate the heat and not exceed the operating  $T_{J(MAX)}$ . If the needed  $\theta_{JA}$  is less than 60°C/W then additional heat-sinking is needed.

The thermal resistance of a TO-220 package can be reduced by attaching it to a heat sink or a copper plane on a PC board. If a copper plane is to be used, the values of  $\theta_{JA}$  will be same as shown in next section for TO-263 package.

The heat-sink to be used in the application should have a heat-sink to ambient thermal resistance,  $\theta_{HA}$ :

$$\theta_{HA} \le \theta_{JA} - (\theta_{CH} + \theta_{JC}) \tag{14}$$

where  $\theta_{JA}$  is the required total thermal resistance from the junction to the ambient air,  $\theta_{CH}$  is the thermal resistance from the case to the surface of the heart-sink, and  $\theta_{JC}$  is the thermal resistance from the junction to the surface of the case.

For this equation,  $\theta_{JC}$  is about 3°C/W for a TO-220 package. The value for  $\theta_{CH}$  depends on method of attachment, insulator, etc.  $\theta_{CH}$  varies between 1.5°C/W to 2.5°C/W. Consult the

heat-sink manufacturer datasheet for details and recommendations.

#### Heat-Sinking The TO-263 Package

The TO-263 package has a  $\theta_{JA}$  rating of 60°C/W, and a  $\theta_{JC}$  rating of 3°C/W. These ratings are for the package only, no additional heat-sinking, and with no airflow.

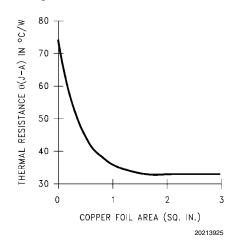

The TO-263 package uses the copper plane on the PCB as a heat-sink. The tab of this package is soldered to the copper plane for heat sinking. shows a curve for the  $\theta_{JA}$  of TO-263 package for different copper area sizes, using a typical PCB with 1 ounce copper and no solder mask over the copper area for heat-sinking.

# FIGURE 3. $\theta_{JA}$ vs Copper (1 Ounce) Area for the TO-263 package

*Figure 3* shows that increasing the copper area beyond 1 square inch produces very little improvement. The minimum value for  $\theta_{JA}$  for the TO-263 package mounted to a PCB is 32°C/W.

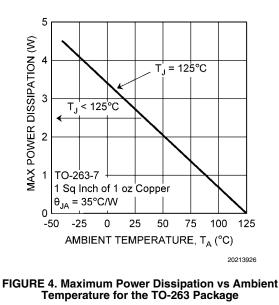

*Figure 4* shows the maximum allowable power dissipation for TO-263 packages for different ambient temperatures, assum-

ing  $\theta_{JA}$  is 35°C/W and the maximum junction temperature is 125°C.

#### Heat-Sinking The PSOP-8 Package

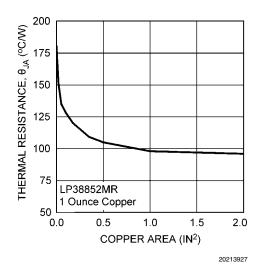

The LP38852MR package has a  $\theta_{JA}$  rating of 168°C/W, and a  $\theta_{JC}$  rating of 11°C/W. The  $\theta_{JA}$  rating of 168°C/W includes the device DAP soldered to an area of 0.008 square inches (0.09 in x 0.09 in) of 1 ounce copper, with no airflow.

FIGURE 5.  $\theta_{JA}$  vs Copper (1 Ounce) Area for the PSOP-8 Package

Increasing the copper area soldered to the DAP to 1 square inch of 1 ounce copper, using a dog-bone type layout, will improve the  $\theta_{JA}$  rating to 98°C/W. *Figure 5* shows that increasing the copper area beyond 1 square inch produces very little improvement.

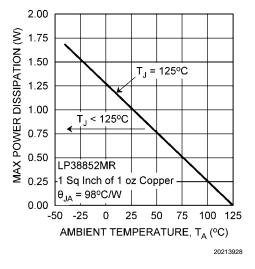

#### FIGURE 6. Maximum Power Dissipation vs Ambient Temperature for the PSOP-8 Package

*Figure 6* shows the maximum allowable power dissipation for the PSOP-8 package for a range of ambient temperatures, assuming that  $\theta_{JA}$  is 98°C/W and the maximum junction temperature is 125°C.

Notes

### TI/NATIONAL INTERIM IMPORTANT NOTICE

Texas Instruments has purchased National Semiconductor. As of Monday, September 26th, and until further notice, products sold or advertised under the National Semiconductor name or logo, and information, support and interactions concerning such products, remain subject to the preexisting National Semiconductor standard terms and conditions of sale, terms of use of website, and Notices (and/or terms previously agreed in writing with National Semiconductor, where applicable) and are not subject to any differing terms and notices applicable to other TI components, sales or websites. To the extent information on official TI and National websites and business social networking media, etc., pertains to both TI and National-branded products, both companies' instructions, warnings and limitations in the above-referenced terms of use apply.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Product                                        | s                      | Appl                                | cations                               |  |  |  |

|------------------------------------------------|------------------------|-------------------------------------|---------------------------------------|--|--|--|

| Audio                                          | www.ti.com/audio       | Communications and Telecom          | www.ti.com/communications             |  |  |  |

| Amplifiers                                     | amplifier.ti.com       | Computers and Peripherals           | www.ti.com/computers                  |  |  |  |

| Data Converters                                | dataconverter.ti.com   | Consumer Electronics                | www.ti.com/consumer-apps              |  |  |  |

| DLP® Products                                  | www.dlp.com            | Energy and Lighting                 | www.ti.com/energy                     |  |  |  |

| DSP                                            | dsp.ti.com             | Industrial                          | www.ti.com/industrial                 |  |  |  |

| Clocks and Timers                              | www.ti.com/clocks      | Medical                             | www.ti.com/medical                    |  |  |  |

| Interface                                      | interface.ti.com       | Security                            | www.ti.com/security                   |  |  |  |

| Logic                                          | logic.ti.com           | Space, Avionics and Defense         | www.ti.com/space-avionics-<br>defense |  |  |  |

| Power Mgmt                                     | power.ti.com           | Transportation and Automotive       | www.ti.com/automotive                 |  |  |  |

| Microcontrollers                               | microcontroller.ti.com | Video and Imaging                   | www.ti.com/video                      |  |  |  |

| RFID                                           | www.ti-rfid.com        | Wireless                            | www.ti.com/wireless-apps              |  |  |  |

| RF/IF and ZigBee® Solutions                    | www.ti.com/lprf        | TI E2E Community Home Page          | e2e.ti.com                            |  |  |  |

| Mailing A                                      | ddress: Texas Instrume | ents, Post Office Box 655303, Dalla | as, Texas 75265                       |  |  |  |

| Copyright© 2011 Texas Instruments Incorporated |                        |                                     |                                       |  |  |  |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u llama Dava                  | -0- #                             |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated