Downloaded from Elcodis.com electronic components distributor

#### LM5030 **100V Push-Pull Current Mode PWM Controller General Description** Features

The LM5030 High Voltage PWM controller contains all of the features needed to implement Push-Pull and Bridge topologies, using current-mode control in a small 10 pin package. This device provides two alternating gate driver outputs. The LM5030 includes a high-voltage start-up regulator that operates over a wide input range of 14V to 100V. Additional features include: error amplifier, precision reference, dual mode current limit, slope compensation, softstart, sync capability and thermal shutdown. This high speed IC has total propagation delays less than 100ns and a 1MHz capable single resistor adjustable oscillator.

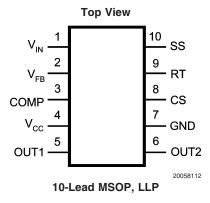

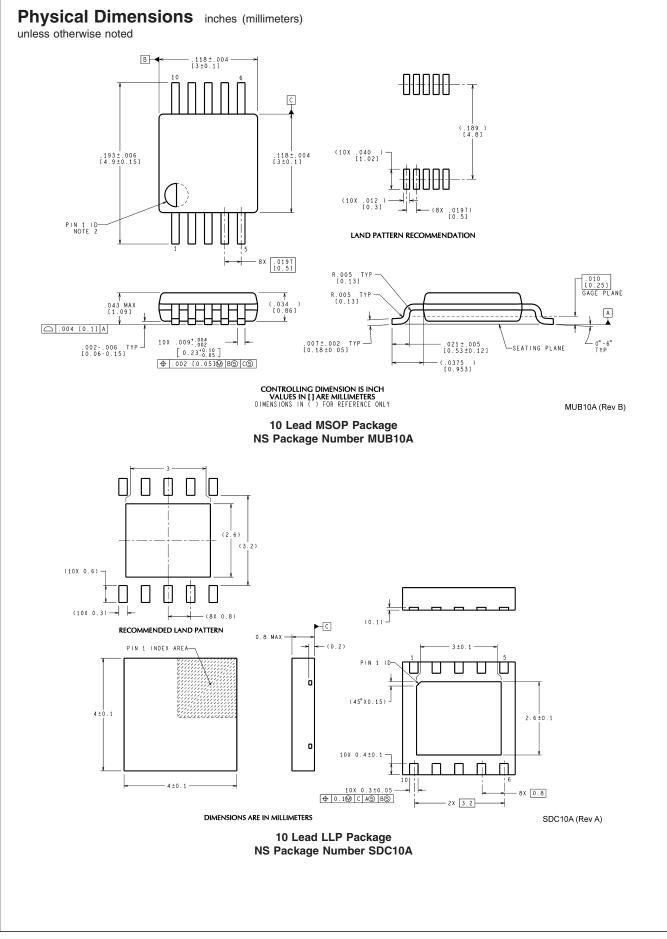

Package: MSOP-10 and thermally enhanced LLP-10 (4mm x 4mm).

- Internal High Voltage Start-up Regulator

- Single Resistor Oscillator Setting

- Synchronizable

- Error Amplifier

- Precision Reference

- Adjustable Softstart

- Dual Mode Over-Current Protection

- Slope Compensation

- Direct Optocoupler Interface

- 1.5A Peak Gate Drivers

- Thermal Shutdown

#### Applications

- Telecommunication Power Converters

- Industrial Power Converters

- +42V Automotive Systems

#### **Connection Diagram**

### **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Supplies As                 |

|--------------|--------------|---------------------|-----------------------------|

| LM5030MM     | MSOP-10      | MUB10A              | 1000 Units on Tape and Reel |

| LM5030MMX    | MSOP-10      | MUB10A              | 3500 Units on Tape and Reel |

| LM5030SD     | LLP-10       | SDC10A              | 1000 Units on Tape and Reel |

| LM5030SDX    | LLP-10       | SDC10A              | 4500 Units on Tape and Reel |

March 2005

LM5030

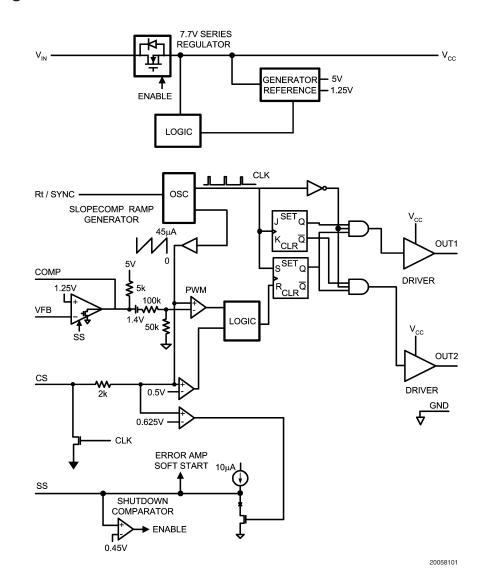

# Block Diagram

FIGURE 1.

#### **Pin Description** Pin Name Pin Description **Application Information** Number VIN 1 Source Input Voltage Input to start-up regulator. Input range 14 to 100 Volts. 2 V<sub>FB</sub> The non-inverting input is internally connected to a 1.25 Volt Inverting input to the error amplifier reference. COMP 3 Output to the error amplifier There is an internal 5K resistor pull-up on this pin. The error amplifier provides an active sink. Vcc 4 Output from the internal high If an auxiliary winding raises the voltage on this pin above the voltage series pass regulator. The regulation setpoint the internal series pass regulator will regulation setpoint is 7.7 Volts. shutdown, reducing the IC power dissipation. OUT1 Output of the PWM controller 5 Alternating PWM output gate driver. OUT2 6 Output of the PWM controller Alternating PWM output gate driver. GND 7 Return Ground CS 8 Current sense input Current sense input for current mode control and current limit sensing. Using separate dedicated comparators, if CS exceeds 0.5 Volt the outputs will go into Cycle by Cycle current limit. If CS exceeds 0.625V the outputs will be disabled and a softstart commenced. RT 9 An external resistor sets the oscillator frequency. This pin will Oscillator timing resistor pin and synchronization input. also accept synchronization pulses from an external oscillator. SS 10 Dual purpose Softstart and A 10µA current source and an external capacitor set the softstart Shutdown pin timing length. The controller will enter a low power state if the SS pin is pulled below the typical shutdown threshold of 0.45V. LLP SUB Die Substrtae The exposed die attach pad on the LLP package should be DAP connected to a PCB thermal pad at ground potential. For additional information on using National Semiconductor's No Pull Back LLP package, please refer to LLP Application Note AN-1187.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| V <sub>IN</sub> to GND (Survival) | -0.3V to 100V      |

|-----------------------------------|--------------------|

| V <sub>CC</sub> to GND (Survival) | -0.3V to 16V       |

| RT to GND (Survival)              | -0.3V to 5.5V      |

| All other pins to GND (Survival)  | -0.3V to 7V        |

| Power Dissipation (Note 2)        | Internally Limited |

| ESD Rating (Note 3)               |                    |

| Human Body Model                  | 2kV                |

| Machine Model                     | 200V               |

|                                   |                    |

| Lead Temperature          |                 |

|---------------------------|-----------------|

| (Soldering 4 seconds)     | 260°C           |

| Storage Temperature Range | -55°C to +150°C |

| Junction Temperature      | 150°C           |

|                           |                 |

# **Operating Ratings**

| Junction Temperature | -40°C to +105°C |

|----------------------|-----------------|

| V <sub>IN</sub>      | 14V to 90V      |

# **Electrical Characteristics**

Specifications in standard type face are for  $T_J$ = +25°C and those in **boldface type** apply over the full operating junction temperature range. Unless otherwise specified:  $V_{IN}$  = 48V,  $V_{CC}$  = 10V, and RT = 26.7K $\Omega$

| Symbol                 | Parameter                                          | Conditions                                                                      | Min<br>(Note 4)   | <b>Typ</b><br>(Note 5) | Max<br>(Note 4) | Units |

|------------------------|----------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------------|-----------------|-------|

| Startup Reg            | gulator                                            |                                                                                 |                   | , ,                    |                 |       |

| V <sub>cc</sub> Reg    | V <sub>CC</sub> Regulation                         | open ckt                                                                        | 7.4               | 7.7                    | 8.0             | V     |

|                        | V <sub>CC</sub> Current Limit                      | (Note 2)                                                                        | 10                | 17                     |                 | mA    |

| I-V <sub>IN</sub>      | Startup Regulator Leakage<br>(external Vcc Supply) | V <sub>IN</sub> = 90V                                                           |                   | 150                    | 500             | μA    |

| I <sub>IN</sub>        | Shutdown Current                                   | SS = 0V, $V_{CC}$ = open                                                        |                   | 250                    | 350             | μA    |

| V <sub>cc</sub> Supply | ,                                                  |                                                                                 |                   |                        |                 |       |

|                        | V <sub>CC</sub> undervoltage Lockout<br>Voltage    |                                                                                 | VccReg<br>- 300mV | VccReg -<br>100mV      |                 | V     |

|                        | Undervoltage Hysteresis                            |                                                                                 | 1.2               | 1.6                    | 2.1             | V     |

| I <sub>cc</sub>        | Supply Current                                     | Cload = 0                                                                       |                   | 2                      | 3               | mA    |

| Error Ampl             | ifier                                              |                                                                                 |                   |                        | · · ·           |       |

| GBW                    | Gain Bandwidth                                     |                                                                                 |                   | 4                      |                 | MHz   |

|                        | DC Gain                                            |                                                                                 |                   | 75                     |                 | dB    |

|                        | Input Voltage                                      | V <sub>FB</sub> = COMP                                                          | 1.220             | 1.245                  | 1.270           | V     |

|                        | COMP Sink Capability                               | V <sub>FB</sub> = 1.5V COMP= 1V                                                 | 5                 | 13                     |                 | mA    |

| Current Lin            | nit                                                |                                                                                 |                   |                        |                 |       |

| CS1                    | Cycle by Cycle CS Threshold<br>Voltage             |                                                                                 | 0.45              | 0.5                    | 0.55            | V     |

| CS2                    | Restart CS Threshold Voltage                       | Resets SS capacitor; auto restart                                               | 0.575             | 0.625                  | 0.675           | V     |

|                        | ILIM Delay to Output                               | CS step from 0 to 0.6V<br>Time to onset of OUT<br>Transition (90%)<br>Cload = 0 |                   | 30                     |                 | ns    |

|                        | CS Sink Current (clocked)                          | CS = 0.3V                                                                       | 3                 | 6                      |                 | mA    |

| Soft Start/S           | Shutdown                                           |                                                                                 | · · · · · ·       |                        |                 |       |

|                        | Softstart Current Source                           |                                                                                 | 7                 | 10                     | 13              | μA    |

|                        | Softstart to COMP Offset                           |                                                                                 | 0.25              | 0.5                    | 0.75            | V     |

|                        | Shutdown Threshold                                 |                                                                                 | 0.2               | 0.45                   | 0.7             | V     |

#### Electrical Characteristics (Continued)

| Specifications in standard type face are for $T_{J}$ = +25°C and those in <b>boldface type</b> apply over the full operating junction tem- |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| perature range. Unless otherwise specified: $V_{IN}$ = 48V, $V_{CC}$ = 10V, and RT = 26.7K $\Omega$                                        |  |

| Symbol     | Parameter                      | Conditions                                                                        | Min      | Тур      | Max      | Units |

|------------|--------------------------------|-----------------------------------------------------------------------------------|----------|----------|----------|-------|

|            |                                |                                                                                   | (Note 4) | (Note 5) | (Note 4) |       |

| Oscillator |                                |                                                                                   |          |          |          |       |

|            | Frequency1 (RT = 26.7K)        |                                                                                   | 175      | 200      | 225      | kHz   |

|            | Frequency2 (RT = 8.2K)         |                                                                                   | 510      | 600      | 690      | kHz   |

|            | Sync threshold                 |                                                                                   |          | 3.2      | 3.8      | V     |

| PWM Comp   | parator                        |                                                                                   |          |          |          |       |

|            | Delay to Output                | COMP set to 2V CS<br>stepped 0 to 0.4V, Time<br>to onset of OUT transition<br>low |          | 30       |          | ns    |

|            | Max Duty Cycle                 | Inferred from deadtime                                                            | 47.5     | 49       | 50       | %     |

|            | Min Duty Cycle                 | COMP=0V                                                                           |          |          | 0        | %     |

|            | COMP to PWM Comparator<br>Gain |                                                                                   |          | 0.34     |          |       |

|            | COMP Open Circuit Voltage      | V <sub>FB</sub> = 0V                                                              | 4.3      | 5.2      | 6.1      | V     |

|            | COMP Short Circuit Current     | V <sub>FB</sub> = 0V, COMP=0V                                                     | 0.6      | 1.1      | 1.5      | mA    |

| Slope Com  | pensation                      | •                                                                                 |          |          |          |       |

|            | Slope Comp Amplitude           | Delta increase at PWM<br>Comparator to CS                                         | 80       | 105      | 130      | mV    |

| Output Sec | tion                           |                                                                                   |          |          |          |       |

|            | Deadtime                       | Cload = 0, 10% to 10%                                                             | 85       | 135      | 185      | ns    |

|            | Output High Saturation         | lout = 50mA, $V_{CC}$ - $V_{OUT}$                                                 |          | 0.25     | 0.75     | V     |

|            | Output Low Saturation          | I <sub>OUT</sub> = 100mA                                                          |          | 0.25     | 0.75     | V     |

|            | Rise Time                      | Cload = 1nF                                                                       |          | 16       |          | ns    |

|            | Fall Time                      | Cload = 1nF                                                                       |          | 16       |          | ns    |

| Thermal Sh | nutdown                        |                                                                                   |          |          | · · ·    |       |

| Tsd        | Thermal Shutdown Temp.         |                                                                                   |          | 165      |          | °C    |

|            | Thermal Shutdown Hysteresis    |                                                                                   |          | 15       |          | °C    |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

**Note 2:** The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(MAX)}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \frac{\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{J}\mathsf{A}}}$$

Where the value of  $\theta_{JA}$  for the mini SO-10 (MM) package is 200°C/W. Exceeding the maximum allowable dissipation will cause excessive die temperature, and the device will go into thermal shutdown.

Note 3: The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin. The machine model ESD rating for pin 5 and pin 6 is 150V.

Note 4: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 5: Typical numbers represent the most likely parametric norm for 25°C operation.

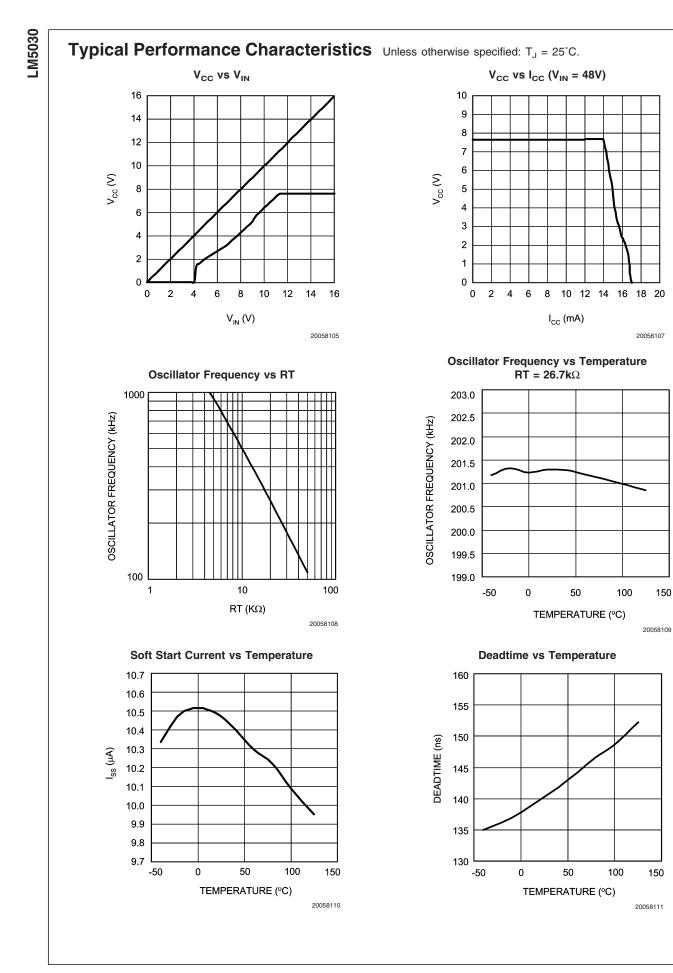

#### Typical Performance Characteristics Unless otherwise specified: T<sub>J</sub> = 25°C. (Continued)

### **Detailed Operating Description**

The LM5030 High Voltage PWM controller contains all of the features needed to implement Push-Pull and Bridge topologies, using current-mode control in a small 10 pin package. Features included are, startup regulator, dual mode current limit, dual alternating gate drivers, thermal shutdown, softstart and slope compensation. This high speed IC has total propagation delays <100nS. The Functional Block Diagram of the LM5030 is shown in *Figure 1*.

The LM5030 is designed for Current-Mode Control converters which require alternating outputs, such as Push-Pull and Half/Full Bridge topologies. The features included in the LM5030 enable all of the advantages of Current-Mode Control, line feed-forward, cycle by cycle current limit and simplified loop compensation. The oscillator ramp is internally buffered and added to the PWM comparator input to provide slope compensation necessary for current mode control at higher duty cycles.

# High Voltage Start-Up Regulator

The LM5030 contains an internal high voltage startup regulator. The input pin (Vin) can be connected directly to line voltages as high as 100V. The regulator output is internally current limited to 10mA. Upon power up, the regulator is enabled and sources current into an external capacitor connected to the V<sub>CC</sub> pin. The recommended capacitance range for the  $V_{CC}$  regulator is 0.1µF to 50µF. When the voltage on the  $V_{\rm CC}$  pin reaches the regulation point of 7.7V, the controller outputs are enabled. The outputs will remain enabled unless,  $V_{CC}$  falls below 6.1V or if the SS/SHUTDOWN pin is pulled to ground or an over temperature condition occurs. In typical applications, an auxiliary transformer winding is diode connected to the  $V_{CC}$  pin. This winding raises the  $V_{CC}$ voltage greater than 8V, effectively shutting off the internal startup regulator and saving power while reducing the controller dissipation. The external  $V_{\rm CC}$  capacitor must be sized such that the self-bias will maintain a  $V_{\text{CC}}$  voltage greater than 6.1V during the initial start-up. During a fault mode when the converter self bias winding is inactive, external current draw on the  $V_{CC}$  line should be limited as to not exceed the maximum power dissipation of the controller. An external start-up or other bias rail can be used instead of the internal start-up regulator by connecting the  $V_{\rm CC}$  and the Vin pins and feeding the external bias voltage (8 - 15V) to that node.

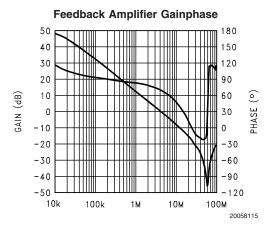

#### **Error Amplifier**

An internal high gain error amplifier is provided within the LM5030. The amplifier's non-inverting reference is tied to 1.25V. In non-isolated applications the power converter output is connected to the VFB pin via the voltage setting resistors and loop compensation is connected between the COMP and VFB pins.

For most isolated applications the error amplifier function is implemented on the secondary side ground. Since the internal error amplifier is configured as an open drain output it can be disabled by connecting VFB to ground. The internal 5K pull-up resistor, connected between the 5V reference and COMP, can be used as the pull-up for an optocoupler or other isolation device.

#### **PWM Comparator**

The PWM comparator compares the compensated current ramp signal to the loop error voltage from the internal error amplifier (COMP pin). This comparator is optimized for speed in order to achieve minimum discernable duty cycles. The comparator polarity is such that zero Volts on the COMP pin will cause a zero duty cycle.

# **Current Limit/ Current Sense**

The LM5030 contains two levels of over-current protection. If the voltage on the current sense comparator exceeds 0.5 Volts the present cycle is terminated (cycle by cycle current limit). If the voltage on the current sense comparator exceeds 0.625 Volts, the controller will terminate the present cycle and discharge the softstart capacitor. A small RC filter, located near the controller, is recommended for the CS pin. An internal MOSFET discharges the current sense filter capacitor at the conclusion of every cycle, to improve dynamic performance.

The LM5030 CS and PWM comparators are very fast, and as such will respond to short duration noise pulses. Layout considerations are critical for the current sense filter and sense resistor. The capacitor associated with the CS filter must be placed very close to the device and connected directly to the pins of the IC (CS and RTN). Also if a current sense transformer is used, both leads of the transformer secondary should be routed to the sense resistor, which should also be located close to the IC. If a current sense resistor located in the drive transistor sources is used, for current sense, a low inductance resistor should be chosen.

# **Current Limit/ Current Sense**

(Continued)

In this case all of the noise sensitive low power grounds should be commoned together around the IC and then a single connection should be made to the power ground (sense resistor ground point).

The second level threshold is intended to protect the power converter by initiating a low duty cycle hiccup mode when abnormally high, fast rising currents occur. During excessive loading, the first level threshold will always be reached and the output characteristic of the converter will be that of a current source but this sustained current level can cause excessive temperatures in the power train especially the output rectifiers. If the second level threshold is reached, the softstart capacitor will be fully discharged, a retry will commence following the discharge detection. The second level threshold will only be reached when a high dV/dt is present at the current sense pin. The signal must be fast enough to reach the second level threshold before the first threshold detector turns off the driver. This can usually happen for a saturated power inductor or shorted load. Excessive filtering on the CS pin, extremely low value current sense resistor or an inductor that does not saturate with excessive loading may prevent the second level threshold from ever being reached.

# Oscillator, Shutdown and Sync Capability

The LM5030 oscillator is set by a single external resistor connected between the RT pin and return. To set a desired oscillator frequency the necessary RT resistor can be calculated as:

$$\mathsf{RT} = \frac{(1/\mathsf{F}) - 172 \times 10^{-9}}{182 \times 10^{-12}}$$

Each output switches at half the oscillator frequency in a Push-Pull configuration. The LM5030 can also be synchronized to an external clock. The external clock must be of higher frequency than the free running frequency set by the RT resistor. The clock signal should be capacitively coupled into the RT pin with a 100pF capacitor. A peak voltage level greater than 3 Volts with respect to ground is required for detection of the sync pulse. The sync pulse width should be set in the 15 to 150nS range by the external components. The RT resistor is always required, whether the oscillator is free running or externally synchronized. The voltage at the RT pin is internally regulated to a nominal 2 Volts. The RT resistor should be located very close to the device and connected directly to the pins of the IC (RT and GND).

#### **Slope Compensation**

The PWM comparator compares the current sense signal to the voltage derived from the COMP pin. The COMP voltage is set by either the internal error amplifier or an external error amplifier through an optocoupler. At duty cycles greater than 50% (composite of alternating outputs) current mode control circuits are prone to subharmonic oscillation. By adding an additional ramp signal to the current sense ramp signal this condition can be avoided. The LM5030 integrates this slope compensation by buffering the internal oscillator ramp and summing it internally to the current sense (CS) signal. Additional slope compensation may be added by increasing the source impedance of the current sense signal.

#### Soft Start/ Shutdown

The softstart feature allows the converter to gradually reach the initial steady state operating point, thus reducing start-up stresses and surges. An internal 10uA current source and an external capacitor generate a ramping voltage signal which limits the error amplifier output during start-up. In the event of a second level current limit fault, the softstart capacitor will be fully discharged which disables the output drivers. When the fault condition is no longer present, the softstart capacitor is released to ramp and gradually restart the converter. The SS pin can also be used to disable the controller. If the SS pin voltage is pulled down below 0.45V (nominal) the controller will disable the outputs and enter a low power state.

#### OUT1, OUT2 and Time Delay

The LM5030 provides two alternating outputs, OUT1 and OUT2. The internal gate drivers can each sink 1.5A peak each. The maximum duty cycle for each output is inherently limited to less than 50%. The typical deadtime between the falling edge of one gate driver output and the rising edge of the other gate driver output is 135ns.

### **Thermal Protection**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event the excessive junction temperature. When activated, typically at 165 degrees Celsius, the controller is forced into a low power reset state, disabling the output drivers and the bias regulator. This feature is provided to prevent catastrophic failures from accidental device overheating.

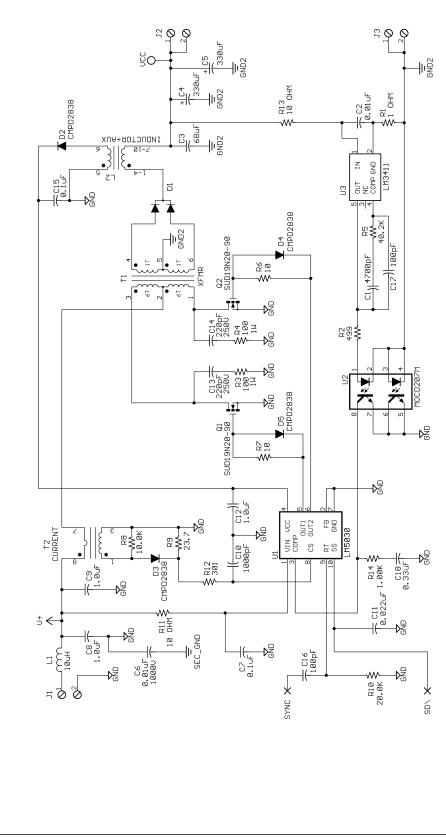

ation Circuit

20058103

LM5030

| ITEM |    | PART NUMBER        | DESCRIPTION             | VALUE        |  |

|------|----|--------------------|-------------------------|--------------|--|

| 2    | 1  | C0805C472K5RAC     | Capacitor, CER, KEMET   | 4700p, 50V   |  |

| )    | 2  | C0805C103K5RAC     | Capacitor, CER, KEMET   | 0.01µ, 50V   |  |

| )    | 3  | C4532X7S0G686M     | Capacitor, CER, TDK     | 68µ, 4V      |  |

| )    | 4  | T520D337M006AS4350 | Capacitor, TANT, KEMET  | 330µ, 6.3V   |  |

| 2    | 5  | T520D337M006AS4350 | Capacitor, TANT, KEMET  | 330µ, 6.3V   |  |

| С    | 6  | C4532X7R3A103K     | Capacitor, CER, TDK     | 0.01µ, 1000V |  |

| 2    | 7  | C3216X7R2A104K     | Capacitor, CER, TDK     | 0.1µ, 100V   |  |

| С    | 8  | C4532X7R2A105M     | Capacitor, CER, TDK     | 1µ, 100V     |  |

| С    | 9  | C4532X7R2A105M     | Capacitor, CER, TDK     | 1µ, 100V     |  |

| 0    | 10 | C0805C102K1RAC     | Capacitor, CER, KEMET   | 1000p, 100V  |  |

| С    | 11 | C1206C223K5RAC     | Capacitor, CER, KEMET   | 0.022µ, 50V  |  |

| С    | 12 | C3216X7R1E105M     | Capacitor, CER, TDK     | 1µ, 25V      |  |

| С    | 13 | C3216COG2J221J     | Capacitor, CER, TDK     | 220p, 630V   |  |

| С    | 14 | C3216COG2J221J     | Capacitor, CER, TDK     | 220p, 630V   |  |

| С    | 15 | C1206C104K5RAC     | Capacitor, CER, KEMET   | 0.1µ, 50V    |  |

| С    | 16 | C0805C101J1GAC     | Capacitor, CER, KEMET   | 100p, 100V   |  |

| С    | 17 | C0805C101J1GAC     | Capacitor, CER, KEMET   | 100p, 100V   |  |

| С    | 18 | C3216X7R1H334K     | Capacitor, CER, TDK     | 0.33µ, 50µ   |  |

| D    | 1  | MBRB3030CTL        | Diode, Schottky, ON     |              |  |

| D    | 2  | CMPD2838-NSA       | Diode, Signal, Central  |              |  |

| D    | 3  | CMPD2838-NSA       | Diode, Signal, Central  |              |  |

| D    | 4  | CMPD2838-NSA       | Diode, Signal, Central  |              |  |

| D    | 5  | CMPD2838-NSA       | Diode, Signal, Central  |              |  |

| L    | 1  | MSS6132-103        | Input Choke, Coilcraft  | 10µH, 1.5A   |  |

| L    | 2  | A9785-B            | Output Choke, Coilcraft | 7μΗ          |  |

| R    | 1  | CRCW12061R00F      | Resistor                | 1            |  |

| R    | 2  | CRCW12064990F      | Resistor                | 499          |  |

| R    | 3  | CRCW2512101J       | Resistor                | 100, 1W      |  |

| R    | 4  | CRCW2512101J       | Resistor                | 100, 1W      |  |

| R    | 5  | CRCW12064022F      | Resistor                | 40.2K        |  |

| R    | 6  | CRCW120610R0F      | Resistor                | 10           |  |

| R    | 7  | CRCW120610R0F      | Resistor                | 10           |  |

| R    | 8  | CRCW12061002F      | Resistor                | 10K          |  |

| R    | 9  | CRCW120623R7F      | Resistor                | 23.7         |  |

| R    | 10 | CRCW12062002F      | Resistor                | 20K          |  |

| R    | 11 | CRCW120610R0F      | Resistor                | 10           |  |

| R    | 12 | CRCW12063010F      | Resistor                | 301          |  |

| R    | 13 | CRCW120610R0F      | Resistor                | 10           |  |

| R    | 14 | CRCW12061001F      | Resistor                | 10<br>1K     |  |

| TX   | 1  | A9784-B            | POWER XFR, COILCRAFT    |              |  |

| TX   | 2  | P8208T             | CURRENT XFR, Pulse      | 100:1        |  |

| J1   | 1  | LM5030             | REGULATOR, NATIONAL     |              |  |

| J2   | 2  | MOCD207M           | OPTO-COUPLER, QT        |              |  |

|      |    |                    | OPTOELECTRONICS         |              |  |

| J3   | 3  | LM3411AM5-3.3      | REFERENCE, NATIONAL     |              |  |

|      |    | 651-1727010        | DUAL TERMINALS, MOUSER  | 3 per ASSY   |  |

| Х    | 1  | SUD19N20-90        | FET, N, 200V, SILICONIX |              |  |

| X    | 2  | SUD19N20-90        | FET, N, 200V, SILICONIX |              |  |

LM5030

Notes

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560