# **Protected Quad Power Driver**

### **Features and Benefits**

- 700 mA output current per channel

- Independent overcurrent protection for each driver

- Thermal protection for device and each driver

- Low output-saturation voltage

- Integral output flyback diodes

- TTL and 5 V CMOS-compatible inputs

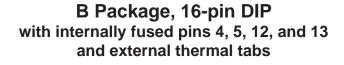

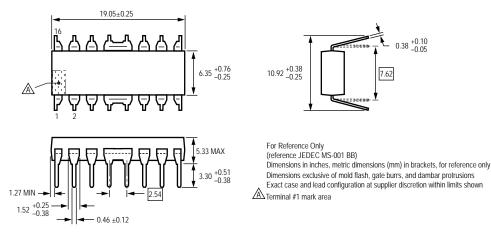

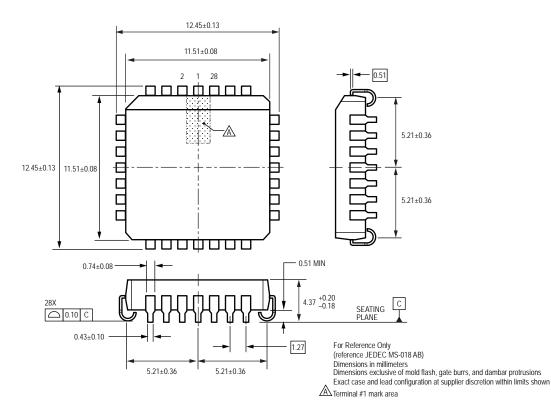

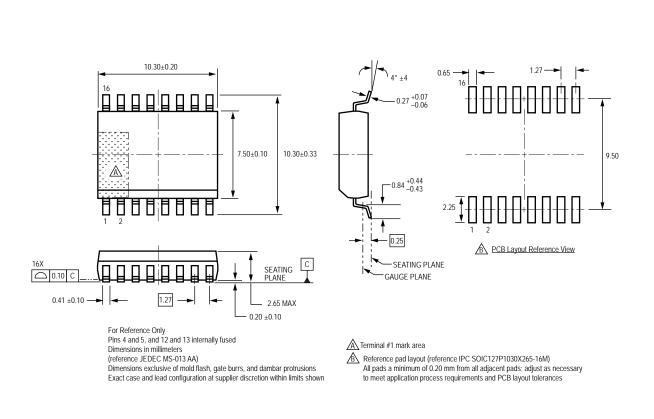

### Packages:

28-pin PLCC

(Package EB)

16-pin DIP with exposed thermal tabs (B package)

16-pin SOICW with internally fused pins (LB package)

Not to scale

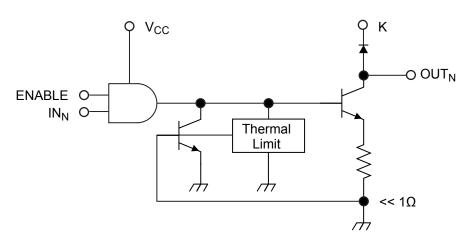

## Description

Providing improved output current limiting, the UDK, UDN, and UDQ2559B, EB, and LB quad power drivers combine AND logic gates and high-current bipolar outputs with complete output protection. Each of the four outputs sink 700 mA in the on state. The outputs have a minimum breakdown voltage (load dump) of 60 V and a sustaining voltage of 40 V. The inputs are compatible with TTL and 5 V CMOS logic systems.

Overcurrent protection for each channel has been designed into these devices and is activated at approximately 1 A. It protects each output from short circuits with supply voltages up to 25 V. When an output current trip point is reached, that output stage is driven linearly resulting in a reduced output current level. If an over-current or short-circuit condition continues, the thermal-limiting circuits will first sense the rise in junction temperature and then the rise in chip temperature, further decreasing the output current. Under worst-case conditions, these devices will tolerate short circuits on all outputs, simultaneously.

These devices can be used to drive various loads including incandescent lamps (without warming or limiting resistors) or inductive loads such as relays, solenoids, or dc stepping motors.

The packages offer fused leads for enhanced thermal dissipation. Package B is a 16-pin power DIP with exposed tabs, EB is a 28-lead power PLCC, and LB is a 16-lead power wide-body SOIC for surface-mount applications. The lead (Pb) free versions have 100% matte tin leadframe plating.

### Functional Block Diagram (1 of 4 Channels)

#### **Selection Guide**

| Part Number    | Pb-free | Package                  | Packing       | Ambient Temperature<br>(°C) |  |

|----------------|---------|--------------------------|---------------|-----------------------------|--|

| UDN2559B-T     | Yes     | 16-pin DIP, exposed tabs | 25 per tube   |                             |  |

| UDN2559EBTR-T  | Yes     | 28-lead PLCC             | 800 per reel  | -20 to 85                   |  |

| UDN2559LBTR-T* | Yes     | 16-lead SOIC             | 1000 per reel |                             |  |

| UDQ2559B-T*    | Yes     | 16-pin DIP, exposed tabs | 25 per tube   | -40 to 85                   |  |

| UDQ2559LBTR-T  | Yes     | 16-lead SOIC             | 1000 per reel | -40 to 85                   |  |

| UDK2559B-T     | Yes     | 16-pin DIP, exposed tabs | 25 per tube   |                             |  |

| UDK2559EBTR*   | _       | 28-lead PLCC             | 800 per reel  |                             |  |

| UDK2559EBTR-T  | Yes     | 28-lead PLCC             | 800 per reel  | -40 to 125                  |  |

| UDK2559LBTR*   | _       | 16-lead SOIC             | 1000 per reel |                             |  |

| UDK2559LBTR-T  | Yes     | 16-lead SOIC             | 1000 per reel |                             |  |

\*Variant is in production but has been determined to be LAST TIME BUY. This classification indicates that the variant is obsolete and notice has been given. Sale of the variant is currently restricted to existing customer applications. The variant should not be purchased for new design applications because of obsolescence in the near future. Samples are no longer available. Status date change November 2, 2009. Deadline for receipt of LAST TIME BUY orders is April 30, 2010.

### **Absolute Maximum Ratings**

| Characteristic                       | Symbol               | Notes                                                                                                                                                | Rating     | Units |

|--------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| Supply Voltage                       | V <sub>CC</sub>      |                                                                                                                                                      | 7          | V     |

| Input Voltage Range                  | $V_{IN}, V_{EN}$     |                                                                                                                                                      | 7          | V     |

| Output Voltage                       | V <sub>OUT</sub>     |                                                                                                                                                      | 60         | V     |

| Overcurrent-Protected Output Voltage | V <sub>OUT(P)</sub>  |                                                                                                                                                      | 25         | V     |

| Output Current                       | I <sub>OUT</sub>     | Outputs are peak current limited at approxi-<br>mately 1.0 A per driver. See Circuit Description<br>and Application section for further information. | 1.0        | A     |

|                                      |                      | Range K                                                                                                                                              | -40 to 125 | °C    |

| Operating Ambient Temperature        | T <sub>A</sub>       | Range N                                                                                                                                              | -20 to 85  | °C    |

|                                      |                      | Range Q                                                                                                                                              | -40 to 85  | °C    |

| Maximum Junction Temperature         | T <sub>J</sub> (max) |                                                                                                                                                      | 150        | °C    |

| Storage Temperature                  | T <sub>stg</sub>     |                                                                                                                                                      | -55 to 150 | °C    |

# **Protected Quad Power Driver**

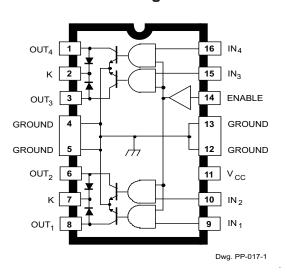

### **Pin-out Diagrams**

Package B

16 IN 4 OUT 4 15 2 IN<sub>3</sub> к 14 ENABLE OUT 3 3 GROUND GROUND 4 13 12 GROUND GROUND 5 h  $v_{\rm cc}$ OUT , 6 11 7 10 IN<sub>2</sub> к IN<sub>1</sub> OUT 1 8 9 Dwg. PP-017-6

Package LB

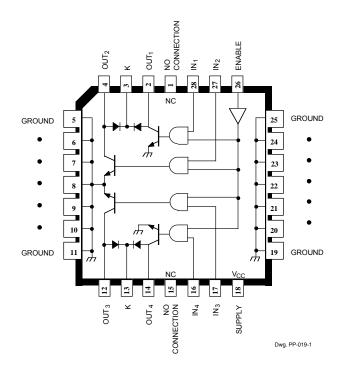

Package EB

Allegro MicroSystems, Inc. 115 Northeast Cutoff

3

# **Protected Quad Power Driver**

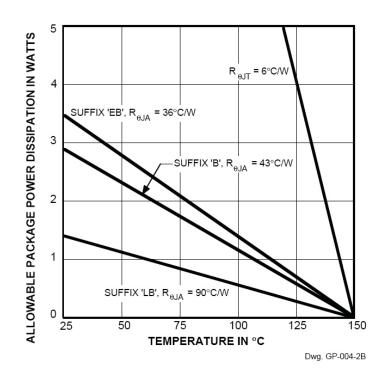

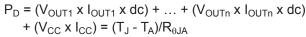

#### **Thermal Characteristics**

| Characteristic             | Symbol          | Test Conditions*                                                          |    | Units |

|----------------------------|-----------------|---------------------------------------------------------------------------|----|-------|

|                            | $R_{\theta JA}$ | Package B, 2-layer PCB with 0.5 in. <sup>2</sup> exposed copper each side |    | °C/W  |

| Package Thermal Resistance |                 | Package EB, 1-layer PCB with copper limited to solder pads                |    | °C/W  |

|                            |                 | Package LB, 1-layer PCB with copper limited to solder pads                | 90 | °C/W  |

\*Additional thermal information available on the Allegro website

# ELECTRICAL CHARACTERISTICS at $T_A = +25$ °C (prefix 'UDN') or over operating temperature range (prefix 'UDK' or 'UDQ'), $V_{CC} = 4.75$ V to 5.25 V

|                             | Symbol                | Test Conditions                                                           | Limits   |      |      |       |

|-----------------------------|-----------------------|---------------------------------------------------------------------------|----------|------|------|-------|

| Characteristic              |                       |                                                                           | Min.     | Тур. | Max. | Units |

| Output Leakage Current      | I <sub>CEX</sub>      | $V_{OUT}$ = 50 V, $V_{IN}$ = 0.8 V, $V_{EN}$ = 2.0 V                      | -        | <1.0 | 100  | μA    |

|                             |                       | V <sub>OUT</sub> = 50 V, V <sub>IN</sub> = 2.0 V, V <sub>EN</sub> = 0.8 V | -        | <1.0 | 100  | μA    |

| Output Sustaining Voltage   | V <sub>OUT(SUS)</sub> | I <sub>OUT</sub> = 100 mA, V <sub>IN</sub> = V <sub>EN</sub> = 0.8 V      | 40       | _    | _    | V     |

| Output Saturation Voltage   | V <sub>OUT(SAT)</sub> | All Devices, I <sub>OUT</sub> = 100 mA                                    | -        | _    | 300  | mV    |

|                             |                       | All Devices, I <sub>OUT</sub> = 400 mA                                    | - 1      | _    | 500  | mV    |

|                             |                       | B or EB package only, I <sub>OUT</sub> = 600 mA                           | -        | _    | 700  | mV    |

| Over-Current Trip           | I <sub>TRIP</sub>     |                                                                           | - 1      | 1.0  | —    | А     |

| Input Voltage               | Logic 1               | V <sub>IN(1)</sub> or V <sub>EN(1)</sub>                                  | 2.0      | _    | —    | V     |

|                             | Logic 0               | V <sub>IN(0)</sub> or V <sub>EN(0)</sub>                                  | - 1      | _    | 0.8  | V     |

| Input Current               | Logic 1               | V <sub>IN(1)</sub> or V <sub>EN(1)</sub> = 2.0 V                          | - 1      | _    | 40   | μA    |

|                             | Logic 0               | V <sub>IN(0)</sub> or V <sub>EN(0)</sub> = 0.8 V                          | - 1      | _    | -10  | μΑ    |

| Total Supply Current*       | I <sub>CC</sub>       | All Outputs ON, $V_{IN} = V_{EN} = 2.0 V$                                 | - 1      | _    | 80   | mA    |

|                             |                       | All Outputs OFF                                                           | -        | _    | 5.0  | mA    |

| Clamp Diode Forward Voltage | V <sub>F</sub>        | I <sub>F</sub> = 1.0 A                                                    | -        | _    | 1.7  | V     |

|                             |                       | I <sub>F</sub> = 1.5 A                                                    | -        | —    | 2.1  | V     |

| Clamp Diode Leakage Current | I <sub>R</sub>        | $V_{R} = 50 V, D_{1} + D_{2} \text{ or } D_{3} + D_{4}$                   | - 1      | —    | 50   | μA    |

| Turn-On Delay               | t <sub>PHL</sub>      | I <sub>OUT</sub> = 500 mA                                                 | - 1      | _    | 20   | μs    |

|                             | t <sub>PLH</sub>      | I <sub>OUT</sub> = 500 mA                                                 | -        | _    | 20   | μs    |

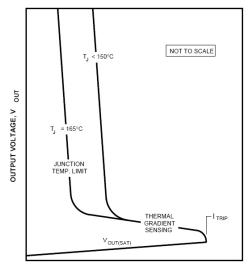

| Thermal Limit               | TJ                    |                                                                           | <u> </u> | 165  |      | °C    |

Typical Data is for design information only.

Negative current is defined as coming out of (sourcing) the specified terminal.

As used here, -100 is defined as greater than +10 (absolute magnitude convention) and the minimum is implicitly zero.

\* All inputs simultaneously, all other tests are performed with each input tested separately.

# TYPICAL OUTPUT CHARACTERISTIC

OUTPUT CURRENT, I OUT

Dwg. GP-013

# **TYPICAL OUTPUT BEHAVIOR**

### **CIRCUIT DESCRIPTION AND APPLICATION**

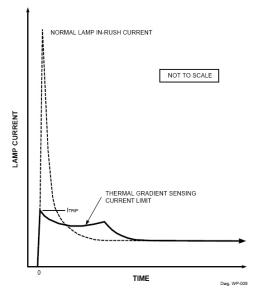

### INCANDESCENT LAMP DRIVER

High incandescent lamp turn-ON/in-rush currents can contribute to poor lamp reliability and destroy semiconductor lamp drivers. Warming or currentlimiting resistors protect both driver and lamp but use significant power either when the lamp is OFF or when the lamp is ON, respectively. Lamps with steady-state current ratings up to 700 mA can be driven by these devices without the need for warming (parallel) or current-limiting (series) resistors.

When an incandescent lamp is initially turned ON, the cold filament is at minimum resistance and would normally allow a 10x to 12x in-rush current. With these drivers, during turn-ON, the high in-rush current is sensed by the internal low-value sense resistor. Drive current to the output stage is then diverted by the shunting transistor, and the load current is momentarily limited to approximately 1.0 A. During this short transition period, the output current is reduced to a value dependent on supply voltage and filament resistance. During lamp warmup, the filament resistance increases to its maximum value, the output stage goes into saturation and applies maximum rated voltage to the lamp.

### INDUCTIVE LOAD DRIVER

Bifilar (unipolar) stepper motors, relays, or solenoids can be driven directly. The internal flyback diodes prevent damage to the output transistors by suppressing the high-voltage spikes that occur when turning OFF an inductive load.

For rapid current decay (fast turn-OFF speeds), the use of Zener diodes will raise the flyback voltage and inprove performance. However, the peak voltage must not exceed the specified minimum sustaining voltage ( $V_{SUPPLY} + V_Z + V_F V_{OUT(SUS)}$ ).

### **FAULT CONDITIONS**

In the event of a shorted load, the load current will attempt to increase. As described above, the drive current to the affected output stage is reduced, causing the output stage to go linear, limiting the peak output current to approximately 1 A. As the power dissipation of that output stage increases, a thermal gradient sensing circuit will become operational, further decreasing the drive current to the affected output stage and reducing the output current to a value dependent on supply voltage and load resistance.

Continuous or multiple overload conditions causing the chip temperature to reach approximately 165°C will result in an additional reduction in output current to maintain a safe level.

If the fault condition is corrected, the output stage will return to its normal saturated condition.

Downloaded from Elcodis.com electronic components distributor

EB Package, 28-pin PLCC with internally fused pins 5 through 11 and 19 through 25

LB Package, 16-pin SOICW with internally fused pins 4 and 5, and 12 and 13

Copyright ©1995-2009, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

<u>Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.</u>

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com