# MITSUBISHI LSIs

# M5L8257P-5

# MITSUBISHI(MICMPTR/MIPRC)

PROGRAMMABLE DMA CONTROLLER

#### **DESCRIPTION**

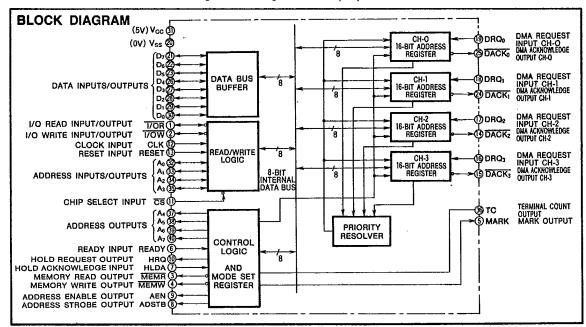

The M5L8257P-5 is a programmable 4-channel direct memory access (DMA) controller. It is produced using the N-channel silicon-gate ED-MOS process and is specifically designed to simplify data transfer at high speeds for microcomputer systems.

The LSI operates on a single 5V power supply.

#### **FEATURES**

- Single 5V supply voltage

- TTL compatible interface

- Priority DMA request logic

- Channel-masking function

- Terminal count and Modulo 128 outputs

- 4-channel DMA controller

- Compatible with MELPS85 devices

#### **APPLICATION**

DMA control of peripheral equipment such as floppy disks and CRT terminals that require high-speed data transfer.

#### **FUNCTION**

The M5L8257P-5 controller is used in combination with the M5L8212P 8-bit input/output port in 8-bit microcomputer systems. It consists of a channel section to acknowledge DMA requests, control logic to exchange commands and data with the CPU, read/write logic, and registers to hold transfer addresses and count the number of bytes to be transferred. When a DMA request is made to an unmasked channel from the peripherals after setting of the transfer mode, transferstart address and the number of transferred bytes for the registers, the M5L8257P-5 issues a priority request for the use of the bus to the CPU. On receiving an HLDA signal

from the CPU, it sends a DMA acknowledge signal to the channel with the highest priority, starting DMA operation. During DMA operation, the contents of the high-order 8 bits of the transfer memory address are transmitted to the M5L8212P address-latch device through pins  $D_0 \sim D_7$ . The contents of the low-order 8 bits are transmitted through pins  $A_0 \sim A_7$ . After address transmission, DMA transfer can be started by dispatching read and write signals to the memories and peripherals.

T-52-33-19

## MITSUBISHI (MICMPTR/MIPRC)

## PROGRAMMABLE DMA CONTROLLER

#### **OPERATION**

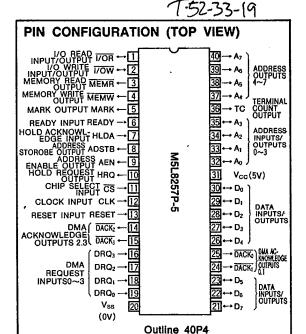

# I/O Read Input/Output (I/OR)

When the M5L8257P-5 is in slave-mode operation, this threestate, bidirectional pin serves for inputting and reads the upper/lower bytes of the 8-bit status register or 16-bit DMA address register and the high/low order bytes of the terminal counter.

In the master mode, the pin gives control output and is used to obtain data from a peripheral equipment during the DMA write cycle.

#### I/O Write Input/Output (I/OW)

This pin is also of the three-state bidirectional type. When the M5L8257P-5 is in slave-mode operation, it serves for inputting and loads the contents of the data bus on the 8-bit status register and the upper/lower bytes of the 16-bit terminal counter or 16-bit DMA address register.

#### Memory Read Output (MEMR)

This active-low three-state output is used to read data from the addressed memory location during DMA read cycles.

#### Memory Write Output (MEMW)

This active-low three-state output is used to write data into the addressed memory location during DMA write cycles.

#### Mark Output (MARK)

This signal notifies that the DMA transfer cycle for each channel is the 128th cycle since the previous MARK output.

Ready Input (READY)

This asynchronous input is used to extend the memory read and write cycles in the M5L8257P-5 with wait states if the selected memory requires longer access time.

#### Hold Acknowledge input (HLDA)

This input from the CPU indicates that the system bus is controlled by the M5L8257P-5.

#### Address Strobe Output (ADSTB)

This output strobes the most significant byte of the memory address into the M5L8212P (8-bit input/output port) through the data bus.

#### Address Enable Output (AEN)

This signal is used to disable the system data bus and system control bus by means of the bus enable pin on the system controller. It may also be used to inhibit non-DMA devices from responding during DMA cycles.

#### Hold Request Output (HRQ)

This output requests control of the system bus. HRQ will normally be applied to the HOLD input on the CPU.

#### Chip-Select Input (CS)

This pin is active on a low-level. It enable the  $\overline{I/OR}$  and  $\overline{I/OW}$  signals output from the CPU, when the M5L8257P-5 is in slave-mode operation.

In the master mode, it is disabled to prevent the chip from selecting itself while performing the DMA function.

#### Clock Input (CLK)

This pin generates internal timing for the M5L8257P-5 and is connected to the  $\phi$  (TTL) output of the system clock.

#### Reset Input (RESET)

This asynchronous input clears some registers and control lines inside the M5L8257P-5.

#### DMA Acknowledge Outputs (DACK0~DACK3)

These active-low outputs indicate that the peripheral equipment connected to the channel in question can execute the DMA cycle.

#### DMA Request Inputs (DRQ0~DRQ3)

These independent, asynchronous channel-request inputs are used to secure use of the DMA cycle for the peripherals. **Data-Bus Buffer**

# This three-state, bidirectional, 8-bit buffer interfaces the M5L8257P-5 to the CPU for data transfer. During a DMA cycle the upper 8 bits of the DMA address are output to the M5L8212P latch device through this buffer.

#### Address Inputs/Outputs (A<sub>0</sub>~A<sub>3</sub>)

The four bits of these input/output pins are bidirectional. When the M5L8257P-5 is in slave-mode operation, serve to input and address the internal registers. In the case of master operation, they output the low-order 4 bits of the 16-bit memory address.

#### Terminal Count Output (TC)

When the terminal count registers became (3FFF)H, terminal count signal is out. And this signal notifies that the present DMA cycle is the last cycle for this data block.

#### Address Inputs/Outputs (A<sub>4</sub>~A<sub>7</sub>)

These four address lines are three-state outputs which constitute bits 4 through 7 of the memory address generated by the M5L8257P-5 during all DMA cycles.

MITSUBISHI LSIs

# M5L8257P-5

# MITSUBISHI (MICMPTR/MIPRC)

#### PROGRAMMABLE DMA CONTROLLER

Register Initialization

Two 16-bit registers are provided for each of the 4 channels. **DMA Address register**

15

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

DMA TRANSFER STARTING ADDRESS

#### Terminal count register

DMA MODE

NUMBER OF TRANSFERRED BYTES-1

The DMA transfer starting address, number of transferred bytes, and DMA mode are written for each channel in 2 steps using the 8-bit data bus. The lower-order and upper-order bytes are automatically indicated by the first-last flip-flop for the writing and reading in 2 continuous steps.

The DMA mode (read, write, or verify) is indicated by the upper 2 bits of the terminal count register. The read mode refers to the operation of peripheral devices reading data out of memory. The write mode refers to data from peripheral devices being written into memory. The verify mode sends neither the read nor the write signals and performs a date check at the peripheral device.

In addition to the above-mentioned registers, there is a mode set register and a status register.

#### Mode set register (write only)

| 7  |     |    |    |     |     | •   | 0   |

|----|-----|----|----|-----|-----|-----|-----|

| AL | TCS | EW | RP | EN3 | EN2 | EN1 | EN0 |

ADDED FUNCTION SETTING BITS

CHANNEL ENABLE BITS

#### Status Register (read only)

| 7  |   |   |    |     |     |     | C   | ) |

|----|---|---|----|-----|-----|-----|-----|---|

| ó, | 0 | 0 | UP | TC3 | TC2 | TC1 | TC0 | 1 |

The upper-order 4 bits of the mode set register are used to select the added function, as described in 5-66. The lower-order 4 bits are mask bits for each channel. When set to 1, DMA requests are allowed. When the reset signal-is input, all bits of the mode set and status registers are reset and DMA is inhibited for all channels. Therefore, to execute DMA operations, registers must first be initialized. An example of such an initialization is shown below.

T-52-33-19

MODESET:

MVI A, ADDL

OUT 00#: Channel 0 lower-order address

MVI A, ADDH

OUT 00#: Channel 0 upper-order address

MVI A, TCL

OUT 01#: Channel 0 terminal count lower-order

MVI A, TCH

OUT 01#: Channel 0 terminal count upper-order

MVI A, XX

OUT 08#: Mode set resister

As can be seen from the above example, until the contents of the address register and terminal count register become valid, the enable bit of the mode set register must not be set. This prevents memory contents from being destroyed by improper DRQ signals from peripheral devices.

#### **DMA OPERATION DESCRIPTION**

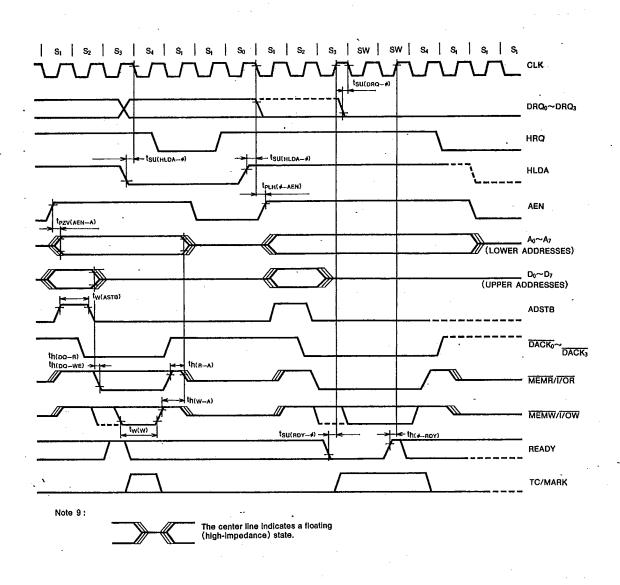

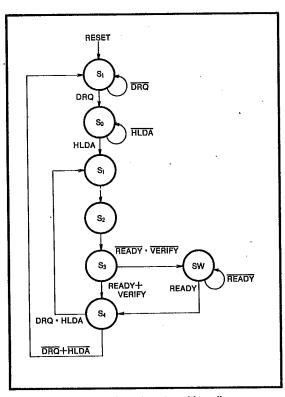

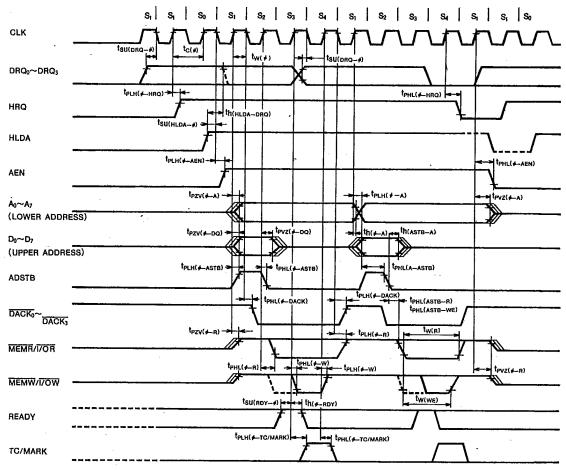

When a DMA request signal is received at the DRQ pin from a peripheral device after register initialization for a channel that is not masked, the M5L8257P-5 outputs a hold request signal to the CPU to begin DMA operation ( $S_1$ ).

The CPU, upon receipt of the HRQ signal, outputs the HLDA signal which reserves capture of the bus after it has executed the present instruction to place this system in the hold state.

When the M5L8257P-5 receives the HLDA signal, an internal priority determining circuit selects the channel with the highest priority for the beginning of data transfer ( $S_0$ ).

Upon the next  $S_1$  state, the address signal is sent. The lower-order 8 bits and upper-order 8 bits are sent by means of the  $A_0 \sim A_7$  and  $D_0 \sim D_7$  pins respectively, latched into the M5L8212P and output at pins  $A_8 \sim A_{15}$ . Simultaneous with this, the AEN signal is output to prohibit the selection of a device not capable of DMA.

In the  $S_2$  state, the read, extended write, and DACK signals are output and data transferred from memory or a peripheral device appears on the data bus.

In the  $S_3$  state, the write signal required to write data from the bus is output. At this time if the remaining number of bytes to be transferred from the presently selected channel has reached 0, the terminal count (TC) signal is output. Simultaneously with this, after each 128-byte data transfer a mark signal is output as required. In addition, in this state the READY pin is sampled and, if low-level, the wait state ( $S_W$ ) is entered. This is used to perform DMA with slow access memory devices. In the verify mode, READY input is ignored.

# MITSUBISHI(MICMPTR/MIPRC)

#### PROGRAMMABLE DMA CONTROLLER

T-52-33-19

In the S4 state, the DRQ and HLDA pins are sampled at the end of a transferred byte as the address signal, control signats, and  $\overline{\text{DACK}}$  signal are held to determine if transfer will continue.

As described above, transfer of 1 byte requires a minimum of 4 states for execution. For example, If a 2MHz clock input is used, the maximum transfer rate is 500k byte/s.

Fig. 1 DMA Operation state transition diagram

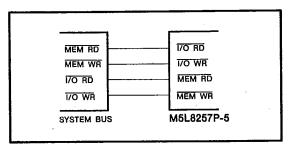

#### **MEMORY MAPPED I/O**

When using memory mapped i/O, it is neccessary to change the connections for the control signals.

2 Memory mapped I/O

Also, the read mode and write mode specifications for setting the mode of the terminal count are reversed.

#### MITSUBISHI LSIs

#### M5L8257P-5

T-52-33-19

PROGRAMMABLE DMA CONTROLLER

MITSUBISHI (MICMPTR/MIPRC)

#### INTERNAL REGISTERS OF THE M5L8257P-5

Upper Lower D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> A7 A<sub>6</sub> DMA address channel-0 Rd Wr C13 C12 C11 C10 C9 C8 C7 C6 C5 C4 C3 C2 C1 C0 terminal count A15 A14 A13 A12 A11 A10 A9 A<sub>8</sub> A7 A6 A<sub>5</sub> A4 A3 A2 A1 A0 DMA address channel-1 C7 C<sub>6</sub> C<sub>5</sub> C4 C<sub>3</sub> C2 C1 C0 Rd Wr C<sub>13</sub> C12 C11 C10 C<sub>9</sub> C8 terminal count A15 A14 A13 A12 A11 A<sub>10</sub> Αg  $A_{R}$ A<sub>7</sub> A<sub>6</sub> A5 A4 A3 A2 A1 A0 DMA address channel-2 Rd Wr C13 C12 C11 C10 C7 C<sub>6</sub> C<sub>4</sub> C<sub>3</sub> C<sub>9</sub> C<sub>8</sub> C<sub>5</sub> terminal count A15 A14 A13 A12 A11 A10 A9 Αa  $A_7$ A<sub>6</sub> A<sub>5</sub> A4 A<sub>3</sub> A<sub>2</sub> A<sub>1</sub> DMA address channel-3 Wr C13 C12 C11 C10 C9 C<sub>8</sub> C<sub>7</sub> C<sub>6</sub> C<sub>5</sub> C4 C3 C2 C1 C0 terminal count AL TOS EW RP EN3 EN2 EN1 EN0 Mode setting (for write only) 0 0 0 UP TG3 TG2 TG1 TG0 Status (for read only)

Address of the memories for which DMA will be carried out from now on. In initialization, DMA start addresses must be written. Terminal counts-in this IC (the number of remaining transfer bytes minus 1) The address is decremented for each DMA transfer of one byte, and when the transfer is finished, becomes (3 FFF) H. If additional DRQ signals are input, the address continues to be decremented. C0~C13

Rd. Wr Used for DMA-mode setting by the following convention:

| Rd | Wr  | Mode to be set |

|----|-----|----------------|

| 0  | . 0 | DMA verify     |

| 0  | 1   | DMA write      |

| 1  | 0   | DMA read       |

| 1  | 1   | Prohibition    |

|    |     |                |

: Automatic load mode. When this bit has been set, contents of the channel 3 register are written, as are on the channel 2 register when channel 2 DMA transfer comes to an end. This mode allows quick, automatic chaining operations without intervention of the software.

: Extended write signal mode. When this bit has been set, write signals can be transmitted in advance to memories and peripheral equip-

ment requiring long access time.

Terminal count stop. When a DMA transfer process is complete, with terminal-count output, the channel-enable mask of that channel is re-TCS

set, prohibiting subsequent DMA cycles.

Rotating priority mode. The setting of this mode allows the priority order to be rotated by each byte transfer.

The setting priority is fixed with the channel 0 as highest, followed by channel 1, 2 and 3 in descending order.

| Channel used for the present da  | ta transfer | CH-0 | CH-1 | CH-2 | CH-3 |

|----------------------------------|-------------|------|------|------|------|

|                                  | 1           | CH-1 | CH-2 | CH-3 | CH-0 |

| Delevite that fee the sent and a | 2           | CH-2 | CH-3 | CH-0 | CH-1 |

| Priority list for the next cycle | 3           | CH-3 | CH-0 | CH-1 | CH-2 |

|                                  | 4           | CH-0 | CH-1 | CH-2 | CH-3 |

EN0~EN3: Channel-enable bit. This mask prohibits or allows the DMA request. When the reset signal is applied, all channels are disabled.

Update flag. This is set when register contents are transferred in an automatic load mode from channel 3 to channel 2. Terminal-count status flags. At the time of terminal-count output, the flag corresponding to the channel is set: TC0 TC3

The flag is, set by reading the status register, annd is unaffected by the TCS bits.

ΑL

EW

RP

MITSUBISHI (MICMPTR/MIPRC)

MITSUBISHI LŞİs

# M5L8257P-5

# T-52-33-19

# PROGRAMMABLE DMA CONTROLLER

# REGISTER ADDRESS

|    | Address        | s input |     | F/L           | Register                            |

|----|----------------|---------|-----|---------------|-------------------------------------|

| Aз | A <sub>2</sub> | At      | Ao  | F/L           | 110910101                           |

| 0  | 0              | 0       | 0   | 0             | channel 0 DMA address Low-order     |

| 0  | 0              | 0       | 0   | 1 .           | channel 0 DMA address High-order    |

| 0  | 0              | 0       | 1   | 0             | channel 0 terminal count Low-order  |

| 0  | 0              | 0       | 1   | 1             | channel 0 terminal count High-order |

| 0  | 0              | 1       | 0   | 0             | channel i DMA address Low-order     |

| 0  | 0              | 1       | 0   | 1             | channel 1 DMA address High-order    |

| 0  | 0              | 1       | 1   | 0             | channel 1 terminal count Low-order  |

| 0  | 0              | 1       | 1   | 1             | channel 1 terminal count High-order |

| 0  | 1              | 0       | 0   | 0             | channel 2 DMA address Low-order     |

| 0  | 1              | 0       | 0   | 1             | channel 2 DMA address High-order    |

| 0  | 1              | 0       | 1   | 0             | channel 2 terminal count Low-order  |

| 0  | 1              | 0       | . 1 | 1             | channel 2 terminal count High-order |

| Ò  | 1              | 1       | 0   | 0             | channel 3 DMA address Low-order     |

| 0  | 1              | 1       | 0   | 1             | channel 3 DMA address High-order    |

| 0  | 1              | 1       | 1   | 0             | channel 3 terminal count Low-order  |

| 0  | 1              | 1       | 1   | 1             | channel 3 terminal count High-order |

| 1  | 0              | 0       | 0   | Γ-            | Mode Setting (for Write Only)       |

| 1  | 0              | 0       | 0   | † <del></del> | Status (for Read Only)              |

F/L: First/last flip-flop. This is toggled when register-write or read operations for each channel are finished, and specifies whether the next write or read operation is to be for the upper bytes or the lower bytes. This means that write and read operations for each register must be carried out for a set of lower and higher bytes.

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                            | Conditions                      | Ratings | Unit |

|--------|--------------------------------------|---------------------------------|---------|------|

| Vcc    | Power-supply voltage                 |                                 | -0.5~7  | V    |

| V.     | Input voltage                        | With respect to V <sub>SS</sub> | −0.5~7  |      |

| Vo     | Output voltage                       |                                 | -0.5~7  | V    |

| Pd     | Power dissipation (max.)             | Ta=25°C                         | 1000    | mW   |

| Topr   | Operating free-air temperature range |                                 | -20~75  | င    |

| Teta   | Storage temperature range            |                                 | -65~150 | ,c   |

# RECOMMENDED OPERATING CONDITIONS (Ta=-20~75°C, unless otherwise noted)

|        |                            |      | Unit |       |       |

|--------|----------------------------|------|------|-------|-------|

| Symbol | Parameter                  | Min  | Nom  | Max   | Oiiit |

| Vcc    | Power-supply voltage       | 4.75 | 5    | 5. 25 | V     |

|        | Power-supply voltage (GND) |      | 0    |       | V     |

T-52-33-19

# PROGRAMMABLE DMA CONTROLLER

#### ELECTRICAL CHARACTERISTICS (Ta=-20~75°C, Vcc=5 V±5%, unless otherwise noted)

| Symbol           | Parameter                                    | Test conditions                                               |      |     |                             |      |

|------------------|----------------------------------------------|---------------------------------------------------------------|------|-----|-----------------------------|------|

| ayınıbu          | Fatanete                                     | Test conditions                                               | Min  | Тур | Max<br>Vcc<br>0, 8<br>0, 45 | Unit |

| VIH              | High-level Input voltage                     | -                                                             | 2.0  |     | Vcc                         | V    |

| V <sub>IL</sub>  | Low-level input voltage                      |                                                               | -0.5 |     | 0.8                         | V    |

| VoL              | Low-level output voltage                     | I <sub>OL</sub> =1.6mA                                        |      |     | 0.45                        | ٧    |

| V <sub>OH1</sub> | High-level output voltage for AB, DB and AEN | I <sub>OH</sub> =-150μA                                       | 2, 4 |     |                             | ٧    |

| V <sub>OH2</sub> | High-level output voltage for HRQ            | 1 - 90 4                                                      | 3.3  |     |                             | V    |

| V <sub>OH3</sub> | High-level output voltage for others         | l <sub>он</sub> =-80µА                                        | 2.4  |     |                             | v    |

| loo              | Supply current from V <sub>CC</sub>          |                                                               |      |     | 120                         | mA   |

| l <sub>t</sub>   | Input current                                | V <sub>I</sub> =0V, V <sub>CC</sub>                           | -10  |     | 10                          | μА   |

| loz              | Off-state output current                     | Vo=0V~Vcc                                                     | -10  |     | 10                          | μА   |

| Çı               | Input terminal capacitance                   | Ta=25°C, Vcc=Vss                                              | Ï.   |     | 10                          | рF   |

| Ciro             | Input/output terminal capacitance            | Pins other than that under measurement are set to 0V, fo=1MHz |      |     | 20                          | рF   |

MITSUBISHI (MICMPTR/MIPRC)

## TIMING REQUIREMENTS ( $\tau_a = -20 \sim 75 \text{C}$ , $V_{co} = 5 \text{V} \pm 5 \%$ , $V_{ss} = 0 \text{V}$ , unless otherwise noted)

| Symbol                                        | Parameter                              | . Test conditions | i    | Limits | ٠                                     |                   |

|-----------------------------------------------|----------------------------------------|-------------------|------|--------|---------------------------------------|-------------------|

| Symbol                                        | Farameter                              | lest conditions   | Min  | Тур    | 20<br>20<br>4<br>0.8t <sub>G(f)</sub> | Unit              |

| t <sub>w(R)</sub>                             | Read pulse width                       |                   | 250  |        |                                       | ns                |

| t <sub>su</sub> (AR)<br>t <sub>su</sub> (CSR) | Address or CS setup time before read   |                   | 0    |        |                                       | ns                |

| կլ(R−A)<br>կլ(R−CS)                           | Address or CS hold time after read     |                   | 0    |        |                                       | ns                |

| tw(w)                                         | White pulse width                      |                   | 200  |        |                                       | ns                |

| t <sub>su(A</sub> —w)                         | Address setup time before write        |                   | 20   |        | T                                     | ns                |

| th(w-A)                                       | Address hold time after write          |                   | 0    |        | 1                                     | ns                |

| t <sub>su(DQ-w)</sub>                         | Data setup time before write           |                   | 200  |        |                                       | ns                |

| th(w-pa)                                      | Data hold time after write             |                   | 0 -  |        |                                       | ns                |

| t <sub>W(RST)</sub>                           | Reset pulse width                      |                   | 300  |        |                                       | ns                |

| tsu(vcc-RST)                                  | Supply voltage setup time before reset |                   | 500  |        |                                       | ns                |

| tr                                            | Input signal rise time                 |                   |      |        | 20                                    | пз                |

| tş                                            | Input signal fall time                 |                   |      |        | 20                                    | пѕ                |

| tsu(AST-W)                                    | Reset setup time before write          |                   | 2    |        |                                       | t <sub>G(≠)</sub> |

| t <sub>C</sub> (≠)                            | Clock cycle time                       |                   | 0.32 |        | 4                                     | μs                |

| t <sub>w(≠)</sub>                             | Clock pulse width high-level           |                   | 80   |        | 0.8t <sub>C(#)</sub>                  | ns                |

| tsu(DRO-1)                                    | DRQ setup time before clock            |                   | 70   |        |                                       | กร                |

| h(HLDA-DRQ)                                   | DRQ hold time after HLDA               |                   | 0    |        |                                       | ns                |

| SU(HLDA#)                                     | HLDA setup time before clock           |                   | 100  |        |                                       | ns                |

| t <sub>SU(RDY</sub> - f)                      | Ready setup time before clock          |                   | 30   |        | -                                     | กร                |

| th(≠-80Y)                                     | Ready hold time after clock            |                   | - 20 |        |                                       | ns                |

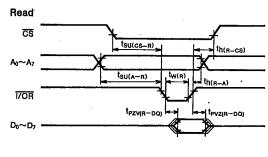

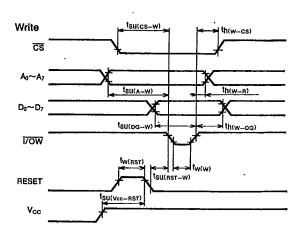

# SLAVE MODE SWITCHING CHARACTERISTICS ( $\tau_a = -20 \sim 75 \, \text{C}$ , $v_{cc} = 5 \, \text{V} \pm 5 \, \text{\%}$ , $v_{ss} = 0 \, \text{V}$ , unless otherwise noted)

| Symbol                  | Parameter                           | Test conditions       |     | Limits |     | 14-16          |

|-------------------------|-------------------------------------|-----------------------|-----|--------|-----|----------------|

|                         | 1 31 3110101                        | Teat Conditions       | Min | Тур    | Max | Unit           |

| t <sub>PZV(R-00)</sub>  | Output data enable time after read  | 0 -150-5              | 0   |        | 200 | n <del>s</del> |

| t <sub>PVZ</sub> (R-DQ) | Output data disable time after read | C <sub>L</sub> =150pF | 20  |        | 100 | ns             |

# MITSUBISHI(MICMPTR/MIPRC)

T-52-33-19

# PROGRAMMABLE DMA CONTROLLER

# DMA MODE SWITCHING CHARACTERISTICS ( $\tau_a = -20 \sim 75^{\circ}$ C, $V_{cc} = 5V \pm 5\%$ , $V_{ss} = 0V$ , unless otherwise noted).

| 01                                             | Parameter                                                               | Test conditions                                                                                                                                  |                                               | Limits                                  |          | Unit |

|------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|----------|------|

| Symbol                                         | Parameter                                                               | Total containent                                                                                                                                 | Min                                           | Тур                                     | Max      |      |

| PHL(#-HRQ)                                     | Propagation time from clock to HRQ (Note1)                              |                                                                                                                                                  |                                               |                                         | 160      | ns   |

|                                                | Propagation time from clock to HRQ (Note3)                              |                                                                                                                                                  |                                               |                                         | 250      | ns   |

|                                                | Propagation time from clock to AEN (Note1)                              |                                                                                                                                                  |                                               |                                         | 300      | ns   |

|                                                | Propagation time from clock to AEN (Note1)                              | ]                                                                                                                                                |                                               | <u> </u>                                | 200      | ns   |

|                                                | Propagation time from AEN to address active (Note4)                     |                                                                                                                                                  | 20                                            |                                         |          | ns   |

|                                                | Propagation time from clock to address active (Note2)                   |                                                                                                                                                  |                                               |                                         | 250      | ns   |

|                                                | Propagation time from clock to address floating (Note2)                 | 1                                                                                                                                                |                                               |                                         | 150      | ns   |

|                                                | Address setup time after clock (Note2)                                  |                                                                                                                                                  |                                               |                                         | 250      | ns   |

|                                                | Address hold time after clock (Note2)                                   |                                                                                                                                                  | <sup>t</sup> рін( + —<br>A) —50               |                                         |          | ns   |

| h(R-A)                                         | Address hold time after read (Note4)                                    | 1                                                                                                                                                | 60                                            |                                         |          | ns   |

| h(w-A)                                         | Address hold time after write (Note4)                                   | 1                                                                                                                                                | 300                                           |                                         |          | ns   |

| PZV( + - DQ)                                   | Propagation time from clock to data active                              |                                                                                                                                                  |                                               |                                         | 300      | ns   |

| tpvz( +pq)                                     | Propagation time from clock to data floating (Note2)                    |                                                                                                                                                  | <sup>†</sup> РНС( # —<br>ASTB) +20            |                                         | 170      | กร   |

| PHL(A-ASTB)                                    | Propagation time from address to address strobe (Note2)                 |                                                                                                                                                  | 100                                           |                                         |          | ns   |

| h(ASTB-A)                                      | Propagation time from address strobe to address hold (Note4)            | 1                                                                                                                                                | 50                                            |                                         |          | ns   |

| PLH(#-ASTB)                                    | Propagation time from clock to address strobe (Note1)                   | <b>1</b> ·                                                                                                                                       |                                               |                                         | 200      | ns   |

| PHL(#-ASTB)                                    | Propagation time from clock to address strobe (Note1)                   | 1                                                                                                                                                |                                               |                                         | 140      |      |

| W(ASTB)                                        | Address strobe pulse width (Note4)                                      |                                                                                                                                                  | t <sub>O(≠)</sub><br>—100                     |                                         |          | пѕ   |

| t <sub>PHL(AS-R)</sub>                         | Propagation time from address strobe to read or extended write (Note4)  |                                                                                                                                                  | 70                                            |                                         |          | ns   |

| th(pq—H)<br>th(pq—WE)                          | Read or extended write hold time after data (Note4)                     |                                                                                                                                                  | 20                                            |                                         |          | ns   |

| TPLH(#-DACK) TPHL(#-TC/MARK) TPLH(#-TC/MARK)   | Propagation time from clock to DACK or TC/MARK (Note1, 5)               |                                                                                                                                                  |                                               |                                         | 250      | ns   |

| tpHL(#-R)<br>tpHL(#-W)<br>tpHL(#-WE)           | Propagation time from clock to read, write or extended write (Note2, 6) |                                                                                                                                                  |                                               |                                         | 200      | ns   |

| t <sub>PLH(≠—R)</sub><br>t <sub>PLH(≠—W)</sub> | Propagation time from clock to read or write<br>(Note2, 7)              |                                                                                                                                                  |                                               |                                         | 200 -    | ns   |

| tpzv( + -n)<br>tpzv( + -w)                     | Propagation time from clock to read active or write active (Note2)      |                                                                                                                                                  |                                               |                                         | 300      | пз   |

| tpvz(≠-8)<br>tpvz(≠-w)                         | Propagation time from clock to read floating or write floating (Note2)  |                                                                                                                                                  |                                               |                                         | 150      | ns   |

| t <sub>W(R)</sub>                              | Read pulse width (Note4)                                                |                                                                                                                                                  | 2t <sub>C(#)</sub> +<br>t <sub>W(#)</sub> -50 |                                         |          | ns   |

| t <sub>w(w)</sub>                              | Write pulse width (Note4)                                               |                                                                                                                                                  | t <sub>G(≠)</sub><br>—50                      |                                         |          | ns   |

| t <sub>W(WE)</sub>                             | Extended write pulse width (Note4)                                      |                                                                                                                                                  | 2t <sub>C(≠)</sub><br>—50                     |                                         |          | ns   |

| 3 : Los<br>Vos                                 | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                   | t <sub>PHL(∮</sub> -w)<50ns, Δt <sub>p</sub><br>t <sub>PLH(∮</sub> -w)<50ns<br>n<br>0.45~2.<br>ime 20ns<br>me 20ns<br>input V <sub>IH</sub> =2V, | HL(∮-WE)<                                     | (# — TC/M.<br>50ns<br>2.4 ==<br>0.45 == | 2<br>0.8 | 0.8  |

MITSUBISHI(MICMPTR/MIPRC)

# M5L8257P-5

T-52-33-19

PROGRAMMABLE DMA CONTROLLER

# **TIMING DIAGRAMS**

**DMA Mode**

## Slave Mode

MITSUBISHI(MICMPTR/MIPRC)

T-52-33-19

PROGRAMMABLE DMA CONTROLLER