# **SARA Chipset** Technical Manual

TranSwitch Corporation 8 Progress Drive Shelton, CT 06484

Tel: (203) 929-8810 Fax: (203) 926-9453 E-Mail: mktg@txc.com Web: http://www.transwitch.com

SARA-S/R Document Number: TXC-95000-TM

Part Numbers: TXC-05501/05601 Edition 6, April 1996

# **SARA Chipset** Technical Manual

#### Notice

This Technical Manual describes current SARA chipset devices, which are now in production.

Please refer to the SARA Chipset Deviation List in Appendix H for the list of differences, as of the publication date of this Manual, between the actual performance of identified SARA chips and the specified functional performance in this Technical Manual. Please contact the TranSwitch Applications Engineering Department for current information.

Edition 6

## SARA Chipset Technical Manual

**Edition 6**

Issued: April 1996.

TRANSWITCH PROVIDES THIS DOCUMENT AS IS, WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

TranSwitch may make improvements and changes to the product or products described in this document at any time without notice. TranSwitch assumes no responsibility for the use of the product(s) or this document except as expressly set forth in an applicable TranSwitch contract. This document may contain technical inaccuracies or typographical errors. Changes may be made to the information contained herein and incorporated from time to time in new editions of this document.

TranSwitch accepts no liability for TranSwitch applications assistance, customer product design, software performance, or infringements of patents or trademarks described herein. Nor does TranSwitch warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TranSwitch covering or relating to any combination, machine or process in which such semiconductor products or services might be or are used.

No part of this document may be stored in a retrieval system, transmitted or reproduced in any way, including, but not limited to, photocopy, photograph, magnetic, or other record, without the prior written permission of TranSwitch.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 52.227-7013.

TranSwitch Corporation 8 Progress Drive Shelton, CT 06484

Copyright © 1996 TranSwitch Corporation TranSwitch, TXC and SARA are registered trademarks of TranSwitch Corporation.

ii Edition 6

# **Table of Contents**

| List of H | igures   | ix                                              |

|-----------|----------|-------------------------------------------------|

| List of T | Tables   | xii                                             |

| Preface   | •••••    | XV                                              |

|           | About    | This Manualxv                                   |

|           |          | nce of This Manualxv                            |

|           | Organ    | ization of This Manualxv                        |

| Chapter   | 1. Intro | duction1-1                                      |

| 1.1       | Overa    | 11 Operation 1-2                                |

| 1.2       | ATM      | Adaptation Layer 1-3                            |

|           |          | AAL 3/4                                         |

|           |          | AAL 5                                           |

| 1.3       | The A    | TM Layer 1-8                                    |

| Chapter   | 2. SAR   | A Functional Description2-1                     |

| 2.1       | Major    | SARA Features                                   |

| 2.2       | Segme    | entation SARA Data Structures2-1                |

| 2.3       | SARA     | -S Operation2-3                                 |

|           | 2.3.1    | ~                                               |

|           | 2.3.2    | Peak and Average Metering 2-4                   |

|           | 2.3.3    | Congestion Control                              |

| 2.4       |          | embly SARA Data Structures2-5                   |

| 2.5       |          | -R Operation                                    |

|           | 2.5.1    |                                                 |

|           | 2.5.2    | Packet Timeout                                  |

| Chapter   | 3. Hard  | ware Description3-1                             |

| 3.1       | Segme    | entation SARA Hardware Description 3-1          |

|           | 3.1.1    | r                                               |

|           | 3.1.2    | Segmentation SARA Hardware Interfaces 3-2       |

|           |          | 3.1.2.1 Processor Interface                     |

|           |          | 3.1.2.2 Cell Interface                          |

|           |          | 3.1.2.3 Control Memory Interface                |

|           |          | 3.1.2.4 Packet Memory Interface                 |

|           |          | 3.1.2.5 Congestion Control Interface            |

|           |          | 3.1.2.6 Constant Bit Rate Traffic Interface 3-5 |

|           |          | 3.1.2.7 Miscellaneous Signals 3-6               |

| 3.2       | Reass    | embly SARA Hardware Description                 |

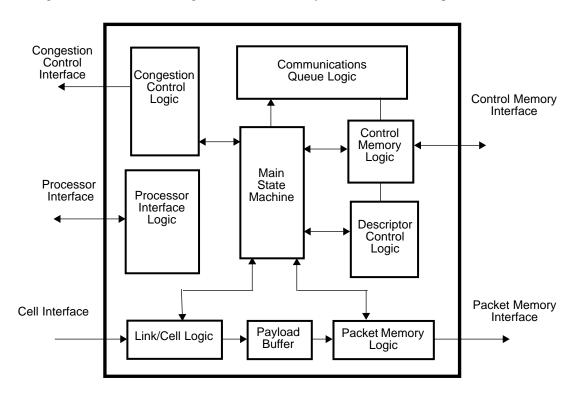

|           | 3.2.1    | Reassembly SARA Internal Block Description 3-7  |

|           | 3.2.2    | Reassembly SARA Hardware Interfaces             |

|           |         | 3.2.2.1    | Processor Interface           | 3-8  |

|-----------|---------|------------|-------------------------------|------|

|           |         | 3.2.2.2    | Cell Interface                | 3-9  |

|           |         | 3.2.2.3    | Control Memory Interface      | 3-9  |

|           |         | 3.2.2.4    | Packet Memory Interface       | 3-10 |

|           |         | 3.2.2.5    | Congestion Control Interface  | 3-11 |

|           |         | 3.2.2.6    | Miscellaneous Signals         | 3-11 |

| 3.3       | Hardw   | are Inter  | face Operation                | 3-12 |

|           | 3.3.1   | Processo   | or Interface                  | 3-12 |

|           | 3.3.2   | Control    | Memory Interface              | 3-14 |

|           |         | 3.3.2.1    | Address Bus CA(23:1)          | 3-14 |

|           |         | 3.3.2.2    | Data Bus CD(17:0)             | 3-14 |

|           |         | 3.3.2.3    | Control Interface             | 3-14 |

|           |         | 3.3.2.4    | Synchronous Mode              | 3-14 |

|           |         | 3.3.2.5    | Asynchronous Mode             | 3-22 |

|           | 3.3.3   | Packet N   | Memory Interface              | 3-23 |

|           |         | 3.3.3.1    | Data Bus PD(35:0)             | 3-23 |

|           |         | 3.3.3.2    | Address Bus PA(15:0)          | 3-23 |

|           |         | 3.3.3.3    | Control Signals               | 3-24 |

|           |         | 3.3.3.4    | Synchronous Mode              | 3-24 |

|           |         | 3.3.3.5    | Asynchronous Mode             | 3-28 |

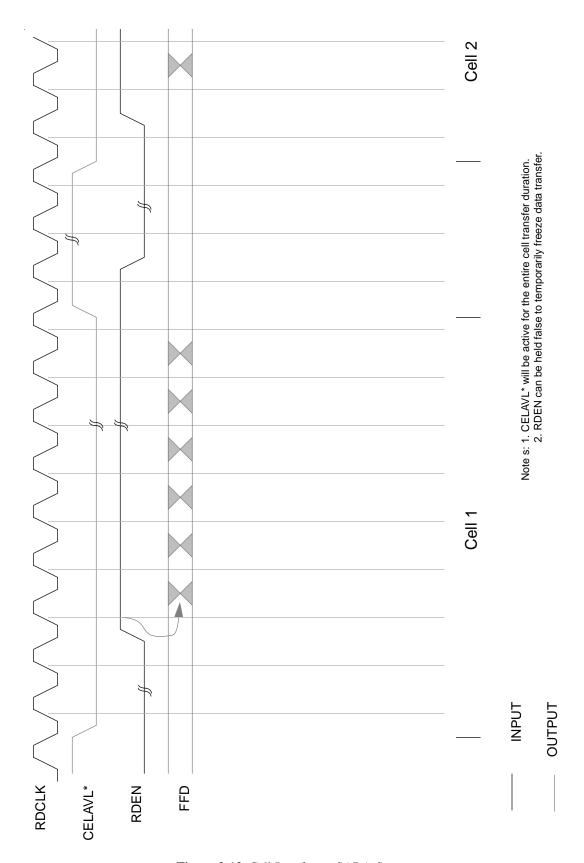

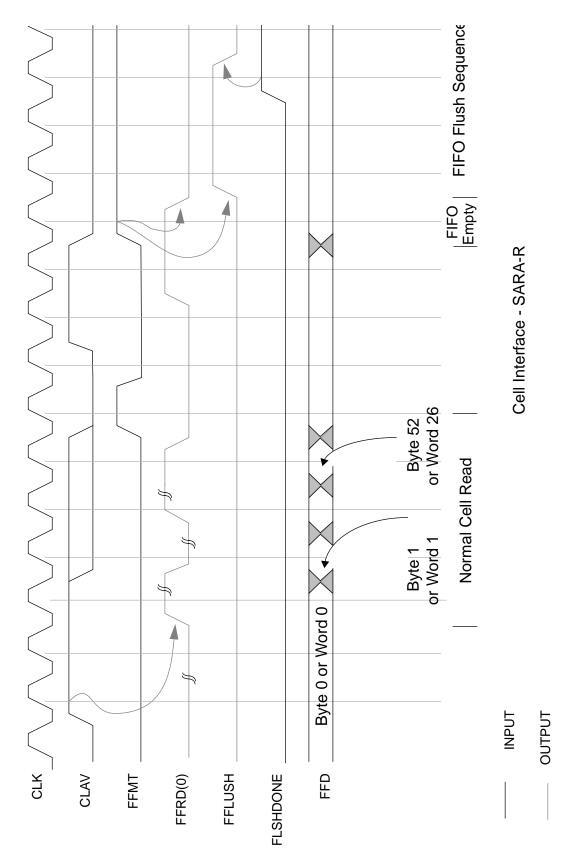

|           | 3.3.4   | Link/Ce    | ll Interface                  | 3-28 |

|           |         | 3.3.4.1    | SARA-S                        | 3-29 |

|           |         | 3.3.4.2    | SARA-R                        | 3-30 |

|           | 3.3.5   | Congesti   | ion Control Interface         | 3-33 |

|           | 3.3.6   | _          | t Bit Rate Interface          |      |

|           |         | 3.3.6.1    | SARA-S                        | 3-33 |

|           |         | 3.3.6.2    | SARA-R                        | 3-34 |

|           | 3.3.7   | Cross Re   | eference by Pin Name (SARA-S) | 3-36 |

|           | 3.3.8   |            | Pin Configuration             |      |

|           | 3.3.9   |            | eference by Pin Name (SARA-R) |      |

|           |         |            | Pin Configuration             |      |

| 2.4       |         |            | ackaging Dimensions           |      |

| 3.4       |         |            | tics                          |      |

| 3.5       | 3.5.1   |            | tics ng Characteristics       |      |

|           | 3.5.2   |            | e Signal Timings              |      |

|           | 3.3.2   | Titterract | Signal Timings                |      |

| Chapter 4 | I. SARA | A-S Regis  | ter Descriptions              | 4-1  |

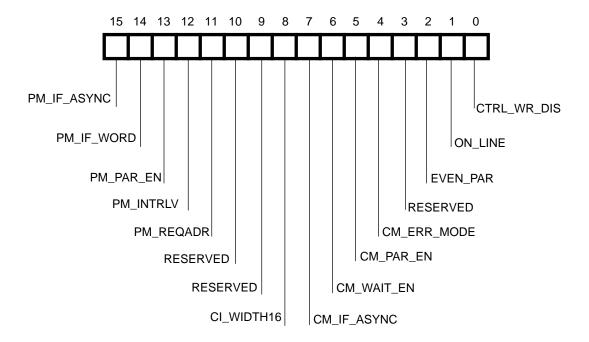

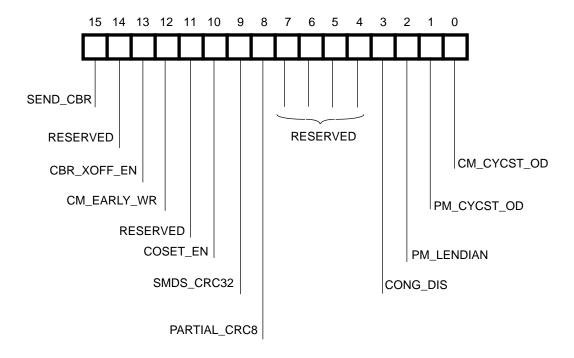

| 4.1       | Mode    | Registers  |                               | 4-3  |

|           | 4.1.1   | _          | egister 0                     |      |

|           | 4.1.2   |            | egister 1                     |      |

| 4.2       | Interru | ipt Status | Register                      | 4-9  |

iv Edition 6

| 4.3     | State Register                                             | 4-11 |

|---------|------------------------------------------------------------|------|

| 4.4     | Interrupt Mask Register                                    | 4-13 |

| 4.5     | Rate Queue Registers                                       | 4-15 |

| 4.6     | Queue Base Address Register                                | 4-17 |

| 4.7     | Descriptor Table Base Address Register                     | 4-17 |

| 4.8     | Virtual Circuit (VC) Table Base Address Register           | 4-18 |

| 4.9     | Packet Memory Address Match Register                       | 4-21 |

| 4.10    | Command Register                                           | 4-21 |

| 4.11    | Communication Queues                                       | 4-22 |

| 4.12    | Cell Counter Registers                                     | 4-23 |

| 4.13    | Constant Bit Rate Address Registers                        | 4-23 |

| 4.14    | Rate Queue Starting Descriptor Number Diagnostic Registers | 4-24 |

| 4.15    | Current Descriptor Number Diagnostic Register              | 4-24 |

| 4.16    | CC_Label Diagnostic Register                               | 4-24 |

| Chapter | 5. SARA-R Register Descriptions                            | 5-1  |

| 5.1     | Mode Registers                                             |      |

| 0.1     | 5.1.1 Mode Register 0                                      |      |

|         | 5.1.2 Mode Register 1                                      |      |

| 5.2     | Interrupt Status Register                                  |      |

| 5.3     | State Register                                             |      |

| 5.4     | Interrupt Mask Register                                    |      |

| 5.5     | Queue Base Address Register                                |      |

| 5.6     | Descriptor Table Base Address Register                     |      |

| 5.7     | VC Table Base Address Register                             |      |

| 5.8     | VP Base Address Register                                   | 5-18 |

| 5.9     | VP Filter Register                                         | 5-18 |

| 5.10    | Reassembly Table Base Register                             | 5-19 |

| 5.11    | Packet Memory Address Match Register                       | 5-22 |

| 5.12    | Command Register                                           | 5-22 |

| 5.13    | Dropped Packet Count Register                              | 5-23 |

| 5.14    | Error Count Register                                       | 5-23 |

| 5.15    | Dropped CBR Cells Count Register Queue                     | 5-23 |

| 5.16    | Received Cell Count Register                               | 5-23 |

| 5.17    | Small Buffer Check Register                                | 5-23 |

| 5.18    | Large Buffer Check Register                                | 5-24 |

| 5.19    | Large Buffer Size Register                                 | 5-24 |

| 5.20    | Packet Timeout Count Register                              |      |

| 5.21    | Packet Aging Interval Count Register                       | 5-24 |

| 5.22    | Timeout Index Register                                     |      |

| 5.23    | Timeout Index Range Register                               |      |

| 5.24    | Communication Queues                                       |      |

|         | 5.24.1 Small Free Descriptor Queue                         |      |

|         | 5.24.2 Large Free Descriptor Queue                         | 5-26 |

Edition 6

|         | 5.24.3  | Packet (  | Complete Queue                                     | 5-26    |

|---------|---------|-----------|----------------------------------------------------|---------|

|         | 5.24.4  | Exception | on Queue                                           | 5-26    |

| 5.25    | CBR a   | and Raw   | Cell Queue Base Address Registers                  | 5-27    |

| 5.26    | CBR (   | Queue Re  | gisters                                            | 5-27    |

| 5.27    | Raw C   | Cell Queu | e Registers                                        | 5-28    |

| 5.28    | OAMO    | CC_CHK    | Register                                           | 5-28    |

| Chapter | 6. SARA | A-S Softv | vare Interfaces                                    | 6-1     |

| 6.1     | SARA    | -S Contr  | ol Memory                                          | 6-1     |

|         | 6.1.1   | Buffer I  | Descriptor Table                                   | 6-1     |

|         | 6.1.2   |           | Circuit (VC) Table:                                |         |

|         | 6.1.3   | Average   | Metering Function                                  | 6-7     |

|         | 6.1.4   |           | Ready Queue                                        |         |

|         | 6.1.5   |           | t Complete Queue                                   |         |

| 6.2     | SARA    |           | t Memory                                           |         |

|         | 6.2.1   |           | Data Buffers                                       |         |

|         | 6.2.2   | •         | Test) Data                                         |         |

|         | 6.2.3   |           | ıta                                                |         |

| 6.3     |         |           | Software Functions                                 |         |

|         | 6.3.1   | •         | Initialization                                     |         |

|         |         |           | Allocating Buffers in the Packet Memory            | 6-15    |

|         |         | 6.3.1.2   | Allocating and Initializing the Buffer Descriptors | 6-15    |

|         |         | 6.3.1.3   | Allocating the VC Table                            |         |

|         |         | 6.3.1.4   | Setting-up the Communication Queues                |         |

|         |         | 6.3.1.5   | Setting the Peak-Rate Metering Parameters          |         |

|         |         | 6.3.1.6   | Initializing the Mask Bits                         |         |

|         |         | 6.3.1.7   | Setting the Mode Registers                         |         |

|         | 6.3.2   |           | Circuit Setup                                      |         |

|         | 6.3.3   |           | tting a Packet                                     |         |

|         | 6.3.4   |           | tting OAM Cells                                    |         |

|         | 6.3.5   |           | tting a CBR Cell                                   |         |

| Chapter | 7. SAR  | A-R Softs | ware Interfaces                                    | 7-1     |

| 7.1     |         |           | ol Memory                                          |         |

| ,,,     | 7.1.1   |           | Descriptor Table                                   |         |

|         | 7.1.2   | Reassen   | ably Table Pointer/Descriptor Table Entry          |         |

|         | 7 1 2   |           | ion                                                |         |

|         | 7.1.3   |           | le                                                 |         |

|         | 7.1.4   |           | le                                                 |         |

|         | 7.1.5   |           | ably Table                                         |         |

|         | 7.1.6   |           | arge Free Descriptor Queues                        |         |

|         | 7.1.7   |           | Complete Queue                                     |         |

|         | 7.1.8   | Exception | on Queue                                           | / - 1 1 |

vi Edition 6

| 7.2        | SARA           | A-R Packet Memory                                                   | 7-13       |

|------------|----------------|---------------------------------------------------------------------|------------|

|            | 7.2.1          | Packet Data for Reassembly                                          | 7-13       |

|            | 7.2.2          | CBR Data                                                            | 7-14       |

|            | 7.2.3          | Raw Cell Queue                                                      | 7-15       |

| 7.3        | SARA           | A-R Basic Software Functions                                        | 7-16       |

|            | 7.3.1          | Startup Initialization                                              | 7-16       |

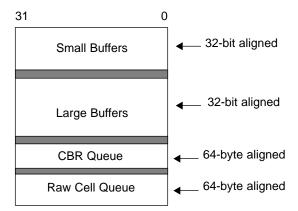

|            |                | 7.3.1.1 Allocating Buffers in the Packet Memory                     | 7-16       |

|            |                | 7.3.1.2 Allocating and Initializing the Buffer Descriptors          | 7-17       |

|            |                | 7.3.1.3 Allocating the VP Table                                     | 7-17       |

|            |                | 7.3.1.4 Allocating the VC Table                                     | 7-17       |

|            |                | 7.3.1.5 Allocating the Reassembly Table                             |            |

|            |                | 7.3.1.6 Setting-up the VC Table                                     |            |

|            |                | 7.3.1.7 Setting-up the VP Table                                     |            |

|            |                | 7.3.1.8 Setting-up the Reassembly Table                             |            |

|            |                |                                                                     |            |

|            |                |                                                                     |            |

|            |                | 7.3.1.10 Initializing the Mask Bits                                 |            |

|            |                | 7.3.1.11 Setting the Mode Registers                                 |            |

|            | 7.3.2          | Receiving a Cell                                                    |            |

|            | 7.3.3          | Receiving a Packet                                                  |            |

|            | 7.3.4          | Receiving Constant Bit Rate Traffic                                 |            |

|            | 7.3.5<br>7.3.6 | Receiving Congestion Notification Cells<br>Exception Queue Handling |            |

|            | 7.3.0          | Exception Queue Handling                                            |            |

| Appendix   | A. Co          | ntrol Memory Size Examples                                          | A-1        |

| Appendix   | B. Pac         | eket Memory Interface Example                                       | В-1        |

| Appendix   | C. Lin         | ık Interface Example                                                | C-1        |

| Appendix   | D. Co          | ntrol Memory Example                                                | D-1        |

| Appendix   | E. SA          | RA Performance Examples                                             | E-1        |

| Appendix   | F. Co          | ngestion Control in SARA                                            | F-1        |

| Appendix   | G. SA          | RA Time-Out Operation                                               | G-1        |

| Appendix   | H. SA          | RA Chipset Deviation List                                           | Н-1        |

| Standards  | s Docu         | mentation Sources                                                   | Sources-1  |

| List of Te | chnica         | l Manual Changes                                                    | Changes-1  |

| Glossary   | •••••          |                                                                     | Glossary-1 |

Edition 6 vii

viii Edition 6

# **List of Figures**

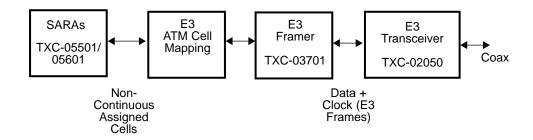

| Figure 1-1.  | Typical ATM Network Interface Unit Implementation                         | 1-2  |

|--------------|---------------------------------------------------------------------------|------|

| Figure 1-2.  | Protocol Model for Variable Bit Rate AAL Type 3/4                         | 1 1  |

| F: 1 2       | and Type 5                                                                |      |

| Figure 1-3.  | Structure of the AAL 3/4 CPCS-PDU                                         |      |

| Figure 1-4.  | CRC-32 in an 802.6 Frame                                                  |      |

| Figure 1-5.  | TranSwitch Proprietary CRC-32                                             |      |

| Figure 1-6.  | The Segmentation Process for AAL 3/4                                      |      |

| Figure 1-7.  | Structure of the AAL 3/4 SAR_PDU                                          |      |

| Figure 1-8.  | Structure of the AAL 5 CPCS_PDU                                           |      |

| Figure 1-9.  | Segmentation Process for AAL 5                                            |      |

| Figure 1-10. | Structure of an ATM Cell at the User Network Interface                    |      |

| Figure 2-1.  | Segmentation SARA Data Structures                                         |      |

| Figure 2-2.  | Typical Rate Queue Data Structure                                         |      |

| Figure 2-3.  | SARA-R Data Structures                                                    | 2-6  |

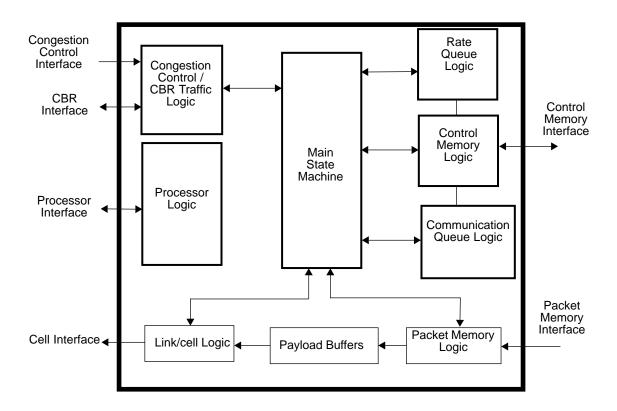

| Figure 3-1.  | Segmentation SARA Block Diagram                                           | 3-1  |

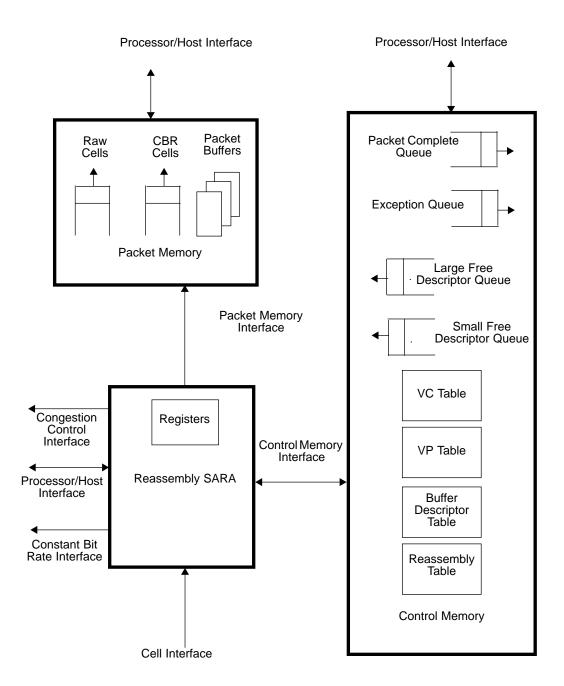

| Figure 3-2.  | Block Diagram of Reassembly SARA                                          | 3-7  |

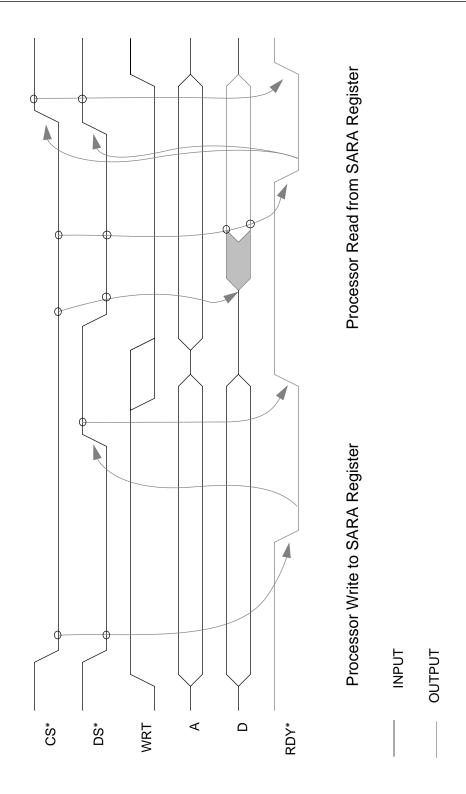

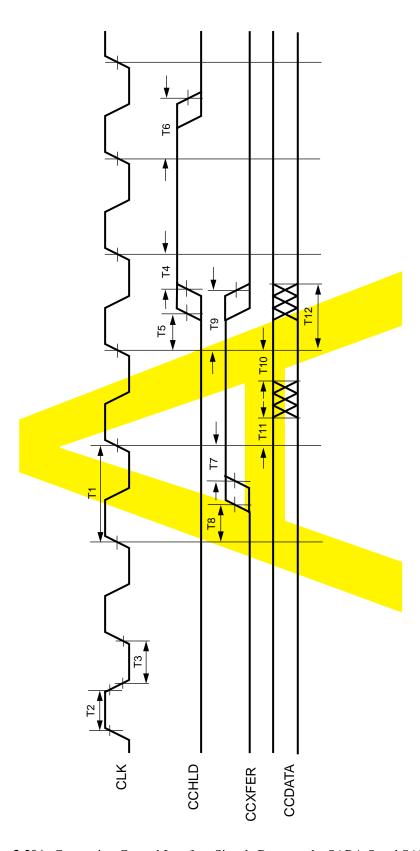

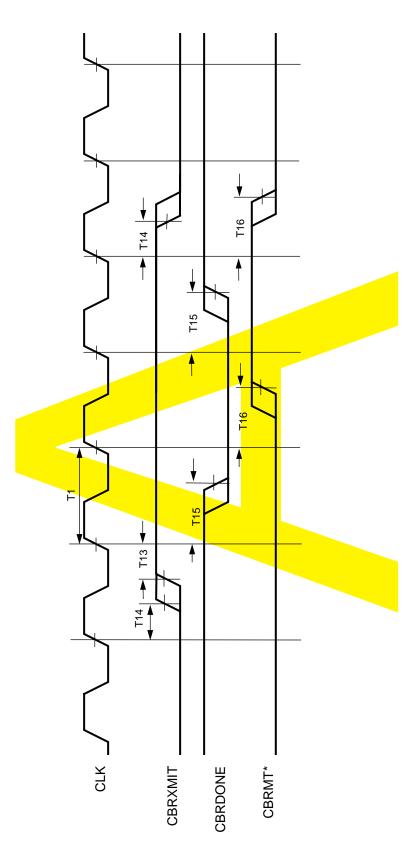

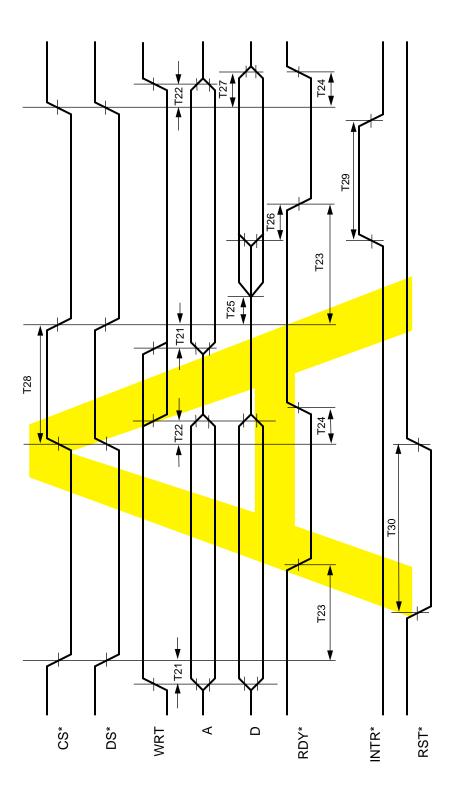

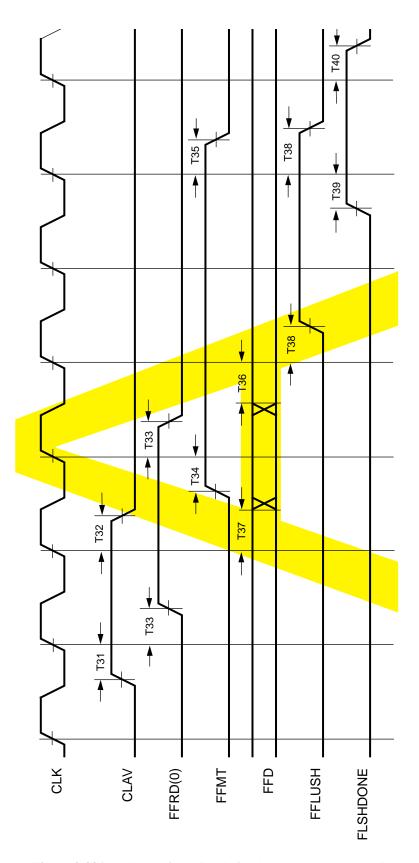

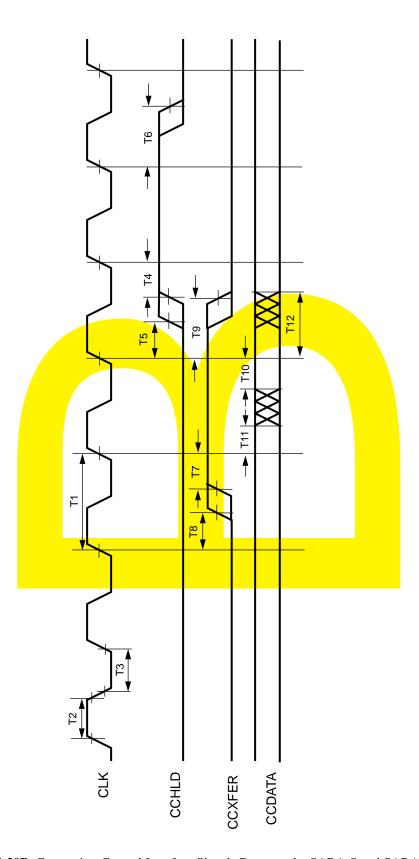

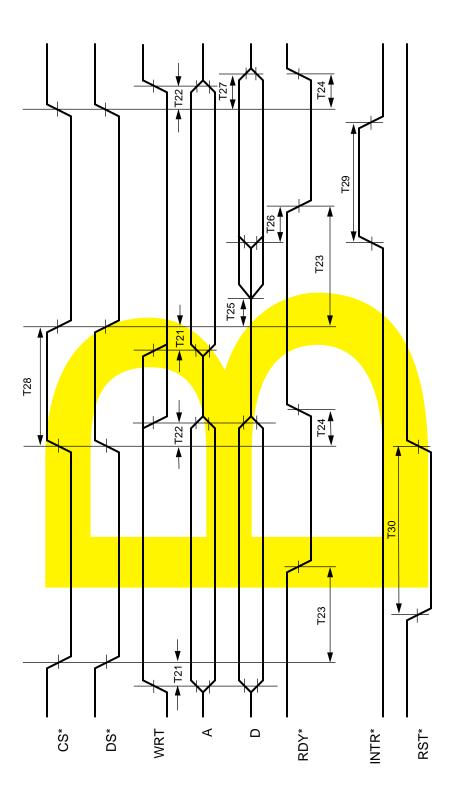

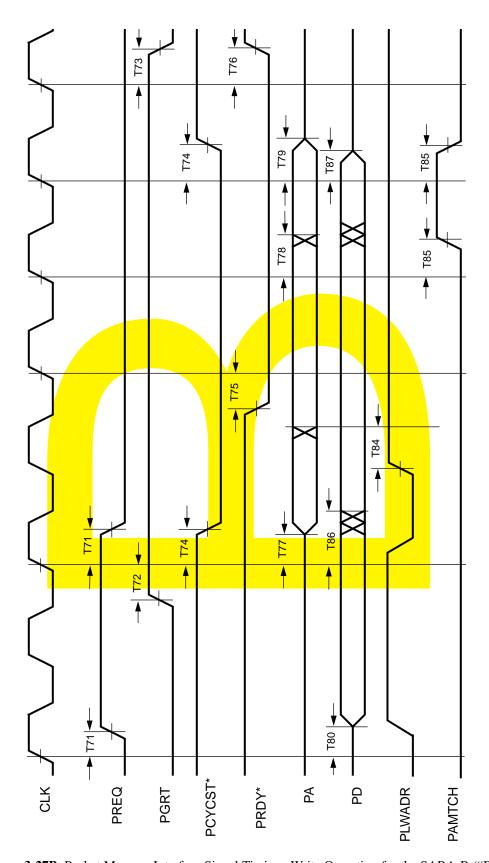

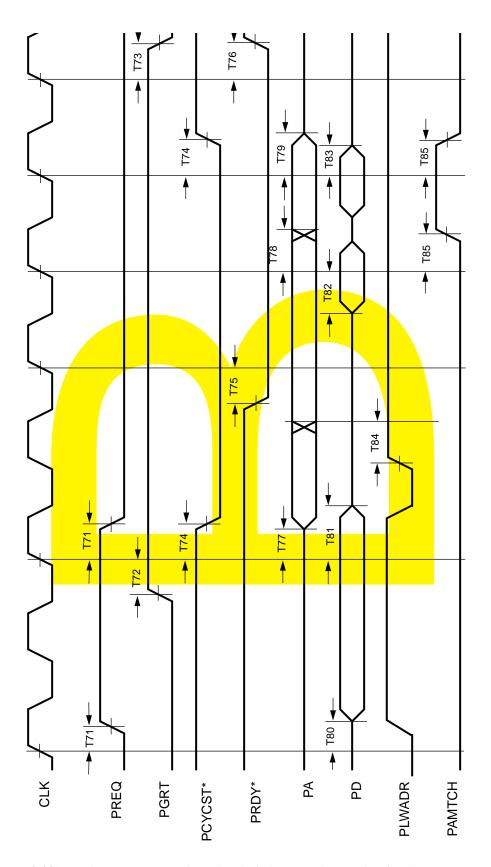

| Figure 3-3.  | Processor Interface Functional Timing                                     | 3-13 |

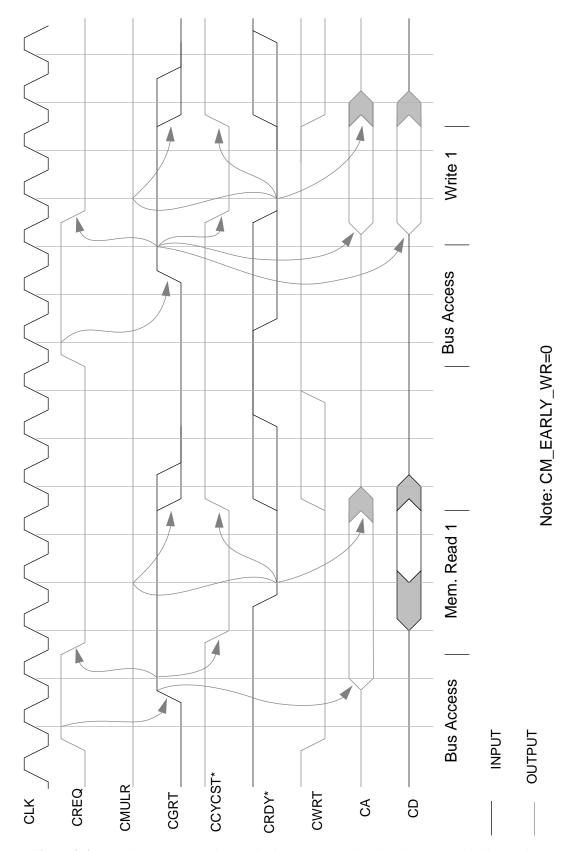

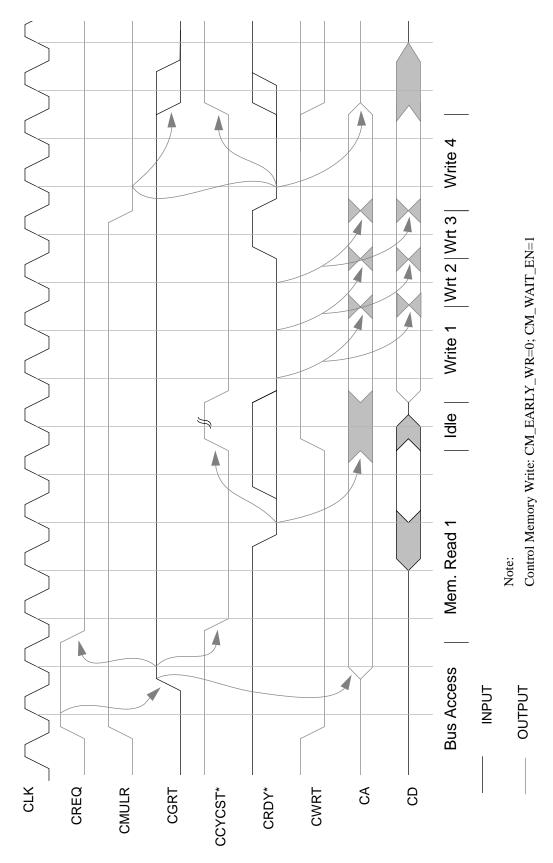

| Figure 3-4.  | Control Memory Interface—Single Access Read and Write—Normal Write Mode   | 3-15 |

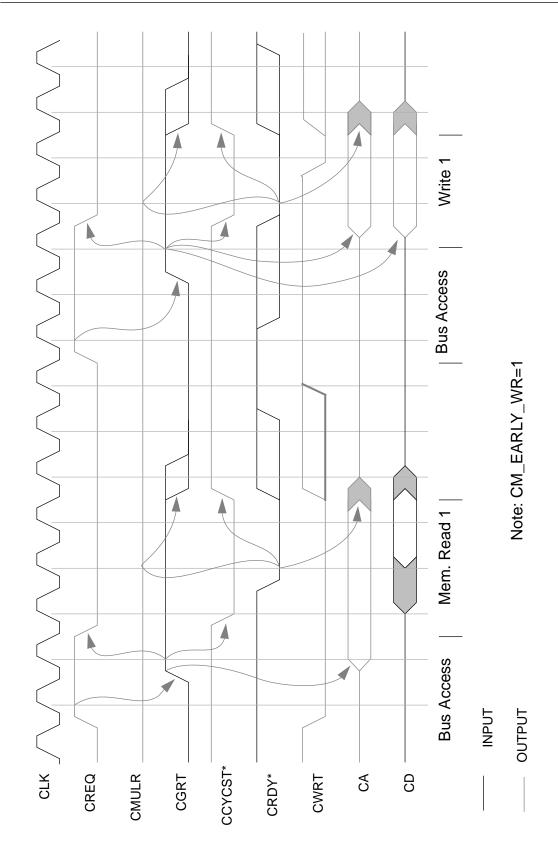

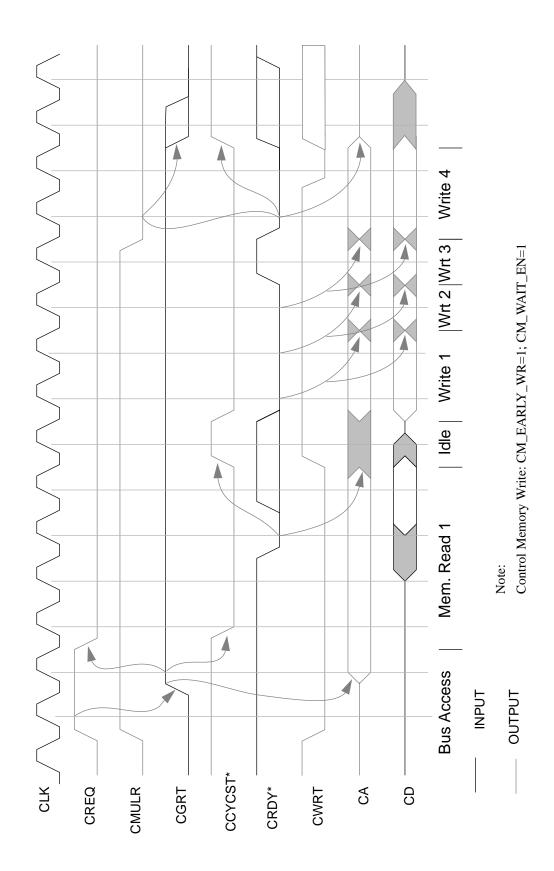

| Figure 3-5.  | Control Memory Interface—Single Access Read and Write—Early Write Mode    | 3-16 |

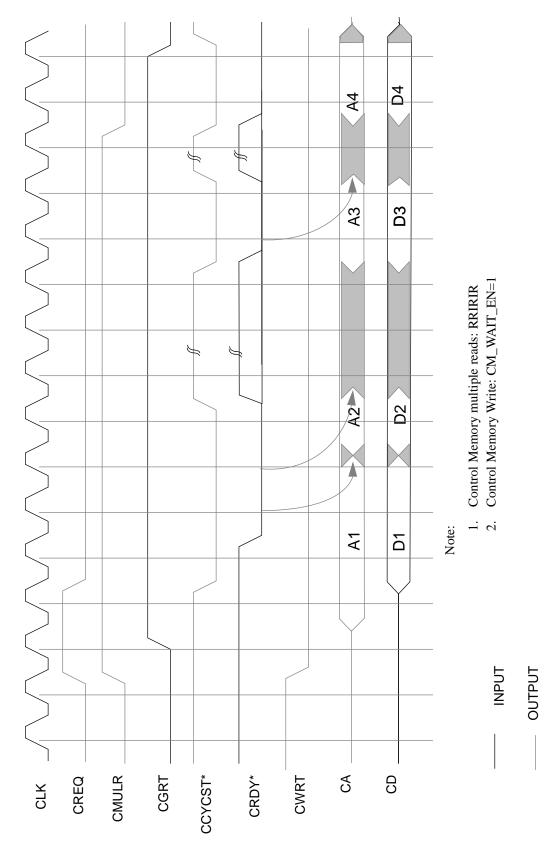

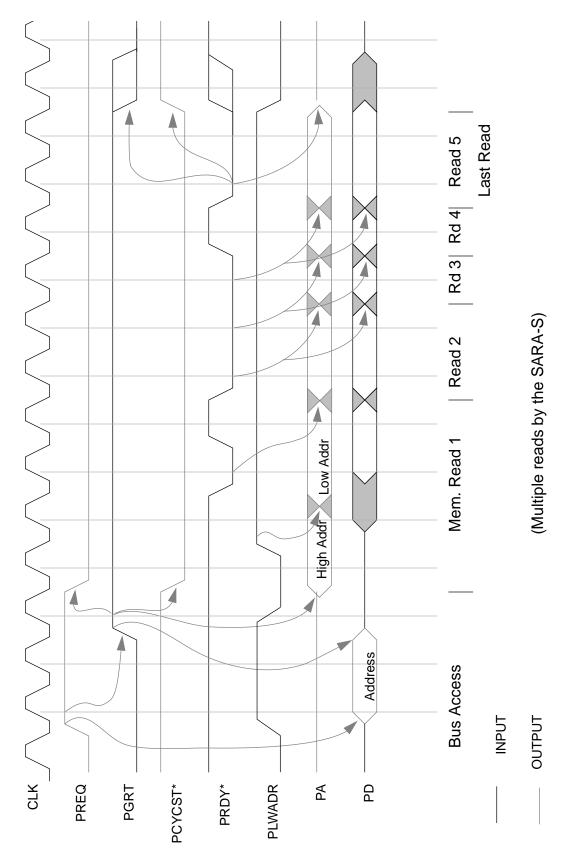

| Figure 3-6.  | Control Memory Interface—Multiple Reads                                   | 3-17 |

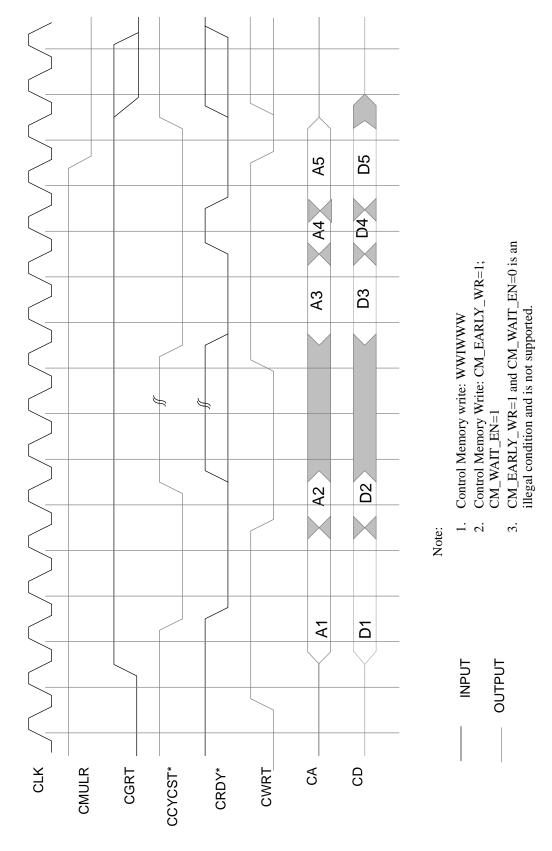

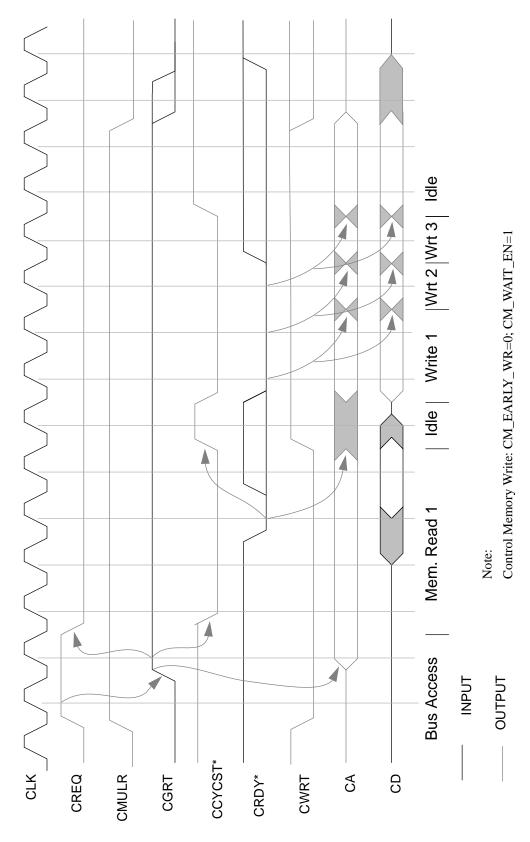

| Figure 3-7.  | Control Memory Interface—Multiple Writes                                  | 3-18 |

| Figure 3-8.  | Control Memory Interface—Single Read/ Multiple Writes—Normal Write Signal | 3-19 |

| Figure 3-9.  | Control Memory Interface—Single Read/ Multiple Writes—Early Write Signal  | 3-20 |

| Figure 3-10. | Control Memory Interface—Without Last Access                              | 3-21 |

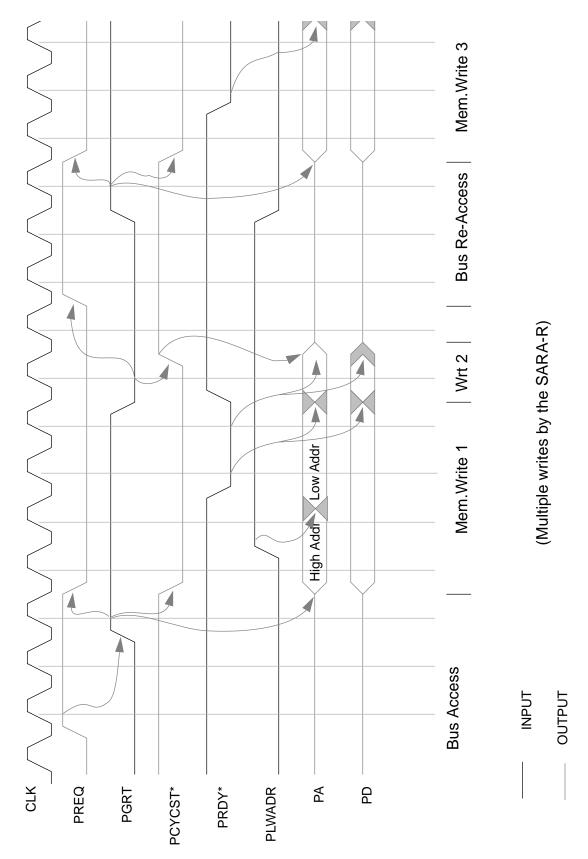

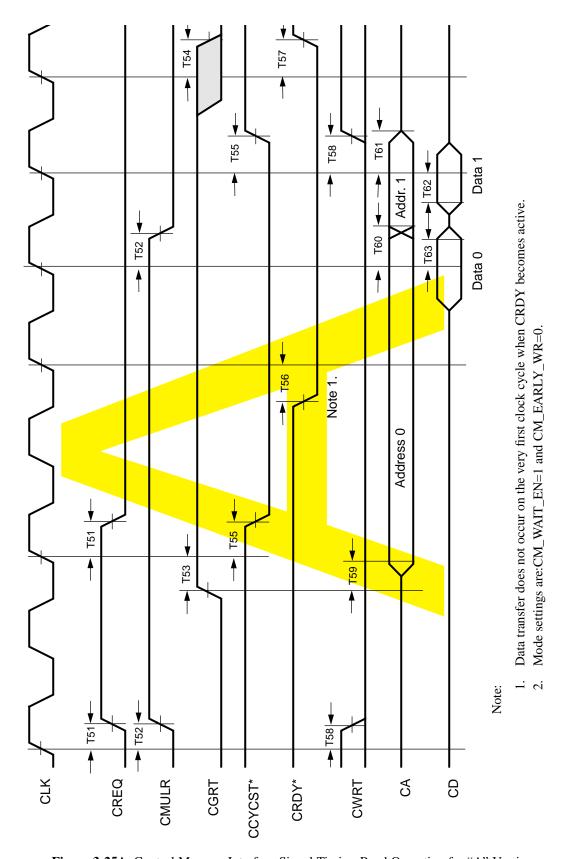

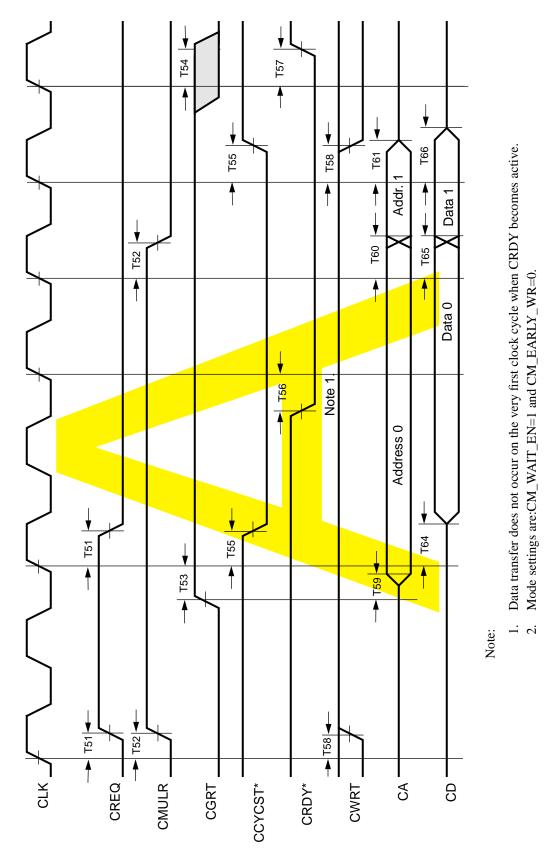

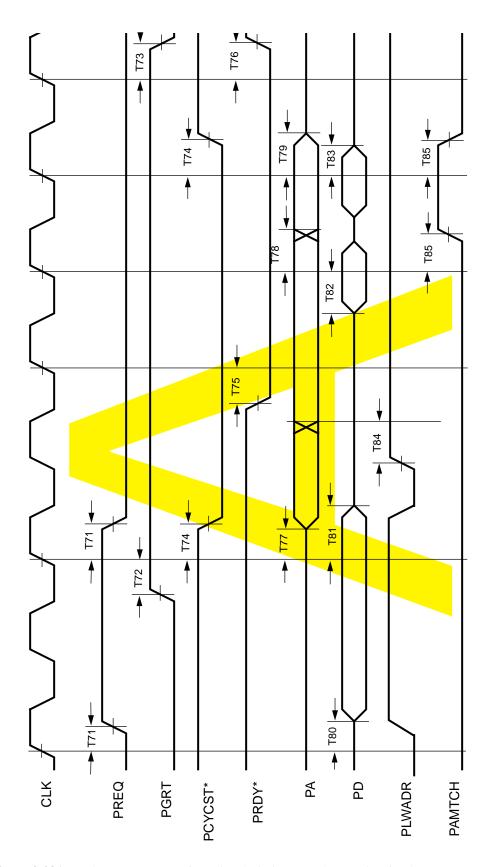

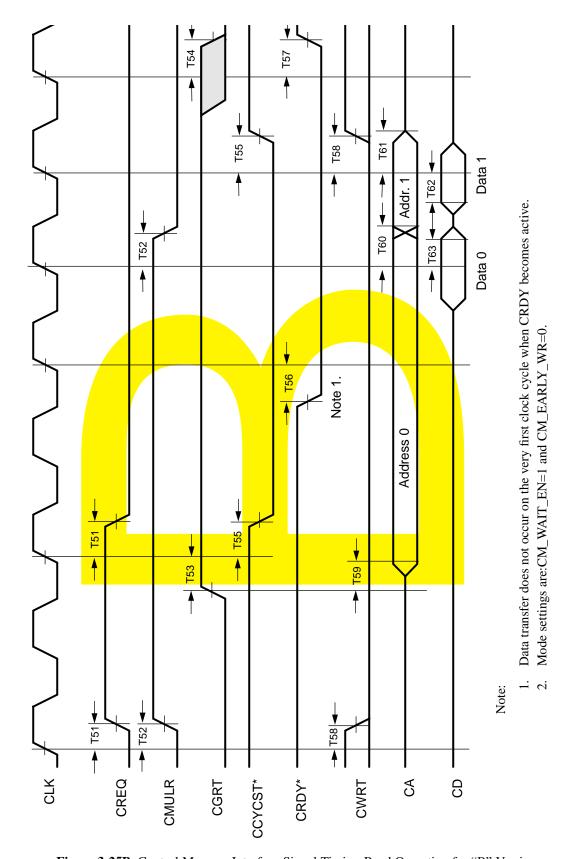

| Figure 3-11. | Packet Memory Interface—Address Driven on Data Bus During Bus Access      | 3-26 |

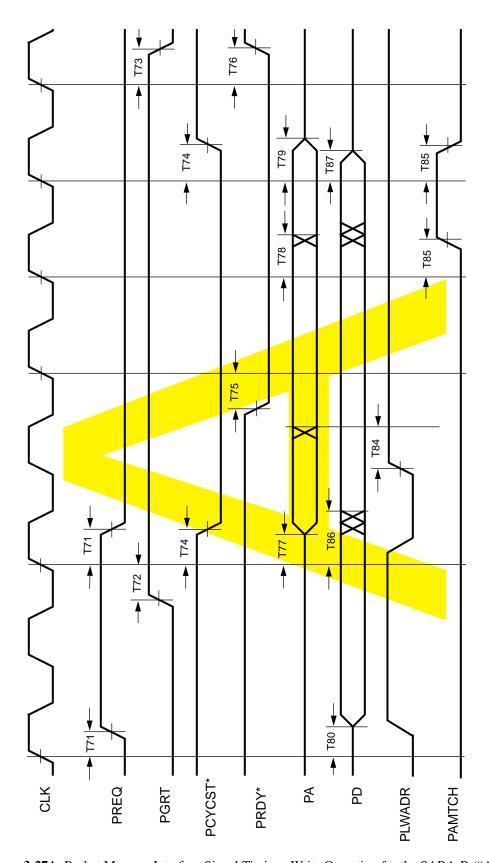

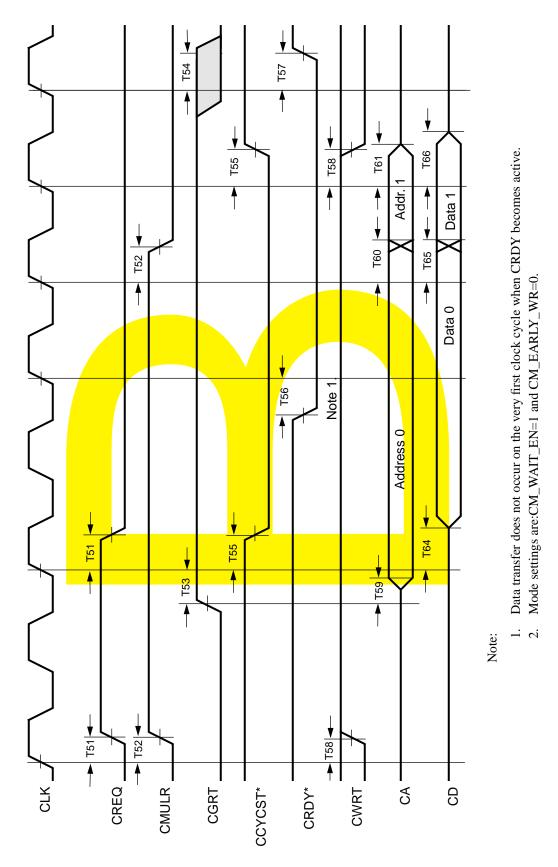

| Figure 3-12. | Packet Memory Interface—Bus Preempted by De-assertion of PGRT             | 3-27 |

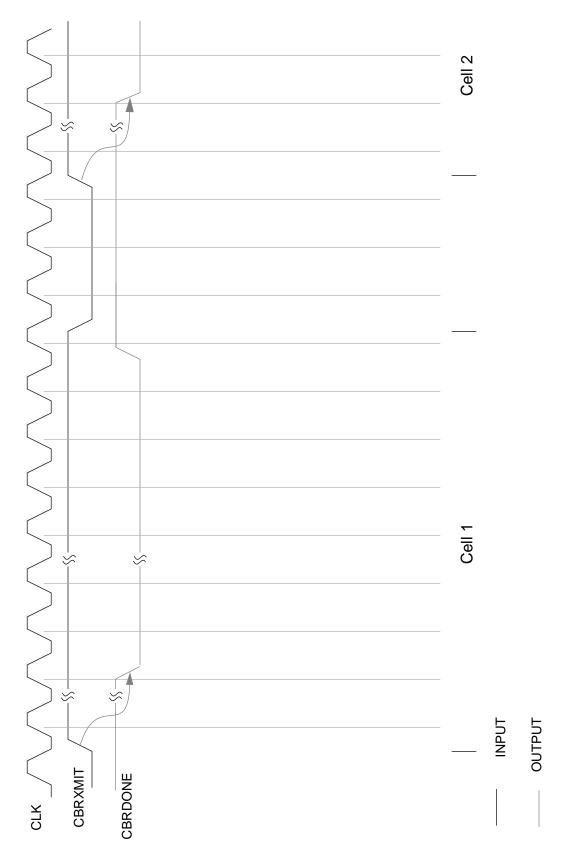

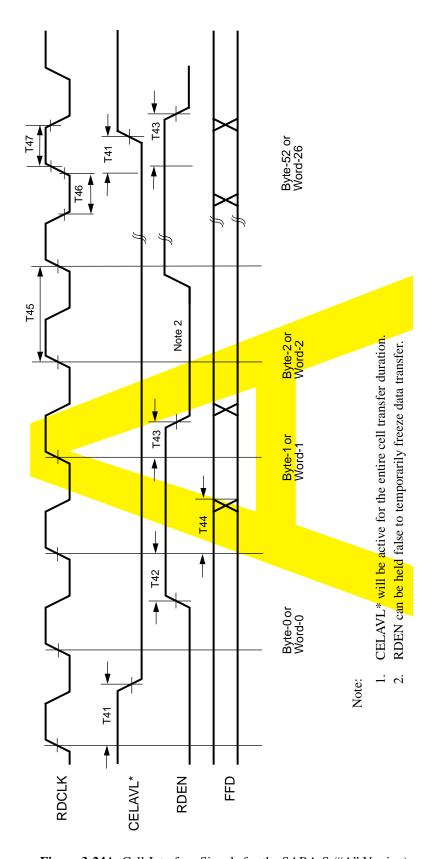

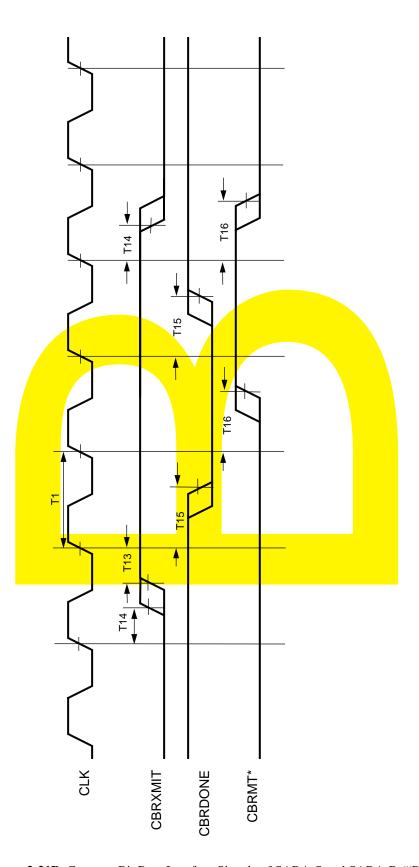

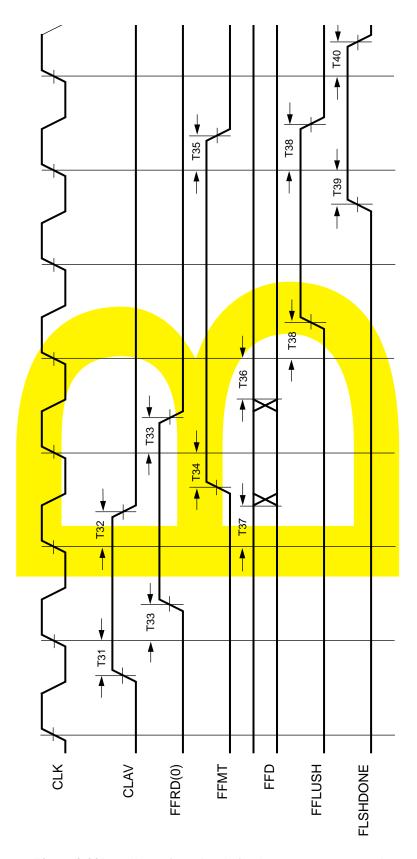

| Figure 3-13. | Cell Interface—SARA-S                                                     | 3-31 |

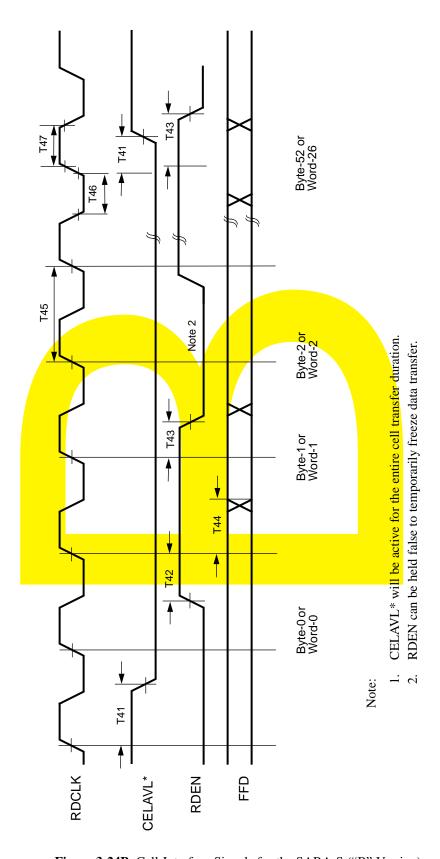

| Figure 3-14. | Cell Interface—SARA-R                                                     | 3-32 |

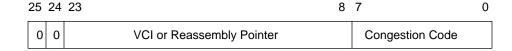

| Figure 3-15. | CCDATA Format                                                             | 3-33 |

| Figure 3-16. | Constant Bit Rate Interface—SARA-S                                        | 3-35 |

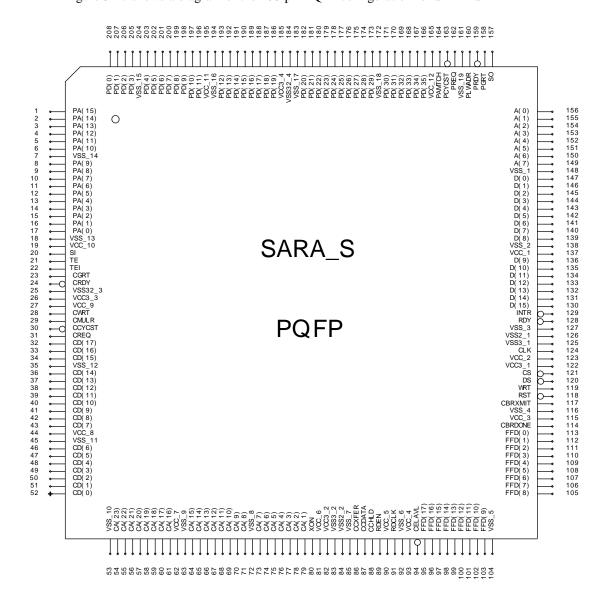

| Figure 3-17. | 208-pin PQFP Pin Configuration—SARA-S                                     | 3-37 |

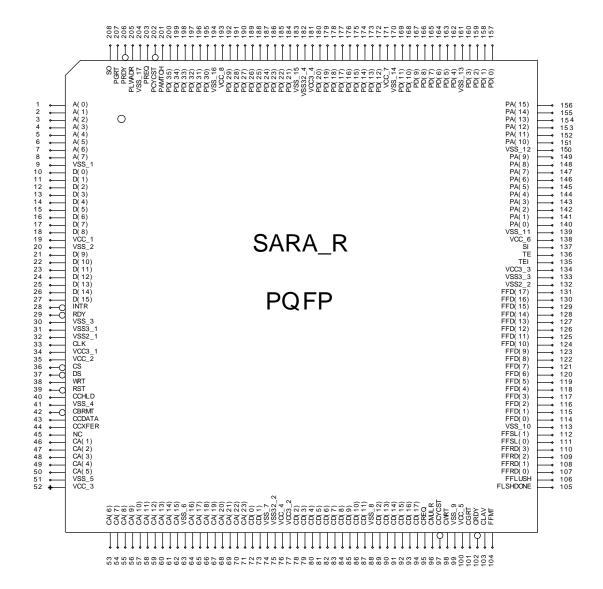

| Figure 3-18. | 208-pin PQFP Pin Configuration—SARA-R                                     | 3-39 |

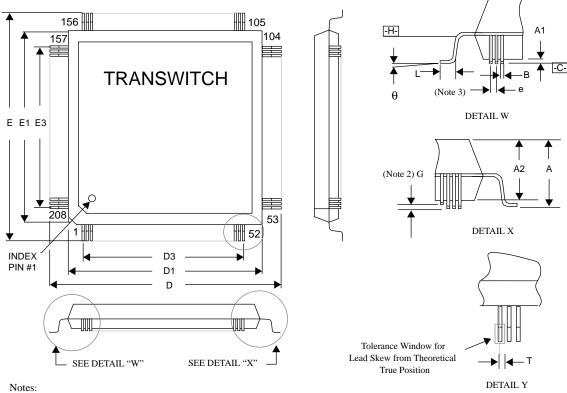

| Figure 3-19. | SARA Packaging                                                            | 3-40 |

Edition 6 ix

| Figure 3-20A   | .Congestion-Control Interface Signals Between the SARA-S and SARA-R ("A" Versions)     | 3-48 |

|----------------|----------------------------------------------------------------------------------------|------|

| Figure 3-21A   | .Constant Bit Rate Interface Signals of SARA-S and SARA-R ("A" Versions)               | 3-49 |

| Figure 3-22A   | .Processor-Interface Signal Timing for "A" Versions                                    | 3-50 |

| _              | .Cell-Interface Signals for the SARA-R ("A" Version)                                   |      |

| Figure 3-24A   | .Cell-Interface Signals for the SARA-S ("A" Version)                                   | 3-52 |

| Figure 3-25A   | .Control Memory Interface Signal Timing-Read Operation for "A" Versions                | 3-53 |

| Figure 3-26A   | .Control Memory Interface Signal Timings-Write Operation for "A" Versions              | 3-54 |

| Figure 3-27A   | .Packet Memory Interface Signal Timings-Write Operation for the SARA-R ("A" Version)   | 3-55 |

| Figure 3-28A   | .Packet Memory Interface Signal Timings-Read<br>Operation for the SARA-S ("A" Version) | 3-56 |

| Figure 3-20B   | .Congestion-Control Interface Signals Between the SARA-S and SARA-R ("B" Versions)     | 3-57 |

| Figure 3-21B   | .Constant Bit Rate Interface Signals of SARA-S and SARA-R ("B" Versions)               | 3-58 |

| Figure 3-22B   | .Processor-Interface Signal Timing for "B" Versions                                    | 3-59 |

| Figure 3-23B   | .Cell-Interface Signals for the SARA-R ("B" Version)                                   | 3-60 |

| Figure 3-24B   | .Cell-Interface Signals for the SARA-S ("B" Version)                                   | 3-61 |

| Figure 3-25B   | .Control Memory Interface Signal Timing-Read Operation for "B" Versions                | 3-62 |

| Figure 3-26B   | .Control Memory Interface Signal Timings-Write Operation for "B" Versions              | 3-63 |

| Figure 3-27B   | Packet Memory Interface Signal Timings-Write Operation for the SARA-R ("B" Version)    | 3-64 |

| Figure 3-28B   | Packet Memory Interface Signal Timings-Read Operation for the SARA-S ("B" Version)     | 3-65 |

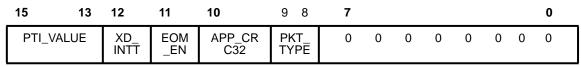

| Figure 4-1.    | Mode Register 0 Data Bits                                                              | 4-4  |

| Figure 4-2.    | Mode Register 1 Data Bits                                                              | 4-7  |

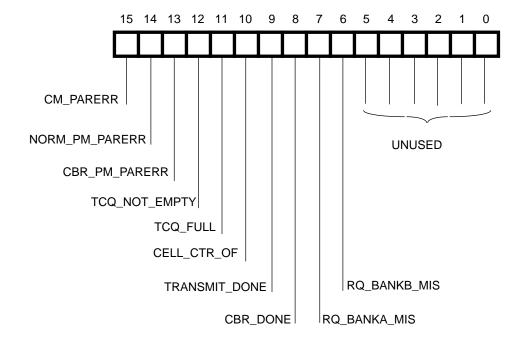

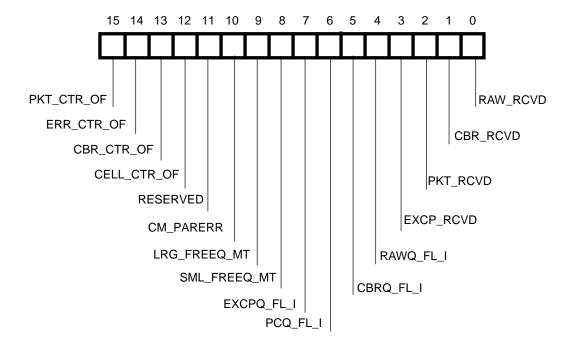

| Figure 4-3.    | Interrupt Status Register Bit Positions                                                | 4-10 |

| Figure 4-4.    | State Register Bit Positions                                                           | 4-12 |

| Figure 4-5.    | Bit Positions for SARA-S Interrupt Mask Register                                       | 4-13 |

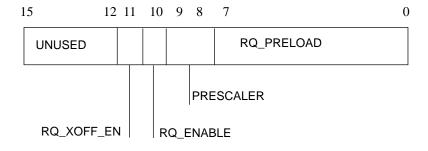

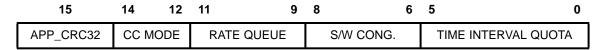

| Figure 4-6. I  | Rate Queue Register                                                                    | 4-15 |

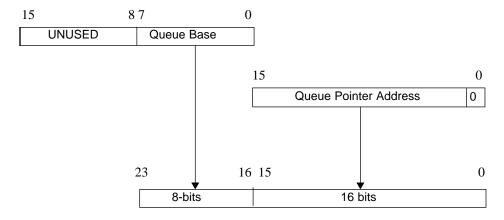

| Figure 4-7.    | SARA-S Queue Address Generation                                                        | 4-17 |

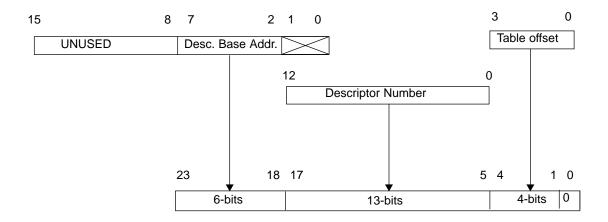

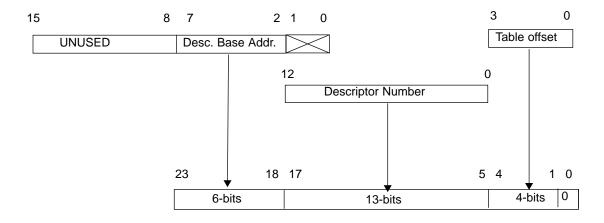

| Figure 4-8.    | SARA-S Descriptor Table Address Generation                                             | 4-18 |

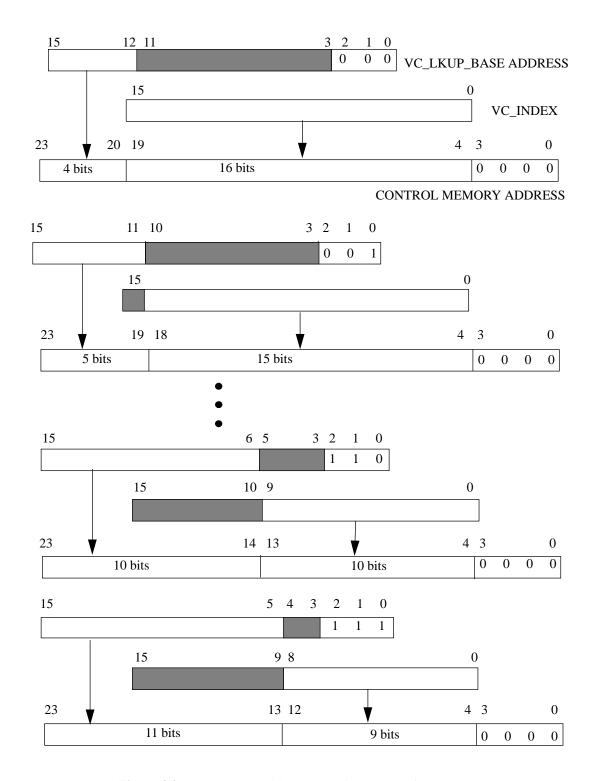

| Figure 4-9.    | SARA-S VC Table Entry Address Generation                                               | 4-20 |

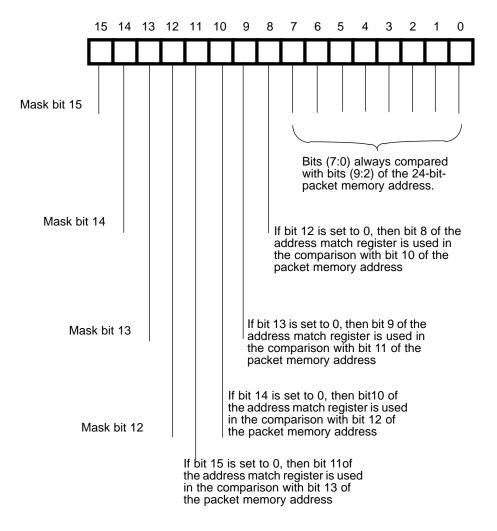

| Figure 4-10. S | SARA-S Packet Memory Address Match Register                                            | 4-21 |

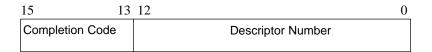

| Figure 4-11    | Transmit Complete Queue                                                                | 4-22 |

x Edition 6

| Figure 4-12. | SARA-S Packet Ready and Transmit Complete Queue Operational States | 4-23 |

|--------------|--------------------------------------------------------------------|------|

| Figure 5-1.  | SARA-R Mode Register 0 Bit Positions                               |      |

| -            | SARA-R Mode Register 1 Bit Positions                               |      |

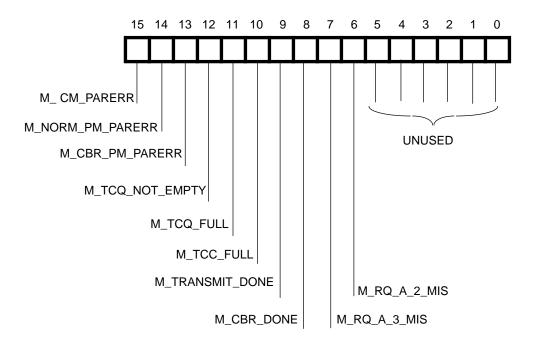

|              | Interrupt Status Register Bit Positions                            |      |

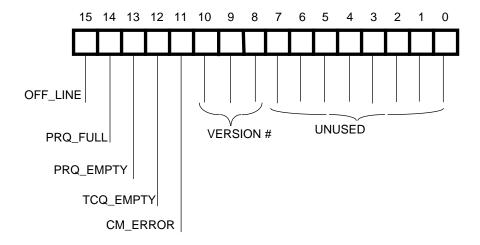

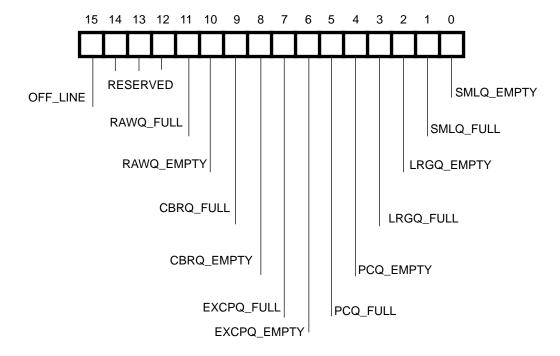

| Figure 5-4.  | SARA-R State Register Bit Positions                                |      |

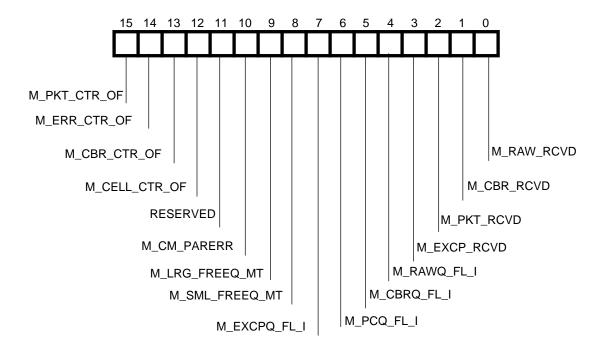

| Figure 5-5.  | Mask Register Bit Positions                                        |      |

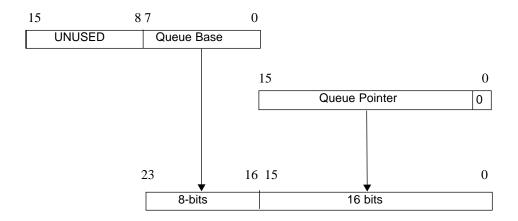

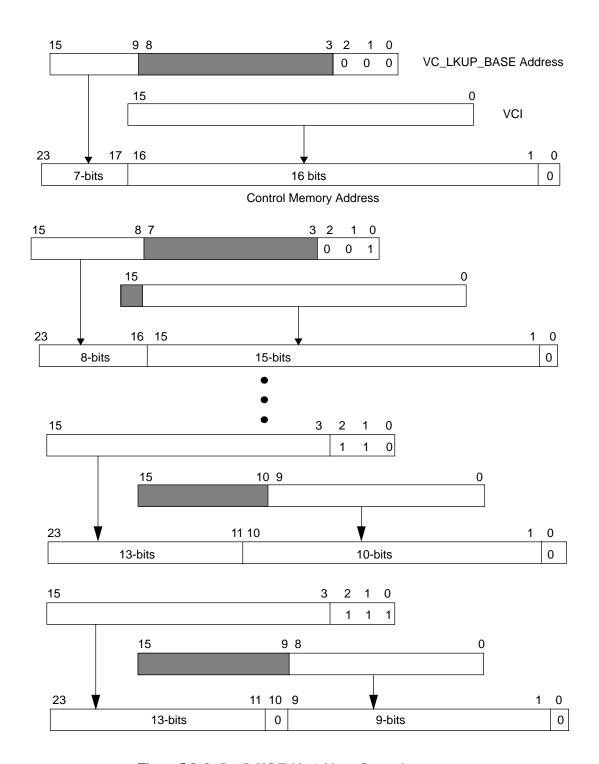

| Figure 5-6.  | SARA-R Queue Address Generation                                    | 5-15 |

| Figure 5-7.  | SARA-R Descriptor Table Address generation                         | 5-15 |

| Figure 5-8.  | SARA-R VC Table Address Generation                                 | 5-17 |

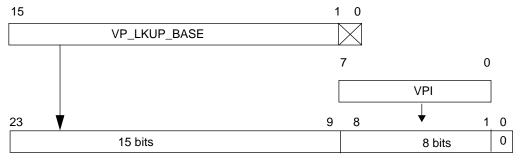

| Figure 5-9.  | SARA-R VP Base Address Register                                    | 5-18 |

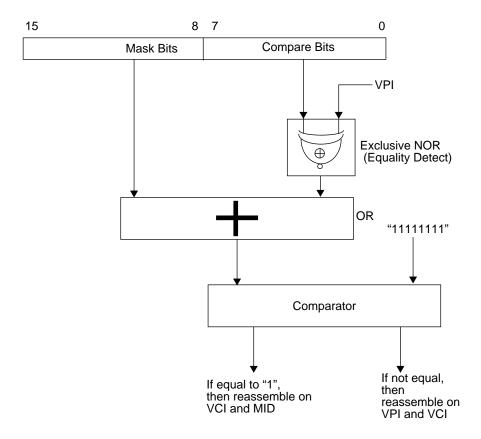

| Figure 5-10. | VP Filter Register                                                 | 5-19 |

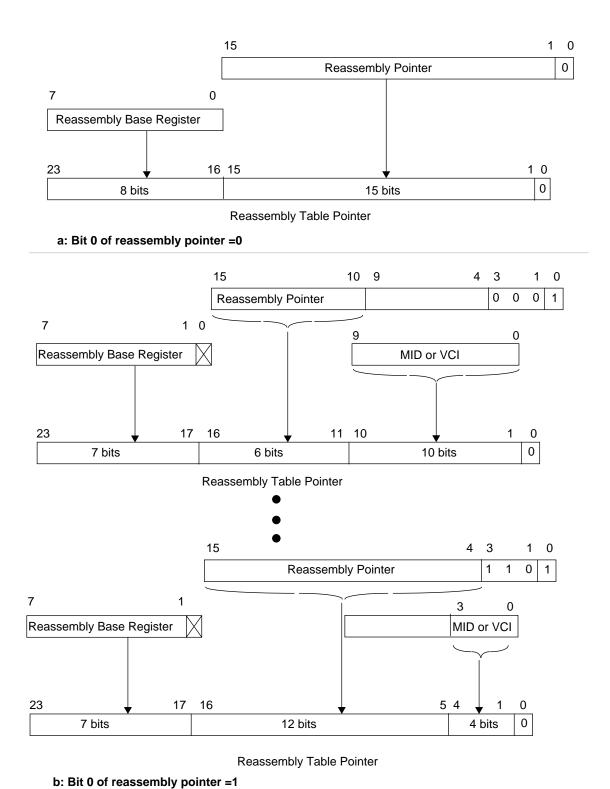

| Figure 5-11. | Reassembly Table Pointer Construction                              | 5-21 |

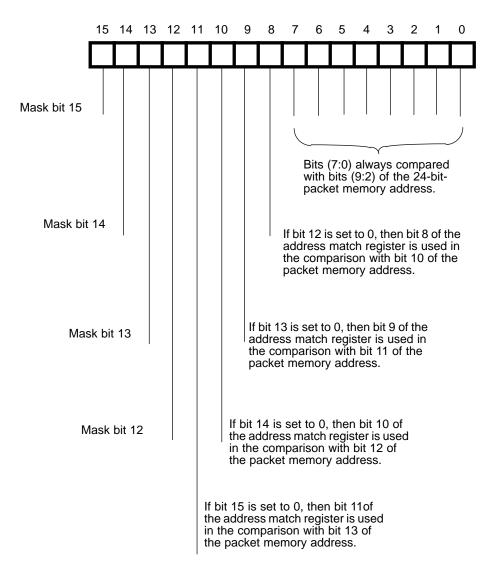

| Figure 5-12. | SARA-R Packet Memory Address Match Register                        | 5-22 |

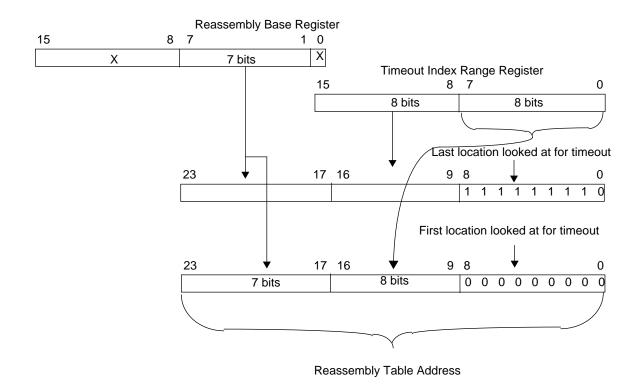

| Figure 5-13. | Timeout Index Range Register                                       | 5-25 |

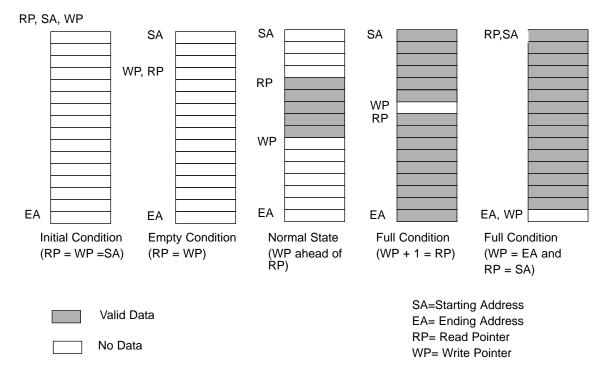

| Figure 5-14. | SARA-R Communication queues - Operational States                   | 5-26 |

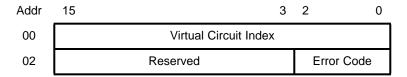

| Figure 5-15. | Entries in Exception Queue                                         | 5-27 |

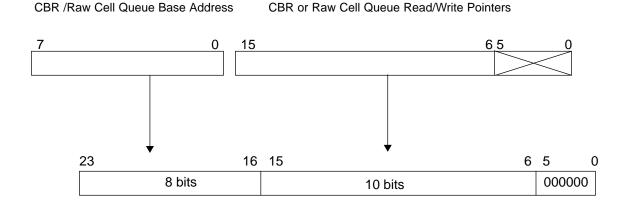

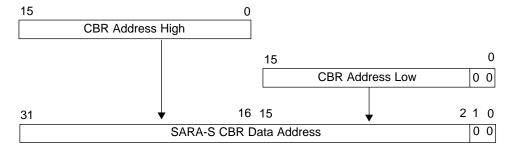

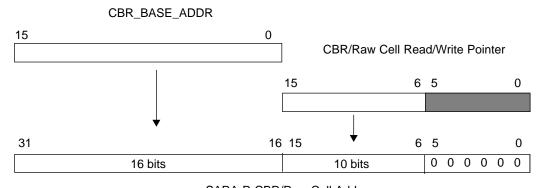

| Figure 5-16. | CBR and Raw Cell Queue Address Generation                          | 5-27 |

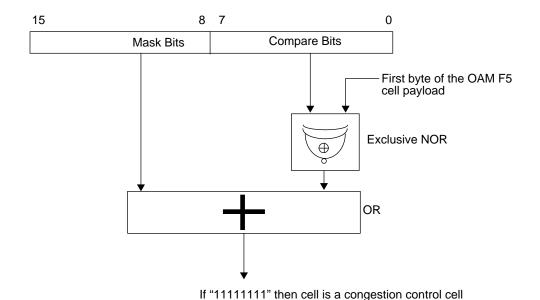

| Figure 5-17. | OAMCC_CHK Register                                                 | 5-28 |

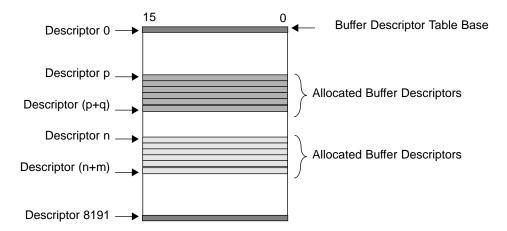

| Figure 6-1.  | Buffer Descriptors Mapped into Two Regions                         | 6-1  |

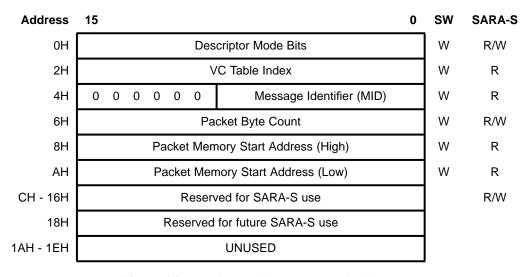

| Figure 6-2.  | Descriptor Table Entry Organization                                | 6-2  |

| Figure 6-3.  | Descriptor Mode Bits                                               | 6-2  |

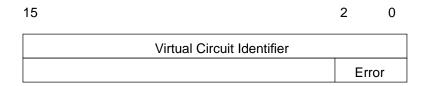

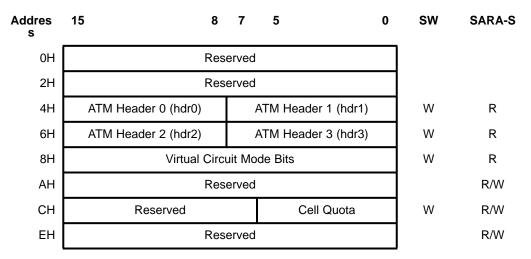

| Figure 6-4.  | Virtual Circuit Table Entry                                        | 6-4  |

| Figure 6-5.  | Virtual Circuit Mode Bits Word                                     | 6-5  |

| Figure 6-6.  | Packet Ready Queue Entry                                           | 6-9  |

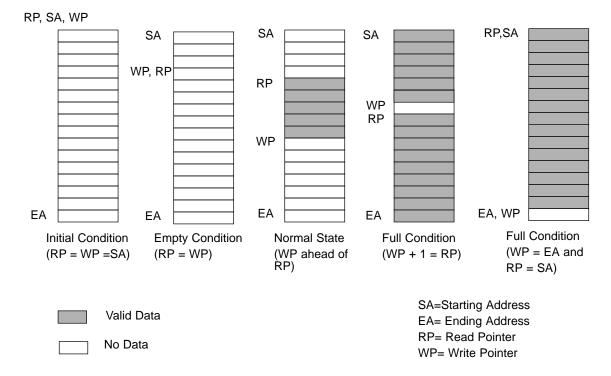

| Figure 6-7.  | Communication Queue Operational States                             | 6-10 |

| Figure 6-8.  | Address Generation of Queue Entry                                  | 6-11 |

| Figure 6-9.  | Transmit Complete Queue Entry                                      | 6-11 |

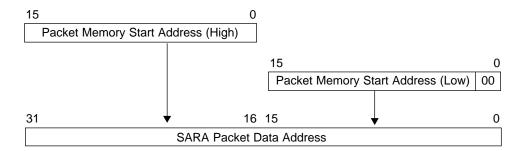

| Figure 6-10. | Address of Data in Packet Memory                                   | 6-12 |

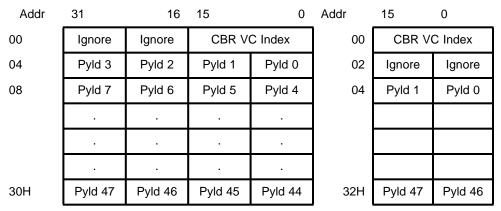

| Figure 6-11. | Address of SARA-S CBR Data in Packet Memory                        | 6-13 |

| Figure 6-12. | Buffers in Packet Memory                                           | 6-15 |

| Figure 6-13. | AAL 3/4 Frame Without CRC-32                                       | 6-17 |

| Figure 6-14. | AAL 3/4 802.6 Frame With CRC-32                                    | 6-18 |

| Figure 6-15. | AAL 3/4, Non-802.6 Frame with CRC-32                               | 6-18 |

| Figure 6-16. | AAL 5 Frame with CRC-32                                            | 6-18 |

| Figure 7-1.  | Receive Descriptor Table Entry Organization                        | 7-2  |

| Figure 7-2.  | Descriptor Mode/Status Bits                                        | 7-2  |

| Figure 7-3.  | Reassembly Table Pointer Process                                   | 7-7  |

| Figure 7-4.  | VC Table Entry                                                     | 7-8  |

Edition 6 xi

| Figure 7-5.  | VP Table Entry                                              | 7-9         |

|--------------|-------------------------------------------------------------|-------------|

| Figure 7-6.  | Reassembly Table Entry                                      | 7-9         |

| Figure 7-7.  | Small/Large Free Descriptor and Packet Complete Queue Entry | .7-11       |

| Figure 7-8.  | Exception Queue Entry                                       | .7-12       |

| Figure 7-9.  | Address of SARA-R CBR/Raw Cell Data in Packet Memory        | .7-14       |

| Figure 7-10. | Packet Memory Data Structure Alignments                     | .7-16       |

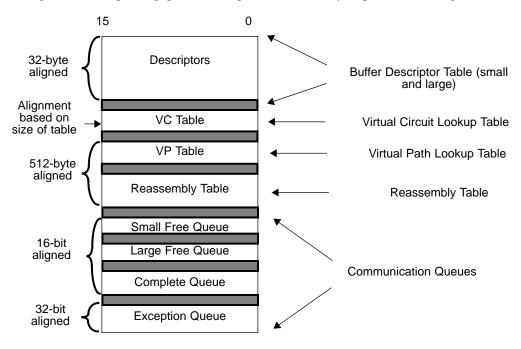

| Figure 7-11. | Control Memory Data Structure Alignments                    | .7-19       |

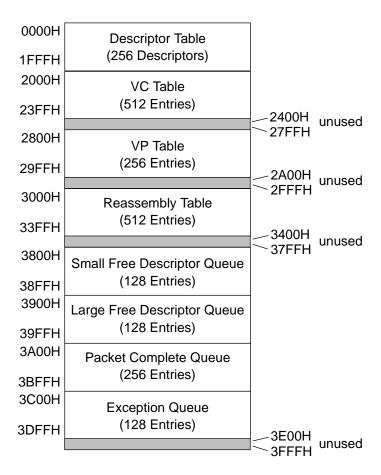

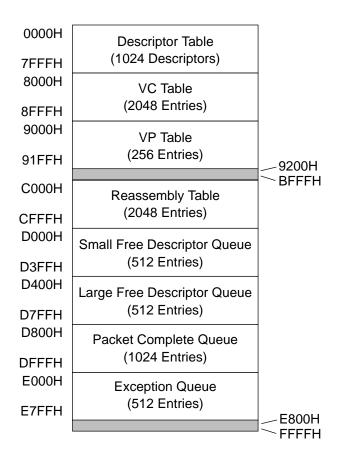

| Figure A-1.  | SARA-R Control Memory Map for Small System                  | A-3         |

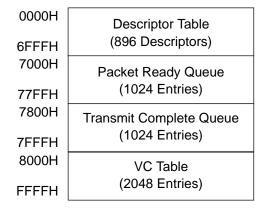

| Figure A-2.  | SARA-S Control Memory Map for Small System                  | A-3         |

| Figure A-3.  | SARA-R Control Memory Map for Large System                  | A-6         |

| Figure A-4.  | SARA-S Control Memory Map for Large System                  | A-6         |

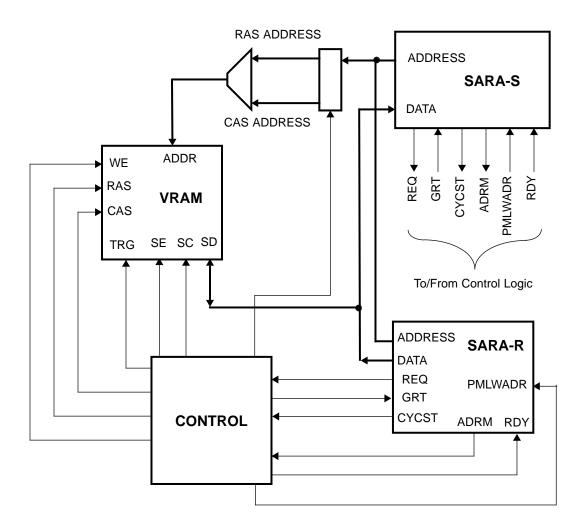

| Figure B-1.  | Packet Memory Interface Example                             | B-1         |

| Figure C-1.  | Transmit and Receive Link Interface Example                 | <b>C</b> -1 |

| Figure C-2.  | Alternative Interface Applications                          | C-2         |

| Figure D-1.  | Control Memory Example                                      | D-1         |

| Figure D-2.  | Control Memory State Diagram                                | D-2         |

xii Edition 6

# **List of Tables**

| Table 3-1.   | SARA-S Processor Interface Pin Descriptions                                 | 3-2  |

|--------------|-----------------------------------------------------------------------------|------|

| Table 3-2.   | SARA-S Cell Interface Pin Descriptions                                      | 3-3  |

| Table 3-3.   | SARA-S Control Memory Interface Pin Descriptions                            | 3-3  |

| Table 3-4.   | SARA-S Packet Memory Interface Pin Descriptions                             | 3-4  |

| Table 3-5.   | SARA-S Congestion Control Interface Pin Descriptions                        | 3-5  |

| Table 3-6.   | SARA-S Constant Bit Rate Transfer Interface                                 |      |

|              | Pin Description                                                             |      |

| Table 3-7.   | SARA-S Miscellaneous Signals Pin Description                                |      |

| Table 3-8.   | SARA-R Processor Interface Pin Descriptions                                 |      |

| Table 3-9.   | SARA-R Cell Interface Pin Description                                       |      |

| Table 3-10.  | SARA-R Control Memory Interface Pin Descriptions                            | 3-10 |

| Table 3-11.  | SARA-R Packet Memory Interface Pin Descriptions                             |      |

| Table 3-12.  | SARA-R Congestion Control Interface Pin Descriptions                        | 3-11 |

|              | SARA-R Miscellaneous Signals Pin Descriptions                               | 3-11 |

| Table 3-14.  | Interactions of PREQ, PGRT, and PLWADR with the                             | 2 22 |

| Table 2 15   | Packet Data Bus PD(31:0)                                                    |      |

|              | Mode Bit/PLWADR Interactions                                                |      |

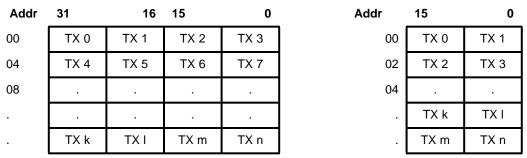

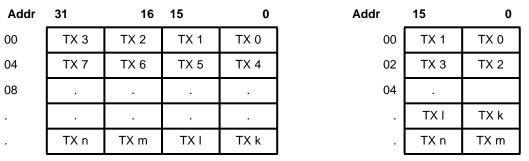

|              | Byte Ordering of Data for Link/Cell Interface                               |      |

|              | Cross Reference by Pin Name for SARA-S                                      |      |

|              | Cross Reference by Pin Name for SARA-R                                      |      |

|              | SARA Packaging Dimensions                                                   | 3-40 |

| Table 3-20.  | SARA DC Characteristics Over Commercial Operating Ranges                    | 3-41 |

| Table 3-21.  | SARA Capacitance Characteristics                                            |      |

|              | Switching Characteristics for "A" Versions over                             |      |

| 14010 3 2211 | Commercial Operating Conditions                                             | 3-42 |

| Table 3-22B  | .Switching Characteristics for "B" Versions over                            |      |

|              | Commercial Operating Conditions                                             | 3-45 |

| Table 4-1.   | SARA-S Internal Registers                                                   | 4-1  |

| Table 4-2.   | SARA-S Diagnostic Registers                                                 | 4-3  |

| Table 4-3.   | Interactions of PREQ, PGRT, and PLWADR with Packet Data Bus PD(31:0)—SARA-S | 4-5  |

| Table 4-4.   | Rate Queue Registers                                                        | 4-15 |

| Table 4-5.   | Peak Segmentation Rates for Different Prescaler Values                      | 4-16 |

| Table 4-6.   | Rate Queue Register Programming Values                                      | 4-17 |

| Table 4-7.   | Number of VC Table Entries for Various Values of                            |      |

|              | VC_LKUP_BASE Register                                                       |      |

| Table 5-1.   | SARA-R Internal Registers                                                   | 5-1  |

Edition 6 xiii

| Tabl | le 5-2.  | Interactions of PREQ, PGRT, and PLWADR with Packet Data Bus PD(31:0)—SARA-R      | 5-5  |

|------|----------|----------------------------------------------------------------------------------|------|

| Tabl | le 5-3.  | Number of VC Table Entries for Various Values of the VC_LKUP_BASE Register       | 5-18 |

| Tabl | le 5-4.  | Reassembly Table Pointer Construction                                            | 5-20 |

| Tabl | le 6-1.  | Congestion Control Mode                                                          | 6-5  |

| Tabl | le 6-2.  | Rate Queue Modes                                                                 | 6-6  |

| Tabl | le 6-3.  | Software Congestion Level Modes                                                  | 6-6  |

| Tabl | le 6-4.  | Average Metering Rate                                                            | 6-8  |

| Tabl | le 6-5.  | Completion Codes for Transmit Complete Queue                                     | 6-11 |

| Tabl | le 6-6.  | Packet Memory Data in Big-Endian 32-bit and 16-bit Modes                         | 6-13 |

| Tabl | le 6-7.  | Packet Memory Data in Little-Endian 32-bit and 16-bit Modes                      | 6-13 |

| Tabl | le 6-8.  | Packet Memory Data in Big-Endian 32-bit and 16-bit Modes for CBR Cells           | 6-14 |

| Tabl | le 6-9.  | Packet Memory Data in Little-Endian 32-bit and 16-bit Modes for CBR Cells        | 6-14 |

| Tabl | le 6-10. | Setting the Number of VCs for SARA-S                                             | 6-16 |

| Tabl | le 7-1.  | Number of MID Bits in Reassembly Pointer                                         | 7-8  |

| Tabl | le 7-2.  | Number of VCI Bits in the Reassembly Pointer                                     | 7-9  |

| Tabl | le 7-3.  | Reassembly Table Entry State Bits Description                                    | 7-10 |

| Tabl | le 7-4.  | Error Code Explanations for Exception Queue                                      | 7-12 |

| Tabl | le 7-5.  | Packet Memory Data in Big Endian 32-bit and 16-bit Modes                         | 7-13 |

| Tabl | le 7-6.  | Packet Memory Data in Little Endian 32-bit and 16-bit Modes                      | 7-13 |

| Tabl | le 7-7.  | Packet Memory 32-bit and 16-bit Data Format of CBR /Raw Cells—Big Endian Mode    | 7-15 |

| Tabl | le 7-8.  | Packet Memory 32-bit and 16-bit Data Format of CBR /Raw Cells—Little Endian Mode | 7-15 |

| Tabl | le 7-9.  | Setting the Number of VCs for SARA-R                                             | 7-18 |

| Tabl | le 7-10. | Receive Descriptor Error Status Bits                                             | 7-20 |

| Tabl | le A-1.  | SARA-R Control Memory Data Structures                                            | A-1  |

| Tabl | le A-2.  | SARA-S Control Memory Data Structures                                            | A-1  |

| Tabl | le A-3.  | SARA-R Control Memory Size Example                                               | A-2  |

| Tabl | le A-4.  | SARA-S Control Memory Size Example                                               | A-2  |

| Tabl | le D-1.  | Explanation of Symbols in the Control Memory State Diagram                       | D-1  |

| Tabl | le E-1.  | SARA-S Throughput Performance for AAL 3/4                                        |      |

| Tabl | le E-2.  | SARA-R Throughput Performance for AAL 3/4                                        |      |

xiv Edition 6

# **Preface**

#### **About This Manual**

This manual describes the characteristics of the SARA ATM interface devices together with their hardware and software features. Sufficient detail is provided to facilitate their incorporation in the design of ATM network interfaces.

In this edition of the manual (Edition 6), two functional versions of the SARA chipset are described. The original functional "A" version, which operates at a maximum clock speed of 20 MHz, was the only version described in earlier editions. This edition also describes the functional "B" version introduced in 1995, which operates at a maximum clock speed of 33 MHz. The two functional versions are very similar, and have common descriptions in this manual, except for differences in their part numbers (Section 1), DC characteristics (Section 3.4) and AC characteristics (Section 3.5).

#### Audience of This Manual

This manual is written for hardware and software engineers who design ATM (Asynchronous Transfer Mode) interface devices. Specifically, the chipset described in this manual is intended for application in ATM network interfaces for terminals, bridges, routers, workstations or PCs which may attach to an ATM network.

## **Organization of This Manual**

#### Chapter 1—Introduction

This chapter introduces the SARA devices, and describes their application in a typical network interface unit (NIU) design. The functions of the Segmentation and Reassembly SARA devices (SARA-S, TXC-05501; and SARA-R, TXC-05601) are briefly described. The segmentation and reassembly process required to achieve packet transmission across an ATM network as defined in the ANSI draft standards for B-ISDN are briefly described.

#### Chapter 2—SARA Functional Description

Chapter 2 provides an overview of the most important features and functions of the SARA chipset. The features of both the SARA-S and SARA-R chips, taken together, are summarized. The individual features of SARA-S and SARA-R are presented next, with particular attention to the interfaces between each SARA device and the packet and control memory. The data structures in the packet and control memories are outlined.

The data structures and interactions with the SARA-S rate queue structure are described in detail, together with the methods of peak and average metering and congestion control. The process of cell reassembly into packets by SARA-R is discussed. Attention is given to the exception handling for errors in the cell syntax, in the received packets, and those errors not associated with packets. The buffer recovery mechanism in SARA-R for packets that have "timed-out" is also given.

## **Chapter 3—Hardware Description**

Chapter 3 describes the SARA chipset as hardware devices. Separately for both SARA-S and SARA-R, signals are grouped according to their associated interface, categorized as input, output or both, and their functions described. For SARA-S, the interfaces are the processor, cell, control memory, packet memory, congestion control, constant bit rate and miscellaneous. For SARA-R, the same interfaces apply except for the constant bit rate.

Each interface is then described in detail. The signals are described functionally and their timing is shown with respect to each other.

Edition 6 xv

A cross reference table by pin name is given for both SARA-S and SARA-R together with pin configuration diagrams for both chips. The DC and capacitance characteristics of each chip are given. AC characteristics, including signal timings for all interfaces, are specified.

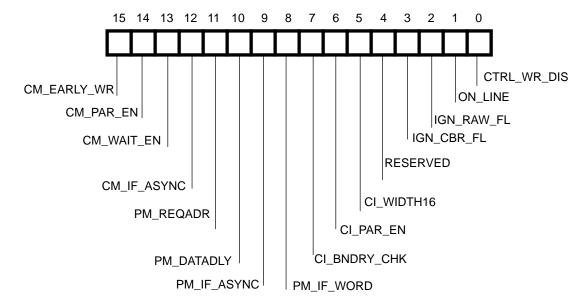

#### Chapter 4—SARA-S Register Descriptions

The SARA-S registers are described as a software reference. The register name, address, description, read/write type and reset value are provided for all the internal and diagnostic registers of each chip. A bit-by-bit description is presented for each register. Similar treatment is given for each queue.

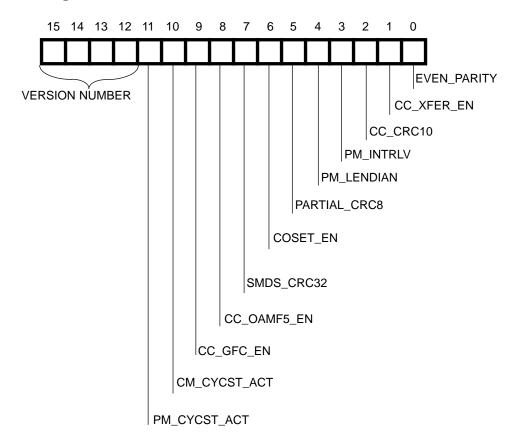

#### Chapter 5—SARA-R Register Descriptions

The SARA-R registers are described as a software reference as the SARA-S registers are described in Chapter 4.

#### Chapter 6—SARA-S Software Interfaces

The interfaces from the SARA-S to control and packet memory data structures are described in considerably greater detail than that given in Chapter 2. For SARA-S, the control memory structures include the buffer descriptor table, the VC table, the packet ready queue, and the transmit complete queue.

The packet memory structures described for SARA-S include the packet data and CBR data. Software functions are described. For SARA-S these include start-up initialization, virtual circuit setup, and transmitting a packet.

#### Chapter 7—SARA-R Software Interfaces

The SARA-R software interfaces are described as the SARA-S software interfaces are described in Chapter 6. For SARA-R, the control memory structures include the buffer descriptor table, the VP table, the reassembly table, the VC table, the small/large free descriptor queues, the packet complete queue and exception queue. The packet memory structures described for SARA-R are packet data, CBR data and raw cell data. SARA-R software functions described are start-up initialization, virtual circuit setup, and packet reception.

#### **Appendices**

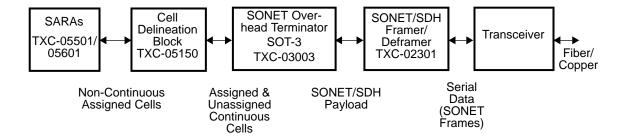

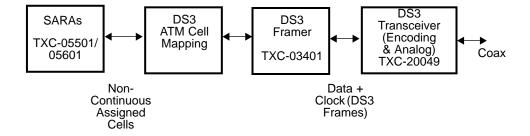

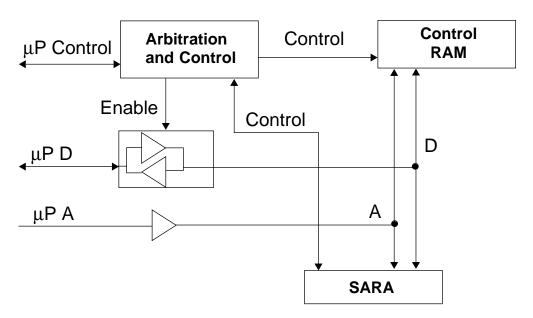

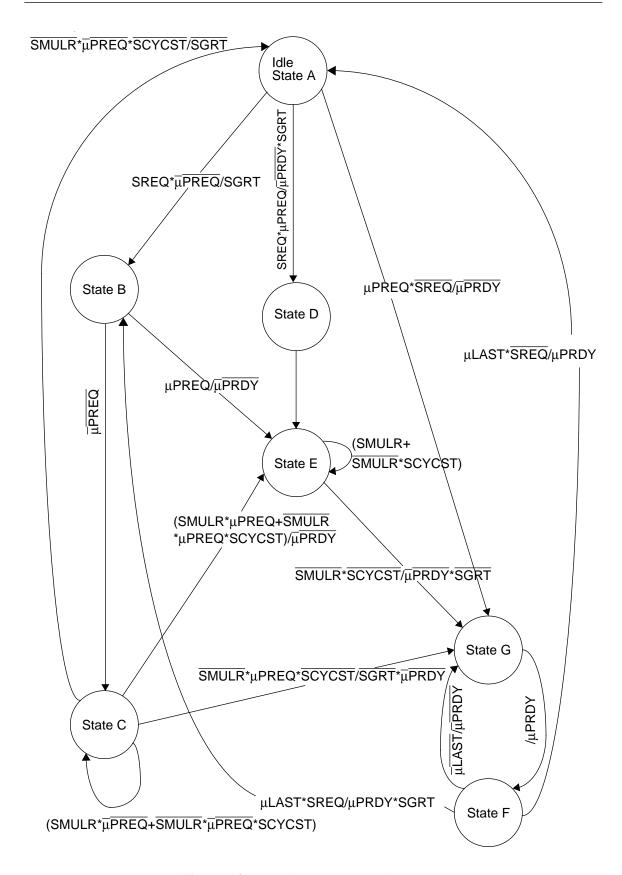

Appendix A gives control memory size examples. In Appendix B a packet memory interface example is illustrated. Link interface and application examples are given in Appendix C. Appendix D shows a specific example of the SARA and a microprocessor interface to control memory, with a description of the state machine inside the arbitration and control block. SARA performance examples are given in Appendix E. Appendix F discusses congestion control in SARA. SARA Time-Out Operation is presented in Appendix G. The SARA Chipset Deviation List is presented in Appendix H.

#### **Standards Documentation Sources**

The addresses and telephone/fax numbers of the international organizations that publish telecommunication technical standards and reference documentation are listed.

#### **List of Technical Manual Changes**

This list of technical manual changes is a comprehensive list of all significant changes made since the last published edition of the SARA Manual.

#### Glossary

A glossary of ATM, data communications, and networking terms is given.

xvi Edition 6

# **Chapter 1. Introduction**

In this edition of the manual (Edition 6), two functional versions of the SARA chipset are described. The original functional "A" version, which operates at a maximum clock speed of 20 MHz, was the only version described in earlier editions. This edition also describes the functional "B" version introduced in 1995, which operates 65% faster at a maximum clock speed of 33 MHz, and consumes 30% less power, while retaining form, fit and function compatibility with the functional "A" version. The two functional versions are very similar, and have common descriptions in this manual, except for differences in their part numbers (described below), DC characteristics (Section 3.4) and AC characteristics (Section 3.5).

The part numbers which may be used for ordering SARA chipset devices are as follows:

|        | Functional "A" Parts | Functional "B" Parts |

|--------|----------------------|----------------------|

| SARA-S | TXC-05501-ACPQ       | TXC-05501-BCPQ       |

| SARA-R | TXC-05601-ACPQ       | TXC-05601-BCPQ       |

The two-chip SARA chipset provides a powerful and easy-to-use interface between packet-oriented equipment and ATM networks. SARA simplifies the design of high performance interfaces for computers, workstations, bridges, routers, etc.—conveniently providing segmentation and reassembly functions in compliance with both the T1S1.5 ATM Adaptation Layer Type 3/4 and Type 5 Common Part draft standards \*,†. Most overhead functions associated with conversion to and from cells are provided with a high-performance, low-overhead ATM interface. This includes packet queueing, buffer management and DMA, CRC generation and checking, and those Asynchronous Transfer Mode (ATM) network-specific functions required to segment and reassemble cells over the attached network link. SARA supports the T1S1.5 ATM Adaptation Layer (AAL) Type 3/4 and Type 5 Common Parts, including the Common Part Convergence Sublayer (CPCS) and the Segmentation and Reassembly Sublayer (SAR). The SARA chipset can reassemble frames from an input stream of cells that originates from many interleaved frames.

SARA also supports some ATM layer functions, as described later in this chapter. ATM cells consist of a five-byte header and a 48-byte payload (53 bytes total).

The SARA chipset is designed to provide routers, bridges, computers, front-end processors and workstations with a high performance chipset to interface with an ATM network. Hardware support for the functions of frame-to-cell segmentation and reassembly in accordance with the requirements of Broadband ISDN (B-ISDN) and Switched Multi-Megabit Data Service (SMDS) are provided. SARA supports up to a maximum of 65,536 virtual circuits. Up to 8,191 virtual circuits may have packets queued for segmentation, with an equal number being concurrently reassembled. A throughput rate of at least 150 Mbps in each direction may be achieved (suitable for SONET STS-3).

In segmentation, the chipset receives both a packet and a corresponding packet descriptor. The packet is segmented into cells. The appropriate ATM cell header is added to each cell, and the cells are sent out on the transmission line interface.

In reassembly, the device receives a multiplexed cell stream from the transmission line interface. ATM layer operations and maintenance (OAM) cells are filtered out of the incoming cell stream. The incoming cell stream is then demultiplexed into its component streams using the virtual channel identifier (VCI) and the message identification (MID) field (AAL 3/4 only), or the virtual path identifier (VPI) and the VCI, to form the reassembly identifier. The cells in

Edition 6

<sup>\*.</sup> T1S1.5/92-003R2 "Broadband ISDN—ATM Adaptation Layer 3/4 Common Part Functionality and Specification" May 1992.

<sup>†.</sup> T1S1.5/92-010 "Broadband ISDN—ATM Adaptation Layer 5 Common Part Functionality and Specification" May 1992.

each component stream are reassembled into frames using the ATM adaptation layer information fields. The AAL and ATM headers are removed and the completed frames queued for software processing.

Constant Bit Rate (CBR) traffic can also be accommodated by the SARA chipset. The SARA-S can add headers to an external queue of CBR payload cells and multiplex them with the Variable Bit Rate (VBR) cell stream using an interrupt-like mechanism. The SARA-R demultiplexes incoming CBR cells and stores them in an external CBR cell queue.

Both SARA chips are packaged in a 208-pin EIA-J Plastic Quad Flat Package (PQFP). They are both fabricated with one micron CMOS technology.

# 1.1 Overall Operation

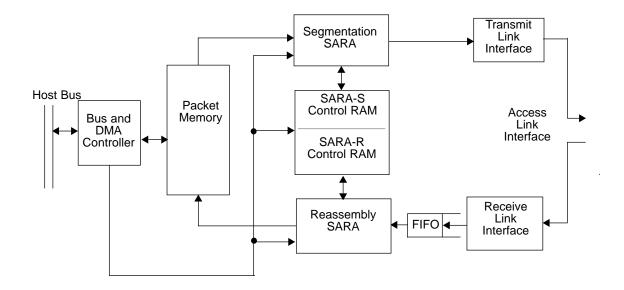

Figure 1-1 shows an example of an ATM Network Interface Unit (NIU) implementation using SARA segmentation and reassembly devices (SARA-S and SARA-R). In some applications, a local processor may be included (not shown in Figure 1-1). If the application performance is not too demanding, the control RAM and packet memory can be externally combined into a single memory.

Data packets are queued, segmented, and reassembled in the packet memory. Buffer descriptors, virtual circuit parameters, and SARA operating variables are all stored in tables that reside in the control RAM. The processor-to-SARA communication queues also reside in the control RAM. The control RAM can be separated into two control RAMs (one RAM for segmentation and one for reassembly) externally, depending on the application performance requirements.

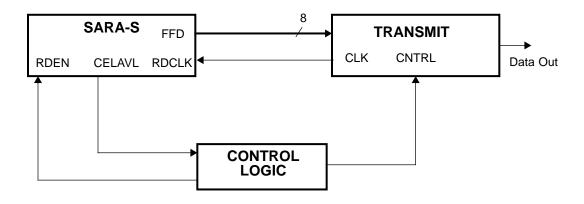

Figure 1-1. Typical ATM Network Interface Unit Implementation

A DMA controller places packets received across the host bus into buffers in the packet memory. The software informs SARA of the packet's location. The packet is then segmented into cells, and the cells are multiplexed with cells from other packets that are undergoing segmentation. Each cell carries the appropriate header information together with the adaptation layer fields according to the B-ISDN ATM Adaptation Layer protocol in the 48-byte cell payload. Up to eight peak emission rates (the inter-cell gap on each virtual circuit) may be programmed. Using a leaky bucket algorithm, the average cell emission rate can likewise be programmed for each virtual circuit. When segmentation is completed the packet buffer is returned to the software.

1-2 Edition 6

The reassembly device (SARA-R) reassembles an incoming multiplexed stream of ATM cells into packets using the virtual channel identifier (VCI) and the message identification (MID) field (AAL 3/4 only), or the virtual path identifier (VPI) and the VCI, to form the reassembly identifier. When a cell containing the beginning of a new packet is received, SARA-R fetches a buffer and DMAs the cell into it. Subsequent cells from the same packet are accumulated in the buffer. When a cell indicating the end of the packet is received, it is stored in the buffer, and the processor is informed. All of the adaptation layer fields are processed within the chip with all error conditions being monitored and reported.

After a packet is queued for segmentation, processor intervention is not required until the empty buffer is returned after the packet is sent. Similarly, there is no processor intervention on the reassembly side until a packet is completely received and checked for errors. There is no cell-level interaction with the processor; all processor interactions are at the packet level.

The SARA-S and SARA-R support network congestion control by means of backward explicit congestion notification. If congestion is detected in the network, notification cells may be returned by the network to all sources currently transmitting over the congested path. The SARA-R passes control information to the SARA-S for every congestion notification cell it receives. On receiving a congestion notification cell, the SARA-S will throttle the peak rate of the appropriate virtual circuit. Subsequent congestion notification cells that are received for the same virtual circuit will actuate further throttling. After a programmable time interval, the transmission rate will be gradually restored, provided no further congestion notification cells have been received for that virtual circuit.

# 1.2 ATM Adaptation Layer

The SARA chipset has been designed to support the segmentation and reassembly functions required to achieve packet transmission across an ATM network (or an SMDS network). In this and the following section these functions, as defined in the ANSI draft standards for B-ISDN, are briefly reviewed.

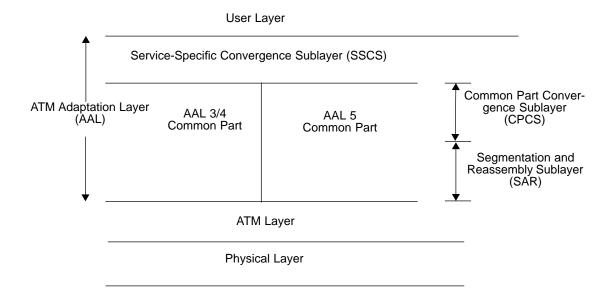

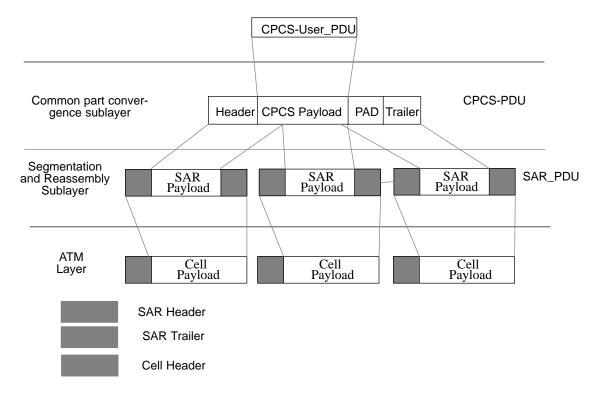

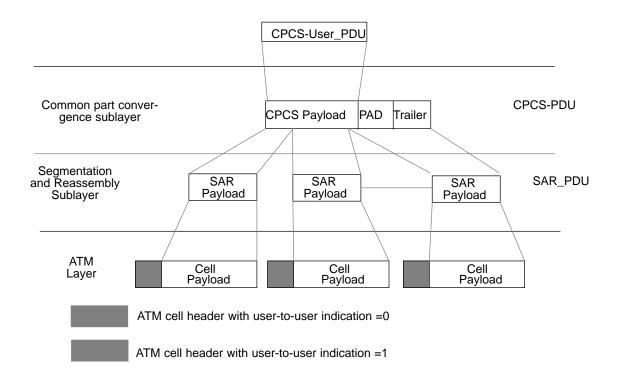

The protocol model for the variable bit rate (i.e. packet based) ATM Adaptation Layer (AAL) Type 3/4 and Type 5 as defined in the ANSI draft standards \*,† is illustrated in Figure 1-2. The AAL is split into three sublayers. The service specific convergence sublayer (SSCS) is used to add additional service features such as assured transfer (error correction by retransmission). It may be a null sublayer for unassured transfer (error detection but no correction). The Common Part Convergence Sublayer (CPCS) performs error detection and control functions at the frame level. The Segmentation and Reassembly Sublayer (SAR) performs the functions necessary to segment frames into ATM cells and reassemble a multiplexed stream of ATM cells back into their original frames. Two AAL types have been specified to implement the functions of the CPCS and SAR sublayers: AAL 3/4 common part and AAL 5 common part. The SARA chipset supports the functions of the CPCS and the SAR sublayers for both AAL 3/4 common part and AAL 5 common part, and some functions of the ATM layer.

Edition 6

-

<sup>\*.</sup> T1S1.5/92-003R2 "Broadband ISDN—ATM Adaptation Layer 3/4 Common Part Functionality and Specification" May 1992.

<sup>†.</sup> T1S1.5/92-010 "Broadband ISDN—ATM Adaptation Layer 5 Common Part Functionality and Specification" May 1992.

**Figure 1-2**. Protocol Model for Variable Bit Rate AAL Type 3/4 and Type 5

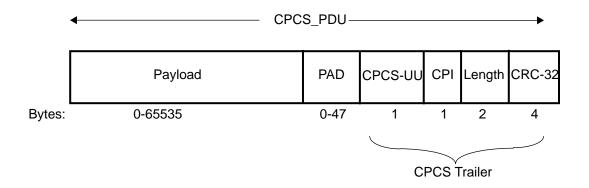

## 1.2.1 AAL 3/4

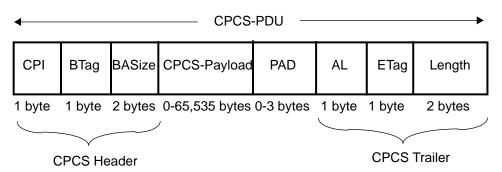

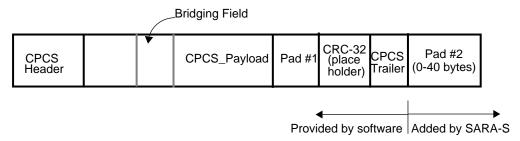

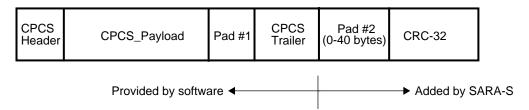

The structure of the CPCS-PDU for AAL3/4 is shown in Figure 1-3. This packet structure is accepted for transmission by the SARA-S and delivered by the SARA-R. The CPI field and the AL field are not used by the SARA. The BTag and ETag are used to check for certain reassembly errors. They should both contain the same eight-bit value but are not modified or checked by the SARA. The BASize field is used by the SARA-R to indicate the minimum buffer size (in bytes) that can contain the CPCS-Payload and PAD. The length field indicates the length of the payload but is not used by the SARA. The CPCS-Payload is a variable length field containing 0-65,535 bytes of CPCS-user information. A PAD field of 0 to 3 bytes is present to align the CPCS-PDU to a four-byte boundary.

Figure 1-3. Structure of the AAL 3/4 CPCS-PDU

The SARA can optionally insert and check the CRC-32 field as shown in Figure 1-4 and Figure 1-5. For the 802.6 frame, the CRC-32 is computed on the CPCS\_Payload and the pad field. The bridging field (the last two bytes of the 20-byte header in the CPCS\_Payload) is considered to be zero for the CRC computation.

1-4 Edition 6

**Figure 1-4**. CRC-32 in an 802.6 Frame

The CRC\_32 can optionally be computed over the entire CS\_PDU and inserted at the end of the last cell as shown in Figure 1-5.

Figure 1-5. TranSwitch Proprietary CRC-32

The CRC-32 computation is the same as in the ANSI FDDI, 802.5, and ANSI fiber channel standards.

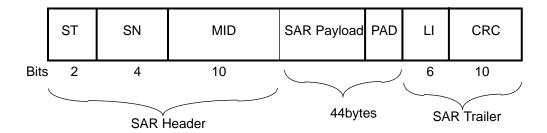

The segmentation process for AAL 3/4 is illustrated in Figure 1-6. The CPCS-PDU is segmented into 44-byte segments. Each segment forms the payload of an SAR-PDU. A two-byte SAR header and a two-byte SAR trailer are added to each segment to form the SAR-PDU. Each SAR-PDU then forms the 48-byte payload of an ATM cell. Each ATM cell has a five-byte cell header.

**Figure 1-6**. The Segmentation Process for AAL 3/4

Edition 6 1-5

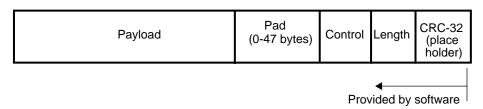

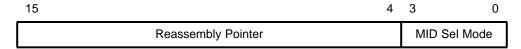

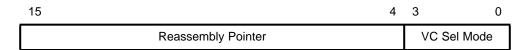

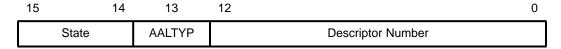

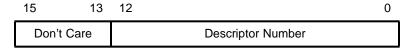

The structure of the SAR-PDU for AAL 3/4 is shown in Figure 1-7. The segment type (ST) field indicates whether the cell is a beginning of message (BOM), continuation of message (COM), or end of message (EOM) cell, or whether it contains a complete CPCS-PDU (SSM). The sequence number (SN) is incremented modulo-16 for each successive SAR-PDU on the same virtual connection (regardless of packet boundaries). The message identification (MID) field has the same value for all SAR-PDUs derived from the same CPCS-PDU. It may be used to form part of the reassembly identifier to demultiplex and reassemble cells from multiple interleaved packets. The length indicator (LI) gives the length of the SAR-PDU payload in bytes. The CRC is a cyclic redundancy check computed over the entire SAR-PDU and is used for error detection. All of the above fields of the SAR-PDU are set, checked and handled by the SARA, according to the ANSI draft standard\*, without any requirement for per cell user interaction.

Figure 1-7. Structure of the AAL 3/4 SAR\_PDU

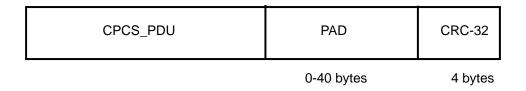

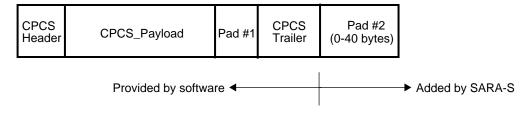

#### 1.2.2 AAL 5

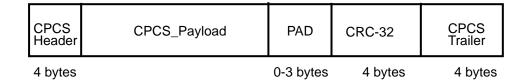

The structure of the CPCS\_PDU for AAL 5 is shown in Figure 1-8. This packet structure is accepted for transmission by the SARA-S and delivered by the SARA-R. The CPCS-payload is a variable length field containing 0 - 65,535 bytes of CPCS-user information. The PAD field is used to align the CPCS-PDU to a 48-byte boundary. The PAD field may contain any value, and it is included in the CRC-32 calculation. The control field is reserved for future use. The length field indicates the length in bytes of the payload field.

The CRC-32 field contains the result of the CRC-32 calculation performed over the entire CPCS-PDU as specified in the ANSI draft standard.  $^{\dagger}$  (This CRC-32 computation is the same as in the ANSI FDDI, IEEE 802.5, and the ANSI Fiber Channel standards.) The CRC-32 computation is optionally performed by the SARA-S and checked by the SARA-R.

1-6 Edition 6

<sup>\*.</sup> T1S1.5/92-003R2 "Broadband ISDN—ATM Adaptation Layer 3/4 Common Part Functionality and Specification" May 1992.

<sup>†.</sup> T1S1.5/92-010 "Broadband ISDN—ATM Adaptation Layer 5 Common Part Functionality and Specification" May 1992.

**Figure 1-8**. Structure of the AAL 5 CPCS\_PDU

The segmentation process for AAL 5 is illustrated in Figure 1-9.

**Figure 1-9**. Segmentation Process for AAL 5

The CPCS\_PDU is segmented into 48-byte segments, with each segment forming a SAR\_-PDU. No SAR\_PDUs are partially filled, since the CPCS\_PDU is aligned to a 48 byte boundary. There is no SAR header or trailer on the SAR\_PDU. Each SAR\_PDU forms the 48-byte payload of an ATM cell.

Each ATM cell has a five-byte cell header. An ATM-user-to-user indication is available in the payload type field of the ATM cell header. AAL 5 uses an ATM user-to-user indication of "1" to indicate the last SAR\_PDU of a CPCS\_PDU. All other SAR\_PDUs are carried in ATM cells

Edition 6

with an ATM user-to-user indication of '0'. The SARA-R can reassemble ATM cells carrying AAL 5 SAR\_PDUs into AAL 5 CPCS\_PDUs without any requirement for per-cell user interaction. All possible reassembly errors are checked and reported by the SARA-R.

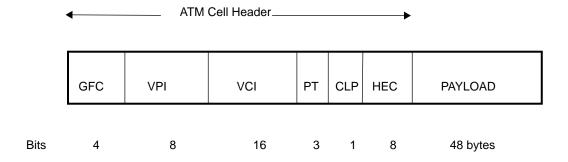

## 1.3 The ATM Layer

The format of the ATM cell at the user network interface (UNI) of an ATM network as defined by the CCITT for the broadband ISDN\* is shown in Figure 1-10. The generic flow control (GFC) field is used to ensure fair and efficient access between multiple devices sharing a single UNI. A label space of 24 bits is provided, divided into two fields: an eight-bit virtual path identifier (VPI), and a 16-bit virtual channel identifier (VCI)†. The VPI allows a group of virtual connections, called a virtual path, to be identified and the VCI identifies the individual virtual connections within each virtual path. The payload type (PT) field is used to distinguish user information and network information. For user information cells, the payload type field carries a single bit ATM user-to-user identification. ATM cells with a payload type field that indicates network information may be inserted by the SARA-S and filtered out by the SARA-R. The cell loss priority (CLP) bit permits two priorities of cell to be defined where the network may discard low priority cells under congestion conditions. The header error check (HEC) field provides an eight-bit cyclic redundancy check on the contents of the cell header.

The SARA-S maintains a connection table with a copy of the four ATM cell header bytes for each virtual connection (the HEC field is computed for each cell and therefore is not stored in the connection table). The SARA-S can thus insert any pattern of bits into the cell header, and may therefore originate cells with any VPI or VCI. The SARA-R performs cell to packet reassembly using up to 16 bits from the VCI field optionally combined with up to ten bits from the MID field of the SAR\_PDU, or eight bits from the VPI field combined with up to ten bits from the VCI field.

Figure 1-10. Structure of an ATM Cell at the User Network Interface

1-8 Edition 6

<sup>\*.</sup> CCITT Recommendations I.150, I.361 (Geneva, June 1992).

<sup>†.</sup> Within the telecommunications industry, the terms "virtual connection", "virtual channel", and "virtual circuit" tend to be used as synonyms. In this document the more general term "virtual circuit" has been adopted.

# **Chapter 2. SARA Functional Description**

This chapter highlights the main features of the SARA chipset. The SARA data structures and operation are also described briefly.

# 2.1 Major SARA Features

The major features of the SARA chipset are as follows:

- Support for B-ISDN standard ATM Adaptation Layer (AAL) 3/4 and AAL 5 Common Parts.

- Selectable packet-level CRC generation and checking on a per connection basis.

- B-ISDN cell payload CRC generation and checking (AAL 3/4).

- B-ISDN cell header CRC generation and checking (with no correction).

- Programmable support of between 512 to 65,536 virtual circuits.

- Support of up to 8,191 buffers in each direction, for simultaneous segmentation and reassembly of up to 16,382 packets.

- Management of constant bit rate traffic.

- Management of OAM cells.

- Management of host interface queues.

- Availability of either synchronous or asynchronous memory interface handshake modes.

- Selectable 16- or 32-bit packet memory interface width.

- 16-bit control memory interface.

- DMA controllers for packet and control memory.

- Simultaneous support for CBR, AAL 3/4, and AAL 5 traffic.

- Selectable eight-bit or 16-bit network cell interface width.

- Optional parity checking on control memory, packet memory and cell interfaces on an individual basis.

- Peak rate metering of cells for each virtual circuit with up to eight programmable peak rates.

- Average metering of cells on each virtual circuit.

- Queueing of multiple frames for each virtual circuit.

- Automatic throttling of virtual circuits upon receipt of backward congestion notification.

- Reassembly of 53-byte cells into packets in programmable-size large or small buffers (AAL 3/4).

- Automatic packet aging and buffer recovery using a packet timeout counter.

- Management of cell and packet exceptions.

# 2.2 Segmentation SARA Data Structures

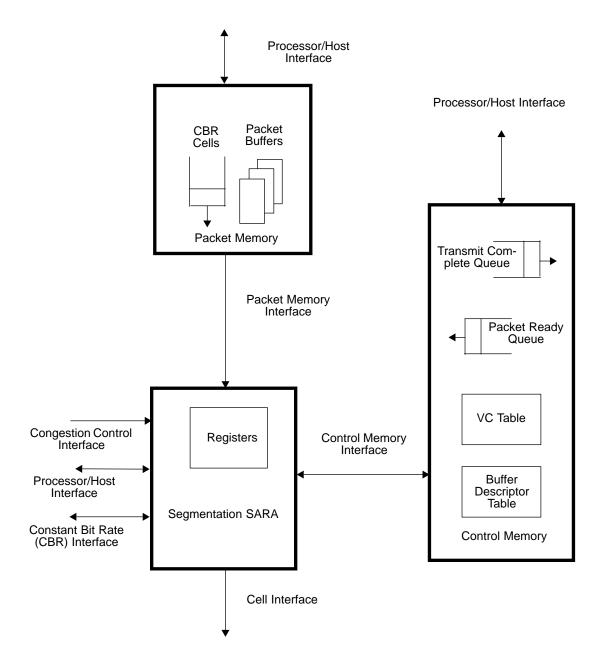

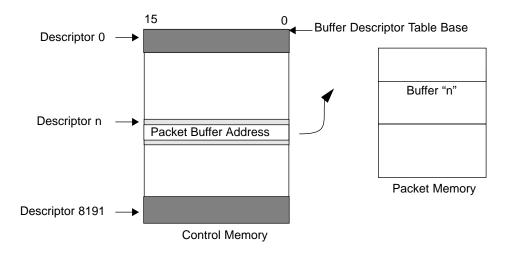

Figure 2-1 shows the basic data structures for the Segmentation SARA (SARA-S).

The data structures contained in packet memory are the packet buffers and optionally the constant bit rate (CBR) traffic queue. These data structures contain the data to be transmitted. The packet memory is accessed through the packet memory interface.

The data structures in control memory are the buffer descriptor table, the virtual circuit table and the communication queues. These data structures contain the overhead information and other segmentation variables. The control memory is accessed through the control memory interface.

Edition 6 2-1

Figure 2-1. Segmentation SARA Data Structures

The internal registers in SARA-S determine the device operation modes. They also contain the base addresses of the buffer descriptor, the virtual circuit tables, the various addresses associated with the communication queues, and the rate queue registers that determine the peak segmentation rate of each rate queue. These registers are accessed using the processor interface.

The packet buffers, the CBR queue, the buffer descriptor table, the virtual circuit (VC) table and the two communication queues - packet ready queue and transmit complete queue - constitute the basic SARA-S data structure elements.

2-2 Edition 6

Each packet buffer contains either a packet ready to be segmented or one being segmented. The CBR traffic is passed to SARA-S through a FIFO whose address is mapped into the packet memory address space.

The buffer descriptor table contains packet-specific information for each packet to be segmented. Each table entry includes the virtual circuit identifier (VCI) associated with the packet, the length of the packet to be segmented, the location of the buffer in the packet memory and other temporary variables. SARA-S supports up to 8,191 descriptors, all of which can be active simultaneously for segmenting packets on different virtual circuits.

The virtual circuit (VC) table contains the ATM header information, congestion control information, and the peak and average rate metering information associated with each virtual circuit. SARA-S supports between 512 and 65,536 virtual circuit entries in the VC table. The table entries are setup by software as virtual circuits are established.

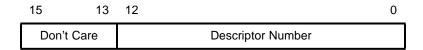

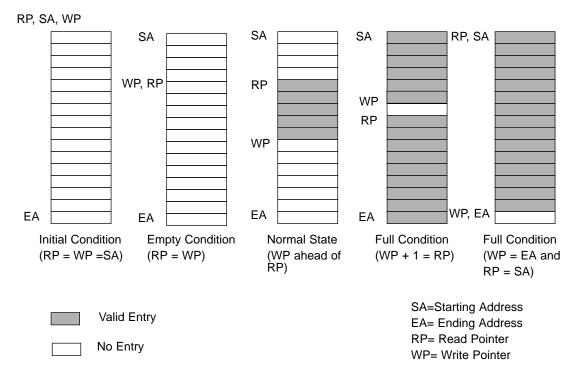

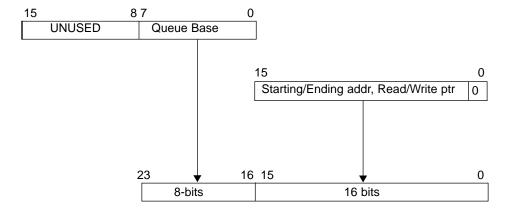

The communication queues—the packet ready queue and the transmit complete queue—are used to pass descriptor numbers between SARA-S and the processor. The queue locations are specified by the common queue base address along with the respective start and end addresses.

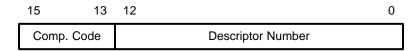

The packet ready queue contains descriptor numbers of those buffer descriptors that are ready to be linked for segmentation by SARA-S. The transmit complete queue contains descriptor numbers and completion codes for buffer descriptors that have been segmented and delinked by SARA-S.

## 2.3 SARA-S Operation

Packets to be segmented by SARA-S are placed in a packet buffer associated with a free buffer descriptor by the processor. The packet segmentation process is then initiated by writing the buffer descriptor number into the packet ready queue. SARA-S then reads the descriptor number from the packet ready queue and links the descriptor to one of the eight internal rate queues as specified by the rate queue field in the corresponding VC table. Upon linking, the segmentation of the packet occurs based on the parameters in the buffer descriptor table and its VC table. SARA-S accesses these packets in memory through the packet memory interface to segment them into 44/48-byte ATM cell payloads. As a packet is segmented into cells, the ATM header, checksum and the ATM adaptation layer header (for AAL 3/4) information is added to the front of each cell. The ATM adaptation layer trailer (for AAL 3/4) is appended to the end of the cells as they are transferred to the link via the cell interface.

The packet segmentation rate is determined by the rate queue parameters programmed into the SARA-S rate queue registers and the average rate metering parameters in the VC table. If SARA-S is notified of congestion in the path, the segmentation rate is throttled on specific virtual circuits. SARA-S is notified of congestion through the congestion control interface used by SARA-R to transfer the congestion control information.

SARA-S also reacts to flow control signals (XON/XOFF) intelligently. Packet segmentation on programmed rate queues will be suspended on receipt of an external XOFF condition. The transfer of constant bit rate traffic can also be suspended during XOFF by setting a bit in a programmable register. Normal segmentation will resume after the XOFF condition goes away.

The interfaces and programming details are described in greater detail in subsequent chapters.

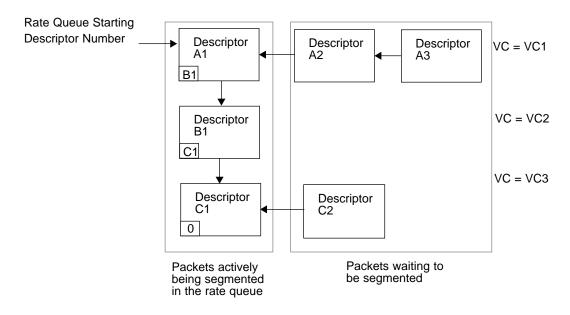

## 2.3.1 SARA-S Rate Queues

Every virtual circuit is associated with a rate queue that determines the peak rate at which the frames are segmented. There are eight rate queues, which are organized into two banks of four rate queues each. These are designated as high priority bank A and low priority bank B. Each rate queue has a rate queue register that sets the rate queue characteristics. The rate queues and registers are discussed further in Chapter 4.

Edition 6 2-3

Rate queues within each bank are serviced in a sequential or "round robin" manner. The value programmed into the rate queue register determines the peak rate at which the rate queue is serviced. The rate queue data structure is two-dimensional. All descriptors associated with the same VC are linked horizontally, one behind the other. All descriptors associated with different virtual circuits (VCs) are linked one above the other, or vertically. When the rate queue is serviced, one cell from each descriptor (packet) in the vertical chain is transferred to the link interface. With this scheme, packets to different virtual circuits on the same rate queue are segmented by one cell every time the rate queue is serviced. Correspondingly, every packet on the same virtual circuit is completely segmented before segmentation of the next packet is commenced, maintaining an ordered segmentation of packets on the same virtual circuit.

Figure 2-2 shows a rate queue data structure with descriptors linked to three different virtual circuits. Buffer descriptors A1, A2 and A3 are associated with virtual circuit VC1; B1 is associated with virtual circuit VC2; C1 and C2 are associated with virtual circuit VC3. Every time the rate queue is serviced, one cell from each VC is transferred to the link interface. In this case, one cell from the packet indicated by descriptor A1, one cell from B1 and one cell from C1 are transferred. When A1 is completely transferred, it is delinked and A2 takes its place. Likewise C2 takes the place of C1 when C1 is completely segmented and delinked from the rate queue. Meanwhile if a new descriptor C3 (not shown) on virtual circuit VC3 is queued, it will be linked after C2 so that segmentation of C3 will begin only after segmentation of C2 has completed.

Figure 2-2. Typical Rate Queue Data Structure

## 2.3.2 Peak and Average Metering

A number of virtual circuits emanate from a particular source. Each virtual circuit can be allocated a peak rate—the maximum rate at which cells will be transmitted on that circuit when there is traffic to send. For some network applications, the peak rate must be controllable in order to both avoid congestion in the network and to avoid too many cells being transmitted beyond the receiver's capability. To smooth the traffic, the SARA chipset allows peak rates to be defined associated with the eight rate queues. Any virtual circuit can be a member of any one of those rate queues. If the sum of the active rate queues exceeds the transmission bandwidth available, only the higher priority queues will be served. Peak rates define the time between emission of cells on a virtual circuit. The peak rate is determined by the value programmed in the rate queue registers.

2-4 Edition 6

The traffic on each virtual circuit will be bursty, i.e. there will be times when there is no traffic to send. Average metering smooths traffic to avoid congestion, assists in statistical multiplexing, and places an upper bound on the average amount of traffic carried across each virtual circuit. Average metering may be disabled on any virtual circuit, which causes the cells to be transmitted at the peak rate.

The mechanism used to perform average metering is a "leaky bucket" algorithm. For each virtual circuit, credits accumulate up to a pre-programmed maximum value at the average cell transmission rate. Each time a cell is sent, a credit is removed until the packet(s) are segmented or no credits are left. If credit is exhausted, it is replenished at the rate of the average transmission; cells are sent at this rate if data is available to send. As long as credits exist, cells are sent at the peak rate.

If there has been a gap in the data to send, credits will accumulate up to the maximum. The maximum credit thus determines the maximum burst length. As long as each VC stays within the designated average, cells are transferred at the peak rate (which is also the burst rate). When a burst of transmitted cells on a VC exceeds the burst length specified for that VC, the VC is considered oversubscribed forcing the cells to be segmented and transferred at the average rate. Refer to Chapter 6 for more details.

## 2.3.3 Congestion Control

Some networks may provide a *backward explicit congestion notification* scheme for congestion control. When congestion is experienced in the network, the network may issue congestion notification cells. When SARA-R receives a congestion notification cell, it passes the congestion information to the SARA-S which will automatically throttle the specified virtual circuit. The SARA-R may also pass these cells to the packet memory so that the processor/host can process them if needed. The interface between SARA-R and SARA-S is the serial congestion control interface.

The congestion notification cell contains explicit information which indicates the type of congestion. SARA-S recognizes two types of congestion information: moderate and extreme.

When moderate congestion notification is received on a virtual circuit, SARA-S throttles the segmentation peak rate on that virtual circuit by one "notch." Each notch reduces the peak rate on the circuit by one half of the rate of the previous notch. The fifth notch stops segmentation on the VC. When no congestion notification cells arrive for a throttled VC during a timeout period, the SARA-S will increase the segmentation peak rate to the previous notch. If no further congestion cells are received, this process will continue until the VC is operating at its programmed full peak rate. The VC mode bits in the SARA-S VC Table (Chapter 6) define the timeout period.

When extreme congestion information is received, SARA-S stops segmenting and transmitting additional cells on that particular VC (drops down to the fifth notch) and ramps back up as described above.

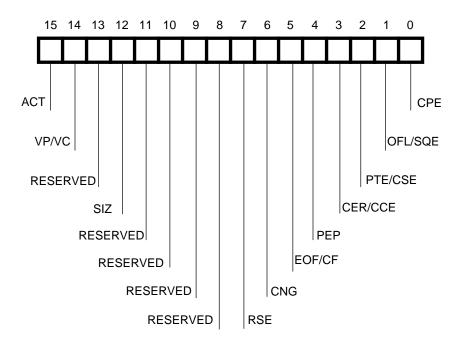

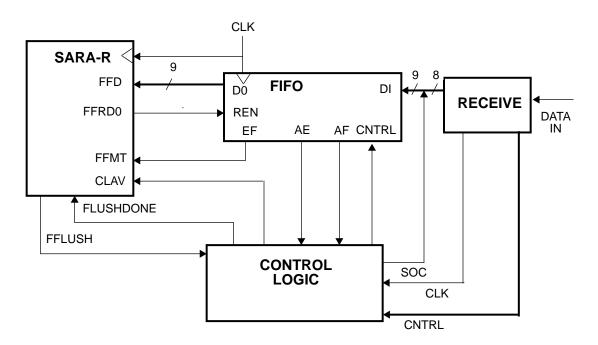

# 2.4 Reassembly SARA Data Structures

Figure 2-3 shows the basic data structures for the Reassembly SARA (SARA-R).

The packet memory contains packet buffers, the raw cells, and, optionally, a constant bit rate (CBR) traffic queue. These data structures contain the data that has been received. The packet memory is accessed through the packet memory interface.