Le9500

# High-Voltage Ringing SLIC Device for VolP Applications VE950 Series

### **APPLICATIONS**

- Interface to *Broadcom*:

- BCM3367/3368 cable modem

- BCM3341/3351/3352 cable modem

- BCM6352 integrated multimedia adaptor

- BCM1101 residential gateway

- Cable modems

- Voice over Internet Protocol (VoIP)

- Voice over DSL

- Remote subscriber units

- Broadband wireless

- Short-loop access

## **FEATURES**

- Differential ringing and codec interface

- Single-ended application also supported

- On-board ringing generation

- 15 to 70 Hz ring frequency supported

- Three ringing options:

- Sine wave input sine wave output

- PWM input sine wave output

- Square wave input trapezoidal output

- Flexible power supply options:

- VBAT2 for active talking

- VBAT1 for ringing, scan, and so on

- 3.3 V for Vcc

- Battery switch to minimize off-hook power

#### Eight operating states:

- Scan

- Forward and reverse battery active

- Forward and reverse battery on-hook transmission

- Ground start

- Ring

- Disconnect

- Ultra-low on-hook power:

- 29 mW scan state

- 38 mW active state

- Loop start, ring trip, and ground start detection

- Fixed off hook threshold with hysteresis

- Fixed ground start threshold with hysteresis

- Fixed ring-trip threshold as a function of battery voltage

- Software-controllable dual-current limit option

- 25 mA or 40mA via ground or open control input

- UL1950 Compatible

- When not in ringing, |VTIP| and |VRING| are clamped to be less than 56.5 V

- Thermal shutdown protection with hysteresis

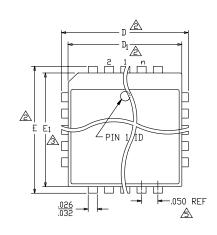

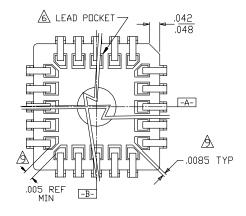

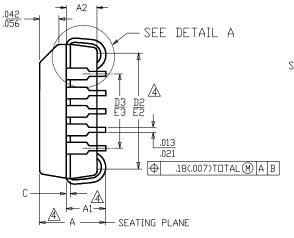

- 28-pin PLCC package

- HV7 Technology

## **ORDERING INFORMATION**

| Device     | Package Type <sup>1</sup>                                  | Packing <sup>2</sup> |

|------------|------------------------------------------------------------|----------------------|

| Le9500ABJC | 28-Pin PLCC, -75V (Green)                                  |                      |

| Le9500BBJC | 28-Pin PLCC, -85V (Green)                                  |                      |

| Le9500CBJC | 28-Pin PLCC, -100V (Green)                                 | Tube                 |

| Le9500DBJC | 28-Pin PLCC, -100V<br>operation / -145V ringing<br>(Green) |                      |

1. The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

2. For delivery using a tape and reel packing system, add a "T" suffix to the OPN (Ordering Part Number) when placing an order.

## DESCRIPTION

The Legerity Le9500 device, part of the VE950 series, is a subscriber line interface circuit (SLIC) that is optimized for short-loop, power-sensitive applications. This device provides the complete set of line interface functionality (including power ringing) needed to interface to a subscriber loop while providing ultra low power dissipation. The Le9500 SLIC device is capable of operating with a Vcc supply of 3.3 V, and is designed to minimize external components required at all device interfaces. The differential ringing and receive inputs make the device ideal for direct interface to Data Over Cable Service Interface Specification (DOCSIS) compliant cable modem gateways, to multimedia adaptors, and to residential gateway products, such as the Broadcom® BCM3367/3368, BCM3341/3351/3352, BCM6353, BCM1101 and equivalent products.

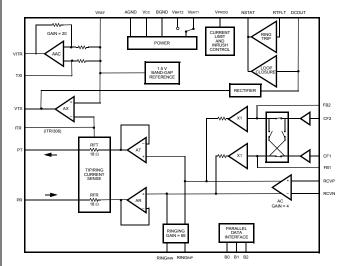

## **BLOCK DIAGRAM**

Document ID#

081189

Date:

Oct 12, 2006

Rev:

G

Version:

1

Distribution:

Public Document

1

Legerity

# TABLE OF CONTENTS

| Applications1               |

|-----------------------------|

| Features                    |

| Ordering Information        |

| Description1                |

| Block Diagram               |

| Table of Contents           |

| Product Description         |

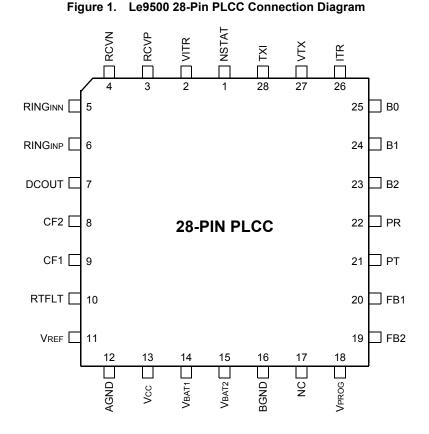

| Connection Diagram          |

| Pin Descriptions            |

| Absolute Maximum Ratings    |

| Operating Ranges            |

| Electrical Characteristics  |

| Supply Currents             |

| Power Dissipation           |

| Line Characteristics        |

| Operating States            |

| Operating State Definitions |

| Test Circuit                |

| Applications                |

| DC Loop Current Limit       |

| Overhead Voltage            |

| DC Loop Range               |

| Battery Reversal Rate       |

| Supervision                 |

| Power Ring                  |

| Design Examples             |

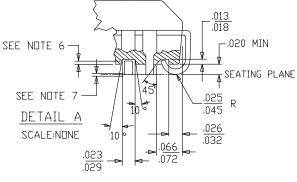

| Physical Dimensions         |

| Revision History            |

| Revision A1 to B1           |

| Revision B1 to C1           |

| Revision C1 to D1           |

| Revision D1 to E1           |

| Revision E1 to F1           |

| Revision F1 to F2           |

| Revision F2 to G1           |

### PRODUCT DESCRIPTION

The Le9500 device is optimized to provide battery feed, ringing, and supervision on short Plain Old Telephone Service (POTS) loops. This device provides power ringing to the subscriber loop through amplification of a low-voltage input. It also provides forward and reverse battery feed states, on-hook transmission, a low-power scan state, ground start (tip open), and a forward disconnect state.

The Le9500 device requires a 3.3V Vcc and battery to operate eight operating states. A battery switch is included to allow for use of a lower-voltage battery in the off-hook condition, thus minimizing short-loop off-hook power.

The following two batteries are used:

1. A high-voltage operation and ringing battery (VBAT1):

VBAT1 is used for scan, on-hook transmission, ground start, and power ringing. It can be a maximum of –75 V for Le9500A, –85 V for Le9500B, or –100V for Le9500C and Le9500D.

For Le9500D during ringing only this voltage may be extended to -145 V. The supply has to be externally adjustable. It has to be adjusted back to no more than -100 V for other operation states. Further, when -145 V is used for ringing special care should be applied to prevent certain faults from happening such as tip to ring, tip or ring to ground.

2. A lower-voltage talk battery (VBAT2):

VBAT2 is used for active state powering.

Loop closure, ring trip, and ground start detection is available. The loop closure detector has fixed threshold with hysteresis. The ring trip detector requires a single-pole filter, thus minimizing external components required. The ring trip threshold at a given battery voltage is fixed and with hysteresis. Ground start detection also has fixed threshold with hysteresis.

The DC current limit is set and fixed by a logic-controllable pin. Ground or open applied to this pin sets the current limit at the low or high value.

This device is designed for ultra-low power in all operating states.

Forward and reverse battery active states are used for off-hook conditions. Since this device is designed for short-loop applications, the lower-voltage VBAT2 is applied during the forward and reverse active states. Battery reversal is quiet, without breaking the AC path. Rate of battery reversal may be ramped to control switching time.

The magnitude of the overhead voltage in the forward and reverse active states has a typical default value of 7.2 V, allowing for an on-hook transmission of an undistorted signal of 3.14 dBm into 900  $\Omega$ . Additionally, this allows sufficient overhead for 500 mV of meter pulse if desired. This overhead is fixed. The ring trip detector is turned off during active states to conserve power.

Because on-hook transmission is not allowed in the scan state, an on-hook transmission state is defined. This state is functionally similar to the active state, except the tip ring voltage is derived from the higher VBAT1 rather than VBAT2.

In the on-hook transmission states with a primary battery whose magnitude is greater than a nominal 56.5 V, the magnitude of the tip-to-ground and ring-to-ground voltage is clamped at less than 56.5 V.

To minimize on-hook power, a low-power scan state is available. In this state, all functions except off-hook supervision are turned off to conserve power. On-hook transmission is not allowed in the scan state.

In the scan state with a primary battery whose magnitude is greater than a nominal 56.5 V, the magnitude of the tip-to-ground and ring-to-ground voltage is clamped at less than 56.5 V.

A forward disconnect state is provided, where all circuits are turned off and power is denied to the loop.

The device offers a ring state, in which a power ring signal is provided to the tip/ring pair. During the ring state, user-supplied lowvoltage ring signals are input to the device's RINGINP/N inputs. The input signals can be differential or single-ended, and can either or both include certain DC offset. Both inputs should reference to Vref. The two signals are amplified to produce the power ring signal. The input signal or signals may be a sine wave or filtered square wave to produce a sine wave or trapezoidal output. The Ring Trip detector is active during the ring state. The flexibility makes the device ideal to directly interface to DOCSIS compliant cable modem gateway products.

This feature eliminates the need for a separate external ring relay, associated external circuitry, and a bulk ringing generator.

The device offers a ground start state. In this state, the tip drive amplifier is turned off. The device presents a high impedance (>100 k $\Omega$ ) to PT and a current-limited battery (VBAT1) to PR. The voltage on PR is clamped to be less than 56.5 V in magnitude. The NSTAT loop current detector is used for ring ground detection. In the ground start state, since the loop current is common state, the loop closure threshold is reduced in half, thus maintaining loop supervision at specified levels.

Upon reaching the thermal shutdown temperature, the device will enter an all off state. Upon cooling, the device will re-enter the state it was in prior to thermal shutdown. Hysteresis is built in to prevent oscillation.

Data control is via a parallel unlatched control scheme.

Circuitry is added to the Le9500 device to minimize the inrush of current from the Vcc supply and to the battery supply during an on- to off-hook transition, thus saving in power supply design cost.

Legerity

The Le9500 device uses a voltage feed-current sense architecture. The transmit gain is a transimpedance. The Le9500 device transimpedance is set via a single external resistor, and this device is designed for optimal performance with a transimpedance set at 300 V/A. This interface is single ended. The Le9500 device offers a differential receive interface with a gain of 8.

The Le9500 device is internally referenced to 1.5 V. This reference voltage is output at the VREF pin of the device. The VITR output is also referenced to 1.5 V. The RCVP/RCVN receive inputs are floating inputs.

The Le9500 device is available in a 28-pin PLCC package.

### **CONNECTION DIAGRAM**

# **PIN DESCRIPTIONS**

| Pin Name | Туре   | Description                                                                                                                                                                                                                                                     |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NSTAT    | Output | Loop Closure Detector Output—Ring Trip Detector Output. When Low, this logic output indicates that an off-hook condition exists or ringing is tripped or a ring ground has occurred.                                                                            |

| VITR     | Output | <b>Transmit AC Output Voltage.</b> Output of internal AAC amplifier. This output is a voltage that is directly proportional to the differential AC tip/ring current.                                                                                            |

| RCVP     | Input  | <b>Receive AC Signal Input (Non inverting).</b> This high-impedance input controls to AC differential voltage on tip and ring. This node is a floating input.                                                                                                   |

| RCVN     | Input  | <b>Receive AC Signal Input (Inverting).</b> This high-impedance input controls to AC differential voltage on tip and ring. This node is a floating input.                                                                                                       |

| RINGINN  | Input  | <b>Power Ring Signal Input.</b> Couple to a sine wave or lower crest factor low-voltage ring signal. The input here is amplified to provide the full power ring signal at tip and ring. This signal may be applied continuously, even during nonringing states. |

| RINGINP  | Input  | <b>Power Ring Signal Input.</b> Couple to a sine wave or lower crest factor low-voltage ring signal. The input here is amplified to provide the full power ring signal at tip and ring. This signal may be applied continuously, even during nonringing states. |

| DCOUT    | Output | <b>DC Output Voltage.</b> This output is a voltage that is directly proportional to the absolute value of the differential tip/ring current. This is used to set ring trip threshold.                                                                           |

| CF2      | _      | Filter Capacitor. Connect a capacitor from this node to ground.                                                                                                                                                                                                 |

| CF1      |        | Filter Capacitor. Connect a capacitor from this node to CF2.                                                                                                                                                                                                    |

| RTFLT    |        | <b>Ring Trip Filter.</b> Connect this lead to DCOUT via a resistor and to AGND with a capacitor to filter the ring trip circuit to prevent spurious responses. A single-pole filter is needed.                                                                  |

| VREF     | Output | SLIC Device Internal Reference Voltage. Output of internal 1.5 V reference voltage.                                                                                                                                                                             |

| AGND     | Ground | Analog Signal Ground.                                                                                                                                                                                                                                           |

| Vcc      | Power  | Analog Power Supply. 3.3 V typical.                                                                                                                                                                                                                             |

| VBAT1    | Power  | Battery Supply 1. High-voltage battery.                                                                                                                                                                                                                         |

| VBAT2    | Power  | Battery Supply 2. Lower-voltage battery.                                                                                                                                                                                                                        |

| BGND     | Ground | Battery Ground. Ground return for the battery supplies.                                                                                                                                                                                                         |

| NC       | _      | No Connection.                                                                                                                                                                                                                                                  |

| Vprog    | Input  | <b>Current-Limit Program Input.</b> Connect this pin to ground to set current limit to 25 mA; leave this pin open to set current limit to 40 mA.                                                                                                                |

| FB2      | _      | <b>Polarity Reversal Slowdown Capacitor.</b> Connect a capacitor from this node for controlling rate of battery reversal. If ramped battery reversal is not desired, leave this pin floating.                                                                   |

| FB1      |        | <b>Polarity Reversal Slowdown Capacitor.</b> Connect a capacitor from this node for controlling rate of battery reversal. If ramped battery reversal is not desired, leave this pin floating.                                                                   |

| PT       | I/O    | <b>Protected Tip.</b> The output drive of the tip amplifier and input to the loop-sensing circuit. Connect to loop through overvoltage and overcurrent protection.                                                                                              |

| PR       | I/O    | <b>Protected Ring.</b> The output drive of the ring amplifier and input to the loop sensing circuit. Connect to loop through overvoltage and overcurrent protection.                                                                                            |

| B2       | Input  | State Control Input. These pins have an internal 150 k $\Omega$ pull-up.                                                                                                                                                                                        |

| B1       | Input  | State Control Input. These pins have an internal 150 k $\Omega$ pull-up.                                                                                                                                                                                        |

| B0       | Input  | State Control Input. These pins have an internal 150 k $\Omega$ pull-up.                                                                                                                                                                                        |

| ITR      | Input  | <b>Transmit Gain.</b> Input to AX amplifier. Connect a 4.75 k $\Omega$ resistor from this node to VTX to set transmit gain. Gain shaping for termination impedance with a first-generation codec is also achieved with a network from this node to VTX.         |

| VTX      | Output | <b>AC Output Voltage.</b> Output of internal AX amplifier. The voltage at this pin is directly proportional to the differential tip/ring current.                                                                                                               |

| TXI      | Input  | AC/DC Separation. Input to internal AAC amplifier. Connect a capacitor from this pin to VTX.                                                                                                                                                                    |

## **ABSOLUTE MAXIMUM RATINGS**

#### (at T<sub>A</sub> = 25 °C)

Stresses above those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Parameter                                    | Symbol   | Min        | Мах                       | Unit |

|----------------------------------------------|----------|------------|---------------------------|------|

| DC Supply (Vcc)                              | Vcc      | -0.5       | 4.0                       | V    |

| Battery Supply (VBAT1) (Le9500A)             | VBAT1    | BGND       | -80                       | V    |

| Battery Supply (VBAT1) (Le9500B)             | VBAT1    | BGND       | -90                       | V    |

| Battery Supply (VBAT1) (Le9500C)             | VBAT1    | BGND       | -110                      | V    |

| Battery Supply (VBAT1) (Le9500D Non-Ringing) | VBAT1    | BGND       | -110                      | V    |

| Battery Supply (VBAT1) (Le9500D Ringing)     | VBAT1    | BGND       | –155 + Vcc                | V    |

| Battery Supply (VBAT2)                       | VBAT2    | BGND       | VBAT1                     | V    |

| Logic Input Voltage                          | —        | -0.5       | Vcc + 0.5                 | V    |

| Logic Output Voltage                         | —        | -0.5       | Vcc + 0.5                 | V    |

| Operating Temperature Range                  | —        | -40        | 125                       | °C   |

| Storage Temperature Range                    | —        | -40        | 150                       | °C   |

| Relative Humidity Range                      | —        | 5          | 95                        | %    |

| PT or PR Fault Voltage (DC)                  | Vpt, Vpr | Vbat1 – 5  | 3                         | V    |

| PT or PR Fault Voltage (10 x 1000 μs)        | Vpt, Vpr | Vbat1 – 15 | 15                        | V    |

| Ground Potential Difference (BGND to AGND)   | —        | —          | ±1                        | V    |

| ESD Immunity (Human Body Model)              | —        | —          | JESD22 Class 1C compliant |      |

Note: Continuous operation above 145°C junction temperature may degrade device reliability.

#### Package Assembly

Green package devices are assembled with enhanced environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly.

Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile.

### **OPERATING RANGES**

#### **Environmental Ranges**

Legerity guarantees the performance of this device over commercial (0 to 70° C) and industrial (-40 to 85°C) temperature ranges by conducting electrical characterization over each range and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore GR-357-CORE Component Reliability Assurance Requirements for Telecommunications Equipment.

| Ambient Temperature       | $-40^{\circ} \text{ C} < \text{T}_{\text{A}} < +85^{\circ} \text{ C}$ |

|---------------------------|-----------------------------------------------------------------------|

| Ambient Relative Humidity | 5 to 95%                                                              |

#### **Electrical Ranges**

| Parameter                                                             | Min  | Тур | Max                     | Unit |

|-----------------------------------------------------------------------|------|-----|-------------------------|------|

| 3.3 V DC Supplies (Vcc)                                               | 3.13 | 3.3 | 3.47                    | V    |

| High Office Battery Supply (VBAT1) (Le9500A)                          | -60  | _   | -75                     | V    |

| High Office Battery Supply (VBAT1) (Le9500B)                          | -60  | -   | -85                     | V    |

| High Office Battery Supply (VBAT1) (Le9500C)                          | -60  | -   | -100                    | V    |

| High Office Battery Supply (VBAT1) (Le9500D)                          | -60  | _   | -100                    | V    |

| High Office Battery Supply (VBAT1) (Le9500D)<br>(during ringing only) | -60  | _   | -145                    | V    |

| Auxiliary Office Battery Supply (VBAT2)                               | -12  | _   | VBAT1<br>( VBAT1 <=100) | V    |

### **Thermal Characteristics**

| Parameter                                                              | Min | Тур  | Max | Unit |

|------------------------------------------------------------------------|-----|------|-----|------|

| Thermal Protection Shutdown (Tjc) <sup>1</sup>                         | 175 | 190  | -   | °C   |

| 28 PLCC Thermal Resistance Junction to Ambient (0JA) <sup>1, 2</sup> : |     |      |     |      |

| Natural Convection 2S2P Board                                          | _   | 35.5 | _   | °C/W |

| Natural Convection 2S0P Board                                          | —   | 50.5 | —   | °C/W |

| Wind Tunnel 100 Linear Feet per Minute (LFPM) 2S2P Board               | —   | 31.5 | —   | °C/W |

| Wind Tunnel 100 Linear Feet per Minute (LFPM) 2S0P Board               | —   | 42.5 |     | °C/W |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

2. Airflow, PCB board layers, and other factors can greatly affect this parameter.

## **ELECTRICAL CHARACTERISTICS**

## **Supply Currents**

Unless otherwise specified,  $V_{BAT1} = -75$  V for Le9500A;  $V_{BAT1} = -85$  V for Le9500B;  $V_{BAT1} = -100$  V for Le9500C and Le9500D;  $V_{BAT2} = -21$  V, Vcc = 3.3 V.

| Parameter                                                                        | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------|-----|------|------|------|

|                                                                                  |     | -    |      | -    |

| Scan state; no loop current:                                                     |     |      |      |      |

| Ivcc                                                                             | _   | 3.2  | 4.4  | mA   |

| IVBAT1                                                                           | —   | 0.25 | 0.44 | mA   |

| IVBAT2                                                                           | —   | 1    | 6    | μΑ   |

| Forward/reverse active; no loop current, with or without PPM, VBAT2 applied:     |     |      |      |      |

| Ivcc                                                                             | _   | 4.6  | 5.8  | mA   |

| IVBAT1                                                                           | —   | 23   | 85   | μA   |

| IVBAT2                                                                           | —   | 1.0  | 1.4  | mA   |

| On-hook transmission state; no loop current, with or without PPM, VBAT1 applied: |     |      |      |      |

| lvcc                                                                             | _   | 4.7  | 6.2  | mA   |

| IVBAT1                                                                           | —   | 1.4  | 1.9  | mA   |

| IVBAT2                                                                           | —   | 1    | 6    | μA   |

| Disconnect state:                                                                |     |      |      |      |

| lvcc                                                                             | _   | 1.8  | 2.8  | mA   |

| IVBAT1                                                                           | —   | 0    | 110  | μA   |

| IVBAT2                                                                           | —   | 1    | 25   | μA   |

| Ground start state, no loop current:                                             |     |      |      |      |

| Ivcc                                                                             | _   | 3.2  | _    | mA   |

| IVBAT1                                                                           | —   | 0.25 | —    | mA   |

| IVBAT2                                                                           | —   | 1    | —    | μA   |

| Ring state; no load (VBAT1= -145V for Le9500D):                                  |     |      |      |      |

| lvcc                                                                             | _   | 4.9  | 6.5  | mA   |

| IVBAT1                                                                           | —   | 2    | 2.8  | mA   |

| IVBAT2                                                                           | —   | 1    | 6    | μA   |

# **Power Dissipation**

VBAT2 = -21V, Vcc=3.3V.

| Parameter                                                  | Min                 | Тур              | Мах | Unit  |

|------------------------------------------------------------|---------------------|------------------|-----|-------|

| Le9500A (VB/                                               | ati = -75 V)        |                  |     |       |

| Scan state; no loop current                                | —                   | 29               | 45  |       |

| Forward/reverse active; no loop current, VBAT2 applied     | _                   | 38               | 53  |       |

| On-hook transmission state; no loop current, VBAT1 applied | —                   | 111              | 151 | m)//  |

| Disconnect state                                           | —                   | 6                | 15  | mW    |

| Ground start state                                         | _                   | 29               | _   |       |

| Ring state; no load                                        | _                   | 150              | 200 |       |

| Le9500B (VB/                                               | ati = -85 V)        |                  |     |       |

| Scan state; no loop current                                | _                   | 32               | 50  |       |

| Forward/reverse active; no loop current, VBAT2 applied     | _                   | 38               | 54  |       |

| On-hook transmission state; no loop current, VBAT1 applied | _                   | 127              | 182 | mW    |

| Disconnect state                                           | _                   | 6                | 17  | TIIVV |

| Ground start state                                         | _                   | 32               | _   |       |

| Ring state; no load                                        | _                   | 171              | 235 |       |

| Le9500C (VBA                                               | ⊤1 <b>=</b> −100 V) |                  |     | _     |

| Scan state; no loop current                                | —                   | 36               | 58  |       |

| Forward/reverse active; no loop current, VBAT2 applied     | —                   | 38               | 56  |       |

| On-hook transmission state; no loop current, VBAT1 applied | _                   | 154              | 215 | mW    |

| Disconnect state                                           | —                   | 6                | 20  | 11100 |

| Ground start state                                         | —                   | 35               | _   |       |

| Ring state; no load                                        | _                   | 204              | 280 |       |

| Le9500D (VBAT1 = -100 V; VBAT                              | 1 = -145 V dur      | ing ringing only | )   |       |

| Scan state; no loop current                                | —                   | 36               | 58  |       |

| Forward/reverse active; no loop current, VBAT2 applied     | _                   | 38               | 56  |       |

| On-hook transmission state; no loop current, VBAT1 applied | —                   | 154              | 215 |       |

| Disconnect state                                           | _                   | 6                | 20  | mW    |

| Ground start state                                         | _                   | 35               | _   |       |

| Ring state; no load <sup>1</sup>                           | _                   | 324              | 435 |       |

1. Tested at -100 V VBAT1 in production with proportioned limits

## LINE CHARACTERISTICS

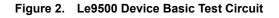

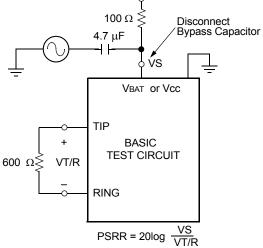

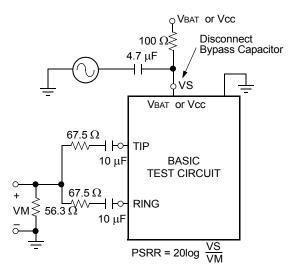

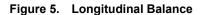

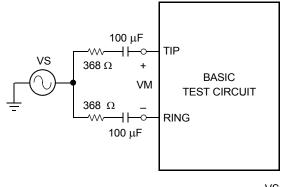

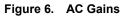

Unless otherwise specified, the test conditions are as specified in Figure 2, on page 14.

Typical values are characteristic of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not a part of the testing requirements. Minimum and maximum values apply across the operating temperature range and the entire battery range unless otherwise specified. Typical is defined as TA=25° C. Vcc = 3.3 V, VBAT2 = -24 V, VBAT1 = -60 V for Scan/OHT/Ground Start/Disconnect states, -75 V/-85 V/-100 V/-145 V for Ringing state of Le9500A/B/C/D.

| Parameter                                                                                                                                                                      | Min      | Тур      | Max      | Unit  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|-------|

| Tip or Ring Drive Current = DC + Longitudinal + Signal Currents <sup>1</sup>                                                                                                   | 105      | —        | - I      |       |

| Tip or Ring Drive Current = Ringing + Longitudinal <sup>1</sup>                                                                                                                | 65       | _        | _        | mApk  |

| Signal Current <sup>1</sup>                                                                                                                                                    | 10       | _        | _        |       |

| Longitudinal Current Capability per Wire (Longitudinal current is independent of DC loop current.) <sup>1</sup>                                                                | 8.5      | 15       | _        | mArms |

| Ringing Current (RLOAD = 1386 $\Omega$ + 40 $\mu$ F) <sup>1</sup>                                                                                                              | 29       | _        | _        |       |

| DC Loop Current Limit – ILIM (VBAT2 applied, RLOOP = 100 Ω):<br>VPROG = AGND<br>VPROG = Open                                                                                   |          | 25<br>40 |          | mA    |

| DC Current Limit Variation                                                                                                                                                     | _        |          | ±8       | %     |

| DC Feed Resistance (does not include protection resistors)                                                                                                                     | _        | 40       | _        | Ω     |

| Open Loop Voltages:<br>Scan state:<br> VBAT1  > 51 V  VTIP  –  VRING                                                                                                           | 44       | 51       | _        |       |

| VTIP ,  VRING  to Battery Ground                                                                                                                                               | —        |          | 56.5     |       |

| OHT state:<br> VBAT1  > 51 V  VTIP  –  VRING <br> VTIP ,  VRING  to Battery Ground<br>Active state:                                                                            | 41       | 49<br>—  | <br>56.5 | V     |

| VTIP – VRING  –  VBAT2                                                                                                                                                         | 5.75     | 7.2      | 8.5      |       |

| IVTIP – VRINGI – IVBAT2]<br>Ring state:<br> VTIP – VRINGI – IVBAT1]                                                                                                            |          | 4        | -        |       |

| Loop Closure Threshold:                                                                                                                                                        |          |          |          |       |

| Scan/Active/On-hook Transmission states, On- to Off-hook                                                                                                                       | 9.4      | 11.0     | 12.6     | mA    |

| Loop Closure Threshold Hysteresis:<br>Scan/Active/On-hook Transmission states                                                                                                  |          | 3.0      | _        | mA    |

| Longitudinal to Metallic Balance at PT/PR <sup>2</sup> :<br>Test Method: Q552 (11/96) Section 2.1.2 and <i>IEEE</i> <sup>®</sup> 455:<br>300 Hz to 600 Hz<br>600 Hz to 3.4 kHz | 52<br>52 | —        | _        | dB    |

| Metallic to Longitudinal (HARM) Balance <sup>3</sup> :<br>200 Hz to 1000 Hz<br>100 Hz to 4000 Hz                                                                               | 40<br>40 | _<br>_   | _<br>_   | dB    |

| PSRR 500 Hz – 3000 Hz <sup>1</sup> :<br>VBAT1, VBAT2<br>Vcc                                                                                                                    | 45<br>25 | —<br>30  |          | dB    |

#### Table 1. Two-Wire Port

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

2. Tested at 1KHz in production.

3. DC test only.

Leaeritu

Legerity

#### Table 2. Analog Pin Characteristics

| Parameter                                                             | Min         | Тур  | Мах         | Unit      |

|-----------------------------------------------------------------------|-------------|------|-------------|-----------|

| TXI (input impedance)                                                 | —           | 100  | _           | kΩ        |

| Output Offset (VTX)                                                   |             |      | ±10         | mV        |

| Output Offset (VITR)                                                  | _           | _    | 100         | mV        |

| Output Drive Current (VTX)                                            | ±300        | _    |             | μA        |

| Output Drive Current (VITR)                                           | ±10         | _    | _           | μA        |

| Output Voltage Swing:                                                 |             |      |             |           |

| Maximum (VTX, VITR)                                                   | AGND        | —    | Vcc         | V         |

| Minimum (VTX)                                                         | AGND + 0.25 | —    | Vcc – 0.5   | V         |

| Minimum (VITR)                                                        | AGND + 0.35 | —    | Vcc – 0.4   | V         |

| Output Short-circuit Current                                          | 10          | _    | ±50         | mA<br>kΩ  |

| Output Load Resistance <sup>1</sup>                                   |             | 20   | _           | pF        |

| Output Load Capacitance <sup>1</sup>                                  |             |      |             | P.        |

| RCVN and RCVP:                                                        | -           |      |             |           |

| Input Voltage Range                                                   | 0           | _    | Vcc – 0.3   | V         |

| Input Bias Current                                                    | —           | 0.12 | —           | μA        |

| Differential PT/PR Current Sense (DCOUT):                             |             | 45   |             | N//A      |

| Gain (PT/PR to DCOUT)<br>Offset Voltage at ILOOP = 0                  | <br>_15     | 15   | —<br>15     | V/A<br>mV |

| 6                                                                     | 150         | 600  | 1400        |           |

| AC Termination Impedance <sup>2</sup>                                 | 150         | 600  | 1400        | Ω         |

| Total Harmonic Distortion (200 Hz – 4 kHz) <sup>1</sup> :             |             |      |             | 0/        |

| Off-hook                                                              | —           | —    | 0.3<br>1.0  | %<br>%    |

| On-hook                                                               |             |      | 1.0         | 70        |

| Transmit Gain (f = 1004 Hz, 1020 Hz) <sup>3</sup> :                   | 004         |      | 000         |           |

| PT/PR Current to VITR                                                 | 291         | 300  | 309         | V/A       |

| Receive Gain, f = 1004 Hz, 1020 Hz Open Loop                          |             |      |             |           |

| RCVP or RCVN to PT – PR                                               | 7.76        | 8    | 8.24        |           |

| Gain vs. Frequency (transmit and receive) <sup>1</sup> ,              |             |      |             |           |

| 600 $\Omega$ Termination, 1004 Hz, 1020 Hz Reference:                 |             |      |             |           |

| 200 Hz to 300 Hz                                                      | -0.3        | 0    | 0.05        | dB        |

| 300 Hz to 3.4 kHz                                                     | -0.05       | 0    | 0.05        |           |

| 3.4 kHz to 20 kHz                                                     | -3.0        | 0    | 0.05<br>2.0 |           |

| 20 kHz to 266 kHz                                                     |             |      | 2.0         |           |

| Gain vs. Level (transmit and receive) <sup>1</sup> , 0 dBV Reference: |             |      |             | dB        |

| –55 dB to +3.0 dB                                                     | -0.05       | 0    | 0.05        |           |

| Idle-channel Noise (tip/ring), 600 $\Omega$ Termination:              |             |      |             |           |

| C-Message                                                             | —           | 8    | 13          | dBmC      |

| Psophometric <sup>1</sup>                                             | —           | -82  | -77         | dBrnp     |

| 3 kHz Flat <sup>1</sup>                                               | —           | —    | 20          | dBrn      |

| Idle-channel Noise (VTX), 600 $\Omega$ Termination:                   |             |      |             |           |

| C-Message                                                             | —           | 8    | 13          | dBmC      |

| Psophometric <sup>1</sup>                                             | —           | -82  | -77         | dBrnp     |

| 3 kHz Flat <sup>1</sup>                                               | —           | —    | 20          | dBrn      |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

2. Set externally either by discrete external components or a third- or fourth-generation codec. Any complex impedance  $R1 + R2 \parallel C$  between 150  $\Omega$  and 1400  $\Omega$  can be synthesized.

3. VITR transconductance depends on the resistor from ITR to VITR. This gain assumes an ideal 4.75  $k\Omega$ , (the recommended value). Positive current is defined as the differential current flowing from PT to PR.

#### Table 3. Logic Inputs and Outputs

| Parameter                                                                                                                                                                    | Symbol     | Min         | Тур        | Max        | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|------------|------|

| Input Voltages:<br>Low Level<br>High Level                                                                                                                                   | Vil<br>Vih | -0.5<br>2.0 | 0.2<br>2.5 | 0.5<br>VCC | V    |

| Input Current:<br>Low Level (Vcc = 3.46 V, VI = 0.4 V)<br>High Level (Vcc = 3.46 V, VI = 2.4 V)                                                                              | І∟<br>Ін   |             |            | ±50<br>±50 | μA   |

| Output Voltages (open collector with internal 60 k $\Omega$ pull-up resistor):<br>Low Level (Vcc = 3.13 V, IoL = 360 $\mu$ A)<br>High Level (Vcc = 3.13 V, IoH = $-5 \mu$ A) | Vol<br>Voн | 0<br>2.2    | 0.2        | 0.5<br>Vcc | V    |

#### Table 4. Ground Start

| Parameter                            | Min | Тур | Max | Unit |

|--------------------------------------|-----|-----|-----|------|

| Tip Open state – Tip Input Impedance | 150 | —   | —   | kΩ   |

| Threshold, On- to Off-hook           | —   | 13  | —   | mA   |

| Hysteresis                           | —   | 2   | _   | mA   |

#### Table 5. Ringing Specifications

| Parameter                                                                                         | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| RINGINN/P:                                                                                        |     |     |     |      |

| Input Voltage Swing                                                                               | 0   | —   | Vcc | V    |

| Ring Signal Isolation:                                                                            |     |     |     |      |

| PT/PR to VTX                                                                                      | —   | 60  | —   | dB   |

| Ring state                                                                                        |     |     |     |      |

| Ring Signal Isolation:                                                                            |     |     |     |      |

| RINGIN to PT/PR                                                                                   | —   | 80  | —   | dB   |

| Non-ringing state                                                                                 |     |     |     |      |

| Ring Signal Distortion <sup>1</sup> :                                                             |     |     |     |      |

| Open or 5 REN Load, 100 $\Omega$ Loop                                                             | —   | 3   | —   | %    |

| 5 REN (Ringing Equivalency Number) is equivalent of 1380 $\Omega$ in series with 40 $\mu\text{F}$ |     |     |     |      |

| Differential Gain RINGINP/N to PT/PR                                                              |     |     |     |      |

| RLOAD = Open,                                                                                     |     |     |     |      |

| Vbat1 = -75 V (Le9500A), Vringinp/n = 0.51 Vpp;                                                   |     |     |     |      |

| VBAT1 = -85 V (Le9500B), VRINGINP/N = 0.59 VPP;                                                   |     |     |     |      |

| VBAT1 = -100 V (Le9500C), VRINGINP/N = 0.70 VPP;                                                  |     |     |     |      |

| VBAT1 = -145 V (Le9500D), VRINGINP/N = 1.04 VPP.                                                  | 124 | 130 | 136 | V/V  |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

#### Table 6. Ring Trip

| Parameter                             | Min | Тур | Мах | Unit |

|---------------------------------------|-----|-----|-----|------|

| Ring Trip (NSTAT = 0):                |     |     |     |      |

| Loop Resistance (total) VBAT1 Applied | 100 | _   | 600 | Ω    |

| Ring Trip (NSTAT = 1):                |     |     |     |      |

| Loop Resistance (total) VBAT1 Applied | —   | —   | 10  | kΩ   |

| Trip Time (f = 20 Hz) <sup>1</sup>    | —   | —   | 100 | ms   |

| Hysteresis <sup>1</sup>               | _   | 10  | —   | mA   |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

Legerity

#### **Pre-trip immunity**

Ringing will not be tripped by the following loads across Tip and Ring as shown in the reference schematic in the this document. Ringing frequency = 17 Hz to 23 Hz otherwise specified.

- 10-kΩ resistor in parallel with 5 Ringer Equivalency Number (REN) (equivalent of 1386-Ω + 40-μF) per GR-909 Issue 2, December 2004

- 10-kΩ resistor in parallel with a 2-µF capacitor in parallel with 5 Ringer Equivalency Number (REN) (equivalent of 1386-Ω + 40-µF) per GR 57 Issue 1 October 2001.

## **OPERATING STATES**

#### Table 7. Control States

| B0 | B1 | B2 | Operating State                            |  |

|----|----|----|--------------------------------------------|--|

| 0  | 0  | 1  | Forward active                             |  |

| 0  | 1  | 1  | Reverse active                             |  |

| 0  | 0  | 0  | On-hook transmission forward battery       |  |

| 0  | 1  | 0  | On-hook transmission reverse battery       |  |

| 1  | 1  | 0  | Ground start                               |  |

| 1  | 0  | 0  | Scan                                       |  |

| 1  | 1  | 1  | Disconnect (default device power up state) |  |

| 1  | 0  | 1  | Ring                                       |  |

#### Table 8. Supervision Coding

| NSTAT                                                                    |

|--------------------------------------------------------------------------|

| 0 = off-hook or ring trip or thermal shutdown or ring ground.            |

| 1 = on-hook and no ring trip and no thermal shutdown and no ring ground. |

## **Operating State Definitions**

#### **Forward Active**

- Pin PT is positive with respect to PR.

- VBAT2 is applied to tip/ring drive amplifiers.

- Loop closure and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- Overhead is set to nominal 7.2 V for undistorted transmission of 3.14 dBm into 900 Ω with 500 mVrms of PPM.

#### **Reverse Active**

- Pin PR is positive with respect to PT.

- VBAT2 is applied to tip/ring drive amplifiers.

- Loop closure and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- Overhead is set to nominal 7.2 V for undistorted transmission of 3.14 dBm into 900  $\Omega$  with 500 mVrms of PPM.

#### Scan

- Except for loop closure, all circuits (including ring trip and common-mode detector) are powered down.

- On-hook transmission is disabled.

- Pin PT is positive with respect to PR and VBAT1 is applied to tip/ring.

- The tip to ring on-hook differential voltage will be typically between -44 V and -51 V with a -51 V to -100 V primary battery.

#### **On-Hook Transmission—Forward Battery**

- Pin PT is positive with respect to PR.

- VBAT1 is applied to tip/ring drive amplifiers.

- Supervision circuits, loop closure, and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip to ring on-hook differential voltage will be typically between -41 V and -49 V with a -51 V to -100 V primary battery.

#### **On-Hook Transmission—Reverse Battery**

- Pin PR is positive with respect to PT.

- VBAT1 is applied to tip/ring drive amplifiers.

- Supervision circuits, loop closure, and common-mode detect are active.

- Ring trip detector is turned off to conserve power.

- On-hook transmission is allowed.

- The tip to ring on-hook differential voltage will be typically between -41 V and -49 V with a -51 V to -100 V primary battery.

#### Disconnect

- The tip/ring amplifiers and all supervision are turned off.

- The SLIC device goes into a high-impedance state.

- NSTAT is forced high (on-hook).

- Due to internal pull-ups, device will power up in this state.

#### Ring

- Power ring signal is applied to tip and ring.

- Input wave form at RINGINN/P is amplified.

- Ring trip supervision and common-mode current supervision are active; loop closure is inactive.

- Overhead voltage is reduced to typically 4 V.

#### **Ground Start**

- Tip drive amplifier is turned off.

- Device presents a high impedance (>100 kΩ) to pin PT.

- Device presents a clamped (amplitude <56.5 V) current-limited battery (VBAT1) to PR.

#### **Thermal Shutdown**

- Not controlled via truth table inputs.

- This mode is caused by excessive heating of the device, such as may be encountered in an extended power cross situation. NSTAT output is forced low or off hook during a thermal shutdown event.

## **TEST CIRCUIT**

#### Figure 4. Longitudinal PSRR

LONGITUDINAL BALANCE = 20log  $\frac{VS}{VM}$

# APPLICATIONS

## **DC Loop Current Limit**

Current limit may be chosen from two discrete values, 25 mA or 40 mA, depending on if VPROG is grounded (25 mA) or left floating (40 mA). Note that there is a 12.5 k $\Omega$  slope to the I/V characteristic in the current-limit region; thus, once in current limit, the actual loop current will increase slightly, as loop length decreases.

The above describes the active state steady-state current-limit response. There will be a transient response of the current-limit circuit upon an on- to off-hook transition. Typical active state transient current-limit response is given in Table 10.

Table 9. Typical Active state On-Hook to Off-Hook Tip/Ring Current-Limit Transient Response

| Parameter                                                  | Value     | Unit |

|------------------------------------------------------------|-----------|------|

| DC Loop Current:<br>Active state                           | hand 60   |      |

| RLOOP = 100 $\Omega$ On- to Off-hook Transition t < 5 ms   | Ilim + 60 | mA   |

| DC Loop Current:                                           |           |      |

| Active state                                               | Ilim + 20 | mA   |

| RLOOP = 100 $\Omega$ On- to Off-hook Transition t < 50 ms  |           |      |

| DC Loop Current:                                           |           |      |

| Active state                                               | ILIM      | mA   |

| RLOOP = 100 $\Omega$ On- to Off-hook Transition t < 300 ms |           |      |

### **Overhead Voltage**

#### Active state

Overhead is fixed to a nominal 7.2 V, which is adequate for an on-hook transmission of 3.14 dBm into 900  $\Omega$  with additional head room for a 500-mV PPM signal.

#### Scan state

If the magnitude of the primary battery is greater than 51 V (but no more than 100 V), the magnitude of the open loop tip-to-ring open loop voltage is clamped typically between 44 V and 51 V. If the magnitude of the primary battery is less than a nominal 51 V, the overhead voltage will track the magnitude of the battery voltage, i.e., the magnitude of the open circuit tip-to-ring voltage will be about 4V less than battery.

#### **On-Hook Transmission state**

If the magnitude of the primary battery is greater than 51 V (but no more than 100 V), the magnitude of the open loop tip-to-ring open loop voltage is clamped typically between 41 and 49 V. If the magnitude of the primary battery is less than a nominal 51 V, the overhead voltage will track the magnitude of the battery voltage, i.e., the magnitude of the open circuit tip-to-ring voltage will be 6 to 8 V less than battery.

#### **Ring state**

In the ring state, to maximize ringing loop length, the overhead is decreased to the saturation of the tip ring drive amplifiers, a nominal 4 V.

During the ring state, to conserve power, the receive input at RCVN/RCVP is deactivated. During the ring state, to conserve power, the AAC amplifier in the transmit direction at VITR is deactivated. However, the AX amplifier at VTX is active during the ring state; differential ring current may be sensed at VTX during the ring state.

## **DC Loop Range**

The DC loop range can be calculated by using the following equation:

$$\mathsf{R}_{\mathsf{LOOP}} = \frac{|\mathsf{V}_{\mathsf{BAT2}}| - \mathsf{VOH}}{\mathsf{I}_{\mathsf{LOOP}}} - 2\mathsf{RP} - \mathsf{RDC}$$

where:

VBAT2 is applied under off-hook conditions for power conservation and SLIC device thermal considerations.

VOH is overhead voltage, typically 7.2V.

RDC is DC feed impedance, typically 40  $\Omega.$

RP is protection resistor, typically 50  $\Omega$ .

ILOOP is the loop DC current, no more than DC current limit.

If the minimum loop current allowed is 22 mA and VBAT2 is -21V then the maximum loop resistance by the equation is 487  $\Omega$ . This includes telephone set at the end of the loop.

The Le9500 device is intended for short-loop applications and, therefore, could always be in current limit during off-hook conditions. The above equation does not apply when the DC current is in the current limit region.

The actual maximum loop length the device can support, however, is often limited by the ringing loop length rather than the DC loop length (with adequate amplitude of VBAT2).

### **Battery Reversal Rate**

The rate of battery reverse is controlled or ramped by capacitors CFB1 and CFB2. A chart showing CFB1 and CFB2 values versus typical ramp time is given below. Leave FB1 and FB2 open if it is not desired to ramp the rate of battery reversal. Use with 0.47  $\mu$ F for CTX.

The voltage seen on FB1 and FB2 pins on the SLIC can be close to VBAT1. The value of CFB1 and CFB2 being greater than 0.22  $\mu$ F is not recommended.

| CFB1 and CFB2 | Transition Time |

|---------------|-----------------|

| 0.001 µF      | 2 ms            |

| 0.01 µF       | 20 ms           |

| 0.022 µF      | 50 ms           |

| 0.047 µF      | 100 ms          |

| 0.1 µF        | 220 ms          |

| 0.15 µF       | 320 ms          |

Table 10.

CFB1 and CFB2 Values versus Typical Ramp Time

## Supervision

The Le9500 device offers the loop closure and ring trip supervision functions. Internal to the device, the outputs of these detectors are multiplexed into a single package output, NSTAT. The ring trip detector is valid on NSTAT during the ring state, and loop closure detector is valid on NSTAT during active and on-hook transmission states. Additionally, common-mode current is detected for ground start applications. This status is output onto NSTAT and is valid during ground start mode.

### Loop Closure

The loop closure has a fixed on-hook to off-hook threshold in Scan/Active/OHT states with hysteresis.

#### **Ring Trip**

The ring trip detector requires only a single-pole filter at the input, minimizing external components. An R/C combination of 383 k $\Omega$  and 0.1  $\mu$ F, for a filter pole at 5.15 Hz, is recommended.

The ring trip threshold is internally fixed as a function of battery voltage and is given by the following:

where:

$R_T$  is ring trip current in mA.

V<sub>BAT1</sub> is the magnitude of the ring battery in V.

There is a typical 10 mA hysteresis.

#### Ground Start

In the ground start applications, the loop closure detector is also used to indicate ring-ground has occurred. During ground start mode, loop current will be common mode, rather than differential as in loop start mode. Thus, in ground start the threshold of the loop closure detector is reduced by one half the threshold seen in the loop start mode. This output is seen at the NSTAT output pin.

## **Power Ring**

The device offers a ring state, in which a balanced power ring signal is provided to the tip/ring pair. During the ring state, a usersupplied low-voltage ring signals are input to the device's RINGINP/N inputs. These signals are amplified to produce the balanced power ring signals. The user may supply a sine wave input, PWM input, or a square wave to produce sinusoidal or trapezoidal ringing at tip and ring.

Legerity

#### Sine Wave Input Signal and Sine Wave Power Ring Signal Output

The low-voltage sine wave input is applied differentially or single ended to the Le9500 device at pins RINGINP and RINGINN. During the ring state, the signals at pins RINGINP and RINGINN are amplified and presented to the subscriber loop. The differential gain from RINGINP/N to tip and ring is specified in the device specifications.

When the device enters the Ring state, the clamp circuit is disabled, allowing the voltage magnitude of the power ring signal to be maximized. Additionally, in the Ring state, the loop current limit is increased and is not limited by DC loop current limit.

The magnitude of the power ring voltage will be a function of the gain of the ring amplifier, the high-voltage battery, and the input signal level at RINGINP/N. The input range of the signal at RINGINP/N is 0 V to Vcc. As the input voltage at RINGINP/N is increased, the magnitude of the power ring voltage at tip and ring will increase linearly, until the tip and ring drive amplifiers begin to saturate. Once the tip and ring amplifiers reach saturation, further increases of the input signal will cause clipping distortion of the power ring signal at tip and ring. The ring signal will appear balanced on tip and ring. That is, the power ring signal is applied to both tip and ring, with the signal on tip 180-degree out of phase from the signal on ring.

The point at which clipping of the power ring signal begins at tip and ring is a function of the battery voltage, the input capacitor at RINGINP/N, and the input signal at RINGINP/N and Vcc. During non-ringing states, the sinusoidal ringing waveform may be left on at RINGINP/N. Via the state table, the ring signal will be removed from tip and ring, even if the low voltage input is still present at RINGINP/N.

#### Power Ringing with Le9500D

For operation of the Le9500D device with a high magnitude on VBAT1 greater than -100 V, special attention must be given to the following areas at system level.

#### Ringing Cadence

Scan or On Hook transmission state must be used during the silent period of ringing. Do not use Active state.

#### VBAT1 supply

VBAT1 may be more negative than -100 V only during the actual power ringing. The amplitude of VBAT1 should not exceed 100 V when the SLIC device is not in the Ringing mode. The amplitude of VBAT1 may not exceed 100 V during the silent period of ringing or any other non-ringing mode of operation.

#### Pre-Trip Immunity

The Le9500D device pre-trip immunity is specified as 2  $\mu$ F. With battery voltages more negative than -100 V, ringing into a heavy pre trip load will generate excessive power. Depending on system and ambient conditions, ringing into a load heavier than 2  $\mu$ F could force the device into thermal shutdown. Under these conditions, as the device goes into and out of thermal shutdown a glitch will appear on NSTAT. Proper operation may require the system to filter out these glitches.

#### **Robust Ring Trip Indication**

Upon ring trip, there will be large current going through the SLIC device which may cause the SLIC to go into thermal shutdown. Upon thermal shutdown, NSTAT remains Low, which is still consistent with the Ring Trip state. During thermal shutdown, the net voltage on RTFLT will go up because the Tip Ring amplifiers are off. When the voltage on RTFLT passes a certain limit (ring trip threshold), until a SLIC state change, NSTAT will toggle between the thermal shutdown inducted low indication and the RTFLT voltage high indication.

There are several ways to help remedy this situation. Limit the current on VBAT1 supply such that VBAT1 will move up towards ground upon off hook, add a 100- $\Omega$  power resistor in the VBAT1, or add a 2-M $\Omega$  resistor from RTFLT to ground to lower ring trip threshold.

For more details, please contact Legerity field/customer applications.

## **Design Examples**

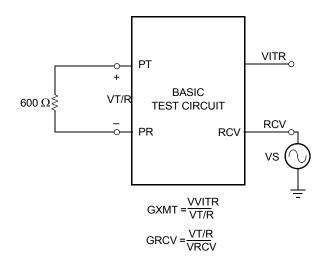

The following reference schematics show the complete Le9500 SLIC schematic for interfaces to Broadcom codecs.

### Le9500/Broadcom<sup>®</sup> Reference Schematic A

The following reference circuit shows the complete Le9500 SLIC device schematic for interface to the *Broadcom* BCM3352 as designed on the *Broadcom* BCM93352SV application reference design and board. This circuit has a  $600-\Omega$  AC termination. The BCM3351, BCM3352, and BCM6352 have programmable registers to modify the external  $600-\Omega$  termination to achieve worldwide real or complex terminations. For complex terminations with BCM1101, the external circuit must be changed to set the complex termination. Other resistive terminations require a change to this circuit. Contact your Legerity account representative for assistance with modifications to this circuit.

Legerity

### **Application Circuit Parts List A**

The following parts list is for the Legerity Le9500 SLIC device and Broadcom BCM3352 codec (per Broadcom BCM93552SV application board daughter board components), fully programmable.

| ltem               | Туре                               | Value                                            | Tolerance | Rating             | Comments                                                                  |  |  |

|--------------------|------------------------------------|--------------------------------------------------|-----------|--------------------|---------------------------------------------------------------------------|--|--|

|                    | Fault Protection                   |                                                  |           |                    |                                                                           |  |  |

| R <sub>PT</sub>    | Resistor                           | 50 Ω                                             | 1%        | Fusible or PTC     | Protection resistor.                                                      |  |  |

| R <sub>PR</sub>    | Resistor                           | 50 Ω                                             | 1%        | Fusible or PTC     | Protection resistor.                                                      |  |  |

| Protector          | Battery<br>referenced<br>thyristor |                                                  | _         | _                  | Secondary protection. Reference to most negative power supply (VBAT1ext). |  |  |

| C <sub>P</sub>     | Capacitor                          | 0.1 μF                                           | 20%       | 100 V <sup>1</sup> | Consult protector vendor for recommended value.                           |  |  |

|                    |                                    |                                                  | Powe      | er Supply          | -                                                                         |  |  |

| C <sub>VBAT1</sub> | Capacitor                          | 0.1 μF                                           | 20%       | 100 V <sup>1</sup> | VBAT1 filter capacitor.                                                   |  |  |

| C <sub>VBAT2</sub> | Capacitor                          | 0.1 μF                                           | 20%       | 50 V <sup>2</sup>  | VBAT2 filter capacitor.  VBAT2  <  VBAT1 .                                |  |  |

| D <sub>VBAT1</sub> | Diode                              | 1N4004                                           | —         | _                  | Reverse current.                                                          |  |  |

| C <sub>CC</sub>    | Capacitor                          | 0.47 μF                                          | 20%       | 10 V               | Ceramic bypass capacitor.                                                 |  |  |

| L                  | Ferrite<br>Bead                    | 600 Ω, <i>Murata<sup>®</sup></i><br>BLM11A601SPB | _         | _                  | Filtering.                                                                |  |  |

| C <sub>F1</sub>    | Capacitor                          | 0.22 μF                                          | 20%       | 100 V              | Filter capacitor.                                                         |  |  |

| C <sub>F2</sub>    | Capacitor                          | 0.1 μF                                           | 20%       | 100 V              | Filter capacitor.                                                         |  |  |

|                    |                                    |                                                  | Ri        | ng Trip            |                                                                           |  |  |

| C <sub>RT</sub>    | Capacitor                          | 0.1 μF                                           | 20%       | 10 V               | Ring trip filter capacitor.                                               |  |  |

| R <sub>RT</sub>    | Resistor                           | 383 kΩ                                           | 1%        | 1/16 W             | Ring trip filter resistor.                                                |  |  |

|                    |                                    |                                                  | AC I      | nterface           | -                                                                         |  |  |

| $R_{GX}$           | Resistor                           | 4.75 kΩ                                          | 1%        | 1/16 W             | Sets T/R to VITR transimpedance.                                          |  |  |

| C <sub>TX</sub>    | Capacitor                          | 0.47 μF                                          | 20%       | 10 V               | AC/DC separation.                                                         |  |  |

| C <sub>C1</sub>    | Capacitor                          | 0.1 μF                                           | 20%       | 10 V               | DC blocking capacitor                                                     |  |  |

| R <sub>4</sub>     | Resistor                           | 78.7 kΩ                                          | 1%        | 1/16 W             | AC interface.                                                             |  |  |

| R <sub>5</sub>     | Resistor                           | 174 kΩ                                           | 1%        | 1/16 W             | AC interface.                                                             |  |  |

| R <sub>6</sub>     | Resistor                           | 88.7 kΩ                                          | 1%        | 1/16 W             | AC interface.                                                             |  |  |

| R <sub>7</sub>     | Resistor                           | 54.9 kΩ                                          | 1%        | 1/16 W             | AC interface.                                                             |  |  |

| R <sub>8</sub>     | Resistor                           | 88.7 kΩ                                          | 1%        | 1/16 W             | AC interface.                                                             |  |  |

| R <sub>NSTAT</sub> | Resistor                           | 10 kΩ                                            | 1%        | 1/16 W             | Control.                                                                  |  |  |

| Le9500             | SLIC<br>device                     | _                                                | —         | —                  |                                                                           |  |  |

Note:

1. Increase to 200 V for Le9500C and Le9500D.

2. Assume |VBAT2|<50V.

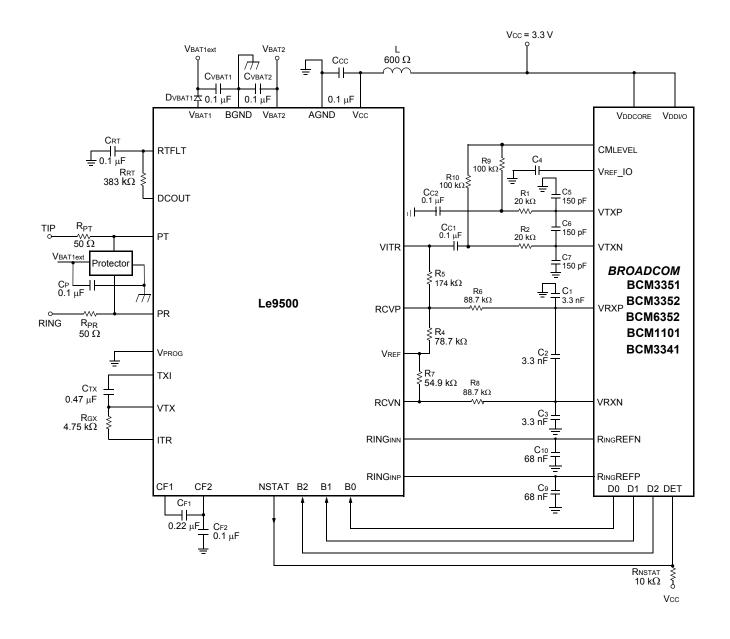

### Le9500/Broadcom<sup>®</sup> Reference Schematic B

The following reference schematic shows the complete Le9500 SLIC device schematic for interface to the *Broadcom* BCM3367/ 3368. This circuit has a natural 700- $\Omega$  AC termination impedance. The BCM3367 or MCB3368 has programmable registers to modify the external 700- $\Omega$  termination to achieve worldwide real or complex terminations, as well as to set transmit and receive gains, and other AC parameters. The BCM3367/3368 codec also drives ringing inputs, sets SLIC operation state, and monitors NSTAT. The voltage of the battery supply to VBAT1 is expected to be properly set and may vary depending upon SLIC operational states.

Contact your Legerity account representative for assistance with other applications.

Legerity

### **Application Circuit Parts List B**

The following parts list is for the Legerity Le9500 SLIC device and Broadcom BCM3367/3368 codec.

| ltem               | Туре                               | Value                                            | Tolerance | Rating             | Comments                                                                  |

|--------------------|------------------------------------|--------------------------------------------------|-----------|--------------------|---------------------------------------------------------------------------|

|                    |                                    |                                                  | Fault I   | Protection         |                                                                           |

| R <sub>PT</sub>    | Resistor                           | 50 Ω                                             | 1%        | Fusible or PTC     | Protection resistor.                                                      |

| R <sub>PR</sub>    | Resistor                           | 50 Ω                                             | 1%        | Fusible or PTC     | Protection resistor.                                                      |

| Protector          | Battery<br>referenced<br>thyristor |                                                  | _         | -                  | Secondary protection. Reference to most negative power supply (VBAT1ext). |

| CP                 | Capacitor                          | 0.1 μF                                           | 20%       | 100 V <sup>1</sup> | Consult protector vendor for recommended value.                           |

|                    |                                    |                                                  | Powe      | er Supply          |                                                                           |

| C <sub>VBAT1</sub> | Capacitor                          | 0.1 μF                                           | 20%       | 100 V <sup>1</sup> | VBAT1 filter capacitor.                                                   |

| C <sub>VBAT2</sub> | Capacitor                          | 0.1 μF                                           | 20%       | 50 V <sup>2</sup>  | VBAT2 filter capacitor.  VBAT2  <  VBAT1 .                                |

| D <sub>VBAT1</sub> | Diode                              | 1N4004                                           | _         | —                  | Reverse current.                                                          |

| C <sub>VCC</sub>   | Capacitor                          | 0.47 μF                                          | 20%       | 10 V               | Ceramic bypass capacitor.                                                 |

| L                  | Ferrite<br>Bead                    | 600 Ω, <i>Murata<sup>®</sup></i><br>BLM11A601SPB | _         | _                  | Filtering.                                                                |

| C <sub>F1</sub>    | Capacitor                          | 0.22 μF                                          | 20%       | 100 V              | Filter capacitor.                                                         |

| C <sub>F2</sub>    | Capacitor                          | 0.1 μF                                           | 20%       | 100 V              | Filter capacitor.                                                         |

|                    | •                                  |                                                  | Rir       | ng Trip            | •                                                                         |

| C <sub>RT</sub>    | Capacitor                          | 0.1 μF                                           | 20%       | 10 V               | Ring trip filter capacitor.                                               |

| R <sub>RT</sub>    | Resistor                           | 383 kΩ                                           | 1%        | 1/16 W             | Ring trip filter resistor.                                                |

|                    |                                    |                                                  | AC I      | nterface           |                                                                           |