# ASSP SWITCHING REGULATOR CONTROLLER

# **MB3775**

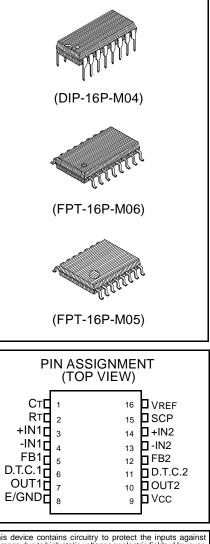

#### LOW VOLTAGE DUAL PWM SWITCHING REGULATOR CONTROLLER

The MB3775 is a dual pulse-width-modulation control circuit. It contains the basic circuits required for two PWM control circuits. Complete synchronization is obtained by using the same oscillator output waveform.

This IC can provide following types of output voltage: step down, step up, and inverter. Power consumption is low, thus the MB3775 is ideal for use in high-efficiency portable equipment.

- Wide supply voltage range: 3.6 V to 18 V

- Low current consumption: 1.3 mA typical

- Wide oscillation frequency range: 1 kHz to 500 kHz

- On-chip timer latch short protection circuit

- On-chip under voltage lockout protection

- On-chip reference voltage: 1.28 V

- Variable dead time provides control over total operating range.

| ABSOLUTE MAXIMUM         | <b>(</b> Ta = 2 | 25°C)                |             |      |

|--------------------------|-----------------|----------------------|-------------|------|

| Rating                   | Symbol          | Condition            | Value       | Unit |

| Power Supply Voltage     | Vcc             |                      | 20          | V    |

| Error Amp. Input Voltage | VI              |                      | -0.3 to +10 | V    |

| Collector Output Voltage | Vo              |                      | 20          | V    |

| Collector Output Current | ю               |                      | 75          | mA   |

|                          |                 | Ta ≤ 25 °C(SOP) *620 |             | mW   |

| Power Dissipation        | PD              | Ta ≤ 25 °C(DIP)      | 1000        | mW   |

|                          |                 | Ta≤25°C(VSOP)        | *430        | mW   |

| Operating Temperature    | Тор             |                      | -30 to +85  | °C   |

| Storage temperature      | Tstg            |                      | -55 to+125  | °C   |

\*: The packages are mounted on the epoxy board (4 cm x 4 cm x 1.5 mm)

**NOTE :** Permanent device damage may occur if the above **Absolute Maximum Ratings** are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

## BLOCK DIAGRAM

## RECOMMENDED OPERATING CONDITIONS

| Parameter                        | Symbol |      | Value   | Unit  |      |

|----------------------------------|--------|------|---------|-------|------|

| Farameter                        | Symbol | Min  | Min Typ |       | Onic |

| Power Supply Voltage             | Vcc    | 3.6  | 6.0     | 18    | V    |

| Error Amp. Input Voltage         | VI     | -0.2 | -       | 1.45  | V    |

| Collector Output Voltage         | Vo     | -    | -       | 18    | V    |

| Collector Output Current         | lo     | 0.3  | -       | 50    | mA   |

| Phase Compensation Capacitor     | СР     | -    | 0.1     | -     | μF   |

| Timing Capacitor                 | Ст     | 150  | -       | 15000 | pF   |

| Timing Resistor                  | RT     | 5.1  | -       | 100   | kΩ   |

| Oscillator Frequency             | fosc   | 1    | -       | 500   | kHz  |

| Reference Voltage Output Current | IREF   | -3   | -1      | -     | mA   |

| Operating Temperature            | Тор    | -30  | 25      | 85    | °C   |

### OPERATION DESCRIPTION

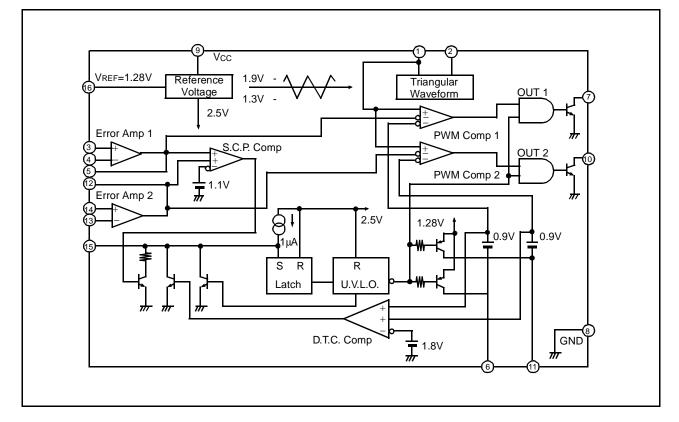

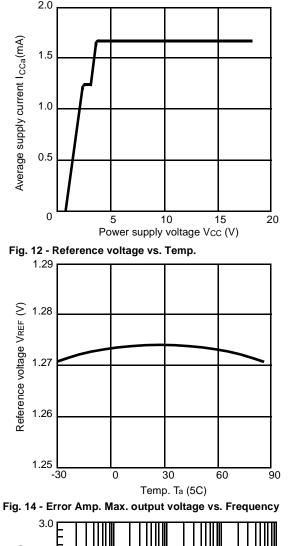

#### 1. Reference voltage

The reference voltage circuit generates a stable, temperature-compensated 2.5 V reference from Vcc (pin 9) for use by internal circuits.

A reference voltage of temperature compensated 1/2 Vref can be obtained to external circuit by Vref terminal (pin 16).

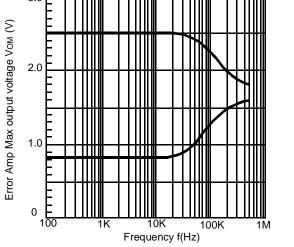

#### 2. Oscillator

A triangular waveform of any frequency is obtained by connecting an external capacitor and resistor to the  $C_T$  (pin 1) and  $R_T$  terminals (pin 2).

The amplitude of this waveform is from 1.3 V to 1.9 V. The oscillator is internally connected to the non-inverting inputs of the PWM comparators. The oscillator waveform is available at the  $C_T$  terminal.

#### 3. Error amplifiers

The error amplifier detects the output voltage of the switching regulator.

The common-mode input voltage range is -0.2 V to 1.45 V, so the input reference voltage can be set the V<sub>REF</sub> and GND levels. Error amplifiers can be used as either inverting and non-inverting amplifiers.

The voltage gain is fixed. Phase compensation is possible by connecting a capacitor to the FB terminals (pins 5 and 12) of the error amplifiers.

The error amplifier output are internally connected to the inverting inputs of the PWM comparators and also to the short protection circuit.

#### 4. Timer latch short protection circuit

The timer latch short protection circuit detects the output levels of the error amplifiers. If one or both error amplifier outputs are 1.1 V or lower, the timer circuit begins charging the externally connected protection enable capacitor.

If the output level of the error amplifier does not drop below the normal voltage range before the capacitor voltage reaches the transistor base-emitter voltage  $V_{BE}$  ( $\doteq 0.65$  V), the latch circuit turns the output drive transistor off and sets the dead time to 100 %.

#### 5. Under voltage lockout protection circuit

An ambiguous transition state at power-on or a momentary fluctuation in the supply line may result in loss of control and may adversely affect or even destroy the system. The under voltage lockout protection circuit compares the internal reference voltage level with the supply voltage level. If the supply voltage level falls below the reference level the latch circuit is reset the output drive transistor is turned off and the dead time is set to 100 %. The protection enable terminal (pin 15) is pulled "Low".

#### 6. PWM comparator

Each PWM comparator has two inverting inputs and one non-inverting input. This voltage-to-pulse-width converter controls the output pulse width according to the input voltage.

The PWM comparator turns the output drive transistor on when the oscillator triangular waveform is higher than the error amplifier output and the dead time control terminal voltage.

#### 7. Output drive transistor

The open-collector output-drive transistors provide common-emitter output of 18 V dielectric capability. The output drive transistors can source up to 50 mA of drive current to the switching power transistor.

## ■ ELECTRICAL CHARACTERISTICS

|                                        |                                                 |        |       | (Ta  | =25°C, V | CC=6V) |

|----------------------------------------|-------------------------------------------------|--------|-------|------|----------|--------|

| Parameter                              | condition                                       | Symbol | Value |      |          | Unit   |

| Faranielei                             | condition                                       | Symbol | Min   | Тур  | Max      | Unit   |

| Reference Section                      |                                                 |        |       |      |          |        |

| Output Voltage                         | IOR =-1 mA                                      | VREF   | 1.26  | 1.28 | 1.30     | V      |

| Output Temp. Stability                 | Ta = -30 °C to +85 °C                           | VRTC   | -2    | ±0.2 | 2        | %      |

| Input Stability                        | VCC = 3.6 V to 18 V                             | Line   | _     | 2    | 10       | mV     |

| Load Stability                         | IOR = -0.1 mA to -1 mA                          | Load   | -     | 1    | 7.5      | mV     |

| Short Circuit Output Current           | VREF = 0 V                                      | los    | -     | -30  | -10      | mA     |

| Under Voltage Lockout Protection Sec   | ction                                           |        | -     |      |          |        |

| Threshold Voltage                      | IOR = -0.1 mA                                   | VtH    | -     | 2.72 | -        | V      |

|                                        | IOR = -0.1 mA                                   | VtL    | -     | 2.60 | -        | V      |

| Hysteresis Width                       | IOR = -0.1 mA                                   | VHYS   | 80    | 120  | -        | mV     |

| Reset Voltage (Vcc)                    |                                                 | VR     | 1.5   | 1.9  | -        | V      |

| Protection Circuit Section             |                                                 |        |       |      |          |        |

| Input Threshold Voltage                |                                                 | VtPC   | 0.60  | 0.65 | 0.7      | V      |

| Input Stand by Voltage                 | No pull up                                      | VSTB   | -     | 50   | 100      | mV     |

| Input Latch Voltage                    | No pull up                                      | VI     | -     | 50   | 100      | mV     |

| Input Source Current                   |                                                 | lbpc   | -1.4  | -1.0 | -0.6     | μA     |

| Comparator Threshold Voltage           | Pin 5, Pin 12                                   | VtC    | -     | 1.1  | _        | V      |

| Triangular Waveform Oscillator Section | on                                              |        |       |      |          |        |

| Ocillator Frequency                    | $CT = 330 \text{ pF}, R_T = 15 \text{ k}\Omega$ | fosc   | _     | 200  | -        | kHz    |

| Frequency Deviation                    | CT = 330 pF, Rτ = 15 kΩ                         | fdev   | -     | 10   | -        | %      |

| Frequency Stability (Vcc)              | Vcc = 3.6 V to 18 V                             | fdV    | _     | 1    | -        | %      |

|                                        |                                                 | -      |       |      |          |        |

#### **Dead-Time Control Section**

Frequency Stability (Ta)

| Input Threshold Voltage   | Duty Cycle = 0 %   | Vt0   | _            | 1.0  | VREF<br>-0.15 | V  |

|---------------------------|--------------------|-------|--------------|------|---------------|----|

| (fosc = 10 kHz)           | Duty Cycle = 100 % | Vt100 | 0.2          | 0.4  | _             | V  |

| Input Bias Current        |                    | lbdt  | -            | -0.2 | -1            | μA |

| Latch Mode Source Current | Vdt = 0.7 V        | ldt   | -            | -150 | -80           | μA |

| Latch Input Voltage       | Idt=-40 μA         | Vdt   | VREF<br>-0.1 | _    | _             | V  |

fdT

-4

\_

4

%

Ta = -30 °C to +85 °C

# ELECTRICAL CHARACTERISTICS (Continued)

|                                 |                  |        |      | (Ta=25°C, VCC |       |     |  |  |  |

|---------------------------------|------------------|--------|------|---------------|-------|-----|--|--|--|

| Parameter                       | Condition        | Symbol |      | Unit          |       |     |  |  |  |

| Falameter                       | Condition        | Symbol | Min  | Тур           | Мах   | Uni |  |  |  |

| Error Amp. Section              |                  |        |      |               |       |     |  |  |  |

| Input Offset Voltage            | Vo = 1.6 V       | Vio    | -10  | _             | +10   | mV  |  |  |  |

| Input Offset Current            | Vo = 1.6 V       | lio    | -100 | _             | +100  | nA  |  |  |  |

| Input Bias Current              | Vo = 1.6 V       | lв     | -500 | -100          | _     | nA  |  |  |  |

| Common Mode Input Voltage Range | VCC=3.6V to 18V  | VICR   | -0.2 | _             | +1.45 | V   |  |  |  |

| Voltage Gain                    |                  | Av     | 84   | 120           | _     | V/V |  |  |  |

| Frequency Band Width            | Av = -3 dB       | BW     | _    | 3             | _     | MH  |  |  |  |

| Common Mode Rejection Ratio     |                  | CMRR   | 60   | 80            | _     | dB  |  |  |  |

|                                 |                  | Vom+   | 2.2  | 2.4           | _     | V   |  |  |  |

| Max. Output Voltage Width       |                  | Vom-   | _    | 0.7           | 0.9   | V   |  |  |  |

| Output Sink Current             | VO = 1.6 V       | IOM+   | 24   | 50            | _     | μA  |  |  |  |

| Output Source Current           | Vo = 1.6 V       | Іом-   | _    | -1.2          | -0.7  | mA  |  |  |  |

| PWM Comparator Section          | 1                |        | 1    | 1             | I     | 1   |  |  |  |

| Input Threshold Voltage         | Duty Cycle = 0 % | Vt0    | -    | 1.9           | 2.1   | V   |  |  |  |

|                                 |                  | 1      | 1    | 1             |       | 1   |  |  |  |

| Input Threshold Voltage | Duty Cycle = 0 %      | VtO   | -    | 1.9  | 2.1  | V  |

|-------------------------|-----------------------|-------|------|------|------|----|

| (fosc=10 kHz)           | Duty Cycle = 100 %    | Vt100 | 1.05 | 1.3  | -    | V  |

| Input Sink Current      | Pin 5, Pin 12 = 1.6 V | lin+  | 24   | 50   | -    | μA |

| Input Source Current    | Pin 5, Pin 12 = 1.6 V | lin-  | 1    | -1.2 | -0.7 | mA |

#### **Output Section**

| Output Leak Current       | Vo=18V   | Leak | _ | _   | 10  | μΑ |

|---------------------------|----------|------|---|-----|-----|----|

| Output Saturation Voltage | Io=50 mA | VSAT | 1 | 1.1 | 1.4 | V  |

| Stand by Current       | Output "OFF" | Iccs | — | 1.3 | 1.8 | mA |

|------------------------|--------------|------|---|-----|-----|----|

| Average Supply Current | R⊤=15kΩ      | ICCa | - | 1.7 | 2.4 | mA |

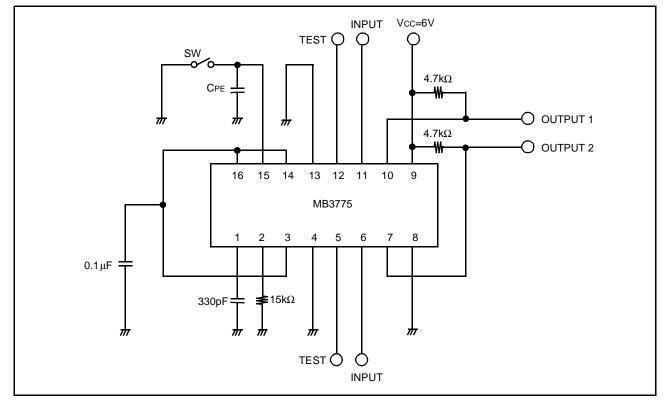

#### ■ TEST CIRCUIT

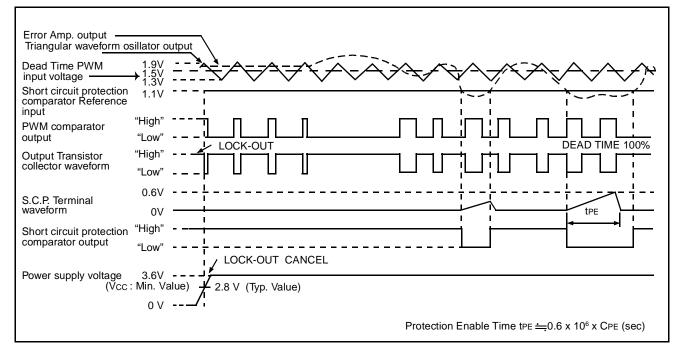

## ■ TIMING CHART (Internal Waveform)

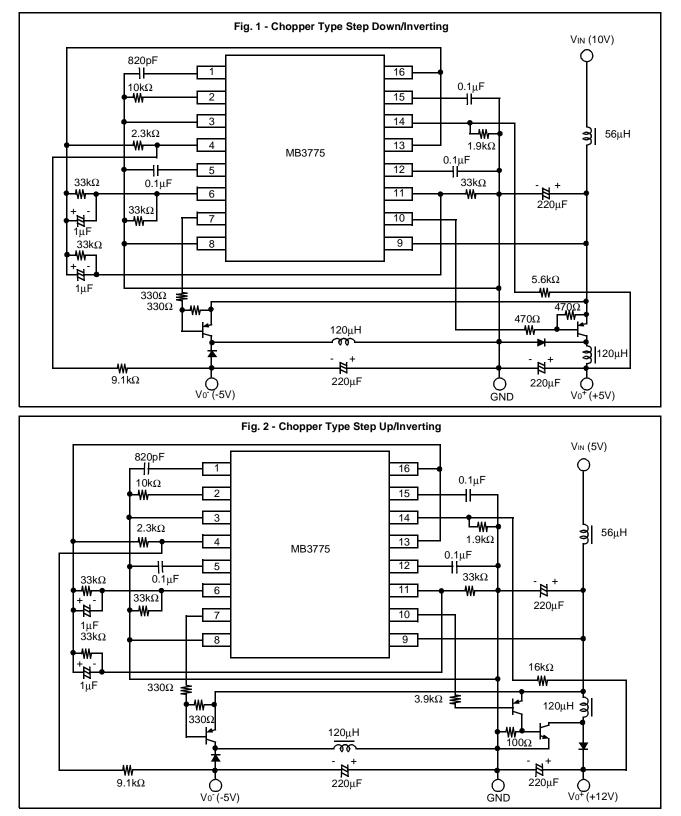

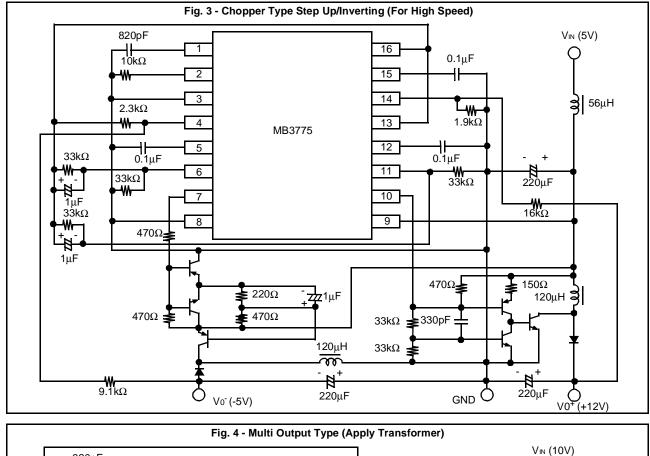

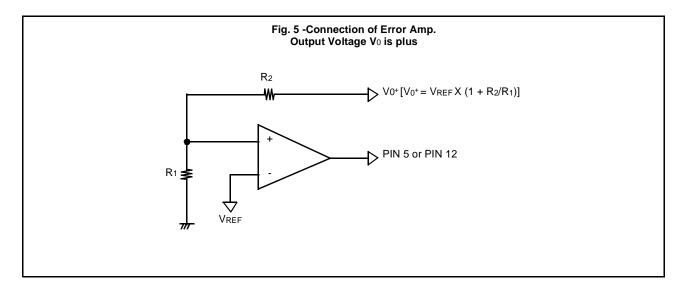

#### APPLICATION CIRCUIT

## ■ APPLICATION CIRCUIT (Continued)

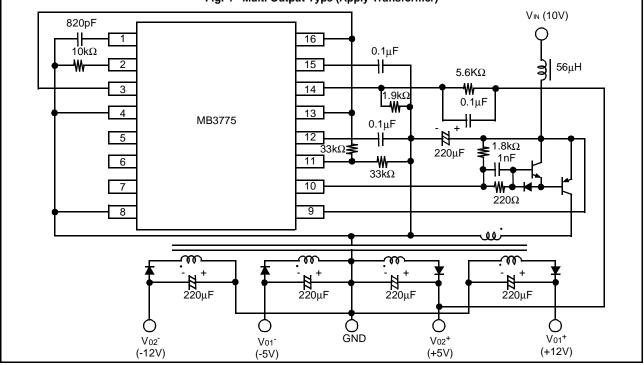

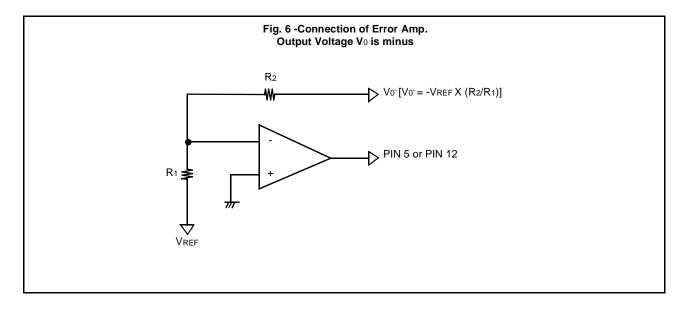

### ■ HOW TO SET OUTPUT VOLTAGE

The output voltage is set using the connection shown in Fig. 5 and 6.

The error amplifiers are supplied to the internal reference voltage circuit as are the other internal circuits. The common-mode input voltage range is from -0.2 V to +1.45 V.

When the amplifiers are operated non-inverting, tie the inverting terminal to  $V_{REF}$  ( $\doteq$ 1.28 V). When the amplifiers are operated inverting, tie the non-inverting terminal to ground.

#### ■ HOW TO SET TIME CONSTANT FOR TIMER LATCH SHORT PROTECTION CIRCUIT

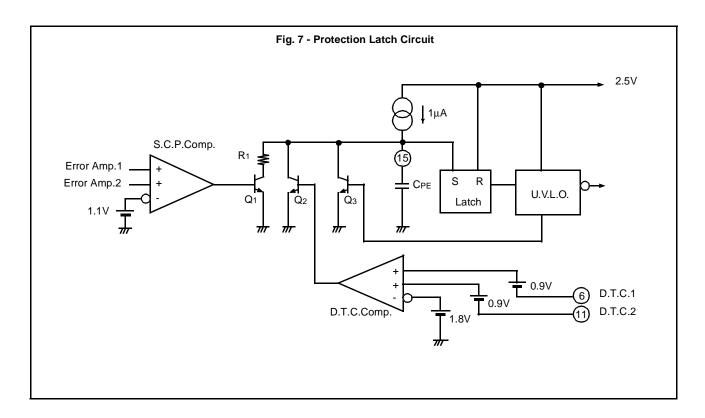

TIMING CHART shows the configuration of the protection latch circuit.

Error amplifier outputs, are internally connected to the non-inverting inputs of the short-circuit protection comparator and are compared with the reference voltage (1.1 V) connected to the inverting input.

When the load condition of the switching regulator is stable, the error amplifier has no output fluctuation. Thus, short-circuit protection control is also kept in balance, and the protection enable terminal (pin 15) voltage is kept at about 50 mV.

If the load condition drastically changes due to a load short-circuit and if low-level signals (1.1 V or lower) are input to the noninverting inputs of the short-circuit protection comparator from the error amplifiers, the short-circuit protection comparator outputs a "Low" level to turn transistor  $Q_1$  off. The protection enable terminal voltage is discharged, and then the short-circuit protection comparator charges the externally connected protection enable capacitor  $C_{PE}$  according to the following formula:

$V_{PE} = 50 \text{ mV} + t_{PE} \text{ x } 10^{-6}/C_{PE}$  $0.65 = 50 \text{ mV} + t_{PE} \text{ x } 10^{-6}/C_{PE}$  $C_{PE} = t_{PE}/0.6 \text{ (}\mu\text{F)}$

When the protection enable capacitor charges to about 0.65 V, the protection latch is set to enable the under voltage lockout protection circuit and to turn the output drive transistor off. The dead time is set to 100 %.

Once the under voltage lockout protection circuit is enabled, the protection enable is released; however, the protection latch is not reset if the power is not turned off.

The non-inverting inputs of the D.T.C. comparator are connected to the D.T.C. terminals (pins 6 and 11) through the power supply (about 0.9 V) and are compared with a reference voltage (about 1.8 V) connected to the inverting input.

To prevent malfunction of the short protection circuit in soft-start mode (using D.T.C. terminals), the D.T.C. comparator outputs a "High" level to turn  $Q_2$  on until the D.T.C. terminal voltage drops to about 0.9 V.

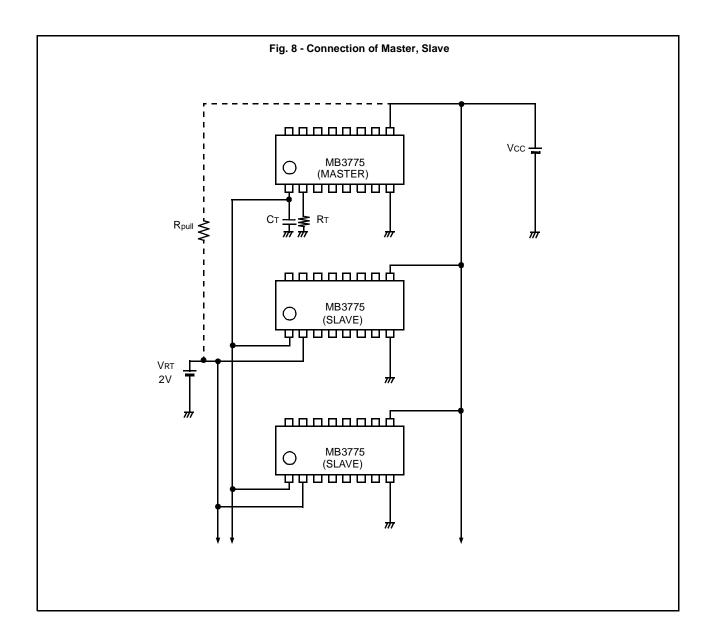

#### ■ SYNCHRONIZATION OF ICs

To synchronize MB3775 ICs, first, the specified capacitor and resistor are connected to the  $C_T$  and  $R_T$  terminals of the master IC to start self oscillation. Next, 2 V is applied to the  $R_T$  terminals of the slave ICs to disable the charge/discharge circuit for triangular wave oscillation. Finally, the  $C_T$  terminals of the master and slave ICs are connected.

Instead of applying  $V_{RT}$  to the  $R_T$  terminals, these terminals can be pulled up by a resistor (see resistance indicated by the dashed line in Fig. 8). Select the pull-up resistance  $R_{pull}$  from the formula given below.

$$\frac{V_{CC}}{0.5 \text{ x N}} \leq R_{pull}$$

$$R_{pull:} Pull up Resistor (k\Omega)$$

$$V_{CC:} Power Supply Voltage (V)$$

$$N: Number of Slave ICs$$

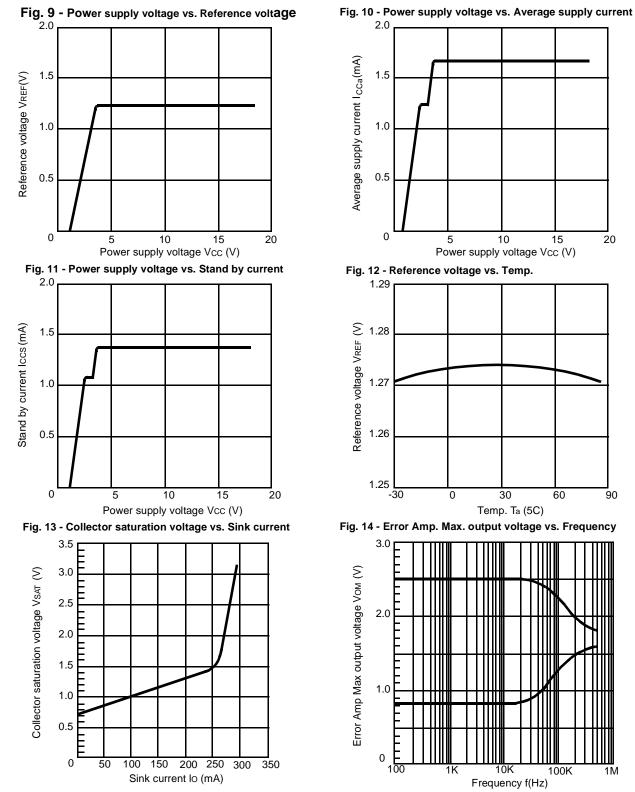

### ■ TYPICAL PERFORMANCE CHARACTERISTICS

#### ■ TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

# ■ TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

#### APPLICATION

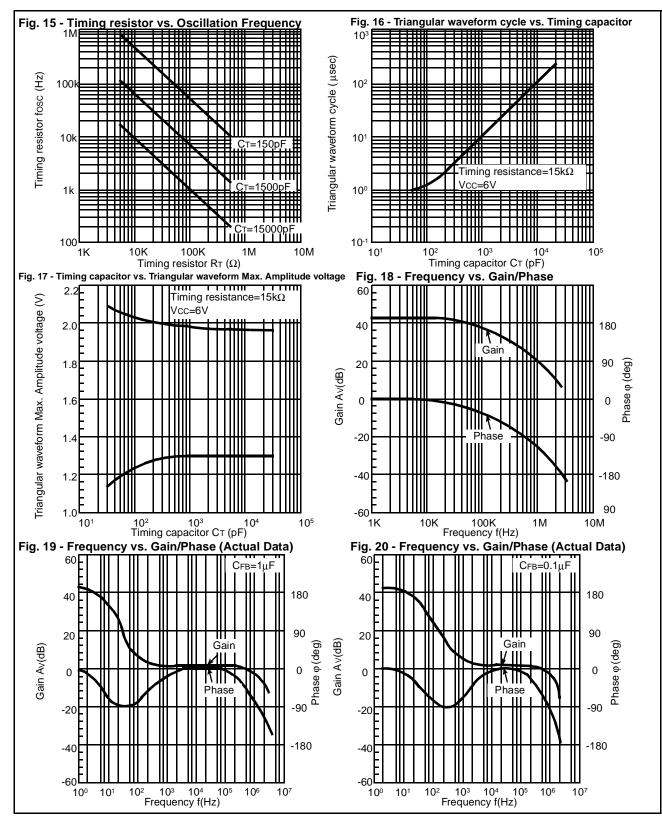

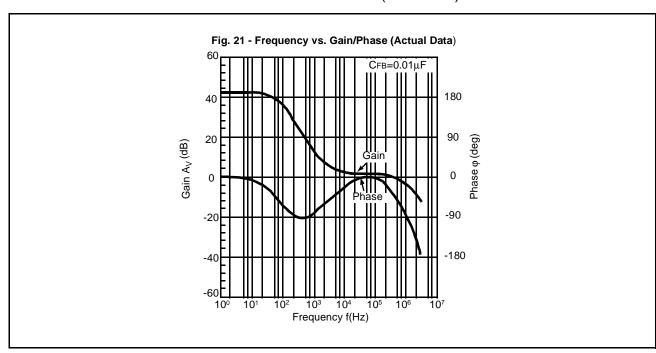

#### 1. How to set the error amplifier frequency characteristic

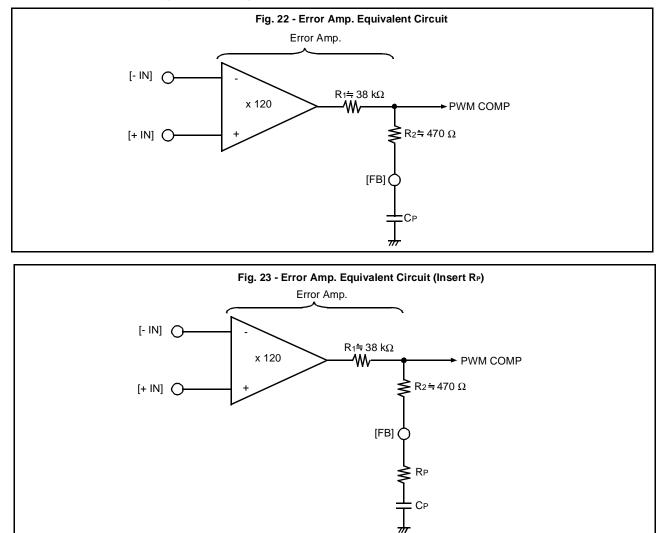

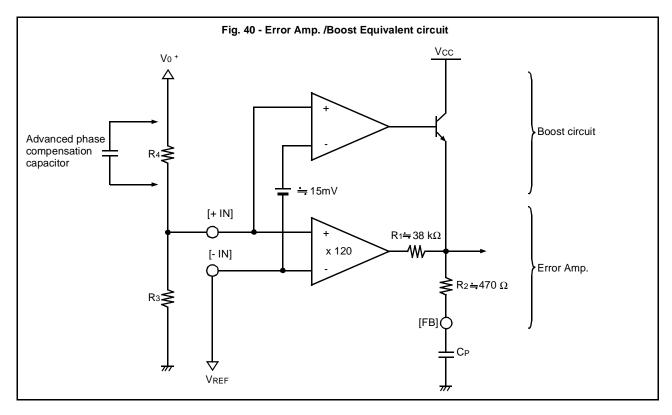

Figure 22 shows the equivalent circuit of the error amplifier.

The frequency characteristic of the error amplifier is set by  $R_1$ ,  $R_2$ , and  $C_P$ . The high-frequency gain is set by the ratio of resistors  $R_1$  and  $R_2$  in the IC (set value  $\doteq 0$  dB).

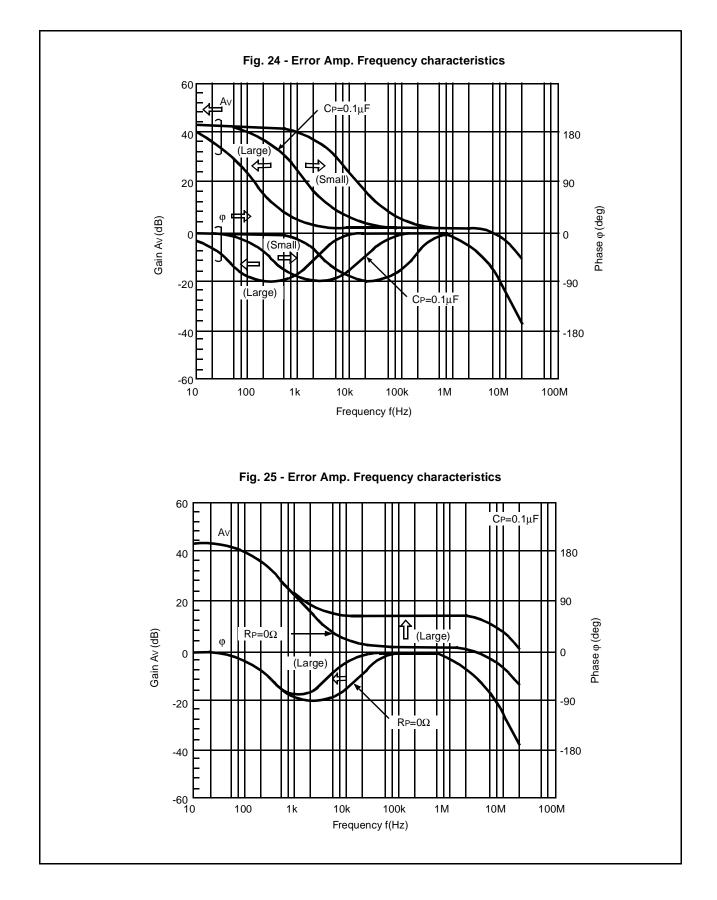

When  $C_P = 0.1 \mu F$ , the gain at 20 kHz  $\leq$  f  $\leq$  5 MHz is about 0 dB. The roll-off frequency is adjusted by changing external phase compensating capacitor  $C_P$  (see Fig. 24).

When high frequency gain is needed or the phase must be advanced at a low frequency, connect a resistor R<sub>P</sub> between the FB terminal and C<sub>P</sub> as shown in Figure 23 (see Fig. 25).

**NOTE:** As shown above, the frequency characteristic of the error amplifier is set by the external phase compensating capacitor CP.

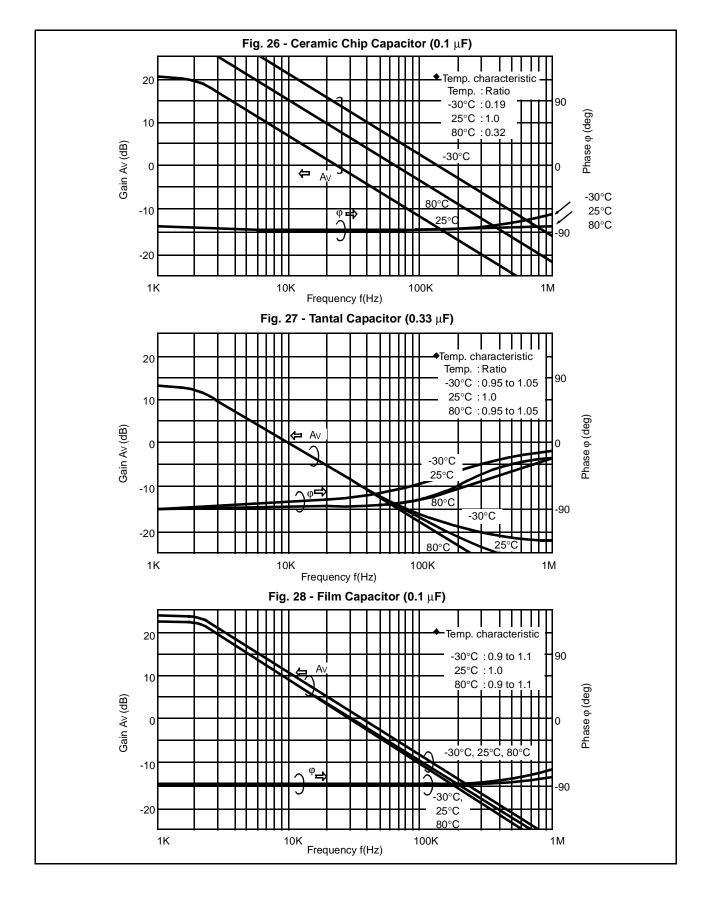

When a ceramic chip capacitor must be used to meet the requirements of a small system, be careful of its temperature characteristic. (-30 °C=1/5 and 80 °C=1/3 for the frequency characteristic, so a sufficient phase margin must be allowed for at room temperature.) Ceramic chip capacitors with a low temperature characteristic (B characteristic) or film capacitors are recommended (see Fig. 26 to 28).

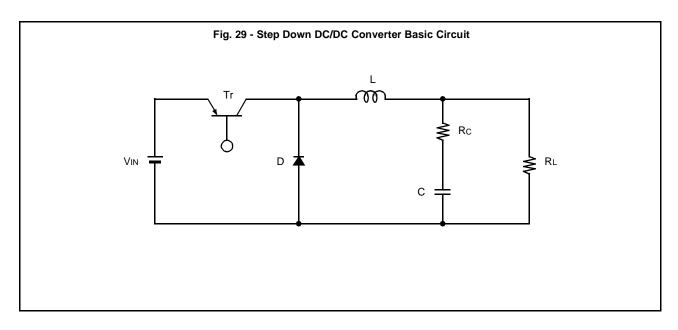

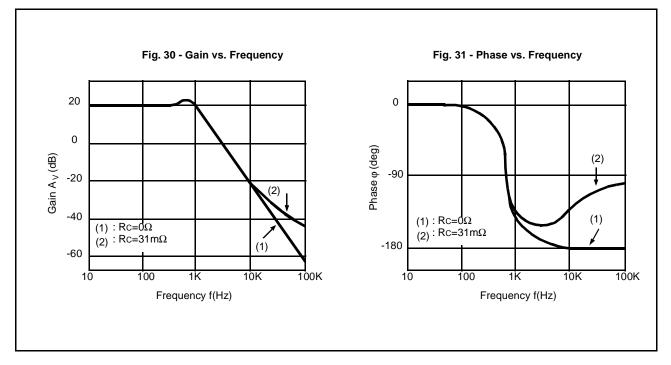

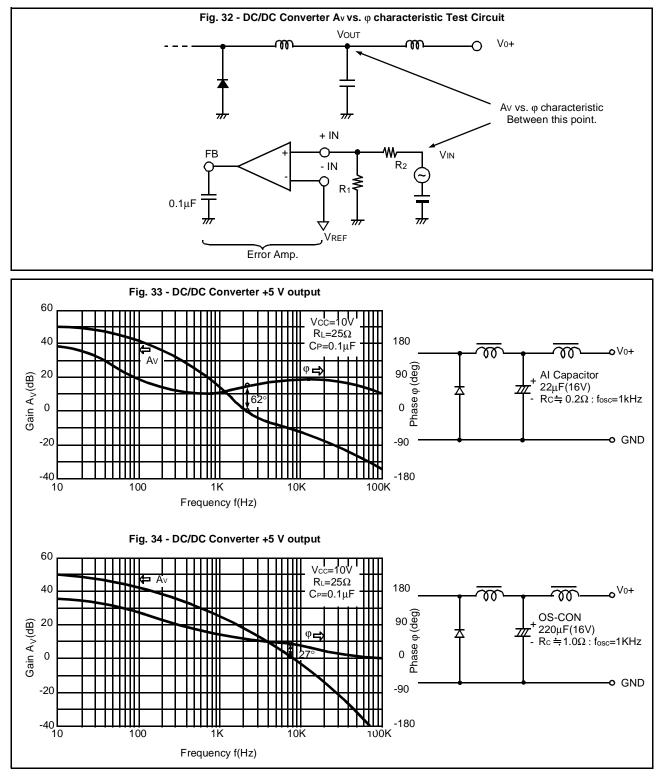

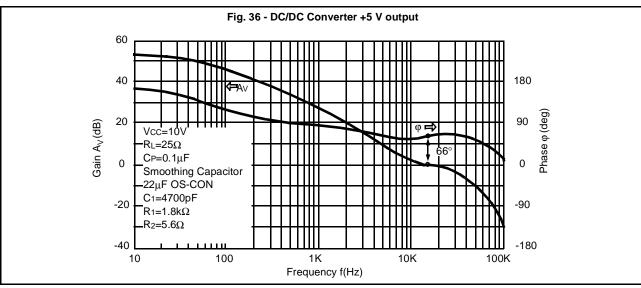

## 2. Effect of equivalent series resistance of smoothing capacitor

The equivalent series resistance (ESR) of the smoothing capacitor in the DC/DC converter greatly affects the loop phase characteristic. A smoothing capacitor with a low ESR reduces system stability by increasing the phase shift in the high-frequency region (see Fig. 30). Therefore, a smoothing capacitor with a high ESR will improve system stability. Be careful when using low ESR semiconductor electrolytic capacitors (OS-CON) and tantalum capacitors.

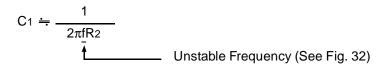

#### **Reference data**

If an aluminum electrolytic smoothing capacitor ( $Rc = 1.0\Omega$ ) is replaced with a low ESR semiconductor electrolytic capacitor (OS-CON:  $Rc = 0.2 \Omega$ ), the phase shift is reduced by half (see Fig. 33 and 34).

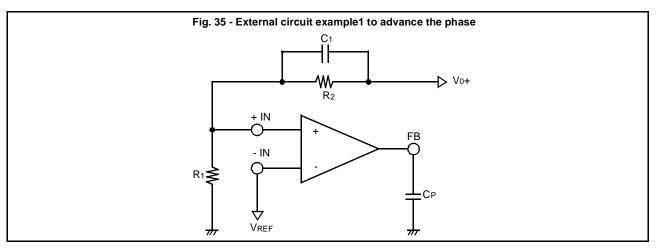

#### 3. Measures for ensuring system stability when a low ESR smoothing capacitor is used

When a low ESR smoothing capacitor is used in the DC/DC converter, only the L and C are apparent even in the high-frequency region, and the phase is delayed by almost 1805. Consequently, the system phase margin and stability are reduced. On the other hand, a low ESR capacitor is needed to reduce the amount of output ripple. This is contrary to the system stability explained above. To solve this problem, phase compensation can be used. This method increases the phase margin by advancing the phase when the phase margin is reduced by a low ESR capacitor.

The three suggestions listed below are recommended for DC/DC converters using the MB3775.

(1) As shown in Fig. 35, a capacitor is connected in parallel with the output feedback resistor to advance the phase. Use the formula below as a guideline for the capacitance.

# 3. Measures for ensuring system stability when a low ESR smoothing capacitor is used (Continued)

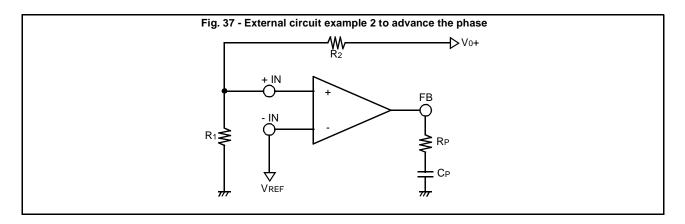

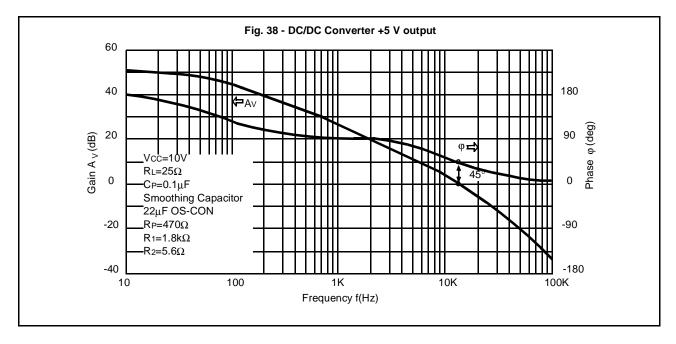

(2) As shown in Figure 37, a resistor (R<sub>P</sub>) is connected between the FB terminal and C<sub>P</sub> of the error amplifier to advance the phase. The more R<sub>P</sub> is increased, the more the phase is advanced. However, the gain in the high-frequency range is also increased, which causes instability. Therefore, select the optimum resistance (see Fig. 38).

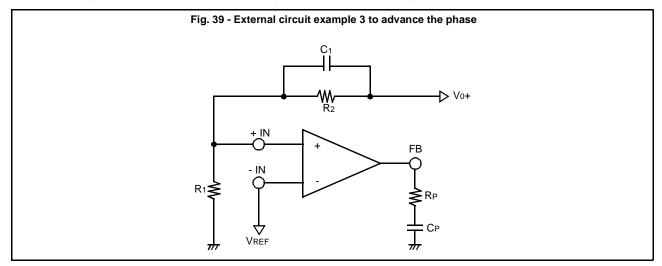

(3) As shown in Fig. 39, the phase is advanced by using both example 1 and 2 (Fig. 35 and 37).

#### 4. Error amplifier input ripple voltage

The boost circuit for charging the phase compensating capacitor  $C_P$  is connected to the error amplifier as shown in Figure 40 to protect against output voltage overload at power-on.

A 15 mV offset voltage is provided for the negative input side so that the boost circuit only operates at power-on. When a capacitor is connected in parallel with the output feedback resistor, because the output ripple is too large or for advanced phase compensation, the boost circuit starts operating, which may degrade regulation if the differential input voltage of the error amplifier exceeds 15 mV. Be careful with the differential input voltage of the error amplifier.

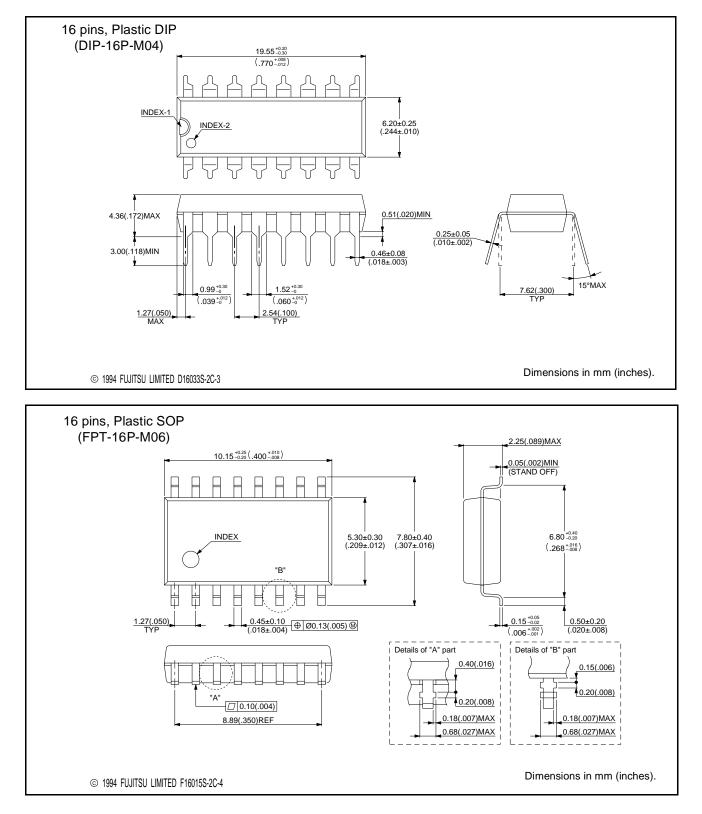

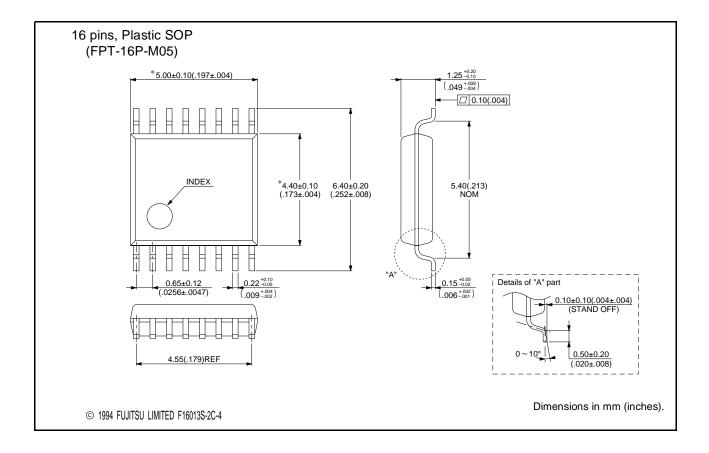

#### ■ PACKAGE DIMENSIONS

# FUJITSU LIMITED

#### All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

F9803 © FUJITSU LIMITED Printed in Japan