# $\mu$ P Compatible High-Speed 8-Bit A/D Converter with T/H (S/H)

#### **GENERAL DESCRIPTION**

The ML2261 is a high-speed,  $\mu P$  compatible 8-bit A/D converter with a conversion time of 670ns over the operating temperature range and supply voltage tolerance. The ML2261 operates from a single 5V supply and has an analog input range from GND to V<sub>CC</sub>.

The ML2261 has two different pin selectable modes. The T/H mode has an internal track and hold. The S/H mode has a true internal sample and hold and can digitize 0 to 5V sinusoidal signals as high as 500kHz. Timing is compatible with the AD7821.

The ML2261 digital interface has been designed so that the device appears as a memory location or I/O port to a  $\mu$ P.

The ML2261 is an enhanced, pin compatible second source for the industry standard ADC0820 and AD7820. The ML2261 enhancements are faster conversion time, parameters guaranteed over the supply tolerance and temperature range, improved digital interface timing, superior power supply rejection, and better latchup immunity on analog inputs.

#### **FEATURES**

- Conversion time, WR-RD mode over temperature and supply voltage tolerance

- Total unadjusted error ......  $\pm 1/2$  LSB or  $\pm 1$  LSB

- Digitizes a 5V, 250kHz sine wave to 8-bit accuracy

- No missing codes

- 0V to 5V analog input range with single 5V power supply

- No zero or full scale adjust required

- Analog input protection ...... 25mA min

- Operates ratiometrically or with up to 5V voltage reference

- No external clock required

- Easy interface to  $\mu$ P, or operates stand alone

- Power-on reset circuitry

- Low power ...... 75mW

- Standard 20-pin DIP or surface mount PCC

- Superior pin compatible replacement for ADC0820 and AD7820

#### **BLOCK DIAGRAM**

#### GND SH/TH $+V_{REF}$ 4-BIT FLASH OFL A/D (MSB) -VREE DECODE -O DB7 VINO +V<sub>REF</sub> -O DB6 LATCH -O DB5 4-BIT THREE -O DB4 HÕLD STATE -O DB3 OUTPUT O DB2 BUFFER +V<sub>REF</sub> O DRI 4-RIT 16 -O DB0 A/D (LSB) -V<sub>REE</sub> 16 TIMING o INT CONTROL SH/TH MODE CS WR/RDY RD

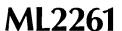

### PIN CONNECTIONS

### **PIN DESCRIPTION**

| PIN NO. | NAME            | FUNCTION                                                                                                                        | PIN NO.                              | NAME              | FUNCTION                                                                                            |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|

| 1       | V <sub>IN</sub> | Analog input.                                                                                                                   | 10                                   | GND               | Ground.                                                                                             |

| 2       | DB0             | Data output — bit 0 (LSB).                                                                                                      | 11                                   | -V <sub>REF</sub> | Negative reference voltage for                                                                      |

| 3       | DB1             | Data output — bit 1.                                                                                                            |                                      |                   | A/D converter.                                                                                      |

| 4       | DB2             | Data output — bit 2.                                                                                                            | 12                                   | $+V_{REF}$        | Positive reference voltage for A/D converter.                                                       |

| 5       | DB3             | Data output — bit 3.                                                                                                            | 13                                   | CS                | Chip select input. This pin must                                                                    |

| 6       | WR/RDY          | Write input or ready out <u>put.</u> In WR-RD mode, this pin is WR input. In RD mode, this pin is                               | 13                                   | C3                | be held low for the device to perform a conversion.                                                 |

|         |                 | RDY open drain output. See                                                                                                      | 14                                   | DB4               | Data output — bit 4.                                                                                |

|         |                 | Digital Interface section.                                                                                                      | 15                                   | DB5               | Data output — bit 5.                                                                                |

| 7       | MODE            | Mode select input.                                                                                                              | 16                                   | DB6               | Data output — bit 6.                                                                                |

|         |                 | MODE = GND: RD mode<br>MODE = V <sub>CC</sub> : WR-RD mode                                                                      | 17                                   | DB7               | Data output — bit 7 (MSB).                                                                          |

|         |                 | Pin has internal current source pulldown to GND.                                                                                | 18                                   | OFL               | Overflow output. This output goes low at end of conversion                                          |

| 8       | RD              | Read input. In RD mode, this pin initiates a conversion. In                                                                     |                                      |                   | if V <sub>IN</sub> is greater than<br>+V <sub>REF</sub> – ½LSB.                                     |

|         |                 | WR-RD mode, this pin latches data into output latches. See Digital Interface section.                                           | 19                                   | SH/TH             | S/H, T/H mode select. When SH/TH = V <sub>CC</sub> , the device is in sample and hold mode. When    |

| 9       | INT             | Interrupt output. This output signals the end of a conversion and indicates that data is valid on the data outputs. See Digital | of a conversion<br>nat data is valid |                   | SH/TH = GND, the device is in track and hold mode. Pin has internal pulldown current source to GND. |

|         |                 | Interface section.                                                                                                              | 20                                   | $V_{CC}$          | Positive supply. +5 volts $\pm$ 5%.                                                                 |

## ABSOLUTE MAXIMUM RATINGS (Note 1)

| Supply Voltage, V <sub>CC</sub> 6           | .5V |

|---------------------------------------------|-----|

| Voltage                                     |     |

| Logic Inputs0.3V to V <sub>CC</sub> + 0     | .3V |

| Analog Inputs0.3V to V <sub>CC</sub> + 0    |     |

| Input Current per Pin (Note 2)±25           | mΑ  |

| Storage Temperature65°C to +150             |     |

| Package Dissipation                         |     |

| at T <sub>A</sub> = 25°C (Board Mount) 875n | nW  |

| Lead Temperature (Soldering 10 sec.)        |     |

| Dual-In-Line Package (Plastic)              | O°C |

| Dual-In-Line Package (Ceramic) 300          | O°C |

| Molded Chip Carrier Package                 |     |

| Vapor Phase (60 sec.)                       | 5°C |

| Infrared (15 sec.)                          | 0°C |

|                                             |     |

### **OPERATING CONDITIONS**

| Supply Voltage, V <sub>CC</sub> | 4.5V <sub>DC</sub> to 6.0V <sub>DC</sub> |

|---------------------------------|------------------------------------------|

| Temperature Range (Note 3       | ) $T_{MIN} \leq T_A \leq T_{MAX}$        |

| ML2261BCQ, ML2261CCQ            | )                                        |

| ML2261BCP, ML2261CCP            | 0°C to +70°C                             |

**ELECTRICAL CHARACTERISTICS** Unless otherwise specified,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC}$  = + $V_{REF}$  = 5V  $\pm$  5%, and - $V_{REF}$  = GND

|                                                     |       |                                                                      |                                                     | ML2261XCX             |                 |                      | ML2261XIX            |                 |                      |            |  |    |

|-----------------------------------------------------|-------|----------------------------------------------------------------------|-----------------------------------------------------|-----------------------|-----------------|----------------------|----------------------|-----------------|----------------------|------------|--|----|

| PARAMETER                                           | NOTES | CONDITIONS                                                           |                                                     | MIN                   | TYP<br>(Note 4) | MAX                  | MIN                  | TYP<br>(Note 4) | MAX                  | UNITS      |  |    |

| Converter                                           | •     |                                                                      |                                                     |                       | ,               |                      | •••                  |                 |                      |            |  |    |

| Total Unadjusted Error<br>ML2261BXX<br>ML2261CXX    | 5, 7  | V <sub>REF</sub> = V <sub>CC</sub>                                   |                                                     |                       |                 | ±1/2<br>±1           |                      |                 | ±1/2<br>±1           | LSB<br>LSB |  |    |

| +V <sub>REF</sub> Voltage Range                     | 6     |                                                                      |                                                     | -V <sub>REF</sub>     |                 | V <sub>CC</sub> +0.1 | -V <sub>REF</sub>    |                 | V <sub>CC</sub> +0.1 | V          |  |    |

| -V <sub>REF</sub> Voltage Range                     | 6     |                                                                      |                                                     | GND-0.1               |                 | +V <sub>REF</sub>    | GND-0.1              |                 | +V <sub>REF</sub>    | V          |  |    |

| Reference Input<br>Resistance                       | 5     |                                                                      |                                                     | 1                     | 2               | 3                    | 1                    | 2               | 3                    | kΩ         |  |    |

| Analog Input Range                                  | 5, 8  |                                                                      |                                                     | GND-0.1               |                 | V <sub>CC</sub> +0.1 | GND-0.1              |                 | V <sub>CC</sub> +0.1 | V          |  |    |

| Power Supply Sensitivity                            | 5     | DC<br>V <sub>CC</sub> = 5V =                                         | ± 5%, V <sub>REF</sub> = 4.75V                      | _                     | ±1/32           | ±1/4                 |                      | ±1/32           | ±1/4                 | LSB        |  |    |

|                                                     |       | 100mVp-p<br>100kHz sind<br>V <sub>IN</sub> = 0                       | e on V <sub>CC</sub> ,                              |                       | ±1/16           |                      |                      | ±1/16           |                      | LSB        |  |    |

| Analog Input Leakage<br>Current                     | 5, 9  | Converter Idle                                                       |                                                     | -1                    |                 | +1                   | -1                   |                 | +1                   | μΑ         |  |    |

| Analog Input Capacitance                            |       | During Acquisition Period                                            |                                                     |                       | 45              |                      |                      | 45              |                      | ρF         |  |    |

| Digital and DC                                      |       |                                                                      |                                                     | •                     |                 |                      |                      |                 |                      |            |  |    |

| V <sub>IN(1)</sub> , Logical "1" Input              | 5     | $\overline{WR}$ , $\overline{RD}$ , $\overline{CS}$                  |                                                     | 2.0                   |                 |                      | 2.0                  | <del>-</del>    |                      | V          |  |    |

| Voltage                                             |       | MODE, SH                                                             | /TH                                                 | V <sub>CC</sub> -0.5  |                 |                      | V <sub>CC</sub> -0.5 |                 |                      | V          |  |    |

| V <sub>IN(0)</sub> , Logical "0" Input              | 5     | $\overline{WR}$ , $\overline{RD}$ , $\overline{C}$                   | <del></del> <del>S</del>                            |                       |                 | 0.8                  |                      | _               | 0.8                  | V          |  |    |

| Voltage                                             |       | MODE, SH                                                             | /TH                                                 |                       |                 | 0.5                  |                      |                 | 0.5                  | V          |  |    |

| I <sub>IN(1)</sub> , Logical "1"                    | 5     | V <sub>IH</sub> = V <sub>CC</sub>                                    | $\overline{WR}$ , $\overline{RD}$ , $\overline{CS}$ |                       |                 | 1                    |                      |                 | 1                    | μΑ         |  |    |

| Input Current                                       |       |                                                                      | MODE, SH/TH                                         | 15                    | 50              | 150                  | 15                   | 50              | 150                  | μΑ         |  |    |

| I <sub>IN(0)</sub> , Logical "0"                    | 5     | 5                                                                    | 5                                                   | V <sub>IL</sub> = GND | WR, RD, CS      | -1                   |                      |                 | -1                   |            |  | μΑ |

| Input Current                                       | ,     | AIL - GIAD                                                           | MODE, SH/TH                                         | -20                   |                 |                      | -20                  |                 |                      | μΑ         |  |    |

| V <sub>OUT(1)</sub> , Logical "1"<br>Output Voltage | 5     | l <sub>OUT</sub> = -2m                                               | A                                                   | 4.0                   |                 |                      | 4.0                  |                 |                      | V          |  |    |

| V <sub>OUT(0)</sub> , Logical "0"<br>Output Voltage | 5     | I <sub>OUT</sub> = 2m <sup>A</sup>                                   | (                                                   |                       |                 | 0.4                  |                      |                 | 0.4                  | V          |  |    |

| I <sub>OUT</sub> , Three-State Output               | _     | $V_{OUT} = 0V$                                                       |                                                     | -1                    |                 |                      | -1                   |                 |                      | μΑ         |  |    |

| Current                                             | 5     | V <sub>OUT</sub> = V <sub>CC</sub>                                   |                                                     |                       |                 | 1                    |                      |                 | 1                    | μΑ         |  |    |

| C <sub>OUT</sub> , Logic Output<br>Capacitance      |       |                                                                      |                                                     |                       | 5               |                      |                      | 5               |                      | pF         |  |    |

| C <sub>IN</sub> , Logic Input<br>Capacitance        |       |                                                                      |                                                     |                       | 5               |                      |                      | 5               |                      | pF         |  |    |

| I <sub>CC</sub> , Supply Current                    |       | $\overline{CS} = \overline{WR} = \overline{RD} = "1"$ No Output Load |                                                     |                       | 8               | 14                   |                      | 8               | 15.5                 | mA         |  |    |

**ELECTRICAL CHARACTERISTICS** (Continued) Unless otherwise specified,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC}$  = + $V_{REF}$  = 5V  $\pm$  5%, - $V_{REF}$  = GND, and timing measured at 1.4V,  $C_L$  = 100pF.

|                                                                                 |          | res Conditions                                                                                                                                                                                                                                  |                                               | ML2261XCX           |      |      | ML2261XIX |                                              |      |       |

|---------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------|------|------|-----------|----------------------------------------------|------|-------|

| PARAMETER                                                                       | NOTES    |                                                                                                                                                                                                                                                 |                                               | TYP MIN (Note 4) MA |      | MAX  | MIN       | TYP<br>(Note 4)                              | MAX  | UNITS |

| AC and Dynamic Performan                                                        | ce (Note | 9)                                                                                                                                                                                                                                              |                                               |                     |      |      |           |                                              |      |       |

| t <sub>CRD</sub> , Conversion Time,<br>Read Mode                                | 5        | RD to INT, M                                                                                                                                                                                                                                    | ODE = 0V                                      | į                   |      | 1060 |           |                                              | 1100 | ns    |

| t <sub>CWR-RD</sub> , Conversion Time,<br>Write-Read Mode                       | 5, 9     | WR Falling<br>Edge to INT,                                                                                                                                                                                                                      | SH/TH=V <sub>CC</sub>                         |                     | 650  | 700  |           | 690                                          | 740  | ns    |

|                                                                                 |          | $t_{RD} < t_{INT},$ $MODE = V_{CC}$                                                                                                                                                                                                             | SH/TH=GND                                     |                     |      | 850  |           |                                              | 920  | ns    |

| SNR, Signal to Noise Ratio                                                      |          | V <sub>IN</sub> = 5V, 250k<br>Noise is sum<br>nonfundamen<br>components<br>from 0-500kH<br>SH/TH = V <sub>CC</sub><br>f <sub>SAMPLING</sub> = 1                                                                                                 | of all<br>tal<br>z.<br>MODE = V <sub>CC</sub> | ,                   | 48   |      |           | 48                                           |      | dB    |

| HD, Harmonic Distortion                                                         |          | V <sub>IN</sub> = 5V, 250kHz<br>THD is sum of 2–5th<br>harmonics relative to<br>fundamental.<br>SH/TH = V <sub>CC</sub> , MODE = V <sub>CC</sub><br>f <sub>SAMPLING</sub> = 1 MHz                                                               |                                               |                     | -63  |      |           | -63                                          |      | dB    |

| IMD, Intermodulation<br>Distortion                                              |          | fa = 2.5V, 250kHz<br>fb = 2.5V, 248kHz<br>IMB is (fa + fb), (fa - fb),<br>(2fa + fb), (2fa - fb),<br>(fa + 2fb), or (fa - 2fb)<br>relative to fundamental.<br>SH/TH = V <sub>CC</sub> , MODE = V <sub>CC</sub><br>f <sub>SAMPLING</sub> = 1 MHz |                                               |                     | -60  |      |           | -60                                          |      | dB    |

| FR, Frequency Response                                                          |          | V <sub>IN</sub> = 5V, 0-25<br>Relative to 1kl<br>SH/TH = V <sub>CC</sub> ,<br>f <sub>SAMPLING</sub> = 1                                                                                                                                         | Hz<br>MODE = V <sub>CC</sub>                  |                     | ±0.1 | ,    |           | ±0.1                                         |      | dB    |

| SR, Slew Rate Tracking                                                          | 6        | SH/TH = V <sub>CC</sub>                                                                                                                                                                                                                         |                                               |                     |      | 4.0  |           |                                              | 4.0  | V/µs  |

|                                                                                 |          | SH/TH = GND                                                                                                                                                                                                                                     | )                                             | _                   |      | .25  | '         |                                              | .25  | V/μs  |

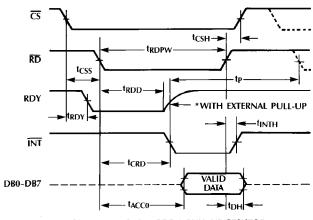

| AC Performance Read Mode                                                        | (Pin 7   | = 0V), Figure 2                                                                                                                                                                                                                                 |                                               |                     |      |      |           | <del>    -   -   -   -   -   -   -   -</del> |      |       |

| t <sub>RDY</sub> , CS to RDY Delay                                              | 5        |                                                                                                                                                                                                                                                 |                                               | 0                   |      | 65   | 0         |                                              | 70   | ns    |

| t <sub>RDD</sub> , RD Low to<br>RDY Delay                                       | 5, 10    | Figure 1                                                                                                                                                                                                                                        |                                               |                     |      | 1060 |           |                                              | 1100 | ns    |

| t <sub>CSS</sub> , <del>CS</del> to <del>RD</del> , <del>WR</del><br>Setup Time |          |                                                                                                                                                                                                                                                 |                                               | 0                   |      |      | 0         |                                              |      | ns    |

| t <sub>CSH</sub> , CS to RD, WR<br>Hold Time                                    | 5        |                                                                                                                                                                                                                                                 |                                               | 0                   |      |      | 0         |                                              |      | ns    |

| t <sub>CRD</sub> , Conversion Time —<br>RD Low to INT Low                       | 5, 10    |                                                                                                                                                                                                                                                 |                                               |                     |      | 1060 |           |                                              | 1100 | ns    |

**ELECTRICAL CHARACTERISTICS** (Continued) Unless otherwise specified,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC}$  = + $V_{REF}$  = 5V  $\pm$  5%, - $V_{REF}$  = GND, and timing measured at 1.4V,  $C_L$  = 100pF

|                                                                                                            |        |                                                |                      | ML2261XCX |                      |                      | ML2261XI)       | (                    | UNITS |

|------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------|----------------------|-----------|----------------------|----------------------|-----------------|----------------------|-------|

| PARAMETER                                                                                                  | NOTES  | CONDITIONS                                     | TYP MIN (Note 4)     |           | MAX                  | MIN                  | TYP<br>(Note 4) | MAX                  |       |

| AC Performance Read Mode                                                                                   | (Pin 7 | = <b>0V</b> ), <b>Figure 2</b> (Continued)     |                      |           | •                    | •                    |                 | •                    |       |

| t <sub>ACC0</sub> , Data Access Time<br>RD to Data Valid                                                   | 5      |                                                | t <sub>CRD</sub>     |           | t <sub>CRD</sub> +30 | t <sub>CRD</sub>     |                 | t <sub>CRD</sub> +30 | ns    |

| t <sub>RDPW</sub> , RD Pulse Width                                                                         | 5      |                                                | t <sub>CRD</sub> +30 |           |                      | t <sub>CRD</sub> +30 |                 |                      | ns    |

| t <sub>INTH</sub> , RD to INT Delay                                                                        | 5, 10  |                                                | 0                    |           | 65                   | 0                    |                 | 70                   | ns    |

| t <sub>DH</sub> , Data Hold Time —<br>RD Rising Edge to Data<br>High Impedance State                       | 6, 10  | Figure 1                                       | 0                    |           | 50                   | 0                    |                 | 60                   | ns    |

| t <sub>P</sub> , Delay Time <u>Between</u><br>Conversions — <u>INT</u> Low                                 | 5, 10  | Sample & Hold Mode,<br>SH/TH = V <sub>CC</sub> | 300                  |           | į                    | 325                  |                 |                      | ns    |

| to RD Low                                                                                                  |        | Track & Hold Mode,<br>SH/TH = GND              | 240                  |           |                      | 260                  |                 |                      | ns    |

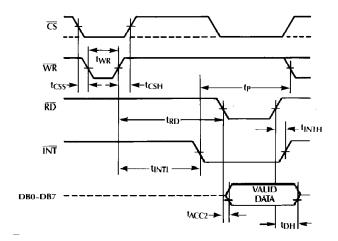

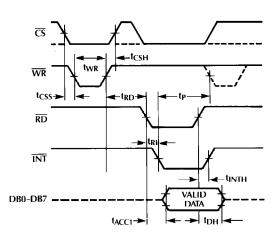

| AC Performance Write-Read                                                                                  | Mode ( | Pin 7 = 5V), Figures 3 and 4                   | •                    |           |                      |                      | •               |                      |       |

| t <sub>CSS</sub> , $\overline{\text{CS}}$ to $\overline{\text{RD}}$ , $\overline{\text{WR}}$<br>Setup Time | 5      |                                                | 0                    |           |                      | 0                    |                 |                      | ns    |

| t <sub>CSH</sub> , CS to RD, WR<br>Hold Time                                                               | 5      |                                                | 0                    |           |                      | 0                    |                 |                      | ns    |

| VA/D. D. J VA/C-lab                                                                                        | 5      | $SH/\overline{TH} = V_{CC}$                    | 170                  |           | 50K                  | 180                  |                 | 50K                  | ns    |

| t <sub>WR</sub> , WR Pulse Width                                                                           | 6      | SH/TH = GND                                    | 320                  |           | 50K                  | 360                  |                 | 50K                  | ns    |

| t <sub>RD</sub> , Read Time — WR<br>High to RD Low Delay                                                   | 5      | $t_{RD} < t_{INTL}$                            | 275                  |           |                      | 290                  |                 |                      | ns    |

| t <sub>RI</sub> , RD to INT Delay                                                                          | 5, 10  | $t_{RD} < t_{INTL}$                            | 0                    |           | 255                  | 0                    |                 | 270                  | ns    |

| t <sub>ACC1</sub> , Data Access Time<br>— RD Low to Data Valid                                             | 5      | $t_{RD} < t_{INTL}$                            | 0                    |           | 260                  | 0                    |                 | 280                  | ns    |

| t <sub>CWR-RD</sub> , Conversion Time                                                                      | 5,9,10 | $t_{RD} < t_{INTL} SH/\overline{TH} = V_{CC}$  |                      | 650       | 700                  |                      | 690             | 740                  | ns    |

| — WR Falling Edge to INT Low                                                                               | 6,9,10 | $t_{RD} < t_{INTL}$ , SH/TH = GND              |                      |           | 850                  |                      |                 | 920                  | ns    |

| t <sub>INTL</sub> Internal Comparison Time — WR Rising Edge to INT Low                                     | 5, 10  | $t_{RD} > t_{INTL}$                            |                      |           | 650                  |                      |                 | 670                  | ns    |

| t <sub>ACC2</sub> , Data Access Time<br>— RD to Data Valid                                                 | 5      | $t_{RD} > t_{INTL}$                            | 0                    |           | 50                   | 0                    |                 | 60                   | ns    |

| t <sub>DH</sub> , Data Hold Time —<br>RD Rising Edge to Data<br>High Impedance State                       | 6, 10  | Figure 1                                       | 0                    |           | 50                   | 0                    |                 | 60                   | ns    |

| t <sub>INTH</sub> , RDt to INTt Delay                                                                      | 5, 10  |                                                | 0                    |           | 65                   | 0                    |                 | 70                   | ns    |

| t <sub>P</sub> , Delay Time <u>Between</u><br>Conversions — <u>INT</u> Low                                 | 5, 10  | Sample & Hold Mode,<br>SH/TH = V <sub>CC</sub> | 300                  |           |                      | 325                  |                 |                      | ns    |

| to WR Low                                                                                                  |        | Track & Hold Mode,<br>SH/TH = GND              | 240                  |           |                      | 260                  |                 |                      | ns    |

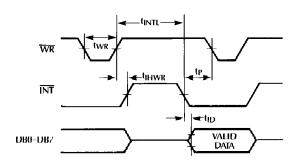

| t <sub>IHWR</sub> , WRt to INTt Delay                                                                      | 5, 10  | Standalone Mode                                | 0                    |           | 100                  | 0                    |                 | 110                  | ns    |

| t <sub>ID</sub> , INTI to Data<br>Valid Delay                                                              | 5, 10  | Standalone Mode                                | 0                    |           | 20                   | 0                    |                 | 30                   | ns    |

- Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with respect to ground.

- Note 2: When the voltage at any pin exceeds the power supply rails (V<sub>IN</sub> < GND or V<sub>IN</sub> > V<sub>CC</sub>) the absolute value of current at that pin should be limited to 25mA or less.

- Note 3: 0°C to 70°C operating temperature range devices are 100% tested with temperature limits guaranteed by 100% testing, sampling, or by correlation with worst-case test conditions.

- Note 4: Typicals are parametric norm at 25°C.

- Note 5: Parameter guaranteed and 100% production tested.

- Note 6: Parameter guaranteed. Parameters not 100% tested are not in outgoing quality level calculation.

- Note 7: Total unadjusted error includes offset, full scale, linearity, and sample and hold errors. Total unadjusted error is tested at the minimum specified times for WR, RD, t<sub>RI</sub>, and t<sub>P</sub>. For example, for the ML2261XCX in the sample and hold mode, WR/RD mode: t<sub>WR</sub> = 170ns, t<sub>RD</sub> = 275ns with a frequency of 1.000MHz (cycle time of 1.000ns)

- Note 8: For -V<sub>REF</sub> ≥ V<sub>IN</sub> the digital output code will be 0000 0000. Two on-chip diodes are tied to the analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the V<sub>CC</sub> supply. Be careful, during testing at low V<sub>CC</sub> levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct especially at elevated temperatures, and cause errors for analog inputs near full scale. This spec allows 100mV forward bias of either diode. This means that as long as the analog V<sub>IN</sub> or V<sub>REF</sub> does not exceed the supply voltage by more than 100mV, the output code will be correct. To achieve an absolute 0V<sub>DC</sub> to 5V<sub>DC</sub> input range will therefore require a minimum supply voltage of 4.900V<sub>DC</sub> over temperature variations, initial tolerance and loading.

- Note 9: Conversion time, write-read mode =  $t_{WR} + t_{RD} + t_{RI}$ .

- Note 10: Defined from the time an input crosses 0.8V or 2.4V.

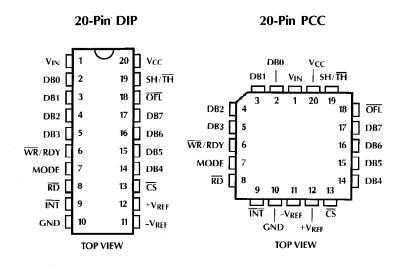

Figure 1. High Impedance Test Circuits and Waveforms

\* IN SAMPLE & HOLD MODE A PULL UP RESISTOR ON RDY SHOULD NOT BE USED UNLESS CSI IS  $\geq$  20ns before RDI.

Figure 2. RD Mode Timing

Figure 3. WR-RD Mode Timing  $(t_{RD} > t_{INTL})$

Figure 4. WR-RD Mode Timing  $(t_{RD} < t_{INTL})$

Figure 5. WR-RD Mode Stand-Alone Timing  $\overline{CS} = \overline{RD} = 0$

### 1.0 FUNCTIONAL DESCRIPTION

The ML2261 uses a two stage flash technique for A/D conversion. This technique first performs a 4 bit flash conversion on  $V_{\text{IN}}$  to determine the 4 MSB's. These 4 MSB's are then cycled through an internal DAC to recreate the analog input. This reconstructed analog input signal from the DAC is then subtracted from the input, and the difference voltage is converted by a second 4 bit flash conversion, providing the 4 LSB's of the output data word. An additional overrange function detects if  $V_{\text{IN}}$  is greater than  $+V_{\text{REF}}$  – 1/2LSB.

#### 1.1 ANALOG INPUT

The analog input on the ML2261 behaves differently from inputs on conventional converters. The analog input current requirements change while the conversion is in progress, and the amount of input current depends on what cycle the converter is in.

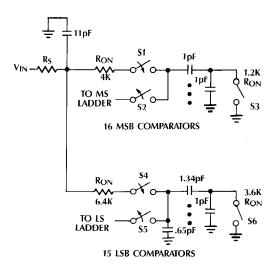

The equivalent input circuit for the converter is shown in Figure 6. When the conversion starts in the T/H mode (WR1 in the WR-RD mode or RD1 in the RD mode) S1, S4 and S6 close and S3 opens. This period is known as the acquisition period where the MSB flash converter tracks the input signal and the LSB flash converter samples it. During this period, VIN is connected to the 16 MSB and 15 LSB comparators. Thus 38 pF of input capacitance must be charged up through the combined RON resistance of the internal analog switches plus any external source resistance, Rs. In addition, there is a stray capacitance of approximately 11 pF that needs to be charged through the external source resistance R<sub>S</sub>. This period ends in the WR-RD mode when WR1 or by an internal timer in the RD mode. At this point \$1 and \$4 open and the analog input at V<sub>IN</sub> is no longer being sampled; thus during this time the analog voltage on V<sub>IN</sub> does not affect converter performance.

Figure 6. Converter Equivalent Input Circuit

As shown above, the critical period for charging up the analog input occurs when the MSB and LSB comparators are sampling the input, known as the acquisition period. The source of the external signal on V<sub>IN</sub> must adequately charge up the analog voltage during the acquisition period. To do this, the input must settle within the required analog accuracy tolerance at least 50ns before the end of the acquisition period so that the MSB comparators have adequate time to make the correct decision. If more time is needed due to finite charging or settling time of the external source, the WR low period can be extended in WR-RD mode. In RD mode, since the acquisition time is fixed by internal delays, the burden is on the external source to charge up and settle the input adequately.

When the ML2261 operates in the S/H mode (pin 19 =  $V_{CC}$ ) both the MSB and the LSB flash converter perform a true sample and hold operation during the acquisition or sampling period. This period starts after the falling edge of INT and ends with the falling edge of WR in the WR-RD mode or the falling edge of RD in the RD mode. The duration of this period is user controlled and must satisfy a minimum of  $t_P$ .

During this period S1, S3, S4 and S6 close, therefore 46 pF of input capacitance must be charged up in addition to the 11 pF of stray capacitance.

#### 1.2 TRACK AND HOLD vs. SAMPLE AND HOLD

The MSB Flash Converter of the ML2261 in T/H mode has a track and hold mechanism for sampling the input. The input is attached to the MSB comparators directly in the MSB compare cycle, or acquisition period. When the MSB compare cycle ends, the state of the MSB comparators is latched. The LSB Flash Converter always performs a S/H operation. Thus, the analog input signal can be changing during the MSB compare cycle, or acquisition period, and the MSB comparators will be tracking it as long as the slew rate of the analog input is slow enough so that the MSB comparators can respond. The ML2261 can track and hold signals with slew rates as high as .25V/µs (16kHz @ 5 volts) without sacrificing conversion accuracy.

The ML2261 in S/H mode does not have the slew rate limitation of the T/H mode since an internal sample and hold acquires the analog signal, holds it internally, and then performs a conversion. Since this is a true sample and hold function, the S/H mode can theoretically digitize signals of frequencies much higher than the T/H mode. The ML2261 in S/H mode can digitize signals of frequencies as high as 250kHz @ 5V (slew rates as high as  $4V/\mu$ s) without sacrificing conversion accuracy. In most applications, the S/H mode is more desirable than T/H mode because of the better dynamic performance.

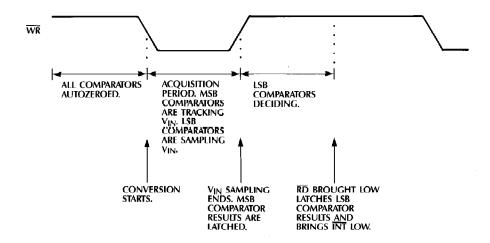

#### 1.2.1 CONVERTER — T/H MODE

The operating sequence for the WR-RD mode is illustrated in Figure 7a. Initially, the internal comparators are auto-zeroed while WR is high. A conversion is initiated by the falling edge of WR. While WR is low, the MSB comparators are tracking the analog input and comparing this voltage against voltages from the internal resistor ladder. At the same time, the input is being acquired or sampled by LSB comparators. On the rising edge of WR, the MSB comparator results are latched, and the LSB acquisition time is ended by closing the sampling switch to the LSB comparators. While WR is high, the LSB comparators then compare the residual input voltage against internal voltages from the resistor ladder to determine the 4 LSB's. When the LSB comparison or conversion is complete, INT goes low and latches the conversion result into the output latches. Then, the comparators are auto-zeroed while WR is high before another conversion can start.

The operating sequence for RD mode, is similar to that described above for the WR-RD mode, except the conversion is initiated by the falling edge of RD, and the MSB and LSB conversions are generated by internal clock edges that are generated while RD is low.

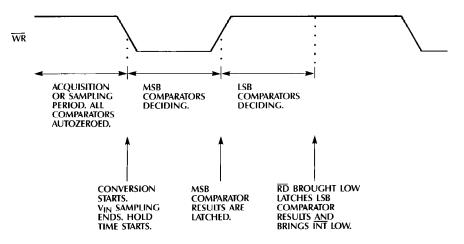

#### 1.2.2 CONVERTER — S/H MODE

The operating sequence for S/H mode is illustrated in Figure 7b. Notice that it is similar to T/H mode described above except this mode has a true sample and hold function. The falling edge of INT closes the sampling switch and starts the acquisition period where the analog input is sampled at the same time all comparators are auto-zeroed. The falling edge of WR opens the internal sampling switch, ends the acquisition period, and starts the conversion on the internally sample and held signal. The MSB comparators make their decisions while WR is low. On the rising edge of WR, the MSB comparator results are latched. The LSB comparators make their decision when WR is high. When the LSB comparison or conversion is complete, INT goes low and latches the conversion result into the output buffers. Then, the acquisition period begins again and the converter is ready for the next conversion.

The operating sequence for the RD mode is the same as the WR-RD mode, except the conversion is initiated by the falling edge of RD, and the MSB and LSB conversions are generated by internal clock edges that are generated while RD is low.

#### a). T/H Mode

#### b). S/H Mode

Figure 7. Operating Sequence (WR-RD Mode)

#### 1.3 REFERENCE

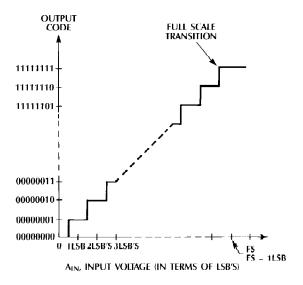

The  $+V_{REF}$  and  $-V_{REF}$  inputs are the reference voltages that determine the full scale and zero input voltages, respectively, for the A/D converter. Thus,  $+V_{REF}$  defines the analog input which produces a full scale output and  $-V_{REF}$  defines the analog input which produces an output code of all zeroes. The transfer function for the A/D converter is shown in Figure 8.

+V<sub>REF</sub> and -V<sub>REF</sub> can be set to any voltage between GND and V<sub>CC</sub>. This means that the reference voltages can be offset from GND and the difference between +V<sub>REF</sub>+ and -V<sub>REF</sub>- can be made small to increase the resolution of the conversion. Note that the total unadjusted error increases when [+V<sub>REF</sub> - (-V<sub>REF</sub>)] decreases.

Figure 8. A/D Transfer Characteristic

#### 1.4 POWER SUPPLY AND REFERENCE DECOUPLING

A  $0.1\mu F$  ceramic disc capacitor is recommended to bypass  $V_{CC}$  to GND, using as short a lead length as possible.

If REF+ and REF- inputs are driven by long lines, they should be bypassed by  $0.1\mu$ F ceramic disc capacitors at the reference input pins.

#### 1.5 DYNAMIC PERFORMANCE

#### 1.5.1 SINUSOIDAL INPUTS

Since the ML2261 has an internal sample and hold, the device can digitize high frequency sinusoids with little or no signal degradations. Using the Nyquist criteria, the highest frequency input to the converter could theoretically be 1/2 the sampling rate ( $f_s$ ). Any frequency components above  $f_s/2$  will be aliased below  $f_s/2$ . In most applications, these aliased components cause unacceptable distortion and must be filtered out of the input. If the input frequency is too close to  $f_s/2$ , then the requirements on the anti-alias filter become difficult

to impossible to realize with standard component and tolerances. In most practical applications, the highest input frequency has to be limited to 1/3 to 1/4 of  $f_{\text{max}}$  in order to relax the filtering requirements enough to make a realizable anti-alias filter.

The maximum sampling rate ( $f_{max}$ ) for the ML2261 in the WR-RD mode, ( $t_{RD} < t_{INTL}$ ) can be calculated as follows:

$$f_{\text{max}} = \frac{1}{t_{\text{WR}} + t_{\text{RD}} + t_{\text{RI}} + t_{\text{P}}}$$

$$f_{\text{max}} = \frac{1}{170\text{ns} + 275\text{ns} + 255\text{ns} + 300\text{ns}}$$

$f_{max} = 1.00 \text{ MHz}$

tWR = Write Pulse Width

$t_{RD}$  = Delay Time between WR and RD Pulses

$t_{RI} = \overline{RD}$  to  $\overline{INT}$  Delay

t<sub>P</sub> = Delay Time between Conversions

This permits a maximum sampling rate of 1MHz for the ML2261. The dynamic performance specifications (SNR, HD, IMD, and FR) for the ML2261 are all specified at 250kHz, which is approximately 1/4 of the sampling rate, f<sub>s</sub>.

In applications where aliased frequency components are acceptable and filtering of the input signal is not needed or where a filter with a steep amplitude response is available, the user can apply an input sinusoid higher than 250kHz to the device. Note, however, that as the input frequency increases above 500kHz, dynamic performance degradation will occur due to the finite bandwidth of the internal sample and hold.

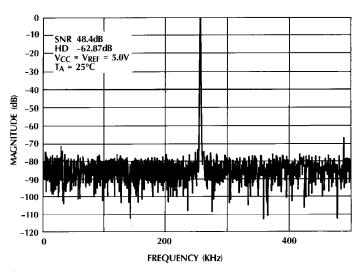

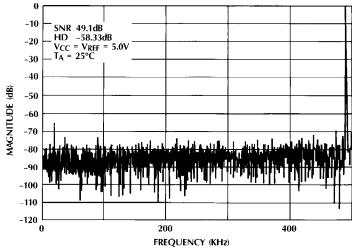

The Figure 9 plots are 4096 point FFT's of the ML2261 converting a 257kHz and a 491kHz, 0 to 4.5V, low distortion sine wave input. The ML2261 samples and digitizes at its specified accuracy, dynamic input signals with frequency components up to the Nyquist frequency (one-half the sampling rate). The output spectra yields precise measurements of the input signal level, harmonic components, and signal to noise ratio up to the 8-bit level. The near ideal signal to noise ratio is maintained independent of increasing analog input frequencies to 500kHz.

#### 1.5.2 SIGNAL-TO-NOISE RATIO

Signal-to-noise ratio (SNR) is the measured signal to noise at the output of the converter. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all the nonfundamental signals up to half the sampling frequency. SNR is dependent on the number of quantization levels used in the digitization process; the more the levels, the smaller the quantization noise. The theoretical SNR for a sine wave is given by

$$SNR = (6.02N + 1.76) dB$$

where N is the number of bits. Thus for ideal 8-bit converter, SNR = 49.92 dB.

- a) Ouput Spectrum with  $f_{IN} = 257kHz$ ,  $f_S = 1MHz$

- b) Output Spectrum with  $f_{IN} = 491kHz$ ,  $f_S = 1MHz$

Figure 9. Dynamic Performance, Sample and Hold Mode

#### 1.5.3 HARMONIC DISTORTION

Harmonic distortion is the ratio of the rms sum of harmonics to the fundamental. Total harmonic distortion (THD) of the ML2261 is defined as

20 log

$$\frac{(V_2^2 + V_3^2 + V_4^2 + V_5^2)^{1/2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  are the rms amplitudes of the individual harmonics.

#### 1,5.4 INTERMODULATION DISTORTION

With inputs consisting of sine waves at two frequencies,  $f_A$  and  $f_B$ , any active device with nonlinearities will create distortion products, of order (m + n), at sum and difference frequencies of  $mf_A$  +  $nf_B$ , where m, n = 0, 1, 2, 3 . . . Intermodulation terms are those for which m or n is not equal to zero. The (IMD) intermodulation distortion specification includes the second order terms  $(f_A + f_B)$  and  $(f_A - f_B)$  and the third order terms  $(2f_A + f_B)$ ,  $(2f_A - f_B)$ ,  $(f_A + 2f_B)$ , and  $(f_A - 2f_B)$  only.

#### 1.6 DIGITAL INTERFACE

The ML2261 has two basic interface modes, RD and WR-RD, which are selected by the MODE input pin.

#### 1.6.1 RD MODE

In the RD mode, the  $\overline{WR}/RDY$  pin is configured as the RDY output. The read mode performs a conversion with a single RD pulse. This allows the  $\mu P$  to start a conversion, wait, and then read data with a single read instruction.

The timing for the RD mode is shown in Figure 2. To do a conversion, CS must be low to select the device. After CS goes low, the RDY output goes low indicating that the device is ready to do a conversion. The conversion starts on the falling edge of RD. While RD is low, the MSB and LSB decisions are made with internally generated clock edges. When the conversion is complete, RDY goes high and INT goes low signaling the end of the conversion. After INT goes low, the data outputs go from high impedance to active state with valid output data. Data stays valid until either RD or CS goes high. When either signal goes high, the output data lines return to the high impedance state and INT returns high. A pull up resistor on RDY in the sample and hold mode will cause clock injection, degrading the total unadjusted error, unless CS1 is  $\geq$  20ns before RD↓.

#### 1.6.2 WR-RD MODE

In the WR-RD mode, the WR/RDY pin is configured as the WR input. In this mode, WR initiates the conversion and RD controls reading the output data. This can be done in several ways, described below.

## 1.6.3 WR-RD MODE — USING INTERNAL DELAY ( $t_{\rm RD} > t_{\rm INTL}$ )

The timing is shown in Figure 3. To do a conversion, CS must be low to select the device. Then, WR falling edge triggers the conversion. While WR is low, the MSB comparison is made. When WR returns high the LSB decision is made. After some internal delay, INT goes low indicating end of conversion. Valid data will appear on DB0–7 when RD is pulled low. INT is then reset by the rising edge of either CS or RD.

## 1.6.4 WR-RD MODE — READING BEFORE DELAY $(t_{RD} < t_{INTL})$

The internally generated delay for the LSB decision when  $t_{RD} > t_{INTL}$  is longer than necessary due to circuit design tolerances of  $t_{INTL}$  delay. If desired, a faster conversion will result without loss of accuracy by bringing RD low within the minimum time specified for  $t_{RD}$ . The timing diagram for this mode is shown in Figure 4. WR is the same as when  $t_{RD} > t_{INTL}$ . But in this case, RD is brought low  $t_{RD}$  ns after WR rising edge and before INT. INT goes low indicating an end of conversion after the falling edge of RD and is reset on the rising edge of RD or CS. When RD is brought low before INT goes low the data bus always remains in the high-impedance state until INT↓.

#### 1.6.5 WR-RD MODE — STAND ALONE OPERATION

Stand alone operation can be implemented by tying CS and RD low as shown in Figure 5. WR initiates a conversion as before. When WR is low, the MSB comparison is made. When, WR goes high, the LSB comparison is made. Since RD is already low, the output data will appear automatically at end of conversion. Since RD is always low, INT is reset on rising edge of WR and goes low at end of conversion.

#### 1.6.6 POWER-ON RESET

When power is first applied, <u>an internal power-on reset</u> and timer circuit inhibits the <u>CS</u> input and resets the internal circuitry to prevent the ML2261 from starting in an <u>unknown</u> state. During this period of approximately <u>3µs</u>, <u>INT</u> remains high and the data bus is in the high-impedance state.

68008

#### **TYPICAL APPLICATIONS** 2.0

\* NO PROTECTION IS REQUIRED IF INPUT CURRENT < 25 mA

Figure 10. Protecting the Input

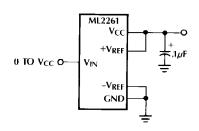

Figure 11. Using  $V_{CC}$  as Reference for Ratiometric Operation

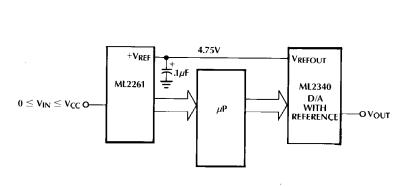

Figure 12. Using External Reference of D/A

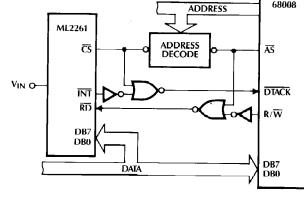

Figure 13. 68000 Type Interface to ML2261

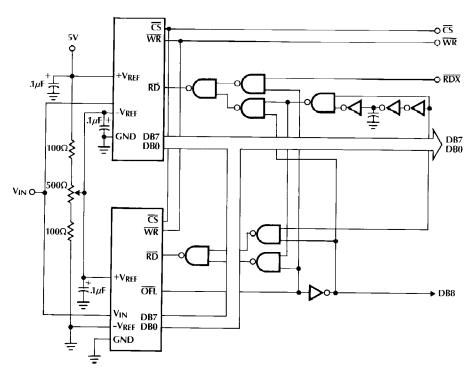

Figure 14. 9-Bit Resolution

### 2.0 TYPICAL APPLICATIONS (Continued)

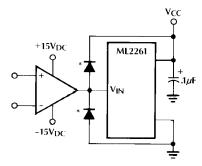

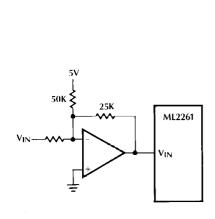

Figure 15. ±2.5V Analog Input Range

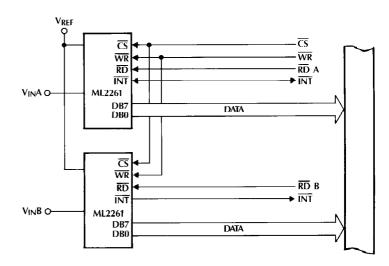

Figure 16. Simultaneous Sampling of Two Variables

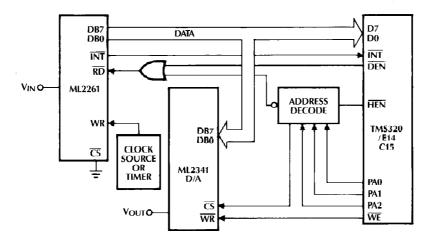

Figure 17. TMS320 Interface with D/A Output

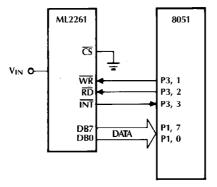

Figure 18. 8051 Interface to ML2261

### TYPICAL APPLICATIONS (Continued)

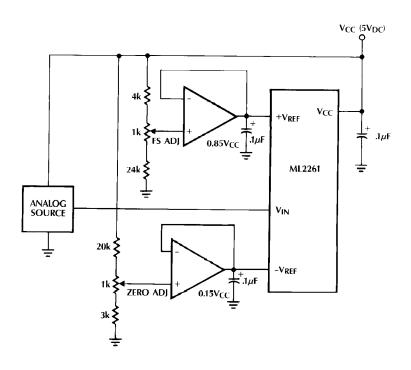

Figure 19. Operating with a Ratiometric Analog Signal of 15% of  $V_{\text{CC}}$  to 85% of  $V_{\text{CC}}$

### **ORDERING INFORMATION**

| PART NUMBER | TOTAL<br>UNADJUSTED ERROR | TEMPERATURE RANGE | PACKAGE          |

|-------------|---------------------------|-------------------|------------------|

| ML2261BCP   | ±1/2 LSB                  | 0°C to 70°C       | Molded DIP (P20) |

| -ML2261BCQ  |                           | 0°C to 70°C       | Molded PCC (Q20) |

| ML2261CCP   | ±1 LSB                    | 0°C to 70°C       | Molded DIP (P20) |

| ML2261CCQ   |                           | 0°C to 70°C       | Molded PCC (Q20) |

To receive a price quote or to request a product sample, call or send e-mail to your local representative.

When sending e-mail, be sure to include the Micro Linear part number and whether you want a price quote or a sample in the subject line.

(i.e. subject: Sample request - ML part#xxxx)

Click here to find your local representative