## EL2006/EL2006A T.19-15 High Gain Fast FET Input Op Amp

ELANTEC INC

#### **Features**

- 90 dB open loop gain

- 450 V/µs slew rate

- 40 MHz bandwidth

- No thermal tail

- 3 mV max input offset voltage

- · Offset nulls with single pot

- No compensation required for gains above 50

- Peak output current to 200 mA

- Pin compatible with LH0032

- 80 dB common mode rejection

#### **Ordering Information**

| Part No.      | Temp. Range     | Pkg.   | Outline# |

|---------------|-----------------|--------|----------|

| EL2006CG      | -25°C to +85°C  | TO-8   | MDP0002  |

| EL2006G       | -55°C to +125°C | TO-8   | MDP0002  |

| EL2006G/883B  | -55°C to +125°C | TO-8   | MDP0002  |

| EL2006ACG     | -25°C to +85°C  | TO-8   | MDP0002  |

| EL2006AG      | -55°C to +125°C | TO-8   | MDP0002  |

| EL2006AG/883G | -55°C to +125°C | TO-8   | MDP0002  |

| EL2006L       | -55°C to +125°C | 52-Pad | MDP0013  |

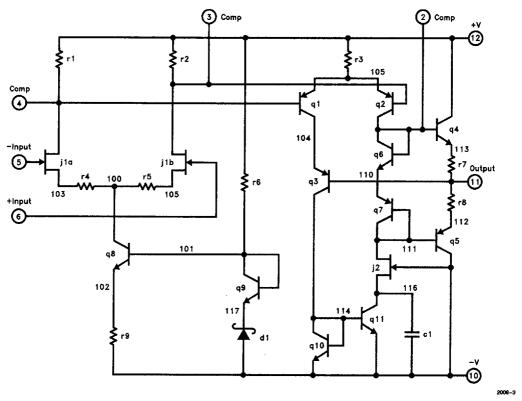

#### **Connection Diagrams**

#### **General Description**

The EL2006/EL2006A are high slew rate, wide bandwidth, high input impedance, high gain and fully differential input operational amplifiers. They exhibit excellent open loop gain characteristics making them suitable for a broad range of high speed signal processing applications. These patented devices have open loop gains in excess of 86 dB making the EL2006/EL2006A ideal choices for current mode video bandwidth digital to analog converters of 10 bits or higher resolution. The EL2006's FET input structure, high slew rate, and high output drive capability allow use in applications such as buffers for flash converter inputs. In general, the EL2006/EL2006A allow the user to take relatively high closed loop gains without compromising gain accuracy or bandwidth.

The EL2006/EL2006A are pin compatible with the popular industry standard ELH0032/ELH0032A offering comparable bandwidth and slew rate, while offering significant improvements in open loop gain, common mode rejection and power supply rejection.

Elantec facilities comply with MIL-I-45208A and are MIL-STD-1772 certified. Elantec's Military devices comply with MIL-STD-883 Class B Revision C and are manufactured in our rigidly controlled, ultra-clean facilities in Milpitas, California. For additional information on Elantec's Quality and Reliability Assurance Policy and procedures request brochure ORA-1.

Manufactured under U.S. Patent No. 4,746,877

### High Gain Fast FET Input Op Amp

#### Absolute Maximum Ratings (TA = 25°C)

$\begin{array}{lll} V_S & Supply \mbox{ Voltage} & \pm 18 \mbox{ V} \\ V_{IN} & Input \mbox{ Voltage} & \pm 15 \mbox{ V} \end{array}$

Differential Input Voltage 30V Peak Output Current (Note 1) ± 200 mA

I<sub>OUT</sub> Peak Output Current (Note 1) ± 200 m P<sub>D</sub> Power Dissipation

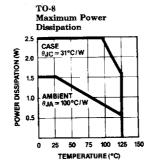

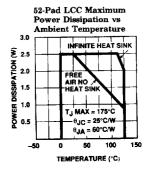

$T_A = 25^{\circ}\text{C }1.5\text{W}$ , derate  $100^{\circ}\text{C/W}$  to  $+125^{\circ}\text{C}$  $T_C = 25^{\circ}\text{C }2.2\text{W}$ , derate  $70^{\circ}\text{C/W}$  to  $+125^{\circ}\text{C}$  T<sub>A</sub> Operating Temperature Range

EL2006, EL2006A -55°C to +125°C EL2006C, EL2006AC -25°C to +85°C

$T_J$  Operating Junction Temperature 175°C  $T_{ST}$  Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C

Lead Temperature

(Soldering 10 seconds) 300°C

#### Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality inspection. Flantec performs most electrical tests using modern high-speed automatic test equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore T<sub>J</sub>-T<sub>C</sub>-T<sub>A</sub>.

Test Level Test Procedure

I 100% production tested and QA sample tested per QA test plan QCX0092.

II 100% production tested at T<sub>A</sub> = 25°C and QA sample tested at T<sub>A</sub> = 25°C.

T<sub>MAX</sub> and T<sub>MIN</sub> per QA test plan QCX0002.

III QA sample tested per QA test plan QCX0002.

IV Parameter is guaranteed (but not tested) by Design and Characterization Data. V Parameter is typical value at  $T_A=2SC$  for information purposes only.

DC Electrical Characteristics  $V_S = \pm 15V$ ,  $T_{MIN} < T_A < T_{MAX}$

|                          | Description                     | Test Conditions                                              | EL2006 |     |     |               | EL2006C |     |     |               |       |

|--------------------------|---------------------------------|--------------------------------------------------------------|--------|-----|-----|---------------|---------|-----|-----|---------------|-------|

| Parameter                |                                 |                                                              | Min    | Тур | Max | Test<br>Level | Min     | Тур | Max | Test<br>Level | Units |

| vos                      | Offset Voltage                  | $T_J = 25^{\circ}C$                                          |        |     | 5   | 1             |         |     | 5   | 1             | mV    |

|                          |                                 |                                                              |        |     | 10  | 1             |         |     | 10  | Ш             | mV    |

| $\Delta V_{OS}/\Delta T$ | Offset Voltage Drift            |                                                              |        | 15  |     | ٧             |         | 15  |     | ٧             | μV/°C |

| $I_{\mathbf{B}}$         | Bias Current                    | $T_{J} = 25^{\circ}C$                                        |        |     | 100 | 1             |         |     | 500 | I             | рA    |

|                          |                                 |                                                              |        | 1   | 10  | 1             |         | 1   | 10  | ш             | nA    |

| Ios                      | Offset Current                  | $T_J = 25^{\circ}C$                                          |        |     | 25  | 1             |         |     | 50  | 1             | pА    |

|                          |                                 |                                                              |        | 0.2 | 2.5 | 1             |         | 0.2 | 2.5 | П             | nA    |

| V <sub>CM</sub>          | Common Mode Range               |                                                              | ±10    |     |     | 1             | ±10     |     |     | п             | v     |

| CMRR                     | Common Mode<br>Rejection Ratio  | $\Delta V_{IN} = \pm 10V$                                    | 70     | 80  |     | 1             | 70      | 80  |     | 11            | ďΒ    |

| PSRR                     | Power Supply<br>Rejection Ratio | $\pm 5V \le V_S \le \pm 15V$                                 | 70     | 88  |     | 1             | 70      | 88  |     | 11            | ďΒ    |

| A <sub>VOL</sub>         | Large Signal<br>Voltage Gain    | $R_L = 1 k\Omega, V_{OUT} = \pm 10V,$<br>$T_J = 25^{\circ}C$ | 74     | 90  |     | 1             | 74      | 90  |     | T             | ₫B    |

|                          |                                 | $R_L = 1 k\Omega, V_{OUT} = \pm 10V$                         | 80     |     |     | 1             | 74      |     |     | ш             | dB    |

| vo                       | Output Voltage Swing            | $R_L = 1 k\Omega$                                            | ±12    |     |     | 1             | ±12     |     |     | п             | v     |

| I <sub>OUT</sub>         | Output Current                  | $V_{OUT} = \pm 10V,$<br>$T_{J} = 25^{\circ}C, (Note 1)$      | ±100   |     |     | 1             | ± 100   |     |     | 1             | mA    |

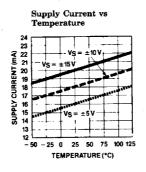

| I <sub>CC</sub>          | Supply Current                  |                                                              |        | 20  | 23  | 1             |         | 20  | 23  | 11            | mA    |

#### ELANTEC INC

### High Gain Fast FET Input Op Amp

#### DC Electrical Characteristics = Contd.

$V_{S}=\pm 15V, T_{MIN} \le T_{A} \le T_{MAX}$  (Note: These tests are in addition to those listed above.)

| Parameter                |                              |                                                               | EL2006A |     |     |                     | EL2006AC      |       |    |   |       |

|--------------------------|------------------------------|---------------------------------------------------------------|---------|-----|-----|---------------------|---------------|-------|----|---|-------|

|                          | Description                  | Test Conditions                                               | Min     | Тур | Max | Level Min Typ Max I | Test<br>Level | Units |    |   |       |

| v <sub>os</sub>          | Offset Voltage               | $T_{J} = 25^{\circ}C$                                         |         |     | 3   | 1                   |               |       | 3  | 1 | mV    |

| $\Delta V_{OS}/\Delta T$ | Offset Voltage Drift         |                                                               |         | 15  | 25  | I                   |               | 15    | 25 | 1 | μV/°C |

| A <sub>VOL</sub>         | Large Signal<br>Voltage Gain | $T_J = 25^{\circ}C$ , $R_L = 1 k\Omega$ , $V_{OUT} = \pm 10V$ | 74      | 90  |     | I                   | 74            | 90    |    | п | d₿    |

|                          |                              | $R_L = 1 k\Omega, V_{OUT} = \pm 10V$                          | 74      |     |     | 1                   | 74            |       |    | ш | ₫B    |

AC Electrical Characteristics  $V_S = \pm 15V$ ,  $R_L = 1 \text{ k}\Omega$ ,  $T_J = 25^{\circ}\text{C}$  (See AC Test Circuits)

|                 | Description                      | Test Conditions                     | EL2006, EL2006A |     |     |               | EL2006C, EL2006AC |     |     |               | İ      |

|-----------------|----------------------------------|-------------------------------------|-----------------|-----|-----|---------------|-------------------|-----|-----|---------------|--------|

| Parameter       |                                  |                                     | Min             | Тур | Max | Test<br>Level | Min               | Тур | Max | Test<br>Level | Units  |

| tr              | Rise Time                        | $A_{V} = 10V, V_{OUT} = 1 V_{P-P}$  |                 | 18  |     | V             |                   | 18  |     | V             | ns     |

|                 |                                  | $A_{V} = 1V, V_{OUT} = 1 V_{P-P}$   |                 | 12  | 15  | I             |                   | 12  | 15  | I             | ns     |

| SR              | Slew Rate (Note 2)               | $A_{V} = 1V, V_{OUT} = 20 V_{P-P}$  | 350             | 450 |     | I             | 350               | 450 |     | 1             | V/μs   |

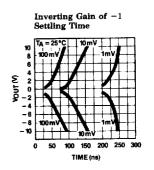

| ts              | Settling Time to 1.0%            | $A_{V} = -1V, V_{OUT} = 10 V_{P-P}$ |                 | 90  |     | ٧             |                   | 90  |     | V             | ns     |

| t <sub>s</sub>  | Settling Time to 0.1%            | $A_{V} = -1V, V_{OUT} = 10 V_{P-P}$ |                 | 160 |     | v             |                   | 160 |     | V             | ns     |

| t <sub>s</sub>  | Settling Time to 0.01%           | $A_{V} = -1V, V_{OUT} = 10 V_{P-P}$ |                 | 250 |     | v             |                   | 250 |     | v             | ns     |

| GBW             | Gain Bandwidth Product           | $A_V \ge 20V$                       |                 | 500 |     | v             |                   | 500 |     | V             | MHz    |

|                 | Pull Power<br>Bandwidth (Note 3) | $V_{OUT} = \pm 10V$                 | 5.5             | 7   |     | 1             | 5.5               | 7   |     | I             | MHz    |

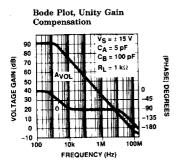

|                 | Unity Gain Bandwidth             | $C_A = 8 pF, C_B = 100 pF$          |                 | 40  |     | v             |                   | 40  |     | v             | MHz    |

| e <sub>N</sub>  | Noise Voltage                    | 1 kHz to 1 MHz                      |                 | 20  |     | v             |                   | 20  |     | V             | nV/√Hz |

| t <sub>D</sub>  | Small Signal Delay               | $A_V = 1V$                          |                 | 13  | 15  | I             |                   | 13  | 15  | I             | ns     |

| C <sub>IN</sub> | Input Capacitance                |                                     |                 | 2   |     | v             |                   | 2   |     | v             | pF     |

Note 1:  $T_I = 25$ °C, duty cycle < 1%, pulse width < 10  $\mu$ s.

Note 2: Slew rate is measured at the 25% and 75% points.

Note 3: The Full Power bandwidth is guaranteed by testing slew rate.

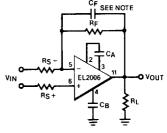

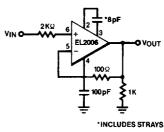

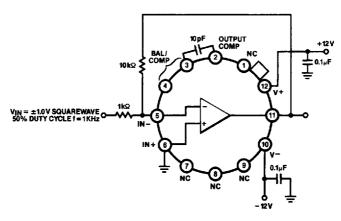

#### **EL2006 Recommended Compensation**

(See Figure 1)

| Avol     | C <sub>A</sub> | $\mathbf{C}_{\mathbf{B}}$ | $R_{S^+}$  | $\mathbf{R_{S^-}}$ | $R_{\mathbf{F}}$ |  |  |

|----------|----------------|---------------------------|------------|--------------------|------------------|--|--|

| +1       | 5-8 pF         | 100 pF                    | 2 <b>k</b> | Open Circuit       | 100              |  |  |

| -1 to +5 | 5 p <b>F</b>   | 68 pF                     | 0          | < 1k               | 1k               |  |  |

| ± 10     | 5 pF           | 10 p <b>F</b>             | < 1k       | 1k                 | > 10k            |  |  |

| > ± 20   | 3 pF           | 10 pF                     | < 1k       | 1k                 | > 20k            |  |  |

Note: Use a small capacitor of about 1 pF in parallel with R<sub>F</sub> to compensate for stray input capacitance.

2006-4

Figure 1

ELANTEC INC

## *EL2006/EL2006A* High Gain Fast FET Input Op Amp

### **Typical Performance Curves**

Input Bias Currents as a Function of Input Voltage 104 INPUT BIAS CURRENT (DA) TA = 25°C STEADY STATE 15 10 20 POSITIVE SUPPLY VOLTAGE MINUS INPUT VOLTAGE [VS+ - VIN] (VOLTS)

#### Normalized Input Bias and Offset Current vs Junction Temperature CURRENT -NORMALIZED TO CURRENT AT TJ = 25°C 104 103 102 105 125 145 165 JUNCTION TEMPERATURE (°C)

# General

The EL2006 was designed to overcome the gain and stability limitations of prior high speed FET input operational amplifiers like the LH0032. Open loop gain is typically 90 dB allowing gain setting to 12-bit accuracy. This new design also eliminates "thermal tail", which is the tendency for the gain to diminish at very low frequencies to DC due to thermal feedback. The EL2006 is also easier to stabilize than earlier designs, thanks to an Elantec proprietary internal compensation technique which eliminates the "second stage bump." The EL2006 open loop gain

**Applications Information**

ELANTEC INC

High Gain Fast FET Input Op Amp

#### Applications Information — Contd.

characteristic is well behaved well beyond the unity gain frequency so that spurious ringing or oscillation in the 100 MHZ-200 MHz region is avoided. Finally, we have provided temperature compensation so that gain and stability are relatively constant over temperature.

These improvements are provided in a configuration which is plug compatible with LH0032 and similar products so that designers can easily upgrade their system performance without extensive re-design. In most cases, the EL2006 can be used to replace LH0032 with no change in external compensation.

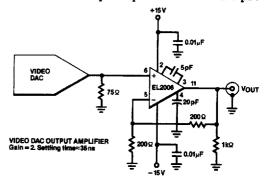

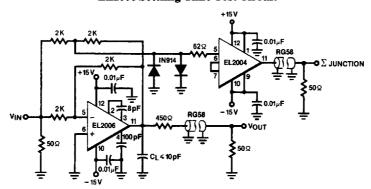

#### Video DAC Amplifiers

A typical application for the EL2006 is to provide gain for video signals. In the example shown, the EL2006 provides a gain of 2 with settling time around 35 ns to 10 mV.

#### **Power Supply Decoupling**

The EL2006/EL2006A, like most high-speed circuits, is sensitive to layout and stray capacitance. Power supplies should be bypassed as near to pins 10 and 12 as possible with low inductance capacitors such as 0.01  $\mu$ F disc ceramics. Compensation components should also be located close to the appropriate pins to minimize stray reactances.

#### **Input Current**

Because the input devices are FETs, the input bias current may be expected to double for each  $11^{\circ}$ C junction temperature rise. This characteristic is plotted in the typical performance characteristics graphs. The device will self-heat due to internal power dissipation after application of power, thus raising the FET junction temperature  $40^{\circ}$ C- $60^{\circ}$ C above the free-air ambient temperature when supplies are  $\pm 15$ V. The device temperature will stabilize within 5-10 minutes after application of power, and the input bias currents measured at the time will be indicative of normal operating currents. An additional rise will occur as power is delivered to a load due to additional internal power dissipation.

#### **Power Dissipation**

There is an additional effect on input bias current as the input voltage is changed. The effect, common to all FETs, is an avalanche-like increase in gate current as the FET gate-to-drain voltage is increased above a critical value, depending on FET geometry and doping levels. This effect will be noted as the input voltage of the EL2006 is taken below ground potential when the supplies are  $\pm\,15\mathrm{V}$ . All of the effects described here may be minimized by operating the device with  $V_S \leq \,\pm\,15\mathrm{V}$ .

These effects are indicated in the typical performance curves.

#### **Input Capacitance**

The input capacitance to the EL2006/EL2006A is typically 2 pF and thus may form a significant time constant with high value resistors. For optimum performance, the input capacitance to the inverting input should be compensated by a small capacitor across the feedback resistor. The value is strongly dependent on layout and closed loop gain, but will typically be in the neighborhood of several picofarads.

In the non-inverting configuration, it may be advantageous to bootstrap the case and/or a guard conductor to the inverting input. This serves both to divert leakage currents away from the non-inverting input and to reduce the effective input capacitance. A unity gain follower so treated will have an input capacitance under a 1 pF.

2006-8

# EL2006/EL2006A High Gain Fast FET Input Op Amp

#### Applications Information — Contd.

#### Heatsinking

While the EL2006/EL2006A are specified for operation without any explicit heatsink, internal power dissipation does cause a significant temperature rise. Improved bias current performance can thus be obtained by limiting this tempera-

malloy No. 2241 or equivalent. The case of the device has no internal connection, so it may be electrically connected to the sink if this is advantageous. Be aware, however, that this will affect the stray capacitances to all pins and may thus require adjustment of circuit compensation values.

ture rise with a small heat sink such as the Ther-

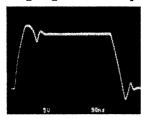

#### Voltage Follower ( $A_V = +1$ ) Large Signal Pulse Response

$V_S = \pm 15V$ ,  $V_{IN} = +10V$  to -10V and -10V to +10V

#### Large Signal Pulse Response Test Circuit

2006-7

#### **EL2006 Settling Time Test Circuit**

$R_L = 2K\Omega I/2K\Omega I/500\Omega = 333\Omega$

2006-8

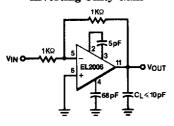

#### **Inverting Unity Gain**

2006-9

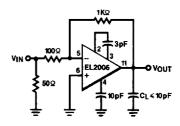

#### **Inverting Gain of 10**

2006-10

ELANTEC INC

High Gain Fast FET Input Op Amp

#### **Burn-In Circuit**

Pin Numbers are for TO-8 package. LCC uses the same schematic.

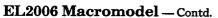

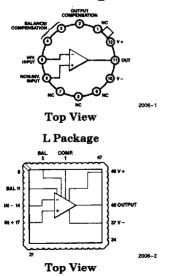

#### **EL2006 Macromodel**

```

* Connections:

+input

-input

+ Vsupply

-Vsupply

Comp 3

Comp 4

Comp 2

Output

.subckt M2006

10

* Models

model \ gfa \ nif \ (vto = -2.5V \ beta = 1.11e - 3 \ cgd = 2pF \ cgs = 5pF \ m = 0.3744)

.model qp pnp (is = 5E - 14 bf = 150 vaf = 100 ikf = 100mA tf = .53nS vtf = 0 ise = 1 nA,

+ cjc = 4pF cje = 5.7pF tr = 170nS rb = 3 br = 5 mje = .32 mjc = .43 xtb = 2.1 ne = 4

+isc = 1nA nc = 4 itf = .4 vtf = 4 xtf = 6)

.model qn npn (is = 5e - 14 bf = 150 vaf = 800 ikf = 200mA tf = .54nS vtf = 0

+ \text{cjc} = 4\text{pF cje} = 5\text{pF rb} = 3 \text{ br} = 5 \text{ mje} = .42 \text{ mjc} = .23 \text{ tr} = 200\text{nS xtb} = 2.1

+ ise = 4nA ne = 4 isc = 4nA nc = 4 itf = .4 vtf = 4 xtf = 2)

.model of b nif (vto = -2.8V beta = 4e-3 cgd = 7pF cgs = 8pF lambda = 4e-3)

.model zener d (bv = 2.49V ibv = 1mA)

* Resistors and Capacitors

r1 12 4 700

r2 12 3 700

r3 12 105 160

r4 103 100 10

r5 108 100 10

r6 12 101 22K

r7 113 11 10

r8 11 112 10

r9 102 10 407

cs2 10 116 100pF

* Transistors and Diodes

j1a 4 5 103 qfa

j1b 3 6 108 qfa

j2 111 10 116 qfb

q1 104 4 105 qp

q2 2 3 105 qp

q3 114 11 104 qp

q4 12 2 113 qn

q5 10 111 112 qp

q6 2 2 110 qn

q7 111 111 110 qp

q8 100 101 102 qn

d1 10 117 zener

q9 101 101 117 qn

q10 114 114 10 qn

q11 116 114 10 qn

.ends

```

ELANTEC INC

High Gain Fast FET Input Op Amp