# **ICs for Communications**

S/T Bus Interface Circuit Extended SBCX

PEB 2081 Version 3.4

User's Manual 11.96

#### Edition 11.96

This edition was realized using the software system FrameMaker'.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1996. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

# Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain hu-

# **ICs for Communications**

S/T Bus Interface Circuit Extended SBCX

PEB 2081 Version 3.4

User's Manual 11.96

| PEB 2081<br>Revision History:            |        | Current Version: 11.96                       |

|------------------------------------------|--------|----------------------------------------------|

| Previous Ve                              | rsion: |                                              |

| Page Page (in previous Version) Version) |        | Subjects (major changes since last revision) |

|                                          |        |                                              |

|                                          |        |                                              |

| Contents                      |                                                                                                       | Page           |

|-------------------------------|-------------------------------------------------------------------------------------------------------|----------------|

| Introduct                     | ion                                                                                                   | 10             |

| 1<br>1.1<br>1.2<br>1.3<br>1.4 | Features   Pin Configuration   Pin Definition and Functions   Logic Symbol   Functional Block Diagram | 12<br>13<br>14 |

| 2                             | System Integration and Applications                                                                   | 16             |

| 2.1                           | Operational Modes and System Integration                                                              |                |

| 2.1.1                         | TE Application                                                                                        | 17             |

| 2.1.2                         | ISDN Network Termination (NT1)                                                                        |                |

| 2.1.3                         | ISDN Network Terminator (NT1) in Star Configuration                                                   |                |

| 2.1.4                         | ISDN Network Terminator Using IOM®-2 Architecture (Intelligent NT)                                    |                |

| 2.1.5                         | Line Card Application (one D-channel controller per line)                                             |                |

| 2.1.6                         | Line Card Application (one D-channel controller for eight lines)                                      |                |

| 2.1.7                         | Private-Branch-Exchange Application (one D-channel controller per line)                               |                |

| 2.2                           | Setting Operating Modes                                                                               |                |

| 2.3                           | Clock Generation                                                                                      |                |

| 2.3.1<br>2.3.2                | TE Mode                                                                                               |                |

| 2.3.2<br>2.3.3                | LT-T Mode                                                                                             |                |

| 2.3.3<br>2.3.4                | LT-S Mode                                                                                             |                |

| 2.4                           | S/T-Interface Configurations                                                                          |                |

| 3                             | Application Guide                                                                                     | 43             |

| 3.1                           | SBCX Device Architecture and General Functions                                                        |                |

| 3.2                           | Interfaces                                                                                            |                |

| 3.2.1                         | IOM®-2 Interface                                                                                      | 45             |

| 3.2.1.1                       | IOM®-2 Frame Structure/Timing Modes                                                                   | 45             |

| 3.2.1.1.1                     | IOM®-2 Interface Line Card Frame Structure                                                            | 47             |

| 3.2.1.1.2                     | IOM®-2 Interface Terminal Frame Structure                                                             |                |

| 3.2.1.2                       | IOM®-2 Interface Command / Indicate Channel                                                           |                |

| 3.2.1.3                       | IOM®-2 Interface Monitor Channel                                                                      |                |

| 3.2.1.3.1                     | Handshake Procedure                                                                                   |                |

| 3.2.1.3.2                     | Monitor Procedure "Timeout" (TOD)                                                                     |                |

| 3.2.1.3.3                     | MON-1, MON-2 Commands (S/Q Channel Access)                                                            |                |

| 3.2.1.3.4                     | MON-8 Commands (Internal Register Access)                                                             |                |

| 3.2.1.3.5                     | MON-8 Identification Register                                                                         |                |

| 3.2.1.3.6                     | MON-8 Configuration Register                                                                          |                |

| 3.2.1.3.7                     | MON-8 Loop-Back Register                                                                              |                |

| 3.2.1.3.8                     | MON-8 IOM®-2 Channel Register                                                                         |                |

| 3.2.1.3.9                     | MON-8 SM/CI Register                                                                                  |                |

| 3.2.1.4                       | MAI Pin Register                                                                                      |                |

| 3.2.2                         | S/T-Interface                                                                                         |                |

| 3.2.3<br>3.2.3.1              | Maintenance Auxiliary Interface (MAI)                                                                 |                |

| J.Z.J. I                      | I/O ODECINO MOUE                                                                                      | 00             |

| Contents  | (cont'd)                                                | Page |

|-----------|---------------------------------------------------------|------|

| 3.2.3.2   | Standard I/O Mode                                       | 69   |

| 3.2.3.3   | μP MAI Mode                                             | 70   |

| 3.3       | Control Procedures                                      |      |

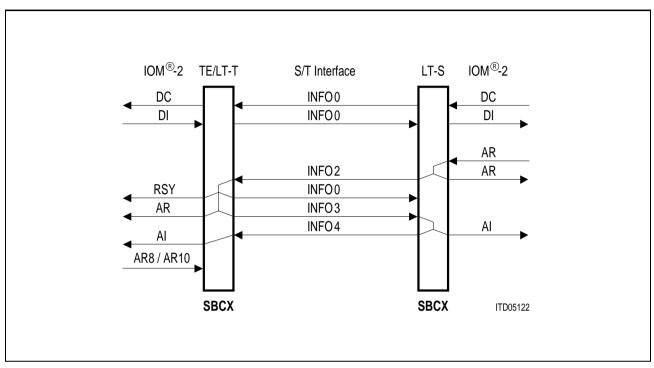

| 3.3.1     | Activation Initiated by Exchange (LT-S)                 | 72   |

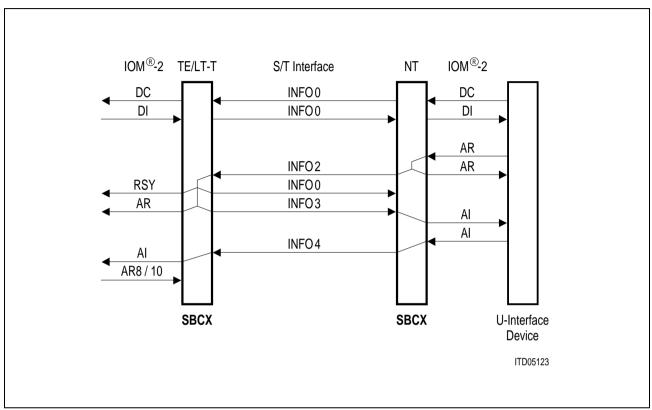

| 3.3.2     | Activation Initiated by Exchange (NT)                   | 72   |

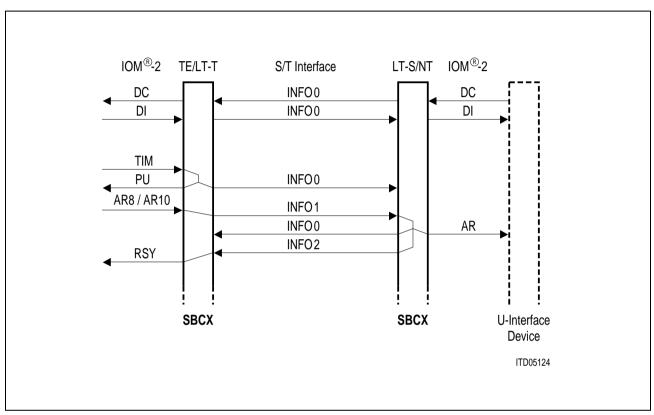

| 3.3.3     | Activation Initiated by Terminal (TE/LT-T)              | 73   |

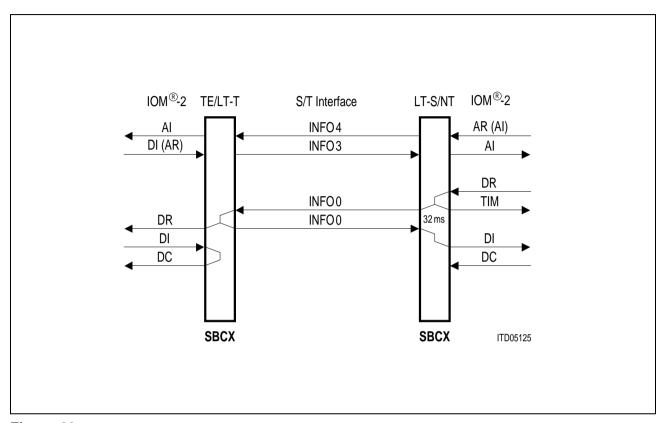

| 3.3.4     | Deactivation                                            |      |

| 3.3.5     | D-Channel Access Control                                | 74   |

| 3.3.5.1   | TIC Bus D-Channel Control in TE                         | 75   |

| 3.3.5.2   | S-Bus Priority Mechanism for D-Channel                  | 76   |

| 3.3.5.3   | S-Bus D-Channel Control in TEs                          |      |

| 3.3.5.4   | S-Bus D-Channel Control in LT-T                         | 78   |

| 3.3.5.5   | D-Channel Control in the Intelligent NT (TIC-and S-Bus) | 78   |

| 3.3.6     | IOM®-2 Interface Channel Switching                      | 81   |

| 3.4       | Maintenance Functions                                   | 84   |

| 3.4.1     | Test Loop-Backs                                         | 84   |

| 3.4.1.1   | Complete Loop-Backs (No. 2, No. 3, and No. A)           | 85   |

| 3.4.1.2   | Single Channel Loop-Backs (No. 4, No. B1/2, No. C)      | 87   |

| 3.4.2     | Monitoring of Illegal Code Violations                   | 88   |

| 3.4.3     | Test Modes and System Measurements                      | 88   |

| 3.4.3.1   | Test Mode 1                                             | 88   |

| 3.4.3.2   | Test Mode 2                                             | 88   |

| 3.4.3.3   | Pulse Mask Measurement                                  | 89   |

| 3.4.3.4   | NT Transmitter Output/Receiver Input Impedance          | 89   |

| 3.4.3.5   | TE Transmitter Output/Receiver Input Impedance          |      |

| 3.4.3.6   | NT/TE Timing Extraction Jitter                          |      |

| 3.4.3.7   | TE Total Phase Deviation                                |      |

| 3.4.3.8   | TE and NT Longitudinal Conversion Loss (LCL)            |      |

| 3.4.3.9   | TE and NT Output Signal Balance (OSB)                   |      |

| 3.4.3.10  | TE Frame Rate Info1                                     |      |

| 3.4.3.11  | Loss and Regain of Frame Alignment (TE)                 | 91   |

| 4         | Technical Description                                   |      |

| 4.1       | Interfaces                                              |      |

| 4.1.1     | IOM®-2 Interface                                        |      |

| 4.1.1.1   | IOM®-2 Dynamic Characteristics                          |      |

| 4.1.1.2   | Timing Characteristics CEB (NT / LT-S)                  |      |

| 4.1.1.3   | Command/Indicate Channel                                |      |

| 4.1.1.4   | Monitor Channel                                         |      |

| 4.1.1.4.1 | Handshake Procedure                                     |      |

| 4.1.1.4.2 | Monitor Procedure Timeout (TOD)                         |      |

| 4.1.1.4.3 | MON-1, MON-2 Commands (S/Q Channel Access)              |      |

| 4.1.1.4.4 | MON-8 Commands (Register Access)                        |      |

| 4.1.2     | S/T-Interface                                           |      |

| 4.1.2.1   | S/T-Interface Coding                                    |      |

| 4.1.3     | S/T-Interface Multiframing                              | 117  |

| Contents  | (cont'd)                                             | Page  |

|-----------|------------------------------------------------------|-------|

| 4.1.4     | Maintenance Auxiliary Interface (MAI)                | . 118 |

| 4.1.4.1   | I/O Specific Mode                                    | . 118 |

| 4.1.4.2   | Standard I/O Mode                                    | . 119 |

| 4.1.4.3   | $\mu P$ MAI Mode                                     | . 120 |

| 4.2       | Control Procedures                                   | . 122 |

| 4.2.1     | Complete Activation Initiated by Exchange (LT-S)     | . 123 |

| 4.2.2     | Complete Activation Initiated by Exchange (NT)       | . 124 |

| 4.2.3     | Complete Activation Initiated by Terminal            | . 125 |

| 4.2.4     | Complete Deactivation                                | . 126 |

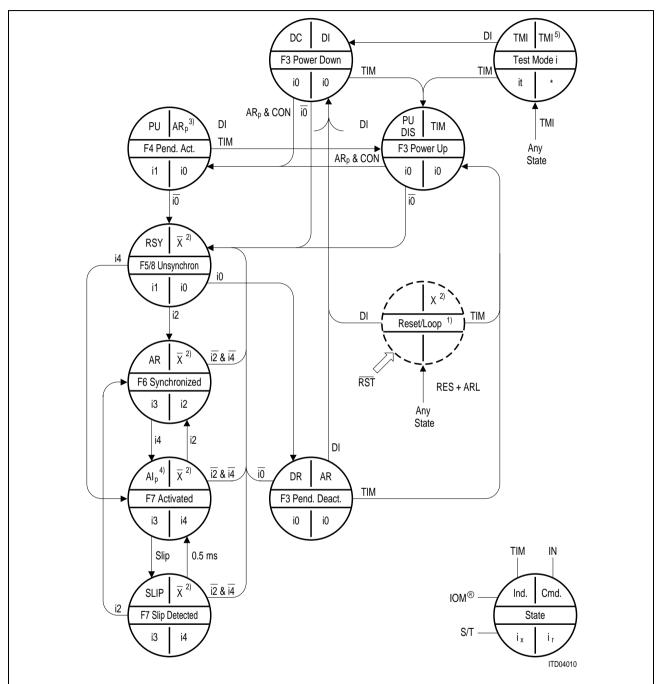

| 4.3       | State Machine                                        | . 128 |

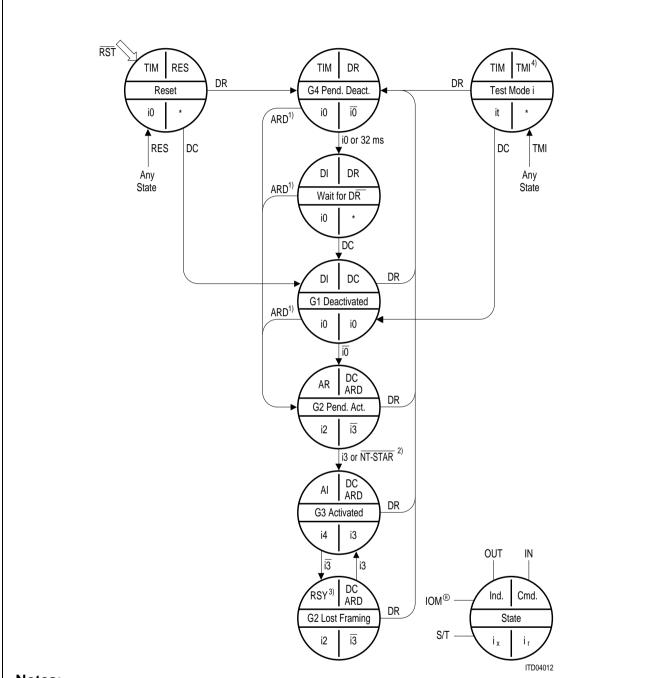

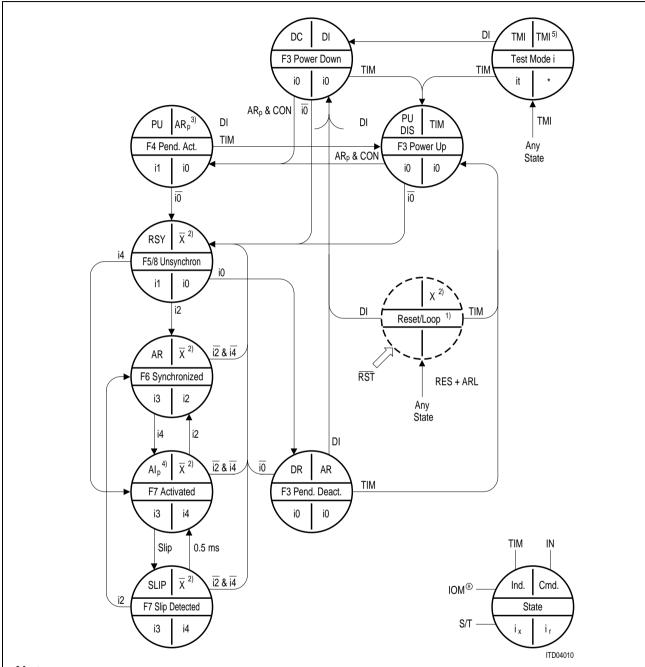

| 4.3.1     | State Machine TE/LT-T Modes                          | . 129 |

| 4.3.1.1   | TE/LT-T Modes State Diagram                          | . 130 |

| 4.3.1.2   | TE/LT-T Modes Transition Criteria                    | . 132 |

| 4.3.1.2.1 | C/I Commands                                         | . 132 |

| 4.3.1.2.2 | Pin States                                           | . 133 |

| 4.3.1.2.3 | S/T-Interface Events                                 | . 133 |

| 4.3.1.3   | Transmitted Signals and Indications in TE/LT-T Modes | . 133 |

| 4.3.1.3.1 | C/I Indications                                      |       |

| 4.3.1.3.2 | S/T-Interface Signals                                | . 134 |

| 4.3.1.4   | States TE/LT-T Mode                                  | . 135 |

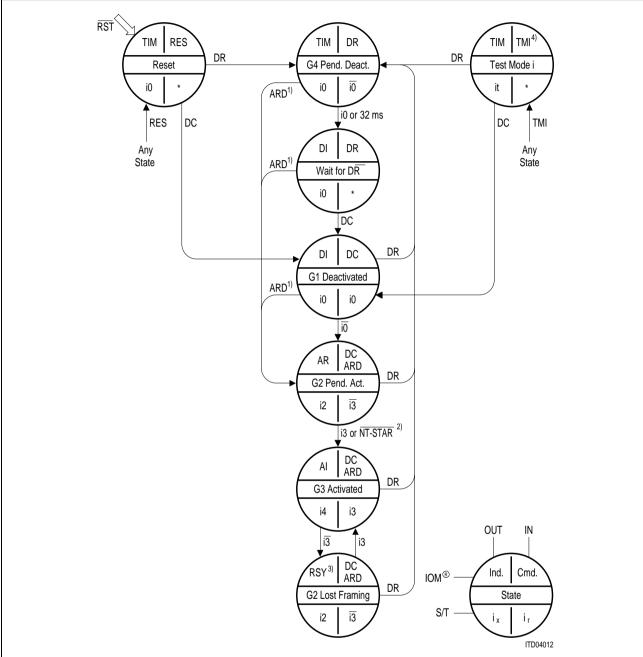

| 4.3.2     | State Machine LT-S Mode                              | . 136 |

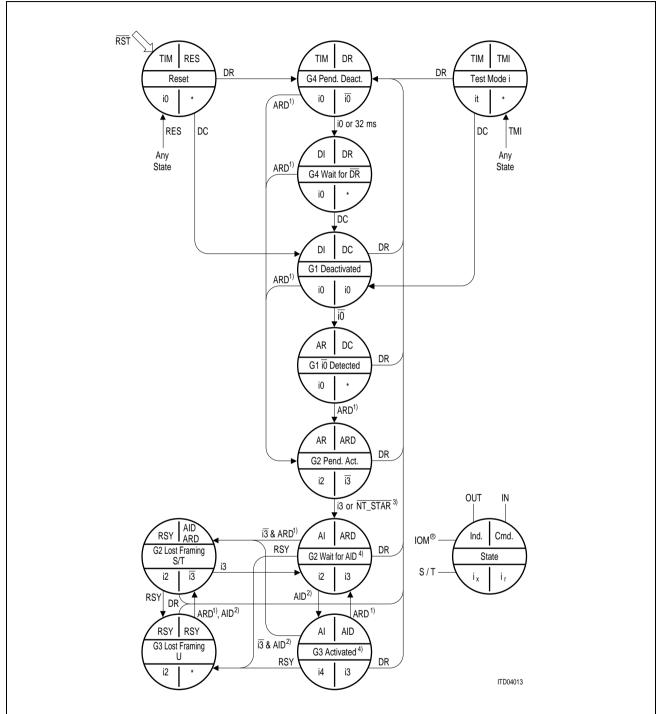

| 4.3.2.1   | LT-S Mode State Diagram                              | . 137 |

| 4.3.2.2   | LT-S Mode Transition Criteria                        | . 138 |

| 4.3.2.2.1 | C/I Commands                                         | . 138 |

| 4.3.2.2.2 | Pin States                                           | . 138 |

| 4.3.2.2.3 | S/T-Interface Events                                 | . 138 |

| 4.3.2.3   | Transmitted Signals and Indications in LT-S Mode     | . 139 |

| 4.3.2.3.1 | C/I Indications                                      |       |

| 4.3.2.3.2 | S/T-Interface Signals                                | . 139 |

| 4.3.2.4   | States LT-S Mode                                     | . 140 |

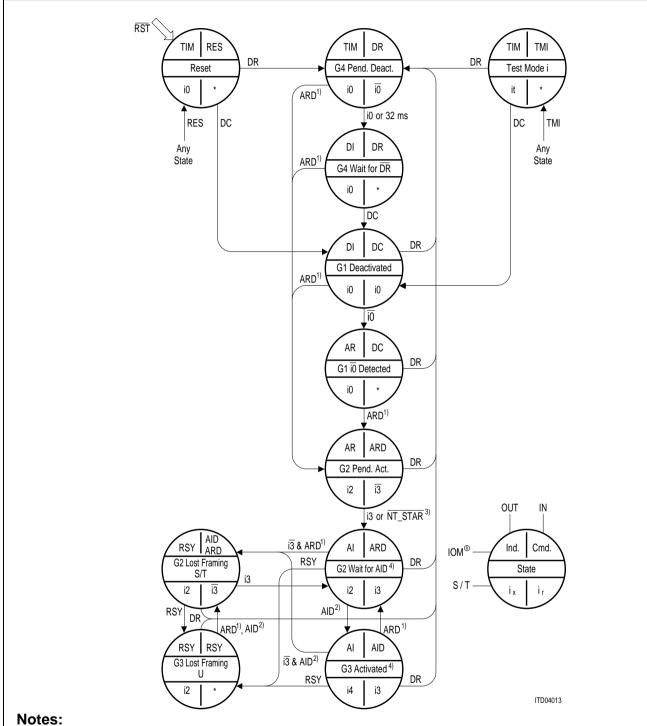

| 4.3.3     | State Machine NT Mode                                | . 140 |

| 4.3.3.1   | NT Mode State Diagram                                | . 141 |

| 4.3.3.2   | NT Mode Transition Criteria                          | . 142 |

| 4.3.3.2.1 | C/I Commands                                         | . 142 |

| 4.3.3.2.2 | Pin States                                           | . 143 |

| 4.3.3.2.3 | S/T-Interface Events                                 |       |

| 4.3.3.3   | Transmitted Signals and Indications in NT Mode       | . 143 |

| 4.3.3.3.1 | C/I Indications                                      | . 143 |

| 4.3.3.3.2 | S/T-Interface Signals                                | . 144 |

| 4.3.3.4   | States NT Mode                                       | . 144 |

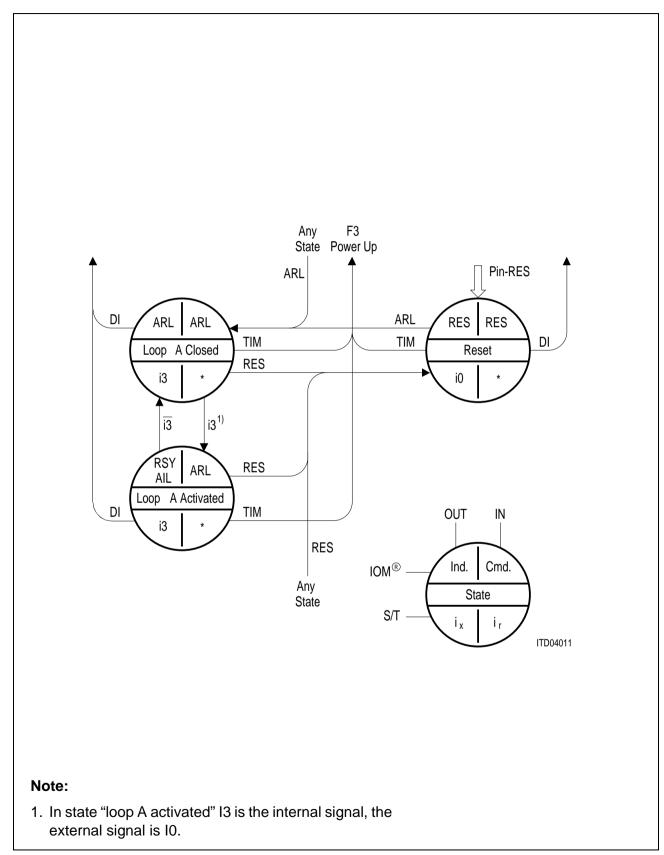

| 4.4       | Reset                                                |       |

| 4.4.1     | C/I Command RES                                      |       |

| 4.4.2     | Hardware Reset RST                                   | . 146 |

| 4.4.3     | Push/Pull Sensing                                    | . 146 |

| 4.4.4     | Initializing LT-T Mode                               | . 146 |

#### **General Information**

### **SIEMENS**

| Contents     | (cont'd)                                         | Page |

|--------------|--------------------------------------------------|------|

| 4.5<br>4.5.1 | Maintenance Functions  Test Loop-Backs           |      |

| 4.5.1.1      | Complete Loop-Backs (No. 2, No. 3, and No. A)    |      |

| 4.5.1.2      | Single Channel Loop-Backs (No. 4, No. B2, No. C) | 148  |

| 4.5.2        | Monitoring of Illegal Code Violations            | 148  |

| 4.6          | Clock Generation and Clock Characteristics       | 149  |

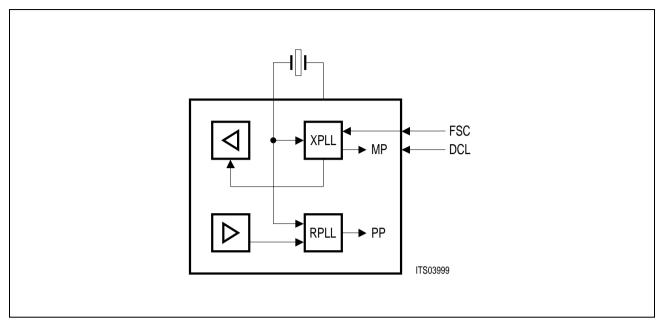

| 4.6.1        | NT and LT-S Mode                                 | 150  |

| 4.6.1.1      | Transmit and Receive PLL                         | 150  |

| 4.6.1.2      | Jitter Requirements                              | 151  |

| 4.6.2        | LT-T and TE Mode                                 | 152  |

| 4.6.2.1      | Receive PLL in TE and LT-T Mode                  | 152  |

| 4.7          | Elastic Buffers in LT-T Mode                     | 153  |

| 4.7.1        | Elastic Buffer                                   | 153  |

| 4.7.1.1      | Jitter Requirements                              | 153  |

| 4.7.1.2      | Output Clock Characteristics                     | 153  |

| 4.7.2        | Recommended Oscillator Circuit                   | 155  |

| 4.8          | Analog Line Port                                 | 156  |

| 4.8.1        | Receiver Characteristics                         | 156  |

| 4.8.2        | Transmitter Characteristics                      | 158  |

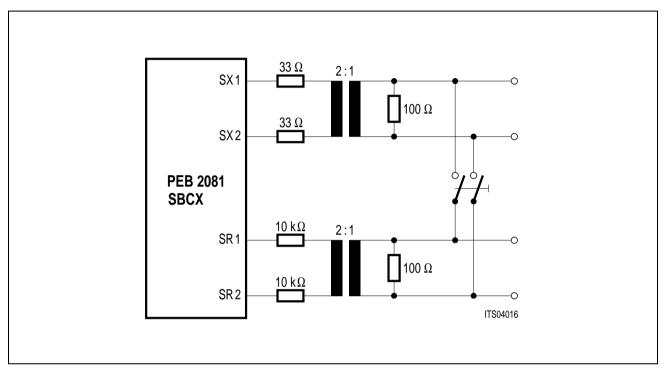

| 4.8.3        | S/T-Interface Circuitry                          | 159  |

| 4.8.3.1      | S/T-Interface Transformer                        | 161  |

| 4.8.3.2      | Line Overload Protection (Transmitter, Receiver) | 162  |

| 4.8.4        | Transmitter Input Current                        | 163  |

| 4.8.5        | Receiver Input Current                           | 164  |

| 5            | Electrical Characteristics                       | 165  |

| 5.1          | Absolute Maximum Ratings                         | 165  |

| 5.2          | Power Supply                                     |      |

| 5.3          | Capacitances                                     | 166  |

| 5.4          | DC Characteristics                               | 167  |

| 5.5          | Power Consumption                                | 168  |

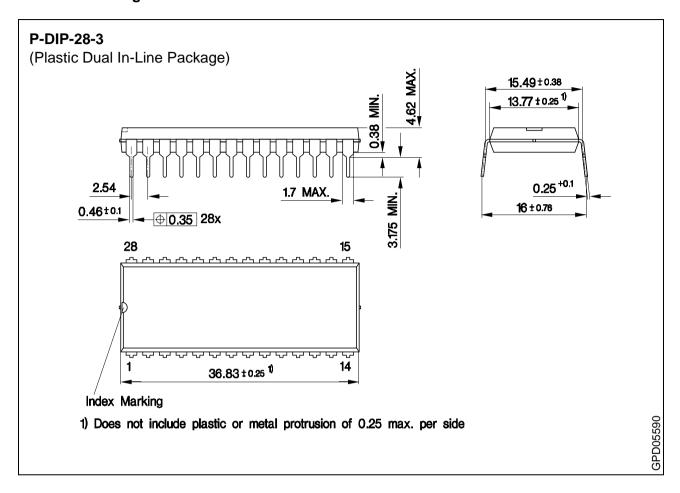

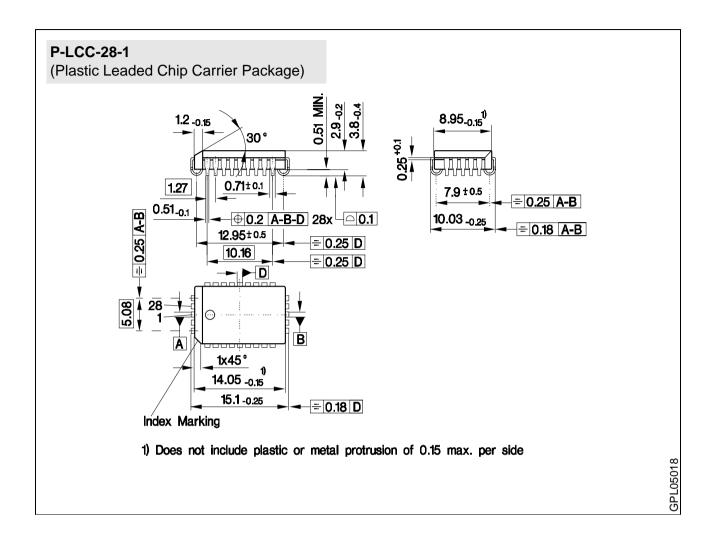

| 6            | Package Outlines                                 | 169  |

| 7            | Appendix                                         | 171  |

| 7.1          | Delta and Errata Sheets                          |      |

| 7.2          | External Components Information                  |      |

| 7.3          | Quick Reference Guide                            |      |

$SICOFI^{@}, SICOFI^{@}-2, SLICOFI^{@}, ARCOFI^{@}, EPIC^{@}-1, EPIC^{@}-2, IPAT^{@}, IOM^{@}, IOM^{@}-1, IOM^{@}-2, ISAC^{@}-S, ISAC^{@}-P, IDEC^{@} are registered trademarks of Siemens AG.$

ELIC<sup>™</sup>, MUSAC<sup>™</sup>, MUSAC<sup>™</sup>-A, OCTAT<sup>™</sup>-P are trademarks of Siemens AG.

| Table of F | igures I                                                                                                  | Page |

|------------|-----------------------------------------------------------------------------------------------------------|------|

| Figure 1:  | PEB 2081 SBCX in P-DIP-28 and P-LCC-28-R Packages                                                         | 12   |

| Figure 2:  | Logic Symbol of the SBCX                                                                                  | 14   |

| Figure 3:  | Block Diagram of the SBCX                                                                                 | 15   |

| Figure 4:  | Operating Modes of the SBCX in the ISDN Basic Access Architecture                                         | 16   |

| Figure 5:  | ISDN Voice/Data Terminal using the IOM®-2 Terminal Architecture (TE)                                      | 17   |

| Figure 6:  | SBCX in TE Mode                                                                                           | 18   |

| Figure 7:  | Basic Network Terminator (NT1)                                                                            | 19   |

| Figure 8:  | SBCX in NT-Mode                                                                                           | 20   |

| Figure 9:  | NT-Star Configuration with 8 TEs Connected Point-to-Point                                                 | 21   |

| Figure 10: | NT-Star Configuration with 2 TEs Connected Point-to-Point and 6 TEs Connected via an Extended Passive Bus | 21   |

| Figure 11: | NT-Star Configuration                                                                                     | 22   |

| Figure 12: | SBCX in NT-Star Mode                                                                                      | 23   |

| Figure 13: | Micro Controlled NT Configuration                                                                         | 24   |

| Figure 14: | Intelligent NT Providing both Terminal (voice/data) and Network Terminating Functions (S/T-interface)     | 25   |

| Figure 15: | SBCX in LT-S Mode for Intelligent NT Configurations                                                       | 26   |

| Figure 16: | IOM®-2 Line Card Architecture (LT-S) with One D-Channel Controller per Line                               | 27   |

| Figure 17: | SBCX in LT-S Mode for Basic Line Card Configuration                                                       | 28   |

| Figure 18: | IOM®-2 Line Card Architecture (LT-S only) with One D-Channel Controller per up to Eight Lines             | 29   |

| Figure 19: | SBCX in LT-S Mode for Star Configuration                                                                  |      |

| _          | PBX Architecture (LT-T) with One D-Channel Controller per Line                                            |      |

| _          | PBX-Configuration Requiring S/G Bit Evaluation                                                            |      |

| Figure 22: | SBCX in LT-T Mode                                                                                         | 33   |

| Figure 23: | Clock Generation for TE Mode                                                                              | 37   |

| Figure 24: | Clocks Generation in NT Mode                                                                              | 38   |

| Figure 25: | Clock Generation in LT-T Mode                                                                             | 39   |

| Figure 26: | Clock Generation in LT-S Mode                                                                             | 41   |

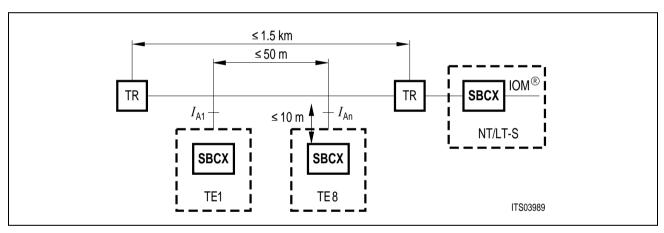

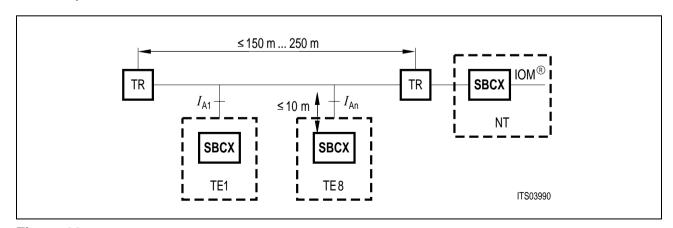

| Figure 27: | S/T-Interface Point-to-Point Configuration ("TR" stands for the 100 $\Omega$ Terminating Resistor)        | 42   |

| Figure 28: | S/T-Interface Extended Passive Bus Configuration ("TR" stands for the 100 $\Omega$ Terminating Resistor)  | 42   |

| Figure 29: | S/T-Interface Short Passive Bus Configuration ("TR" stands for the 100 $\Omega$ Terminating Resistor)     |      |

| Figure 30: | SBCX Device Architecture                                                                                  |      |

| -          | IOM®-2 Interface Structure                                                                                |      |

|            | Basic Channel Structure of IOM®-2                                                                         |      |

| •          | Multiplexed Frame Structure of the IOM®-2 Interface                                                       | 47   |

| Table of F | Figures (cont'd)                                                     | age  |

|------------|----------------------------------------------------------------------|------|

| Figure 34: | Definition of the IOM <sup>®</sup> -2 Channels in a Terminal         | . 48 |

| Figure 35: | C/I-Channel Use with the ICC (all data values hexadecimal)           | . 52 |

| Figure 36: | C/I-Channel Use with the EPIC® (all data values hexadecimal)         | . 53 |

| Figure 37: | Monitor Channel Handling with ICC (all data values hexadecimal)      | . 55 |

| Figure 38: | Monitor Channel Handling with EPIC® (all data values hexadecimal)    | . 57 |

| Figure 39: | S Multiframe Structure                                               | 65   |

| Figure 40: | S-Frame Structure                                                    | 65   |

| Figure 41: | D-Channel Access Control on TIC Bus and S Bus                        | 74   |

| Figure 42: | Data Flow for Collision Resolution Procedure in Intelligent NT       | . 80 |

| Figure 43: | Intelligent NT-Configuration for IOM®-2 Channel Switching            | . 81 |

| Figure 44: | Test Loop-Backs Supported by PEB 2081                                | . 84 |

| Figure 45: | External Loop at the S/T-Interface                                   | . 86 |

| Figure 46: | Single Loops of the SBCX                                             | . 87 |

| Figure 47: | IOM®-2 Interface Timing                                              | . 92 |

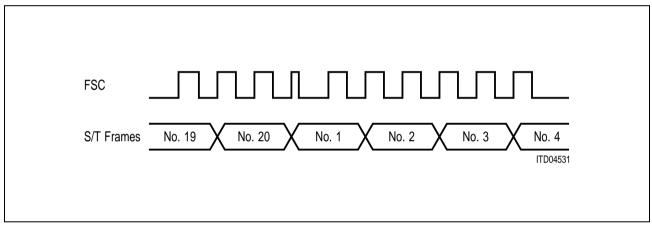

| Figure 48: | S/T-Interface Multi-Frame Synchronization                            | . 93 |

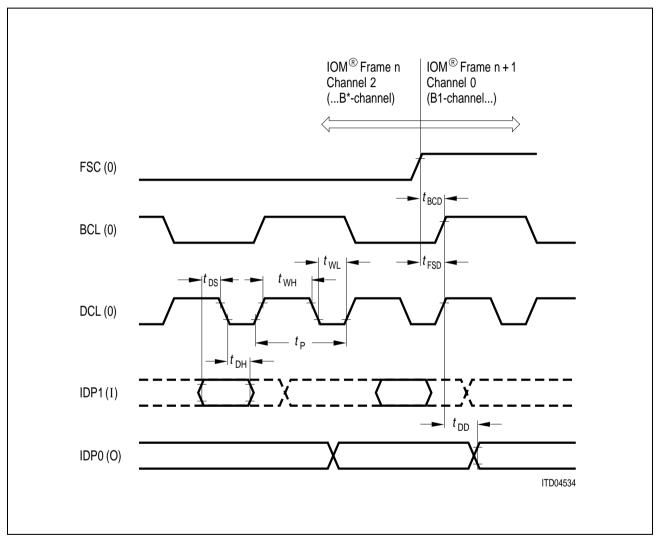

| Figure 49: | Timing of the IOM®-2 Interface in TE Mode                            | . 94 |

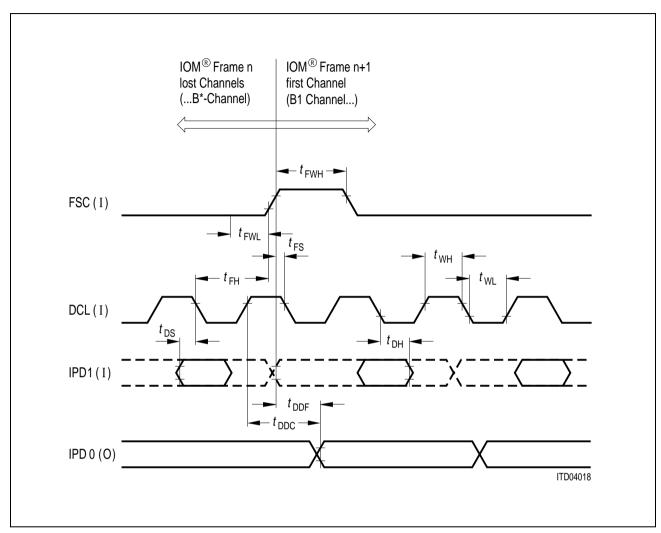

| Figure 50: | Timing of the IOM®-2 Interface in NT / LT-S and LT-T Mode            | . 96 |

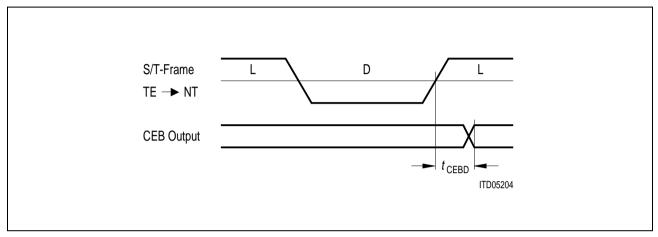

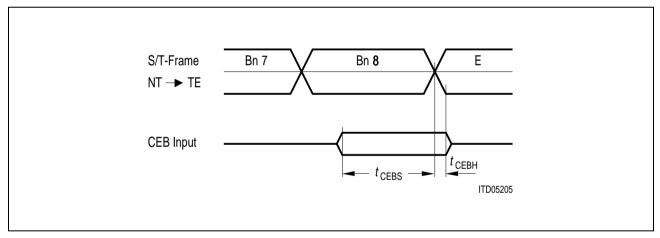

| Figure 51: | Timing of the CEB Output                                             | . 98 |

| Figure 52: | Timing of the CEB Input                                              | . 98 |

| Figure 53: | Functional Timing of the CEB                                         | . 99 |

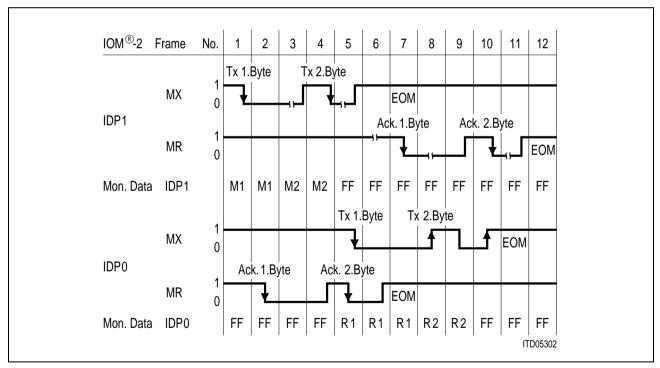

| Figure 54: | Handshake Protocol with a 2-Byte Monitor Message/Response            | 103  |

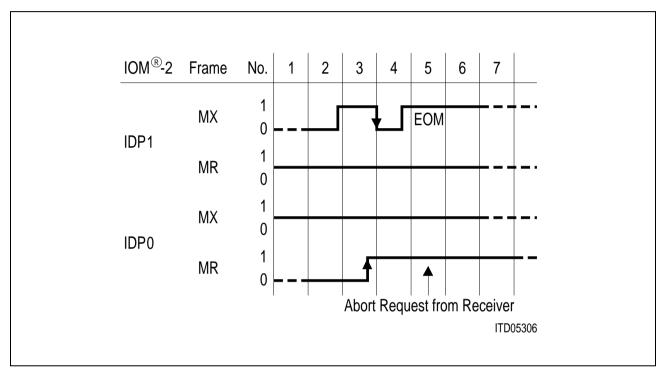

| Figure 55: | Abortion of Monitor Channel Transmission                             | 105  |

| Figure 56: | S/T -Interface Line Code (without code violation)                    | 115  |

| Figure 57: | Frame Structure at Reference Points S and T (ITU I.430)              | 115  |

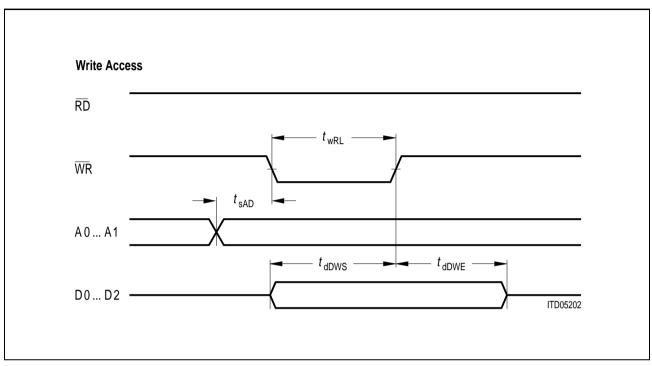

| Figure 58: | Dynamic Characteristics of $\mu P$ Interface Write Access            | 120  |

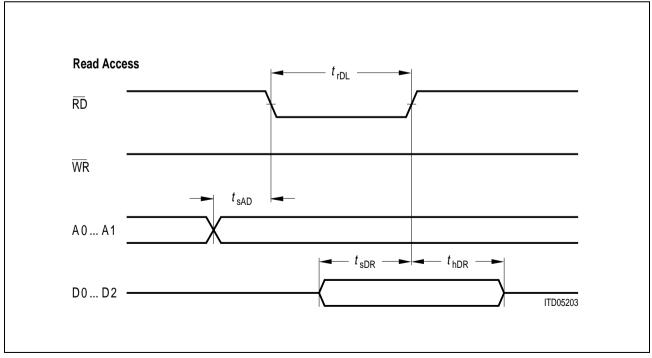

| Figure 59: | Dynamic Characteristics of $\mu P$ Interface Read Access             | 120  |

| Figure 60: | Complete Activation Initiated by Exchange (LT-S)                     | 123  |

| Figure 61: | Complete Activation Initiated by Exchange (NT)                       | 124  |

| •          | Complete Activation Initiated by TE                                  |      |

| Figure 63: | Deactivation Procedure                                               | 126  |

| Figure 64: | Deactivation of the $IOM^{®}$ -2 Interface in the NT (DCL = 512 kHz) | 127  |

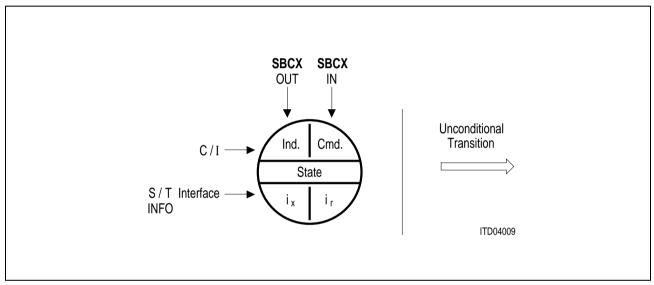

| Figure 65: | State Diagram Notation                                               | 128  |

| Figure 66: | State Transition Diagram in TE/LT-T Modes                            | 130  |

| Figure 67: | State Diagram of the TE/LT-T Modes, Unconditional Transitions        | 131  |

| Figure 68: | State Transition Diagram in LT-S Mode                                | 137  |

| Figure 69: | NT Mode State Diagram                                                | 141  |

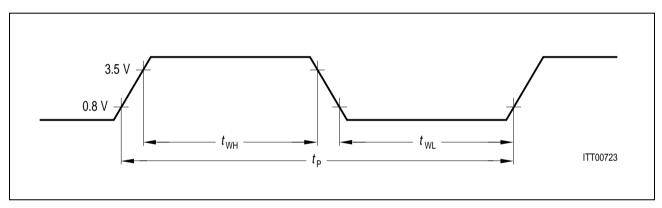

| Figure 70: | Dynamic Characteristics of Duty Cycle                                | 149  |

| Figure 71: | Clock System of the SBCX in NT and LT-S Mode                         | 151  |

### **General Information**

| Table of Figures (cont'd) |                                              |     |  |  |

|---------------------------|----------------------------------------------|-----|--|--|

| Figure 72:                | Receive PLL of the SBCX in TE Mode           | 152 |  |  |

| Figure 73:                | Receive PLL of the SBCX in LT-T Mode         | 152 |  |  |

| Figure 74:                | Phase Relationships of TE Clock Signals      | 154 |  |  |

| Figure 75:                | Recommended Oscillator Circuits              | 155 |  |  |

| Figure 76:                | Receiver Circuit                             | 156 |  |  |

| Figure 77:                | Receiver Thresholds                          | 157 |  |  |

| Figure 78:                | Transmitter Output Stage                     | 158 |  |  |

| Figure 79:                | Dynamic Transmitter Characteristics          | 158 |  |  |

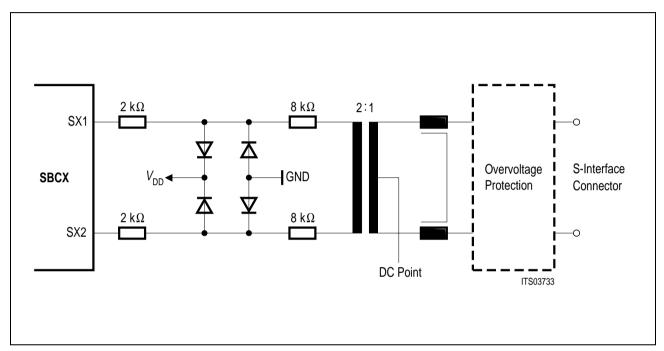

| Figure 80:                | External Circuitry Transmitter               | 159 |  |  |

| Figure 81:                | External Circuitry Receiver                  | 160 |  |  |

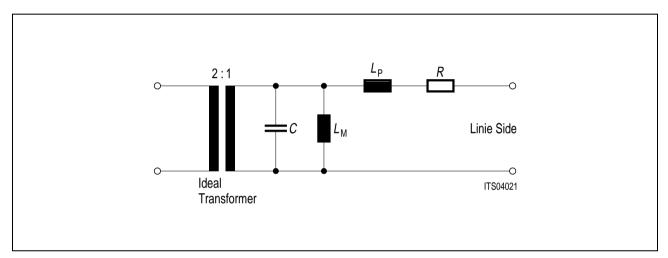

| Figure 82:                | Transformer Model                            | 161 |  |  |

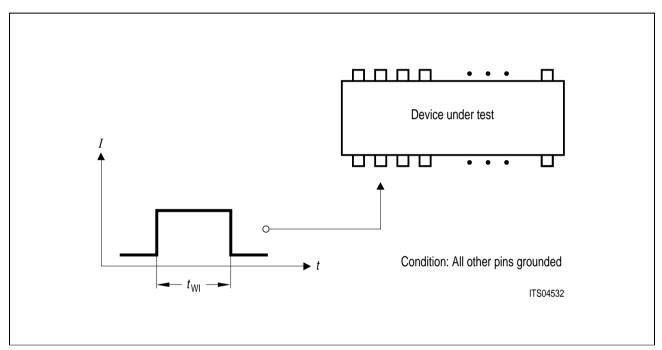

| Figure 83:                | Test Condition for Maximum Input Current     | 162 |  |  |

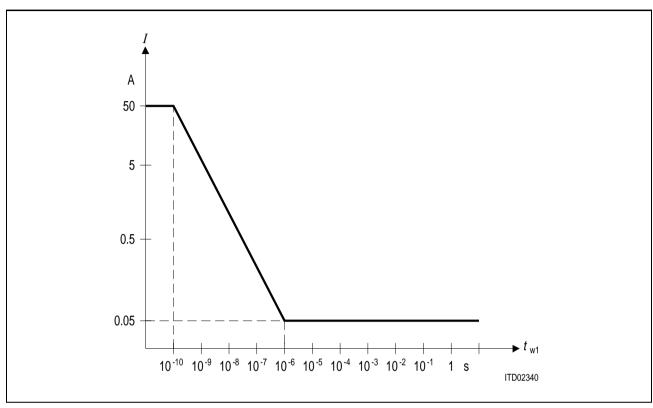

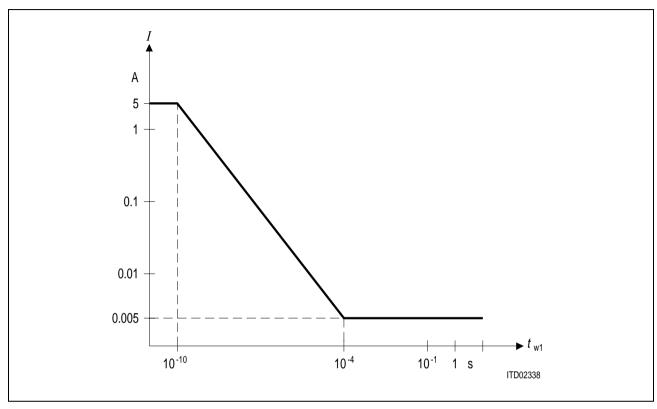

| Figure 84:                | Destruction Limits Transmitter Input Current | 163 |  |  |

| Figure 85:                | Destruction Limits Receiver Input Current    | 164 |  |  |

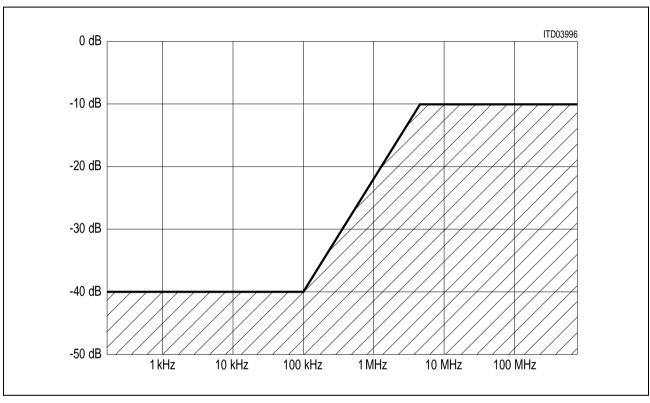

| Figure 86:                | Power Supply Rejection SBCX Receiver         | 166 |  |  |

| Figure 87:                | State Transition Diagram in TE/LT-T Modes    | 189 |  |  |

| Figure 88:                | State Diagram of the LT-S Mode               | 190 |  |  |

| Figure 89:                | NT Mode State Diagram                        | 191 |  |  |

#### Introduction

The PEB 2081 S/T Bus Interface Circuit Extended (SBCX) implements the four-wire S/T-interface used to link voice/data ISDN terminals, network terminators and PABX trunk lines to a Central Office.

The SBCX provides the electrical and functional link between the analog S/T-interface according to ITU recommendation I.430, ETS 300 012 and T1.605 Basic User Network Interface Specification respectively, and the ISDN Oriented Modular interface Rev. 2 (IOM-2).

This manual is divided into 6 major sections. Compared to previous data sheets for the S transceiver, the organization of the data sheet for version 3.4 has been modified in order to make information more readily available to the user.

**Section 1** gives the user an introduction to the PEB 2081 Vers. 3.4. It contains information about the functional blocks, features and pinning of the SBCX.

**Section 2** provides an overview of typical ISDN applications and demonstrates how these applications can be realized with the PEB 2081 Vers. 3.4.

**Sections 3** and **4** are identical in structure. Both cover the major S transceiver topics "Interfaces", "Control Procedures" and "Maintenance Functions". **Section 3** gives the user an overview on the discussed topics without going into technical details. It is intended as an application guide where the user can quickly look up how the registers of ICC, EPIC and SBCX Vers. 3.4 need to be programmed in order to initiate the desired action.

**Section 4** is dedicated to detailed technical information. Status diagrams, state descriptions, algorithms, dynamic characteristics are to be found here. **Section 4** thus is intended for the user who seeks specific technical information.

Section 5 summarizes all electrical, section 6 all environmental characteristics.

#### S/T Bus Interface Circuit Extended

**PEB 2081**

#### 1 Features

- Full duplex 2B+D S/T-interface transceiver according to the following specifications:

- ITU Recommendation I.430

- ETS 300 012

- ANSI T1.605

- 192 kbit/s transmission rate

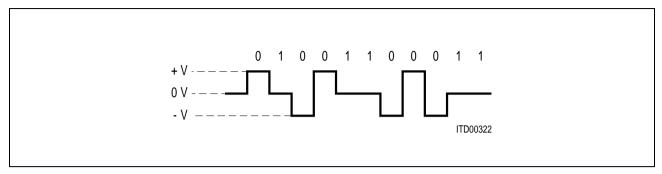

- Pseudo-ternary coding with 100 % pulse width

- Activation and deactivation procedures

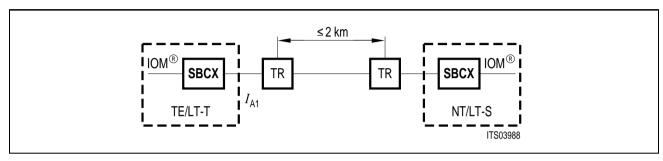

- Extended loop-length up to 2 km

#### IOM®-2 Interface

- Optimized for operation in conjunction with IEC-Q, IBC, ICC, EPIC and IDEC telecom ICs

- Handling of commands and indications contained in the IOM-2 C/I channel for activation, deactivation and testing

- Switching of test-loops

#### Modes

TE : Terminal Mode

NT : Network termination connected to IEC-Q

LT-T : Trunk mode in private exchange

LT-S: Line termination in public or private exchanges

#### **Special Features**

- Fully compliant NT2 trunk mode including multipoint operation

- Frame alignment with absorption of phase wander in NT2 network side applications

- D channel access control, also in trunk application

- Access to S and Q bits of S/T-interface (S1, S2 and Q channel)

- Software controlled maintenance interface (I/O ports)

- Switching of test loops

- Advanced CMOS technology with low power consumption: power down max. 4 mW operational max. 60 mW

| Туре      | Ordering Code | Package    |

|-----------|---------------|------------|

| PEB 2081P | Q67100-H6581  | P-DIP-28-3 |

| PEB 2081N | Q67100-H6580  | P-LCC-28-1 |

### 1.1 Pin Configuration

(top view)

Figure 1

PEB 2081 SBCX in P-DIP-28-3 and P-LCC-28-1 Packages

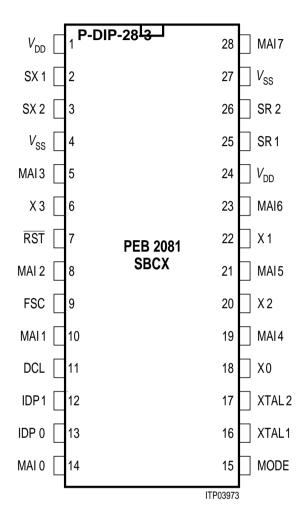

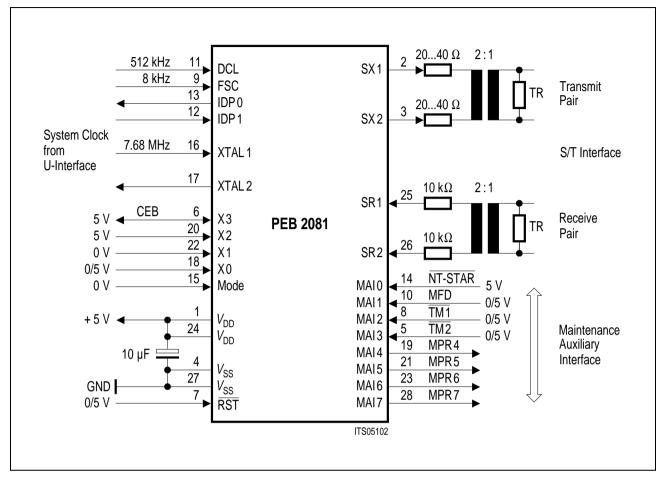

#### 1.2 Pin Definition and Functions

| Pin No.             | Symbol               | Input (I)<br>Output (O) | Function                                                                                                                                                   |  |

|---------------------|----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11                  | DCL                  | I/O                     | Data Clock The frequency is equal to twice the data rate on the IOM-2 interface. LT-S, LT-T, NT: clock input 512 kHz to 8192 kHz TE: clock output 1536 kHz |  |

| 9                   | FSC                  | I/O                     | Frame Synchronization Clock LT-S, LT-T, NT: clock input 8 kHz TE: clock output 8 kHz                                                                       |  |

| 13                  | IDP0                 | I/O                     | IOM-2 data port 0; open drain with an external pull up resistor, otherwise push/pull                                                                       |  |

| 12                  | IDP1                 | I/O                     | IOM-2 data port 1; open drain (if external pull up resistor at IDP0), otherwise push/pull                                                                  |  |

| 25                  | SR1                  | I                       | Differential S/T-interface receiver signal input                                                                                                           |  |

| 26                  | SR2                  | I                       | Differential S/T-interface receiver signal input                                                                                                           |  |

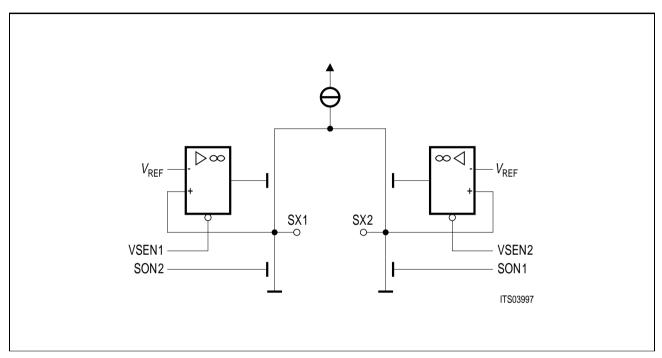

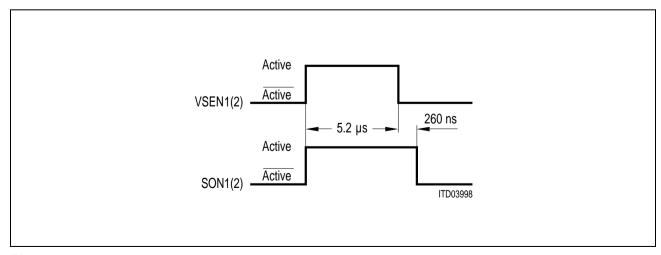

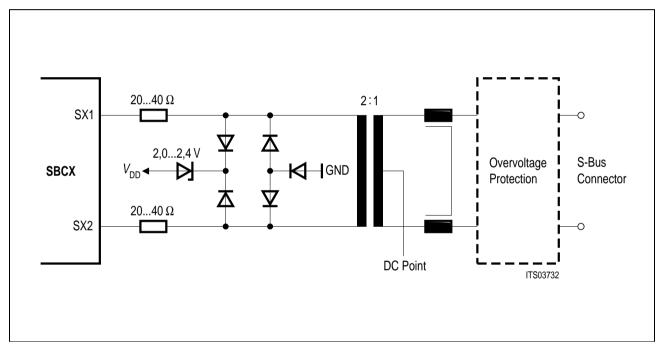

| 2                   | SX1                  | 0                       | Differential S/T-interface positive transmitter output                                                                                                     |  |

| 3                   | SX2                  | 0                       | Differential S/T-interface negative transmitter output                                                                                                     |  |

| 15                  | MODE                 | I                       | Setting of either LT modes or NT and TE mode                                                                                                               |  |

| 6<br>20<br>22<br>18 | X3<br>X2<br>X1<br>X0 | I/O<br>I<br>I<br>I/O    | Specific function pins dependent from the selected operating mode                                                                                          |  |

| 28, 23, 21, 19      | MAI (7:4)            | 0                       | Maintenance Auxiliary Interface; output pins                                                                                                               |  |

| 5                   | MAI 3                | I                       | Maintenance Auxiliary Interface; input pin                                                                                                                 |  |

| 8, 10, 14           | MAI (2:0)            | I/O                     | Maintenance Auxiliary Interface; input/output pins                                                                                                         |  |

| 24                  | $V_{DD}$             | I                       | Power supply + 5 V ± 5 %                                                                                                                                   |  |

| 1                   | $V_{DD}$             | I                       | Power supply + 5 V ± 5 %                                                                                                                                   |  |

| 4                   | $V_{\mathtt{SS}}$    | I                       | Ground                                                                                                                                                     |  |

| 27                  | $V_{\mathtt{SS}}$    | I                       | Ground                                                                                                                                                     |  |

| 7                   | RST                  | I                       | Reset, low active                                                                                                                                          |  |

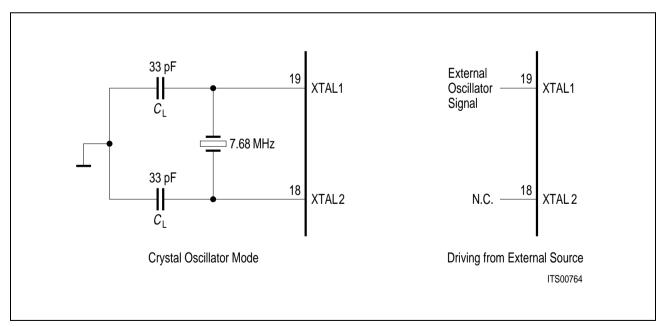

| 16                  | XTAL1                | I                       | Connection for external crystal, or input for external clock generator                                                                                     |  |

| 17                  | XTAL2                | 0                       | Connection for external crystal,<br>not connected, when an external clock generator is<br>used                                                             |  |

### 1.3 Logic Symbol

Figure 2 Logic Symbol of the SBCX

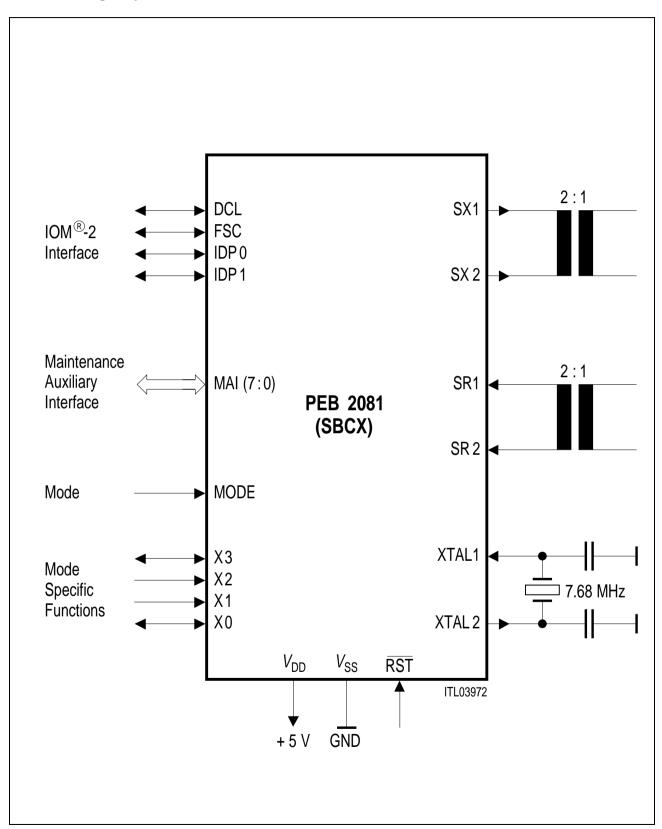

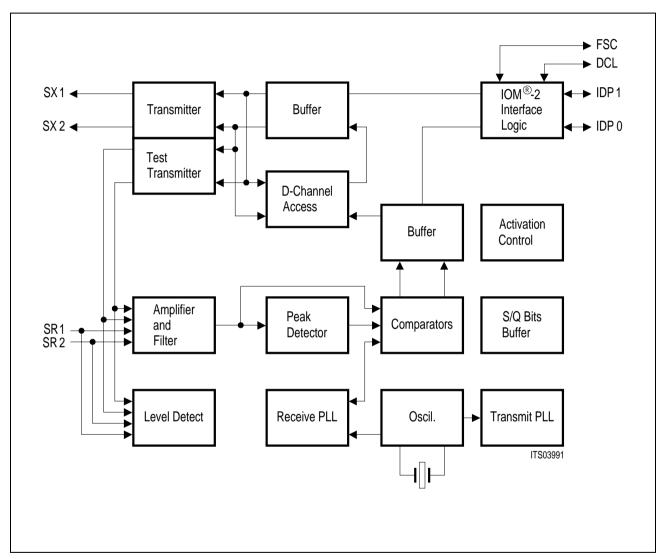

### 1.4 Functional Block Diagram

Figure 3

Block Diagram of the SBCX

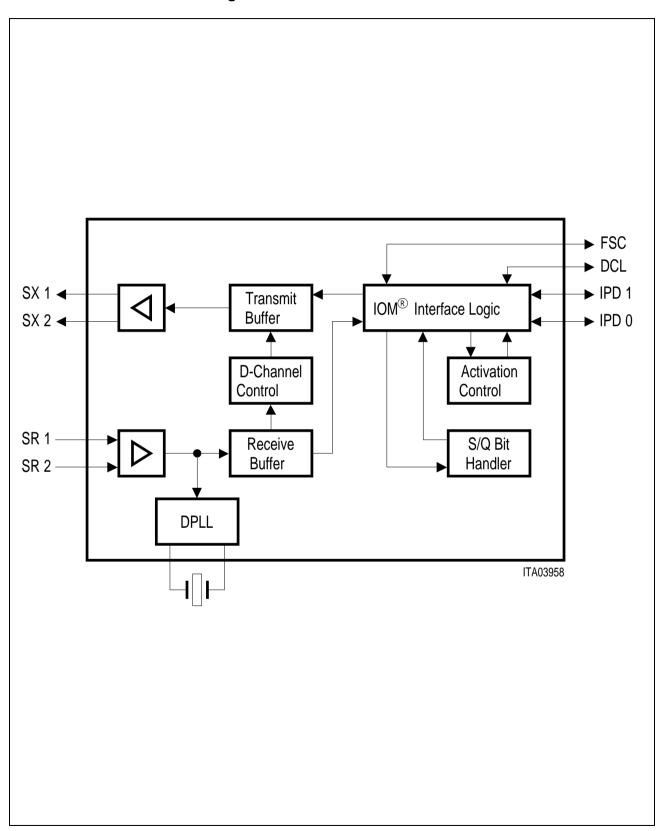

#### 2 System Integration and Applications

The SBCX implements the four-wire S- and T-interfaces used in the ISDN basic access. By programming the corresponding operating mode it may be used at both ends of these interfaces.

The operating modes are:

- ISDN terminals (TE)

- ISDN network termination (NT) for a link between the four-wire S/T-interface and the two-wire U-interface

- ISDN subscriber line termination (LT-S)

- ISDN trunk line termination (LT-T); (PBX connection to Central Office).

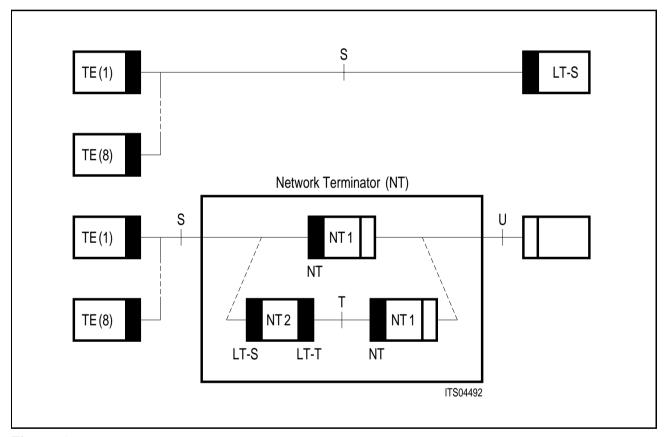

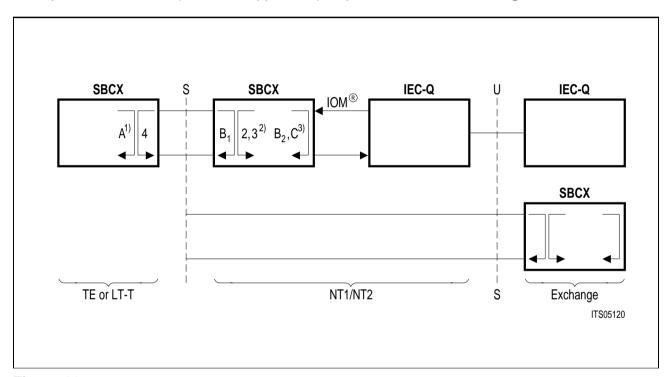

The basic use of these modes is shown in the following figure, where the usual nomenclature as defined by the ITU for the basic access functional blocks and reference points, is used.

Figure 4

Operating Modes of the SBCX in the ISDN Basic Access Architecture

The NT equipment serves as a converter between the U-interface at the exchange and the S-interface at the user premises. The NT may consist of either an NT1 or an NT1 together with an NT2 connected via the T-interface which is physically identical to the S-interface. The NT1 is a direct transformation between layer 1 of S and layer 1 of U. NT2 may include higher level functions like multiplexing and switching as in a PBX.

#### 2.1 Operational Modes and System Integration

#### 2.1.1 TE Application

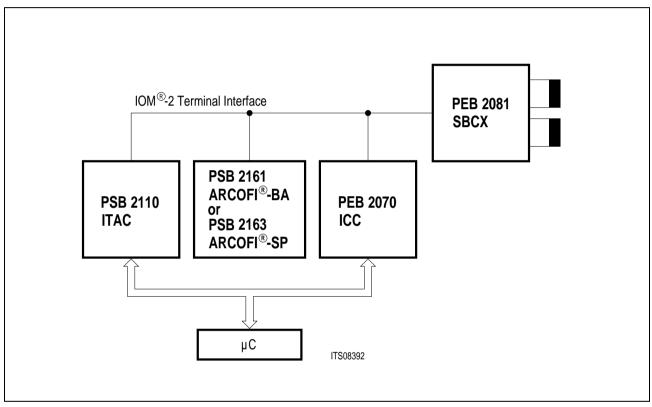

In the terminal several IOM-2 compatible devices can be connected to the IOM-2 bus structure (e.g. PEB 2070 ISDN Communications Controller (ICC), PSB 2161 Audio Ringing Codec Filter (ARCOFI®), PSB 2163 Audio Ringing Codec Filter (ARCOFI®SP) and PSB 2110 ISDN Terminal Adapter Circuit (ITAC®)). The ICC allows access to IOM-2 bus by the microcontroller. The SBCX is controlled via MON0 channel, the other devices via MON1 channel of the IOM-2 bus.

Figure 5 ISDN Voice/Data Terminal using the IOM®-2 Terminal Architecture (TE)

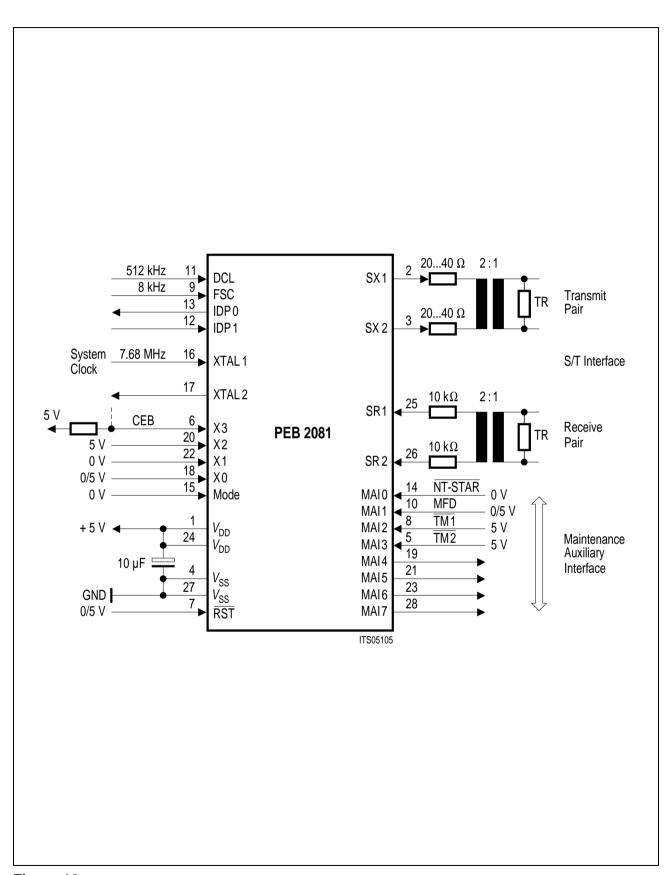

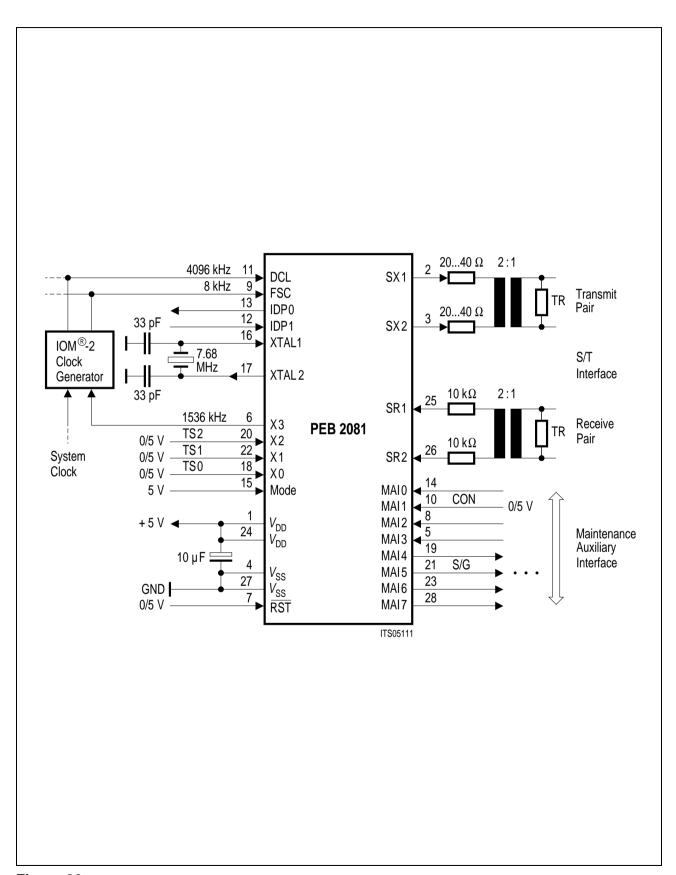

Figure 6 SBCX in TE Mode

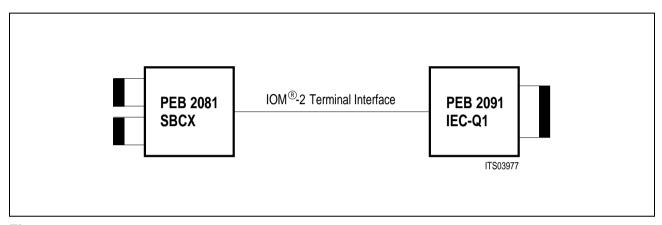

#### 2.1.2 ISDN Network Termination (NT1)

The S-interface is a four-wire interface for connecting ISDN Terminal Equipment (TE) and Terminal Adapter (TA) to the Network Termination (NT). From here a twisted pair interfaces to the exchange. The Network Terminator interfaces the four-wire to the two-wire interface.

A basic Network Terminator (NT1) can be built using the SBCX together with the PEB 2091 ISDN Echo-Cancellation Circuit (IEC-Q1) or in case of a private exchange the PEB 2095 ISDN Burst Transceiver Circuit (IBC). All information between S- and U-interface is handled automatically between the layer-1 devices IEC-Q (or IBC) and the SBCX.

Figure 7

Basic Network Terminator (NT1)

Figure 8 SBCX in NT-Mode

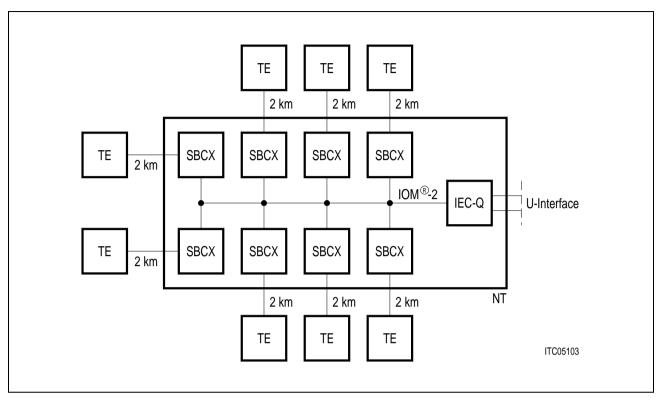

#### 2.1.3 ISDN Network Terminator (NT1) in Star Configuration

A NT-star configuration is used when it is not possible to connect all terminals with a short or extended passive bus configuration. This may be the case if the terminal locations are too far apart to comply to the restrictions specified for short or extended passive bus systems. In this application the IOM-2 interface operates with a DCL frequency of 512 kHz. Downstream data will be transmitted to all connected TEs. The upstream data from all TE's will be wired-ANDed on the IOM-2 interface.

The NT-star mode ensures under these circumstances, the correct D-channel collision detection as well as the correct activation behavior (see also **section 3.3**).

Both point-to-point or passive bus configurations are allowed. A combination of these two configurations is also possible, **see figure 9** and **10**.

Figure 9

NT-Star Configuration with 8 TEs Connected Point-to-Point

Figure 10 NT-Star Configuration with 2 TEs Connected Point-to-Point and 6 TEs Connected via an Extended Passive Bus

Figure 11 NT-Star Configuration

Figure 12 SBCX in NT-Star Mode

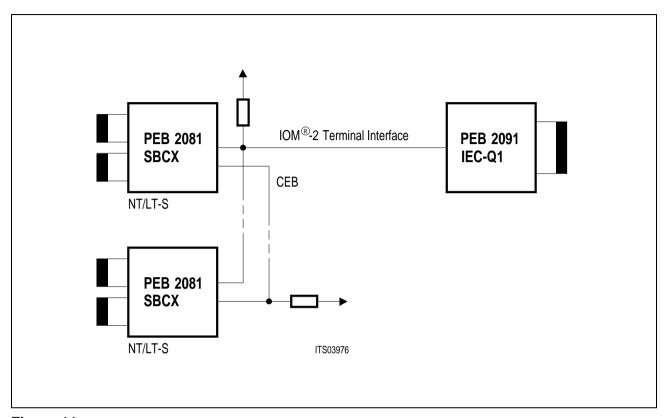

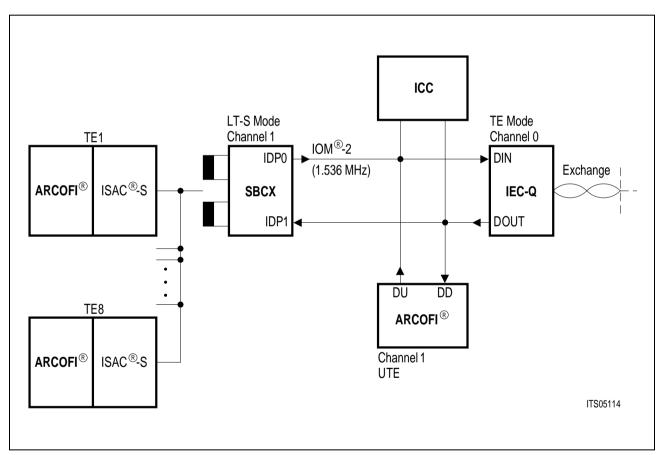

#### 2.1.4 ISDN Network Terminator Using IOM®-2 Architecture (Intelligent NT)

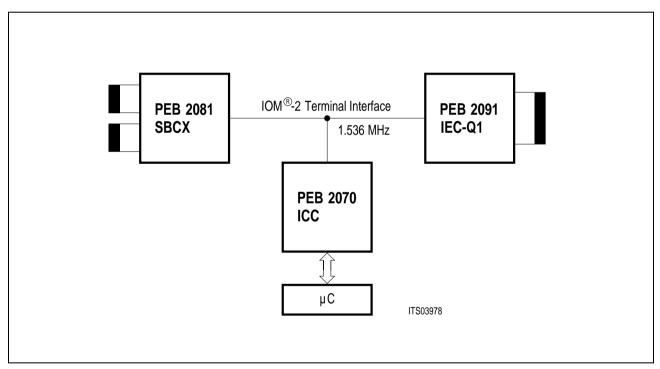

The IOM-2 architecture allows to build a **micro controlled NT** using additionally the ICC and operating the IEC-Q (or IBC) in the IOM-2 terminal mode. The ICC provides software controlled layer-1 maintenance function such as programming the SBCX via the monitor channel.

The SBCX is set to LT-S mode and is operated in the IOM-2 channel 1 of the IOM-2 terminal architecture. For that purpose the SBCX offers the possibility of changing the state machine from LT-S mode to NT mode (refer to FSMM-bit of the configuration register) in order to behave like a Network Termination with only two devices (NT1).

The SBCX provides the required IOM-2 channel switching functions (B1, B2, D and C/I) for this application. To ensure a proper wake up procedure of a micro controlled NT being in power down (case of a deactivated line) the asynchronous timing bit (AST-bit of the loop-back register) should be set.

The U- and S/T-interface maintenance data is conveyed via the IOM-2 interface's monitor channel to the ICC.

Figure 13

Micro Controlled NT Configuration

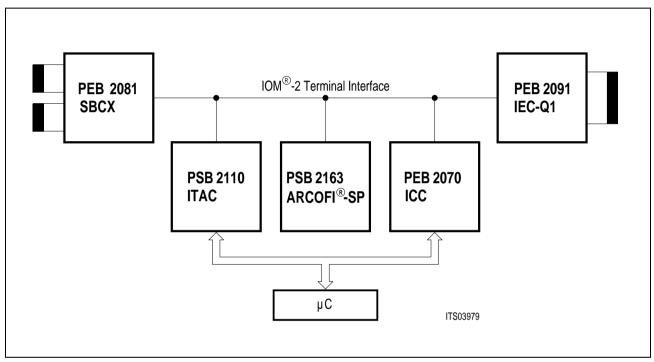

The S-interface is the standard ISDN subscriber interface, but in a PBX environment also an U-interface (e.g. IBC or IEC-Q) may be used for the connection of a subscriber resulting in an U-interface terminal with an S/T-extension (Intelligent NT). The Intelligent NT can be seen as an enhancement of the micro controlled NT.

In this case the SBCX is treated as an additional IOM-2 device. The ICC accesses the IBC or IEC-Q via MON0 channel, the other devices via MON1 channel.

The functionality of such a configuration includes D-channel collision resolution in upstream direction (TIC bus) and IOM-2 channel switching functions for internal communication.

Figure 14 Intelligent NT Providing both Terminal (voice/data) and Network Terminating Functions (S/T-interface)

Figure 15 SBCX in LT-S Mode for Intelligent NT Configurations

#### 2.1.5 Line Card Application (one D-channel controller per line)

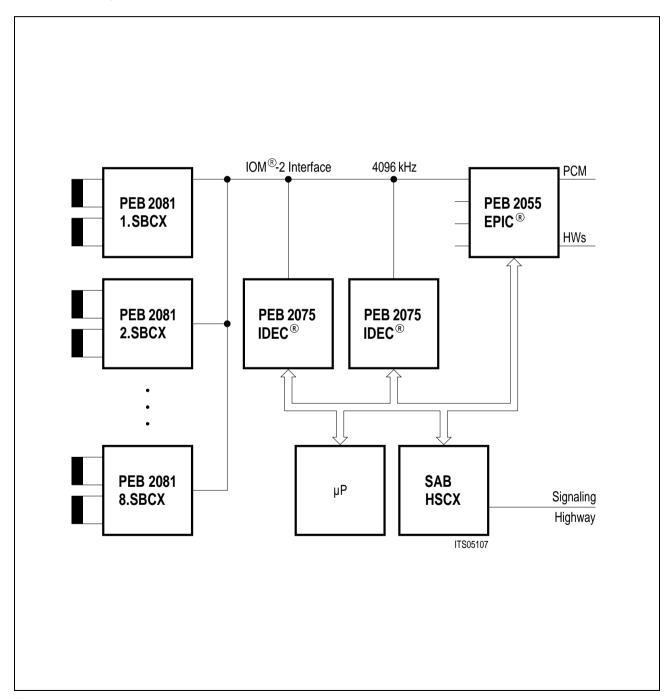

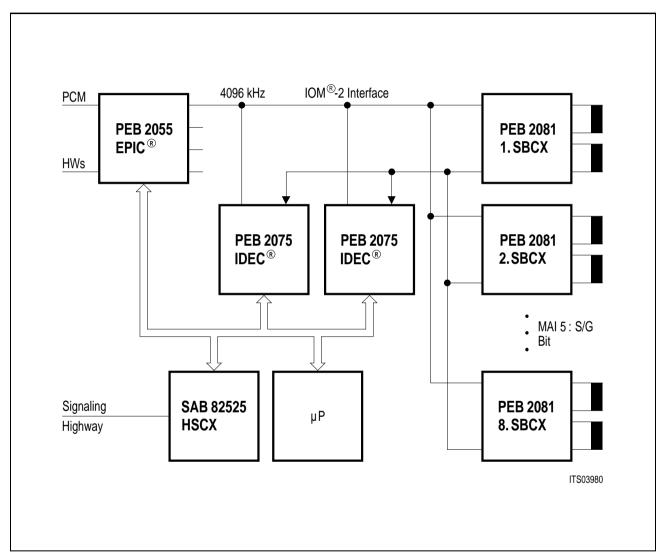

The SBCX supports a line card implementation both in an ISDN Subscriber Line Termination LT-S) and in an ISDN Trunk Line Termination (LT-T) using e.g. the PEB 2055 Extended PCM Interface Controller (EPIC®-1). Up to eight devices can be connected to the IOM-2 interface. This application requires a data clock of 4.096 MHz. The standard implementation of a S/T-interface line card includes one D-channel controller, e.g. PEB 2075 ISDN D-Channel Exchange Controller (IDEC®), per line for decentralized D-channel handling. **Figure 16** illustrates this configuration for line cards on the exchange side.

Figure 16 IOM®-2 Line Card Architecture (LT-S) with One D-Channel Controller per Line

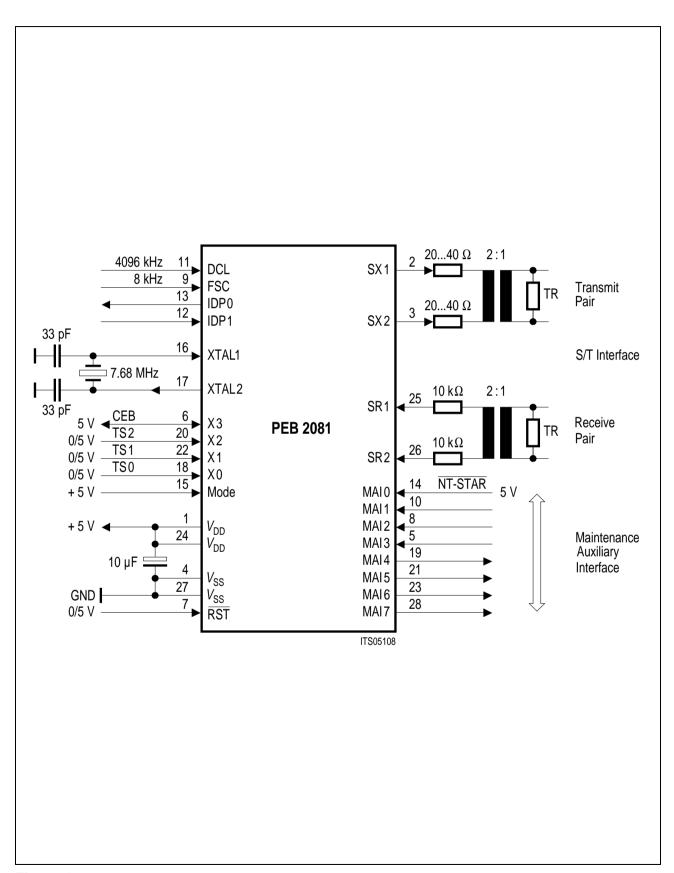

Figure 17 SBCX in LT-S Mode for Basic Line Card Configuration

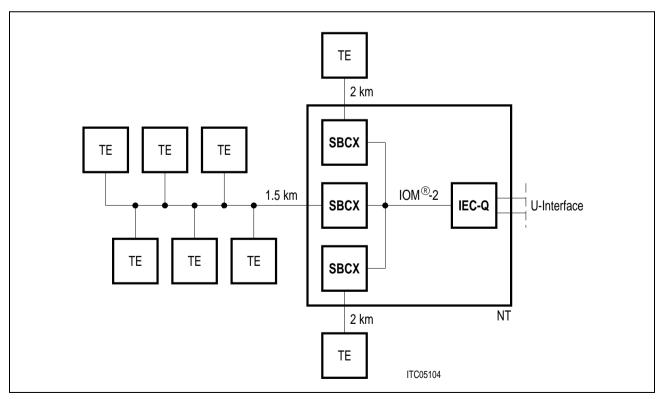

#### 2.1.6 Line Card Application (one D-channel controller for eight lines)

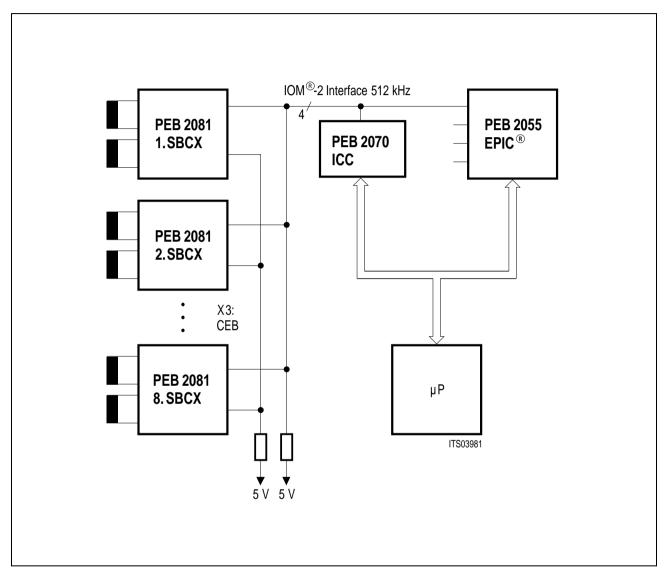

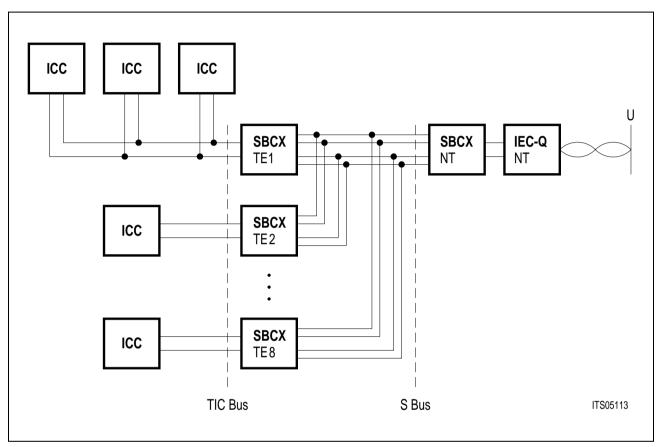

This configuration is used under the same circumstances as described in **section 2.1.3** "NT1 Star Configuration". Refer to this section for additional information.

Figure 18 and figure 19 illustrate the principle and its realization in line card applications.

Figure 18 IOM®-2 Line Card Architecture (LT-S only) with One D-Channel Controller per up to Eight Lines

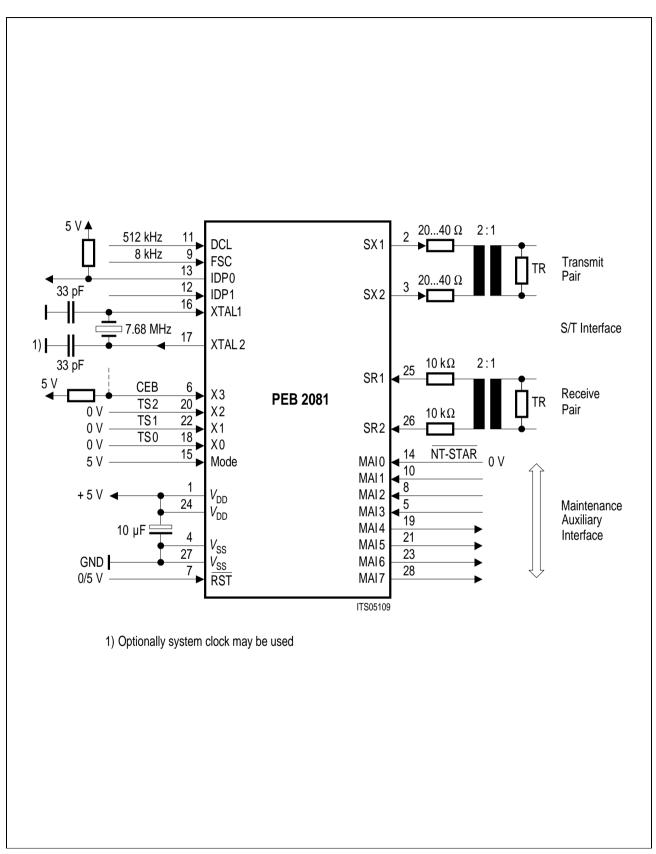

Figure 19 SBCX in LT-S Mode for Star Configuration

#### 2.1.7 Private-Branch-Exchange Application (one D-channel controller per line)

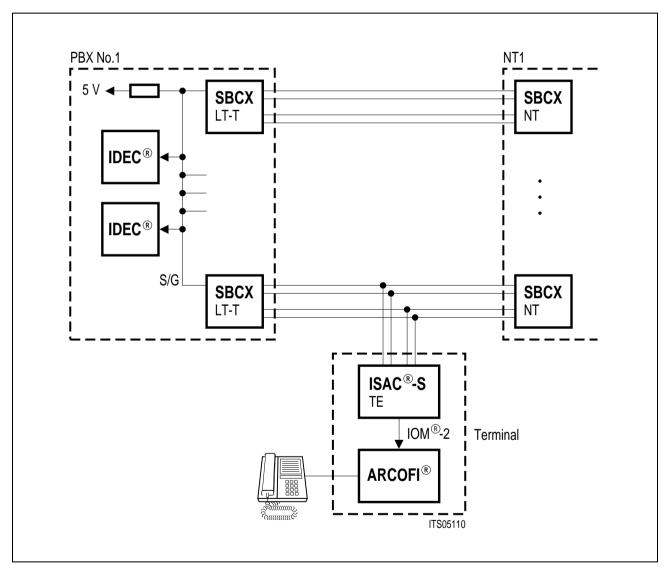

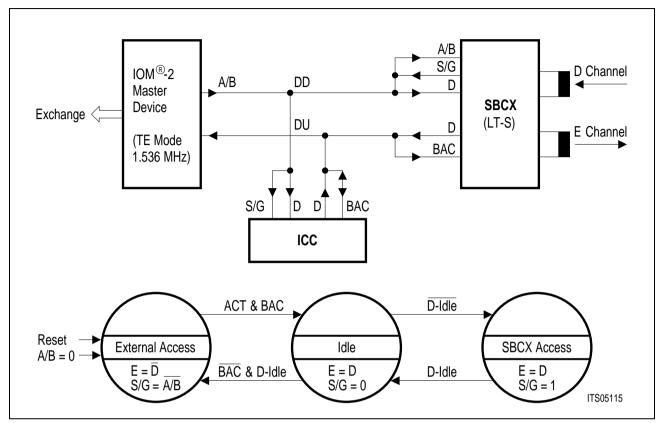

The SBCX also supports ISDN-PBX configurations in its LT-T (Line Termination-Trunk) mode. By providing internal buffers in this mode, the device is able to compensate phase deviations between the two clock systems on the S-interface and the IOM-2 interface (in PBX system the PEB 2081 is slave with respect to these two clock systems). Specific requirements regarding the clock generation in a PBX system are described in **section 2.3** "Clock Generation".

Figure 20 PBX Architecture (LT-T) with One D-Channel Controller per Line

D-channel processing is handled by a separate controller for each line as was the case for line card applications. In order to guarantee correct D-channel access on the S-interface when additional terminals are connected to the same S-bus, an external "D-channel access monitor bit" (≜ S/G bit) is provided in this mode. A system where this bit must be evaluated for correct D-channel access is shown in the following figure. In this configuration the D-channel controller of PBX No. 1 is informed via the S/G bit when the terminal occupies the D-channel on the S-interface. In case a point-to-point configuration is used to connect a single PBX to an exchange the S/G line is not required. Please refer to **section 3.2.3.1** for additional information regarding the use of the S/G bit.

Figure 21 PBX-Configuration Requiring S/G Bit Evaluation

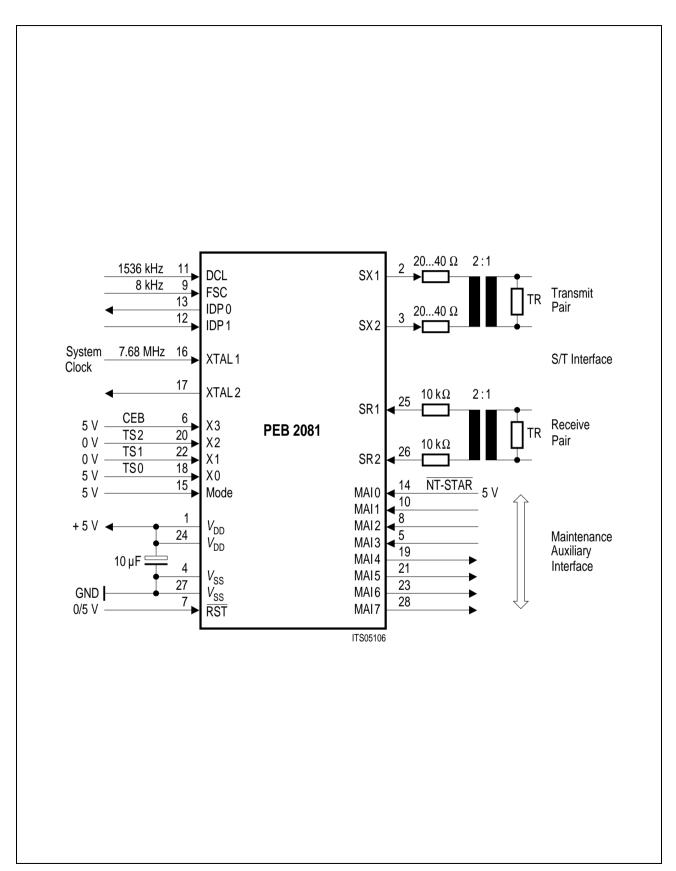

Figure 22 SBCX in LT-T Mode

TE

### **SIEMENS**

#### 2.2 Setting Operating Modes

LT-S

**Tables 1-2** illustrate which modes are supported by the PEP 2081 version 3.4 and how they can be configured by the user. **Table 1** gives an overview of pin signals and the register configuration. For the description of MAI pins it was assumed, that for the initial mode, the "I/O specific" mode was selected. Refer to **chapter 4.1.4** for details on the MAI interface options.

It is possible to change the mode of a device during operation by pin strapping (e.g. for test purposes) if the mode change is followed by a hardware reset. A hardware reset sets all registers to their initial value.

LT-T

NT

Table 1

Modes of Operation

Configuration

|      | Point-Point/Bus | Point-Point/Bus |                     |                       |

|------|-----------------|-----------------|---------------------|-----------------------|

| Pin  |                 |                 |                     |                       |

| Mode | 1               | 0               | 1                   | 0                     |

| X0   | i:TS0           | i:0/i:1 ¹)      | i:TS0               | o:32/16 kHz (1:1)     |

| X1   | i:TS1           | i:0             | i:TS1               | i:0                   |

| X2   | i:TS2           | i:1             | i:TS2               | i:0                   |

| Х3   | i/o:CEB         | i/o:CEB         | o:1536 kHz (3:2)    | o:768 kHz (1:1)       |

| MAIO | i:NT-STAR       | i:NT-STAR       | i:MPR0              | i:MPR0                |

| MAI1 | i:MPR1          | i:MFD           | i:CON <sup>2)</sup> | i:CON <sup>3)</sup>   |

| MAI2 | i:MPR2          | i:TM1           | i:MPR2              | i:MPR2                |

| MAI3 | i:MPR3          | i:TM2           | i:MPR3              | i:MPR3                |

| MAI4 | o:MPR4          | o:MPR4          | o:MPR4              | o:MPR4                |

| MAI5 | o:MPR5          | o:MPR5          | o:S/G               | o:S/G if<br>SGE = "1" |

| MAI6 | o:MPR6          | o:MPR6          | o:MPR6              | o:MPR6                |

| MAI7 | o:MPR7          | o:MPR7          | o:MPR7              | o:MPR7                |

| FSC  | i:8 kHz         | i:8 kHz         | i:8 kHz             | o:8 kHz (1:2)         |

| DCL  | i:512-8192 kHz  | i:512-8192 kHz  | i:512-8192 kHz      | o:1536 kHz (1:1)      |

#### (cont'd)

#### Note:

- 1) Choice for bus configuration (1 = bus). In LT-S mode only programmable. In NT mode programmable or pin strapping. Pin strapping has the higher priority.

- 2) CON-pin functionality is enabled if DH = "1" in the IOM-2 Channel register in LT-T mode.

- 3) CON-pin functionality is enabled if DH = "0" in the IOM-2 Channel register in TE mode.

# **SIEMENS**

Table 1

Modes of Operation (cont'd)

| Configuration                   | LT-S Point-Point/Bus | NT<br>Point-Point/Bus | LT-T              | TE    |

|---------------------------------|----------------------|-----------------------|-------------------|-------|

| Register                        |                      |                       |                   |       |

| Configuration Bit 0 (Mode) [0]  | 0                    | 0/17)                 | 1                 | 0/17) |

| Configuration Bit 1 (C/W/P) [0] | 0/11)                | 0/11)                 | 0/1 <sup>2)</sup> | 0/13) |

| Configuration Bit 5 (FSMM) [0]  | 0/1                  | 0/1                   | 0                 | 0     |

| Configuration Bit 6 (MAIM) [0]  | 0                    | 0                     | 0                 | 0     |

| SM/CI<br>Bit 0 (MIO) [0]        | 0                    | 0                     | 0                 | 0     |

| SM/CI<br>Bit 2 (SGE) [0]        | 0                    | 0                     | 0                 | 0/18) |

| IOM-2 Channel<br>Bit 2 (DH) [0] | 0/14)                | 0/14)                 | 0/15)             | 0/16) |

#### Notes:

- 1) Choice for bus configuration (1 = bus). In LT-S Mode only programmable. In NT mode programmable or pin strapping. Pin strapping has the higher priority.

- 2) Slip warning control. C/W/P = 0 will issue C/I "Slip" code warning after 50  $\mu$ s wander. C/W/P = 1 will issue the "Slip" code warning after 25  $\mu$ s.

- 3) PCK (pin X0) frequency select. C/W/P = 0 will issue a power converter clock frequency of 32 kHz, C/W/P = 1 will issue 16 kHz.

- 4) Select "1" for intelligent NT applications to ensure partial TIC Bus evaluation (see section 3.3.5.5).

- 5) Select "1" for point-to-multipoint configurations to ensure D-channel collision resolution according to ITU I.430 (see section 2.1.7 and 3.3.5.4).

- 6) For normal D-channel collision procedure program DH = "0".

- 7) 0: MAI pins I/O specific; 1: MAI pins only I/O.

- 8) In TE Mode pin MAI5 outputs a D-channel enable signal, which may be used by a general purpose HDLC controller for LAP D handling. The signal continuously monitors the D-E channel status and provides a stop/go information.

- [0] Initial register bit value after hard- or software reset.

# **SIEMENS**

Table 2 IOM®-2 Channel Assignment \*)

| IOM®-2<br>Channel No. | TS2 | TS1 | TS0 | Bit No. | Min. Freq. of DCL (kHz) |

|-----------------------|-----|-----|-----|---------|-------------------------|

| CH 0                  | 0   | 0   | 0   | 0 31    | 512                     |

| CH 1                  | 0   | 0   | 1   | 32 63   | 1024                    |

| CH 2                  | 0   | 1   | 0   | 64 95   | 1536                    |

| CH 3                  | 0   | 1   | 1   | 96 127  | 2048                    |

| CH 4                  | 1   | 0   | 0   | 128 159 | 2560                    |

| CH 5                  | 1   | 0   | 1   | 160 191 | 3072                    |

| CH 6                  | 1   | 1   | 0   | 192 223 | 3584                    |

| CH 7                  | 1   | 1   | 1   | 224 255 | 4096                    |

# Note:

<sup>\*)</sup> TS pins are read continuously (non-latching) after the supply voltage has reached its nominal value.

#### 2.3 Clock Generation

Clock generation varies with the application. The following diagrams show what timing signals need to be generated for each SBCX mode and how system synchronization is obtained.

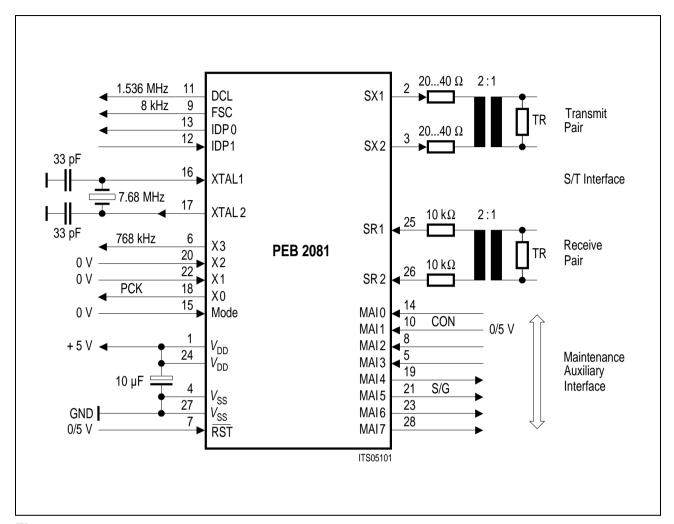

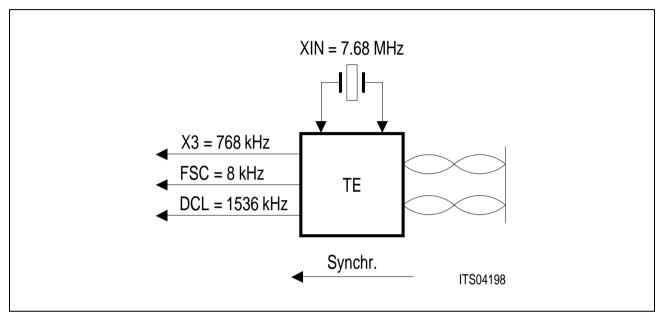

#### 2.3.1 **TE Mode**

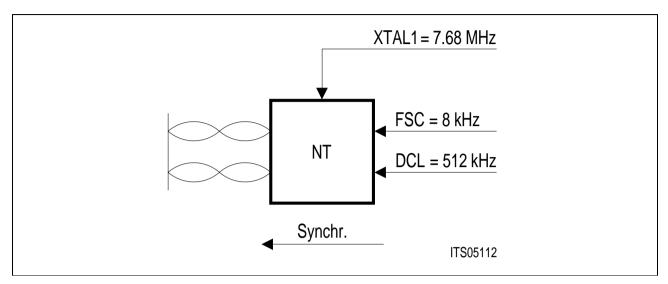

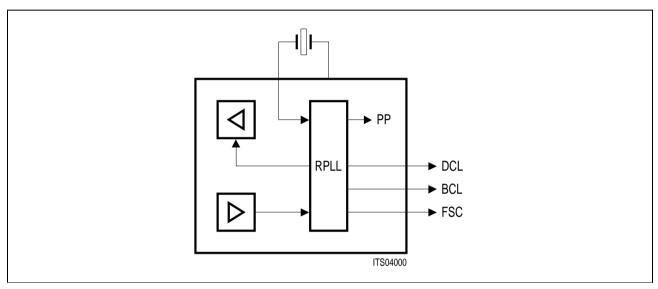

Figure 23 Clock Generation for TE Mode

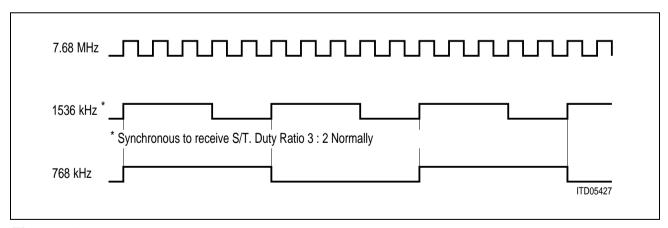

In TE mode the PEB 2081 recovers the timing directly from the S-interface. A free running crystal or other clock source provides a 7.68 MHz base clock. The device synchronizes in TE Mode with a Receive PLL (RPLL) onto the S-interface by including 65 ns correction steps. Thus the issued IOM clocks and the clock signal on pin X3 are synchronous to the PTT master clock.

#### 2.3.2 NT Mode

Figure 24 Clocks Generation in NT Mode

In NT Mode the SBCX is supplied with synchronous IOM clocks and a synchronous base clock signal. These signals typically are generated by the upstream U-interface device (PEB 2091 or PEB 2095).

In case no 7.68 MHz base clock signal is available, a 7.68 MHz crystal may be connected to XTAL1 and XTAL2. In this configuration the internal Transmit PLL (XPLL) synchronizes the freerunning crystal clock onto the FSC signal.

If required DCL clock rates up to 8192 kHz may be used. However the PEB 2081 will operate in IOM channel 0 independently of the DCL frequency applied.

# **SIEMENS**

# 2.3.3 LT-T Mode

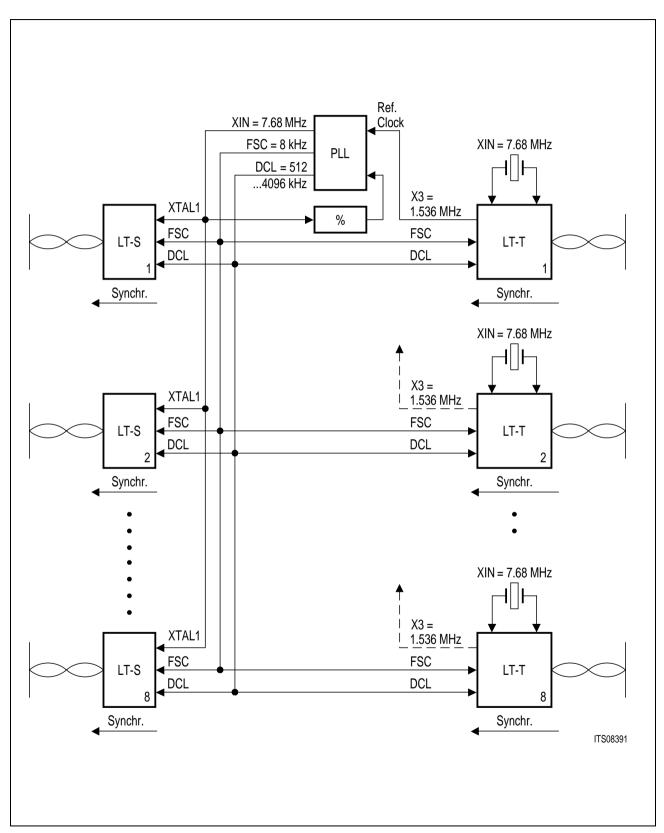

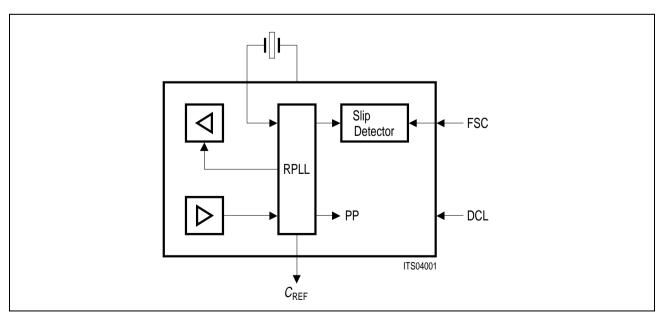

Figure 25 Clock Generation in LT-T Mode

# **SIEMENS**

In LT-T mode IOM-clock signals are not issued by the device but need to be generated externally. In order to ensure synchronous timing to the PTT-master clock, a PLL is used for generation of FSC and DCL (supplied to LT-T and LT-S devices) as well as of the 7.68-MHz system clock (LT-S only). Reference clock for the PLL is the PTT synchronous 1536-kHz signal from pin X3.

#### Note:

It may be necessary to use a multiplexer for the PLL reference clock because the X3 clock signal is synchronous to the PTT clock only if the corresponding line is activated. Otherwise the PLL reference must be supplied by the X3 clock from a different activated line.

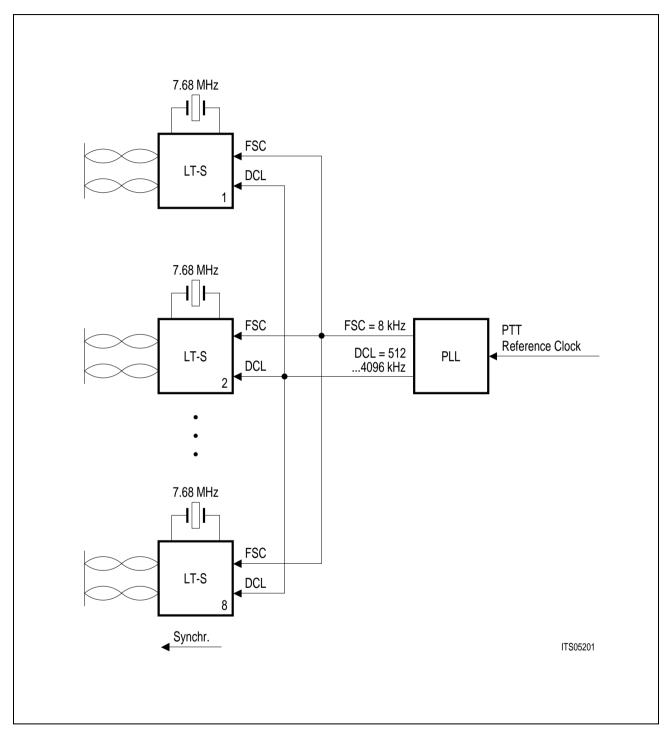

### 2.3.4 LT-S Mode

Figure 26 Clock Generation in LT-S Mode

In LT-S mode the device synchronizes with the internal Transmit PLL (XPLL) the freerunning crystal clock onto the FSC signal. This ensures that transmission on the S-interface will be synchronous to the PTT clock.

# 2.4 S/T-Interface Configurations

The receiver of the SBCX exceeds the electrical requirements of the S/T-interface. An overview of the different wiring configurations is given in the following figures.

The maximum length of a point-to-point configuration depends on the kind of cable installed. The maximum allowable line attenuation is 13 dB. However, the following figures give an idea of the performance of the SBCX.

Figure 27 S/T-Interface Point-to-Point Configuration ("TR" stands for the 100  $\Omega$  Terminating Resistor)

Figure 28 S/T-Interface Extended Passive Bus Configuration ("TR" stands for the 100  $\Omega$  Terminating Resistor)

Figure 29 S/T-Interface Short Passive Bus Configuration ("TR" stands for the 100  $\Omega$  Terminating Resistor)

# 3 Application Guide

### 3.1 SBCX Device Architecture and General Functions

The SBCX performs the layer-1 functions of the S/T-interface according to ITU recommendation I.430, ETS 300 012 and T1.605 Basic User Network Interface Specification, respectively. It can be used at all ends of the S/T-interface. The following figure depicts the device architecture.

Figure 30 SBCX Device Architecture

# The Common Functions for all Operating Modes are:

- line transceiver functions for the S/T-interface according to the electrical specifications of ITU I.430

- The pseudo-ternary pulse shaping which meets the I.430 pulse templates, is achieved with the integrated transmitter.

- The integrated receiver is designed to cope with all wiring configurations of the S/T-interface (point-to-point, passive bus, and extended passive bus). The maximum allowable line attenuation is 13 dB.

- conversion of the frame structure between the IOM-2 interface and S/T-interface

- conversion from/to binary to/from pseudo-ternary code

- access to S and Q bits

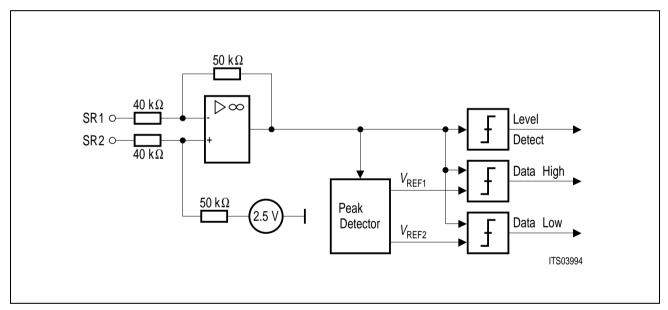

- The level detect block monitors the receive line and therefore initiates switching into power down or power up state.

# **Mode Specific Functions are:**

- receive timing recovery for point-to-point, passive bus and extended passive bus configuration

- S/T timing generation using IOM-2 timing synchronous to system, or vice versa

- D-channel access control and priority handling

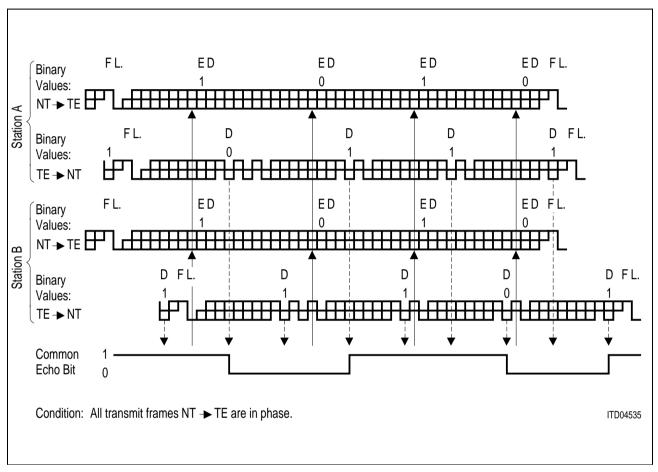

- D-channel echo bit generation by handling of the common echo bit

- activation/deactivation procedures, triggered by primitives received over the IOM-2 interface or by INFOs received from the line

- frame alignment in trunk application with maximum wander of  $\pm$  50 us

- execution of test loops

#### 3.2 Interfaces

Section 3.2 describes the interfaces supplied by the SBCX. Three interfaces are implemented:

- IOM-2 Interface

- S-Interface

- Maintenance Auxiliary Interface

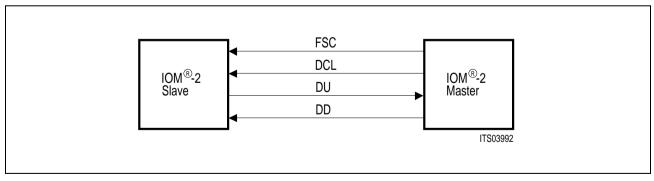

#### 3.2.1 IOM®-2 Interface

The IOM-2 interface is primarily used to interconnect telecommunication ICs. It provides a symmetrical full-duplex communication link, containing user data, control/programming and status channels. The SBCX communicates with other ISDN devices to realize OSI layer-1 functions (such as a U Transceiver) or upper layer functions (such as ICC, EPIC, ARCOFI and ITAC).

The structure used follows the 2B + 1D-channel structure of ISDN. The ISDN user data rate of 144 kbit/s (B1 + B2 + D) on the S/T-interface is transmitted transparently in both directions over the interface. The D-channel switching may also be subject to the D-channel access procedure and collision detection and therefore is not fully transparent.

The IOM-2 interface is a generalization and enhancement of the IOM®-1 interface.

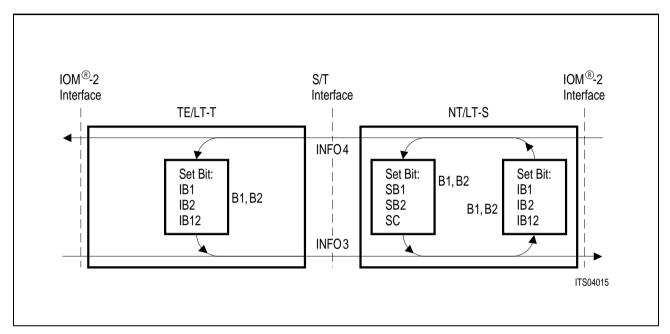

### 3.2.1.1 IOM®-2 Frame Structure/Timing Modes

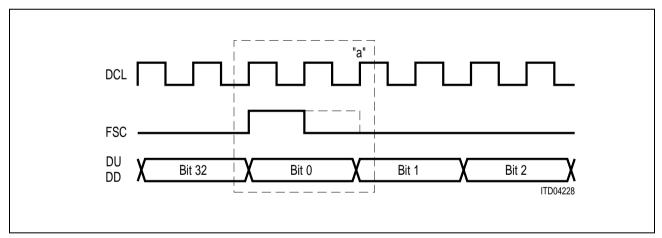

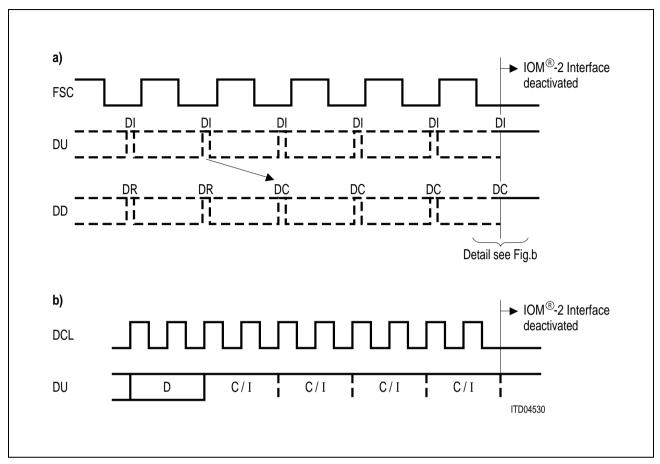

The IOM-2 interface comprises two clock lines for synchronization and two data lines.

Data is carried over Data Upstream (DU) and Data Downstream (DD) signals. The downstream and upstream direction are always defined with respect to the exchange. Downstream refers to information flow from the exchange to the subscriber and upstream vice versa respectively. The IOM-2 Interface Specification describes open drain data lines with external pull-up resistors. However, if operation is logically point-to-point, tristate operation is possible as well.

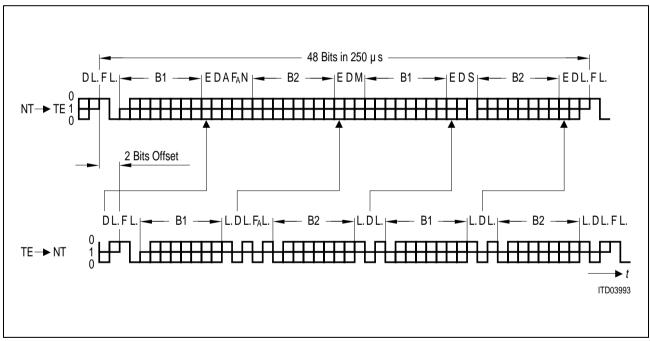

The data is clocked by a Data Clock (DCL) that operates at twice the data rate. Frames are delimited by an 8-kHz Frame Synchronization Clock (FSC).

Figure 31 IOM®-2 Interface Structure

Within one FSC period 32 bit to 512 bit are transmitted, corresponding to DCL frequencies from 512 kHz to 8.192 MHz. The SBCX needs no pin strapping to indicate the actual bit rate, because each rising edge of FSC resets the internal bit counter.

Two optimized IOM-2 timing modes exist for:

- Line card Applications

- Terminal Applications

Both the line card and terminal applications utilize the same basic frame and clocking structure, but differ in the number and usage of the individual channels.

| frame |  |

|-------|--|

| bits  |  |

| B1 | B2 | Monitor | D | Command/Indication | MR | MX |

|----|----|---------|---|--------------------|----|----|

| 8  | 8  | 8       | 2 | 4                  | 1  | 1  |

Figure 32

Basic Channel Structure of IOM®-2

Each frame consists of

- two 64 kbit/s channels B1 and B2

- the monitor channel for transferring maintenance information between the layer-1 functional blocks (SBCX, IEC-Q, etc.) and the layer-2 controller (ICC, EPIC)

- two bits for the 16 kbit/s D-channel

- four command/indication (C/I) bits for controlling of layer-1 functions (activation/deactivation and additional control functions) by the layer-2 controller (ICC, EPIC). For a list of the C/I codes and their use refer to **chapter 4**.

- two bits MR and MX for handling the monitor channel

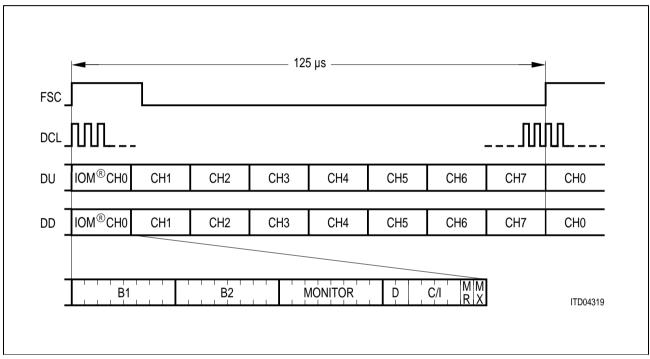

#### 3.2.1.1.1 IOM®-2 Interface Line Card Frame Structure

The SBCX in line card applications (LT-S and LT-T) supports bit rates from 256 kbit/s to 4096 kbit/s corresponding to DCL frequencies from 512 kHz to 8.192 MHz.

The typical IOM-2 line card applications comprises a DCL frequency of 4096 kHz with a nominal bit rate of 2048 kbit/s. Therefore eight channels are available, each consisting of the basic frame with a nominal data rate of 256 kbit/s. The length of the FSC high phase usually covers IOM-2 channel 0 (minimum FSC length is 2 DCL) unless synchronization of the S/T-interface multi-frame is desired.

The SBCX is assigned to an individual channel by pin strapping.

Figure 33

Multiplexed Frame Structure of the IOM®-2 Interface

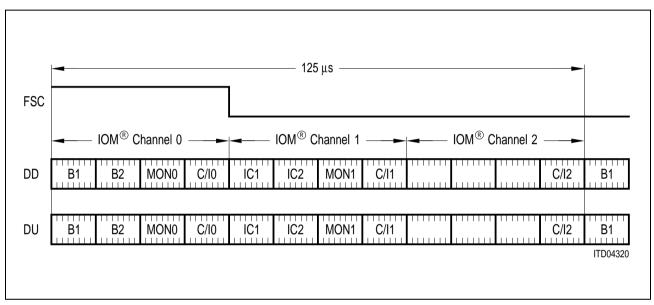

#### 3.2.1.1.2 IOM®-2 Interface Terminal Frame Structure

In TE mode the SBCX provides a data clock DCL with a frequency of 1536 kHz. As a consequence the IOM-2 interface provides three channels each with a nominal data rate of 256 kbit/s.

The SBXC only uses IOM-2 channel 0, and, for D-channel access control, the C/I field of IOM-2 channel 2. The downstream data (DD) are transferred on pin IDP0, the upstream data (DU) on pin IDP1.

The remaining two IOM-2 channels are for the use of other devices (ARCOFI, ITAC) within the TE.

Figure 34

Definition of the IOM®-2 Channels in a Terminal

#### - C/I0 in IOM® Channel 0:

**D:** two bits for the 16 kbit/s D-channel

**C/I:** The four command/indication (C/I) bits are used for controlling of the layer-1

functions (activation/deactivation and additional control functions) by the

layer-2 controller (ICC, EPIC).

MR, MX: two bits MR and MX for handling the monitor channel 0

#### - C/I1 in IOM® Channel 1:

C/I1 to C/I6 are used to convey real status information between a layer-2 device (ICC)

and various non layer-1 devices e.g. ARCOFI.

MR, MX: two bits MR and MX for handling the monitor channel 1

#### - C/I2 in IOM® Channel 2:

DU DD

| 1 | 1 | BAC | TBA2 | TBA1 | TBA0 | 1 | 1 |

|---|---|-----|------|------|------|---|---|

| Е | Е | S/G | A/B  | 1    | 1    | 1 | 1 |

E: D-echo bits

**BAC-bit** (Bus ACcessed), used by the layer-2 device (e.g. ICC). When the TIC bus is

occupied the BAC-bit is low.

**S/G-bit** (Stop/Go), available to the layer-2 devices (e.g. ICC) to determine if they can

access the S bus D-channel (S/G = 1: stop, S/G = 0: go).

**A/B-bit** (available/blocked), supplementary bit for D-channel control.

(A/B = 1: D-channel available, A/B = 0: D-channel blocked).

For more information also refer to the chapters TIC Bus Access and D-channel access control.

#### 3.2.1.2 IOM®-2 Interface Command / Indicate Channel

The Command/Indicate channel (C/I channel) is used to control the operational status of the SBCX and to issue corresponding indications. C/I channel codes serve as the main link between the SBCX and other external intelligence (layer-1 or layer-2 devices). In **chapter 4.3** status diagrams for all selectable modes give information on the commands with which the current operational status may be left, and on indications issued in all states.

The codes originating from the control devices are called "commands", those originating from the SBCX are referred to as "indications". Commands have to be applied continuously by the controller until the command is validated by the SBCX and the desired action has been initiated. Afterwards the command may be changed.

An indication is issued permanently by the SBCX until a new indication needs to be forwarded. Because a number of states issue identical indications it is not possible to identify each state individually.

The interpretation of C/I codes depends on the mode selected. **Table 3** shows the abbreviations used for C/I commands and indications.

The C/I channel can be disabled (Intelligent NT) by setting the CIH-bit in the IOM channel register. The C/I channel would then be accessible via the monitor channel (SM/CI register).

**In TE mode** a second C/I channel can be used to convey real status information between by a layer 2 device (ICC) and various non layer-1 devices e.g. ARCOFI. The channel consists of six bits in each direction.

For a list of the C/I codes and their use, refer to **chapter 4**.

# **SIEMENS**

Table 3

C/I Abbreviations

| Code | Description                            |

|------|----------------------------------------|

| Al   | Activation Indication                  |

| AI8  | Activation Indication with priority 8  |

| Al10 | Activation Indication with priority 10 |

| AIL  | Activation Indication Loop             |

| AR   | Activation Request                     |

| AR8  | Activation Request with priority 8     |

| AR10 | Activation Request with priority 10    |

| ARL  | Activation Request Loop                |

| CVR  | Code Violation Received (far end)      |

| DC   | Deactivation Confirmation              |

| DI   | Deactivation Indication                |

| DR   | Deactivation Request                   |

| MAIC | Maintenance Auxiliary Interface Change |

| PU   | Power Up                               |

| RES  | Reset                                  |

| RSY  | Resynchronizing                        |

| SLIP | Slip of Frame (frame jump)             |

| TIM  | Timing Request                         |

| TM1  | Test Mode 1 (2-kHz test signal)        |

| TM2  | Test Mode 2 (96-kHz test signal)       |

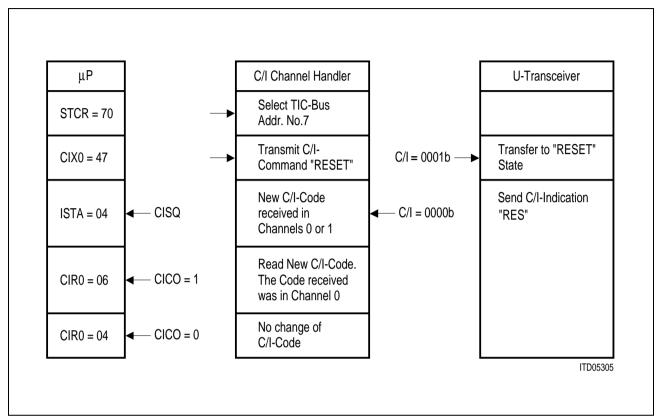

The following examples illustrate the use of the C/I channel in combination with the PEB 2070 and the PEB 2055. Both examples assume that the device has been correctly initialized prior to starting the C/I code transfer.

# PEB 2070 and C/I-Channel Programming

Figure 35 C/I-Channel Use with the ICC (all data values hexadecimal)

The STCR-register is programmed to allocate TIC-bus address 7 to the ICC. The C/I-command is transmitted with the CIX0-register (structure: 0 1 C/I C/I C/I C/I 1 1, bus access bit enabled). After the new C/I-command is loaded it is transmitted immediately.

A change in the C/I-channel is indicated by an ISTA-interrupt (CISQ-bit). The new C/I-message can be read from register CIR0 (structure: 0 0 C/I C/I CIC0 0 1). Bit CIC0 indicates that the new C/I-message was received in channel 0 for at least two consecutive frames. It is reset after the read operation.

ITD05304

#### μΡ EPIC®-1 SBCX in TE Mode C/I-Command MADR = C7"RESET" Select Port 0. Channel 0, C/I-Code MAAR = 08Downstream Transfer to "RESET" C/I = 0001 b — MACR = 48Start Transmission State <- New C/I-Code Send C/I-Indication C/I = 0001 bSFI = 1 ISTA = 40was Received "RES" Read Port and Time-CIFIFO = 88 Slot No. where C/I was Received Select this Port/ Time-Slot for Reading MAAR = 88(port 0, channel 0, C/I-code) Read C/I-Code MACR = C8Return C/I-Code in MADR = C7MADR-Register

# PEB 2055 and C/I-Channel Programming

Figure 36 C/I-Channel Use with the EPIC® (all data values hexadecimal)

After the correct initialization of the EPIC, the C/I-code which is to be transmitted to the SBCX is written into the MADR-register (structure 1 1 C/I C/I C/I C/I 1 1). With the MAAR-register the EPIC is informed where to send this C/I-code (transmission direction, port number and time-slot number). For a description of this register please refer to the EPIC-manual, the example above sends the C/I-command to port 0, IOM-2 channel 0. MACR =  $48_H$  starts the transmission of the command.

If a change in one of the C/I-channels was observed, and ISTA-interrupt (bit SFI) is generated. Because the user does not know in which channel the change occurred, the location needs to be read from the CIFIFO-register. This address is copied via software into address register MAAR. After having started the read operation with MACR =  $C8_H$  the C/I-message can be read from MADR (structure as described earlier).

#### 3.2.1.3 IOM®-2 Interface Monitor Channel

The monitor channel represents a second method to access SBCX specific features. Features of the monitor channel are supplementary to the C/I-channel. The SBCX uses the monitor channel for both, local programming and local functions (register access, e.g. MAI status) and S/Q maintenance bit information transfer. Monitor commands supported by the PEB 2081 divide into three categories. Each category derives its name from the first nibble (4 bits) of the one or two byte long message. All monitor messages representing similar functions are grouped together.

Monitor functions of the SBCX can only be accessed by a control device (ICC, EPIC) in IOM-2 mode. The following chapters describe the principle of monitor handshake in IOM-2, internal safeguards against a blocking of the monitor channel as well as features supported.

In case the IOM-2 Terminal structure is used, monitor channel 1 may be used by a codec device (e.g. ARCOFI).

#### 3.2.1.3.1 Handshake Procedure

IOM-2 provides a sophisticated handshake procedure for the transfer of monitor messages. For handshake control two bits are assigned to each IOM-frame (on IDP0 and IDP1).

The monitor transmit bit (MX) indicates when a new byte has been issued in the monitor channel (active low). The transmitter postpones the next information until the correct reception has been confirmed. A correct reception will be confirmed by setting the monitor read bit (MR) to low.

In order to send a monitor message from the control unit to the SBCX, the MX-bit on IDP1 and the MR-bit on IDP0 are used. In the opposite direction the SBCX handles the MX-bit of the IDP0-pin and watches the MR-bit of the IDP1-signal.

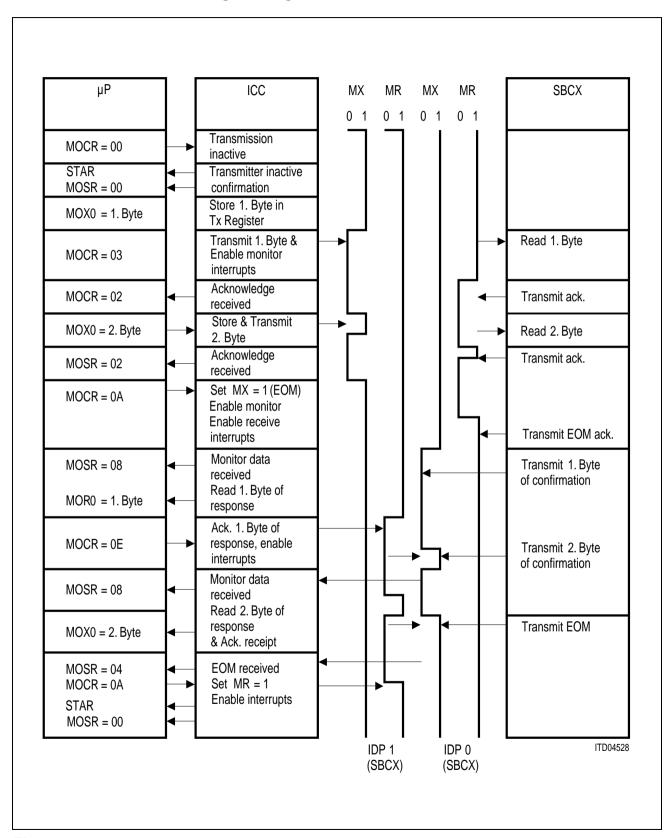

**Figure 37** illustrates monitor channel handling with the PEB 2070 (ICC), **figure 38** demonstrates it with the PEB 2055 (EPIC-1). A two-byte message is sent from the control unit to the SBCX who acknowledges the receipt by returning a two-byte long message in the monitor channel.

# **ICC and Monitor Channel Programming**

Figure 37

Monitor Channel Handling with ICC (all data values hexadecimal)

The  $\mu P$  starts the transfer procedure after having confirmed the monitor channel being inactive. The first byte of monitor data is loaded into the transmit register. Via the Monitor Control Register MOCR-monitor interrupts are enabled and control of the MX-bit is handed over to the ICC. Then transmission of the first byte begins. The SBCX reacts to a low level of the MX-bit on IDP1 by reading and acknowledging the monitor channel byte automatically. On detection of the confirmation, the ICC issues a monitor interrupt to inform the  $\mu P$  that the next byte may be sent. Loading the second byte into the transmit register results in an immediate transmission (timing is controlled by ICC). The SBCX receives the second byte in the same manner as before. When transmission is completed, the ICC sends "End of Message" (MX-bit high).

It is assumed that a monitor command was sent that needs to be confirmed by the SBCX (e.g. EOC commands). Therefore the PEB 2081 commences to issue a two-byte confirmation after an End-of-Message indication from the ICC has been detected. The handshake protocol is identical to that of the ICC. The ICC notifies the  $\mu P$  via interrupt when new monitor data has been received. The processor may then read and acknowledge the byte at a convenient instant. When confirmation has been completed, the SBCX sends "EOM". This generates a corresponding interrupt in the ICC. By setting the MR-bit to high, the monitor channel is inactive, the transmission is finished.

#### PEB 2055 and Monitor Channel Programming:

The EPIC-1 supports monitor transfers on a higher level than the ICC. Several modes are offered to support different types of monitor transfer. For communication with the SBCX, three are of special interest.

- Transmit Only. This mode is required when the EPIC sends monitor messages but no confirmation is returned by the SBCX (e.g. MON8 "Configuration Register").

- Transmit and Receive. The EPIC transmits first and receives afterwards. Confirmations sent by the SBCX can be read (e.g. MON8 "Identification Register").

- Searching for Active Monitor Channels. Listens to the IOM-monitor channel and reads information issued by the SBCX autonomously (e.g. MON1 S/Q-messages). Nothing is transmitted by the EPIC.

Unlike the ICC which had to respond to each change of the MR- and MX-bits individually (interrupt driven), the EPIC uses a FIFO for transmission and reception. The user therefore does not have to provide routines for the handshake protocol.

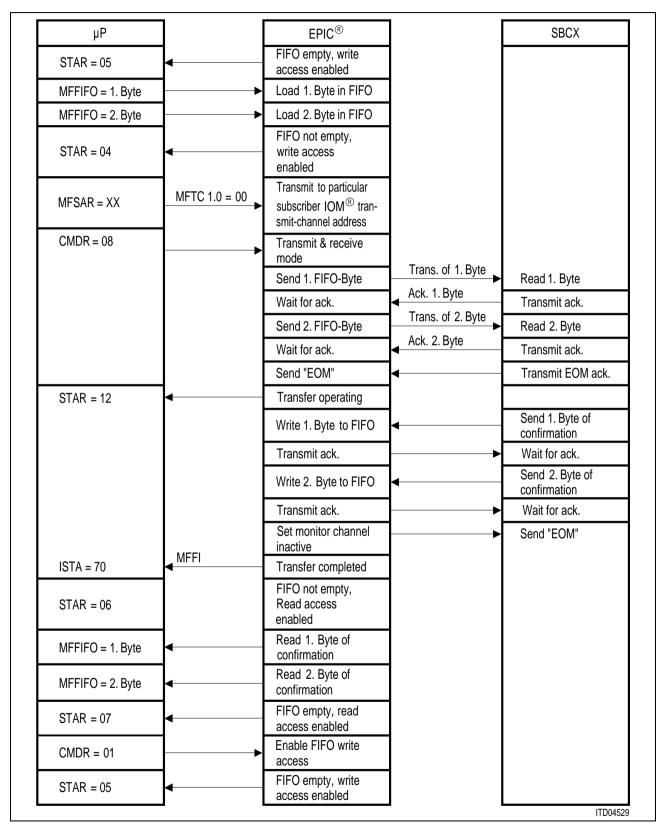

The example of **figure 37** demonstrates the use of EPIC-1 in the transmit-and-receive mode. As for the ICC it is assumed that the transferred monitor message will be followed by a two byte confirmation issued by the SBCX.

Before programming the FIFO, it is verified that the FIFO is empty and write access is possible. All monitor data is loaded into the FIFO (two bytes), the transmission channel and mode are selected. Writing "CMDR = 08" starts transmission of the FIFO contents and enables monitor data reception. After both bytes have been transmitted, the confirmation from the SBCX is read into the FIFO. After completion of the transfer an interrupt is generated. If the operation was successful, "STAR = 26" will indicate that data is loaded and the read access is enabled (in addition it is indicated that the PCM-synchronization status is correct). Following the readout of the confirmation bytes, the FIFO is cleared and the write access is selected again with the CMDR-register ("CMDR = 01").

The handshake timing for byte transfer is identical to that described for the ICC. Both devices (EPIC and SBCX) handle it automatically.

## **EPIC®** and Monitor Channel Programming

Figure 38

Monitor Channel Handling with EPIC® (all data values hexadecimal)

# 3.2.1.3.2 Monitor Procedure "Timeout" (TOD)

The SBCX offers an internal reset (monitor procedure "Timeout") for the monitor routine. This reset function transfers the monitor channel into the idle state (MR and MX set to high) by issuing "EOM" (End of Message). Thereby possible lock-up situations will be resolved. It therefore is recommended to enable the internal timeout feature in all systems when no  $\mu P$  is capable of detecting and resolving hang-up situations in the monitor procedure (e.g. in a standard NT1).

The device checks for lock-up situation every 5 ms. In case a hang-up has been detected "EOM" will be issued on IDP0. Afterwards the original monitor message will be sent in the monitor channel again. The information thus is not lost after a monitor procedure timeout occurred.

In applications where a  $\mu P$  controls the system this internal reset function may be disabled by programming the TOD bit (timeout disable) in the SM/CI Register to ONE. In this mode no restrictions regarding the time for completing a monitor transfer exists.

#### 3.2.1.3.3 MON-1, MON-2 Commands (S/Q Channel Access)

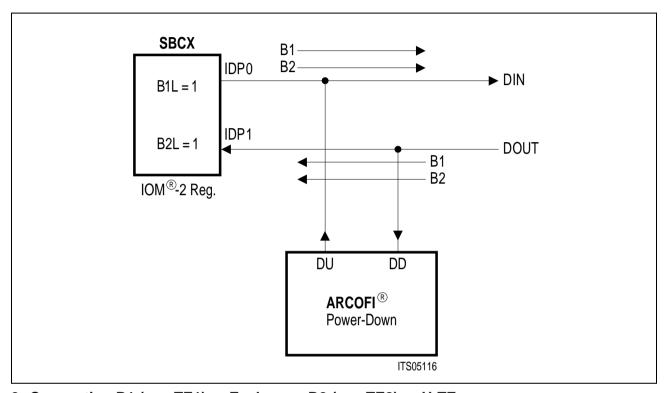

Monitor commands supported by the PEB 2081 divide into three categories. Each category derives its name from the first nibble (4 bits). The first two categories (MON-1 and MON-2) serve a similar function. They are therefore grouped together and will be described in more detail in this section. MON-8 commands are described in the next section.