VSC3139 Data Sheet

#### 3.6Gb/s 72 x 72 Asynchronous Crosspoint Switch

# **FEATURES**

- 72 input by 72 output crosspoint switch

- 3.6Gb/s Non-Return-to-Zero (NRZ) data bandwidth

- Global and per-channel programmable Input Signal Equalization (ISE) and output drive levels

- On-board Pseudo-Random Bit Sequence (PRBS) Generator/Detector

- 2.5/3.3V Complimentary Metal-Oxide Semiconductor/Transistor-Transistor Logic (CMOS/TTL) control Input/Output (I/O)

- Parallel and serial programming modes

- Differential Current Mode Logic (CML) data output driver

- Soft power-down for unused channels

- Secondary access port for configuation and monitoring

- Boundary scan support for data I/O

- 125MHz multimode program port

- Multicast and "striping" programming modes

- On-chip input and output terminations

- Single 2.5V supply, 3.3V option for control port

- 9W/13W typical power in Nominal and High Drive mode

- Integrated temperature sensor/alarm

- High performance, ball-grid array (BGA) package

# **APPLICATIONS**

- Large, 3-stage (Clos) fabrics of up to 2880 x 2880 I/O ports with up to 10 terabytes per second (Tb/s) data throughput

- Dense Wavelength, Division Multiplexing (DWDM) switches

- Wavelength routers

- Storage Area Network (SAN) switch fabrics

- Packet-switching fabrics

# **GENERAL DESCRIPTION**

The VSC3139 is a 72 x 72, asynchronous, crosspoint switch. It is designed to carry broadband data streams in a variety of applications. Its fully non-blocking switch core is programmed using a multi-mode port interface that allows random access programming of each I/O port. A high degree of signal integrity is maintained throughout the device by virtue of its fully differential signal paths.

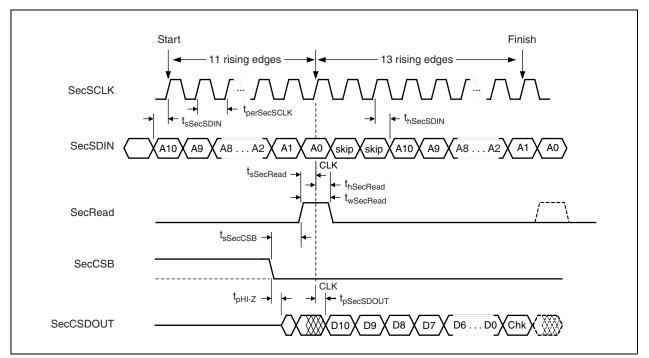

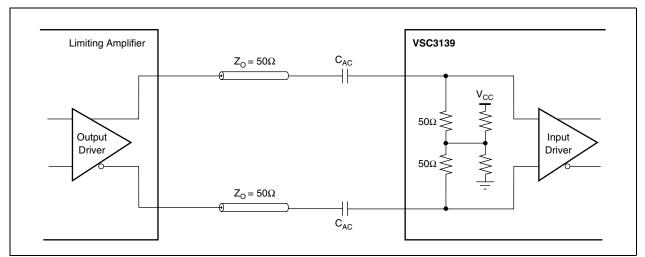

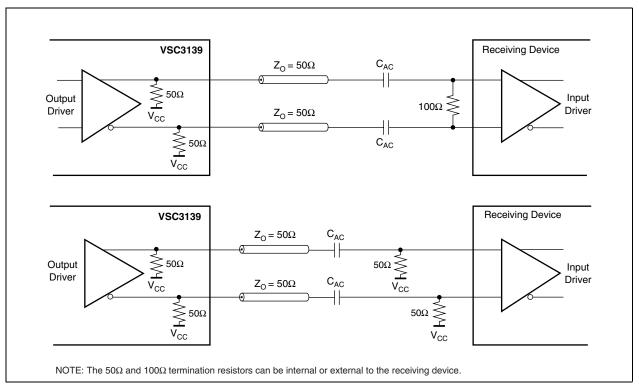

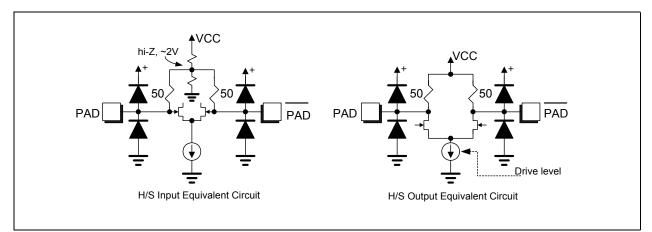

Each data output can be programmed to connect to any one of the 72 inputs. The signal path is unregistered and fully asynchronous, so there are no restrictions on the phase, frequency, of signal pattern on any input. Each high-speed output is a fully differential, switched current driver with on-die terminations for maximum signal integrity. Data inputs are terminated on die using  $100\Omega$  resistors between true and complement inputs with a common connection to an internal bias source that facilitates AC coupling to the switch inputs.

The VSC3139 provides a multi-mode, programming interface that allows commands to be sent as either serial data or multiplexed parallel data. Core programming can be sequential on a port-by-port basis, or multiple program assignments can be queued and issued simultaneously using the CONFIG bit. By default, the device's INIT feature resets the entire switch to a "straight-through" configuration (A0 to Y0, A1 to Y1, and so on); alternatively, the user can configure INIT to initialize to any other configuration.

The VSC3139 is programmed using an 11-bit, multiplexed address/data (ADDR/DATA) bus in conjunction with the device's ALE,  $\overline{RD}$ ,  $\overline{WR}$ , CONFIG, and  $\overline{INIT}$  pins. CONFIG and  $\overline{INIT}$  signals can also be set via an internal control register to reduce the number of signals required to interface with the switch.

Disabling  $\overline{\text{INIT}}$  and CONFIG in software locks in programming of switch connections. This is accomplished by setting the appropriate bits in the Setup register to zero, blocking input on these controls and preventing them from changing the switch configuration.

Unused channels can be powered down to allow efficient use of the switch in applications that require only a subset of the channels. Power-down is enabled in software by programming individual unused outputs with a power-down code.

A Secondary Access Port allows asynchronous readback and configuration control to take place even while the primary programming port is in use.

#### DRIVE SENSE Switch Core Input signal equalization (ISE) and scan registers Output level control and scan registers A[71:0] Y[71:0] Switch Configuration Register Secondary User INIT Register Access Port Staging Register $Sec\_\overline{CS}$ Sec\_SDIN Sec\_Write Sec\_Read Programming Interface Sec\_SCLK RESET -Sec\_SDOUT ADDR/DATA CONFIG Temperature OverTemp INIT Alarm PARALLEL/SERIAL $\overline{cs}$ PRBS\_Out $\overline{\mathsf{WR}}$ PRBS\_ErrDet PRBS Generator/Detector $\overline{\mathsf{RD}}$ PRBS\_In ALE PRBS\_Clk

### VSC3139 Functional Block Diagram

# **FUNCTIONAL DESCRIPTION**

## **DRIVE Input**

The VSC3139 provides a DRIVE input that can be connected internally to any of the 72 data input connections. By connecting an external signal to the DRIVE input and then switching it to one of the data inputs, a test signal can be placed on that input.

The DRIVE input can be used to verify signal path integrity. Because of this, input to the switch is not multiplexed between the DRIVE input and data input; multiplexing the input would alter the configuration after an integrity test. Instead, the signal from the DRIVE input is superimposed onto the data input path. For correct operation, the signal present on the selected input must either be in a neutral state or in a high-impedance state to allow the DRIVE inputs to influence the input.

The DRIVE input can also be used in conjunction with the SENSE output and an external test generator/receiver to verify programmed signal path integrity.

The DRIVE input can be programmed to drive any or all of the 72 data inputs. Writing to the appropriate address either connects or disconnects a data input from the specified DRIVE input.

## **SENSE Output**

The VSC3139 has a SENSE output that can be used to monitor any one of the 72 data outputs. This SENSE output monitors the data output signal at the package pin, thereby facilitating true verification of the complete signal path through the switch.

The SENSE output can also be used in conjunction with the external monitoring circuit and the DRIVE input to determine the presence of a signal on any output, or to verify signal path integrity.

# **Boundary Scan Support**

The VSC3139 incorporates registers that can be used to drive and sense the state of every pin of the high-speed data paths. These registers can be accessed through the programming port in serial mode, allowing the chip to be fully tested using only five active pins.

# **Power-On RESET**

The VSC3139 has a built-in power-on RESET function to ensure the matrix is fully disconnected and powered off prior to its being powered up. When the device is powered up, the switch draws additional power as each output is programmed. The power-on RESET circuit trip point is between 1.9VDC and 2.1VDC. Care must be taken to keep power supply excursions above 2.2VDC by providing adequate supply decoupling.

## **Temperature Sensor/Alarm**

The VSC3139 has circuitry that detects and flags temperatures exceeding a user-set range. The temperature range is set using "Register 5: Temperature Sensor". The device's temperature alarm is asserted when the die temperature meets or exceeds the maximum temperature in the user-set range. There are 15 temperature range presets between 30°C and 160°C. Each range is approximately 8°C,  $\pm$  8°C.

## **PRBS Generator/Detector**

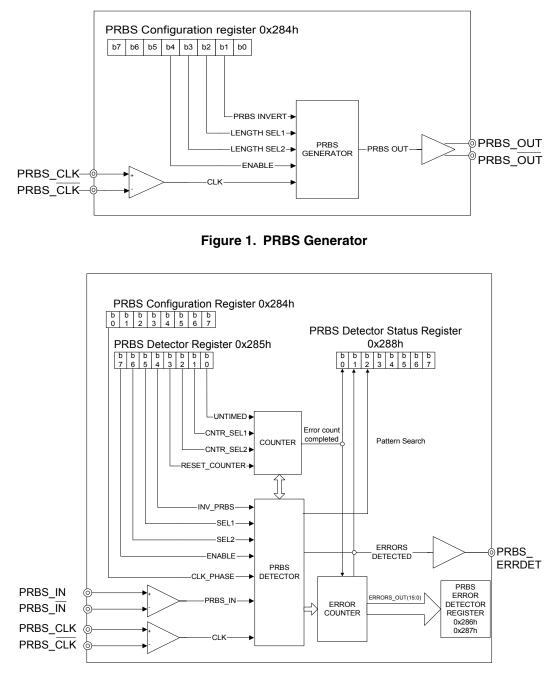

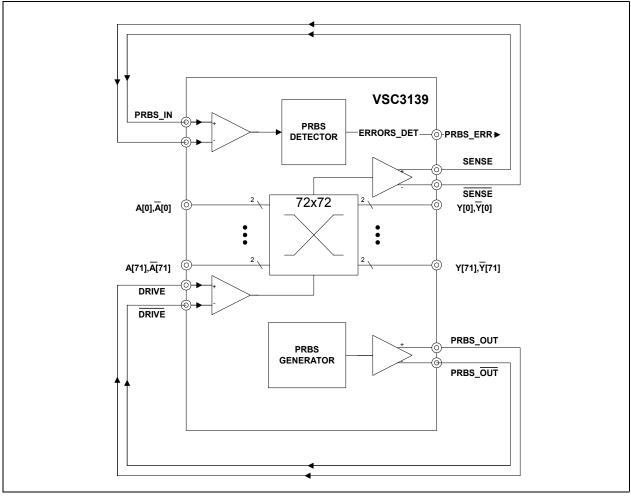

The PRBS Generator/Detector is capable of generating and detecting any of the four NRZ patterns described in the "Register 8 (page 21)" and "Register 10 (page 22)" data tables that appear later in this document. The main purpose of the PRBS Generator/Detector is in switch diagnostics and signal tracing. For more information, see the block diagram of the PRBS Generator/Detector in Figures 1 and 2.

Figure 2. PRBS Error Detector

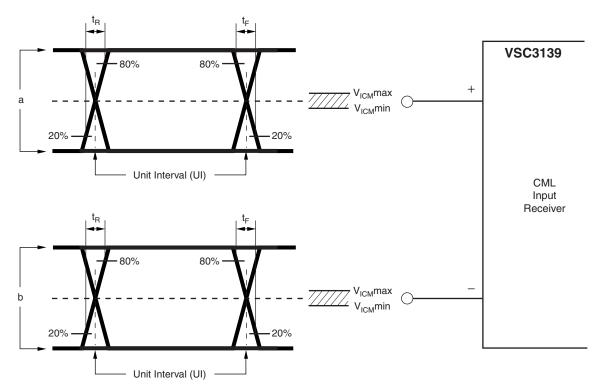

Figure 3 illustrates how the PRBS function can be connected to the switch core for signal path tracing to and from the switch.

Refer to Figure 3 and use the following set of steps to effect a trace.

- 1. Connect PRBS\_OUT and PRBS\_ $\overline{OUT}$  to DRIVE and  $\overline{DRIVE}$ , respectively.

- **2.** Connect SENSE and  $\overline{\text{SENSE}}$  to PRBS\_IN and PRBS\_ $\overline{\text{IN}}$ , respectively.

- **3.** Select channel to send pattern through.

- **4.** Generate pattern with PRBS generator.

- **5.** Check Detector for errors.

Figure 3. PRBS Connection Example

# **PROGRAMMING INTERFACE**

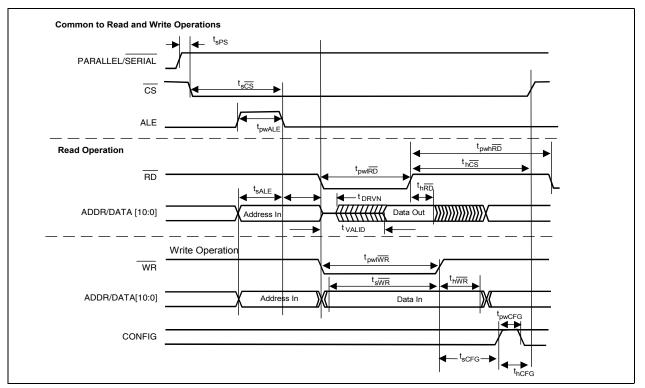

The VSC3139 programming interface uses a multiplexed address/data bus. The ALE signal differentiates whether the binary word on the multiplexed bus is address or data information. Table 1 lists the conventions used in this document to describe the various terms used in the programming interface.

| Convention  | Description                                       |

|-------------|---------------------------------------------------|

| SIGNAL NAME | Active HIGH signal                                |

| SIGNAL NAME | Active LOW signal                                 |

| ADDR        | Identifies OUTPUT channel to be programmed        |

| DATA        | Identifies INPUT channel to be programmed         |

| 1           | A logic level high signal. Also denoted by 'HIGH' |

| 0           | A logic level low signal. Also denoted by 'LOW'   |

Table 1. VSC3139 Data Sheet Programming Interface Conventions

## **Register Use**

All registers are accessed in the manner described in the programming interface description for parallel and serial read and write functions. Each register has a corresponding address which, when written to with a data word, alters the functions defined for that register (see "Registers" on page 13). Table 4 on page 11 provides an overview of all of the device registers, including detailed descriptions of the functions controlled in each register.

Note that all bits in all registers initialize to 0.

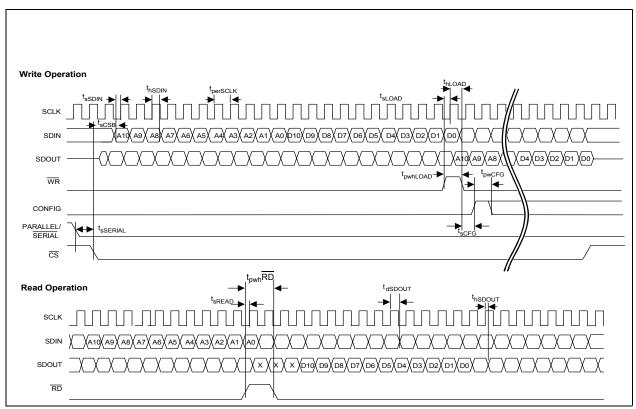

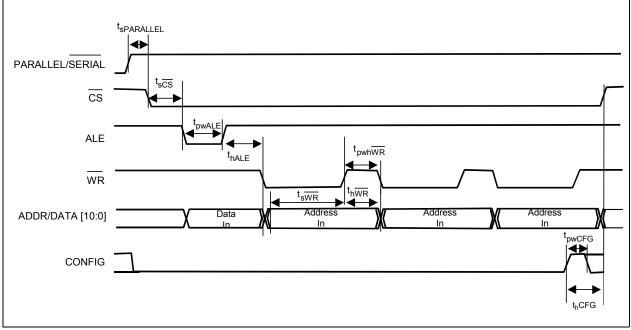

#### Parallel Mode—Write Operation

Parallel mode is enabled when PARALLEL/SERIAL = 1. When ALE = 1, the information on the ADDR/DATA bus is used as the address and it specifies the OUTPUT port that is being programmed in the write cycle. The falling edge of the ALE pin latches the address value. When ALE = 0, the information on the ADDR/DATA bus designates the INPUT port that is to be connected to the previously selected OUTPUT port. The connection between the specified input and output is programmed into memory when  $\overline{WR} = 1$ .

When CONFIG = 1, all new programming data is transferred directly to the switch core and any new connections are configured as they are entered. When CONFIG = 0, newly programmed connections are held in staging registers. Asserting CONFIG = 1 transfers the data from the staging registers to the switch core independent of other control signals so that any changes occur concurrently. CONFIG may be tied HIGH so that all programming changes take effect sequentially as they are written. Alternatively, it may be toggled HIGH and LOW to store multiple programming steps and activate them simultaneously.

Figure 5 on page 29 shows the programming sequence for parallel mode write operations.

#### Parallel Mode—Read Operation

The VSC3139 supports parallel readback using the multiplexed bus to read programming information from the switch fabric. The falling edge of ALE latches the address (OUTPUT) value of the connection to be read. The chip then drives the requested data out onto the bus after the falling edge of  $\overline{\text{RD}}$ , where it remains valid until  $\overline{\text{RD}} = 1$ .

Figure 5 on page 29 shows the programming sequence for parallel mode read operations.

#### Serial Mode—Write Operation

Serial mode operation is enabled when PARALLEL/ $\overline{\text{SERIAL}} = 0$ . In this mode, the ADDR/DATA[0] pin becomes the serial data input (SDIN) pin and the ADDR/DATA[1] pin becomes the serial clock (SCLK) pin which is rising-edge-triggered.

In addition, in serial mode the sense of the  $\overline{WR}$  pin is inverted from parallel operation. That is, the pin should normally be set LOW, and set HIGH to write the address and data information to the programming port. A serial word of the form [Output][Input] is shifted into the internal shift register (MSB-first), and the  $\overline{WR}$  pin is set HIGH, coincident with the last bit of the data word to indicate the last bit of a connection. This transfers the input identifier to the staging register of the addressed output. CONFIG is then asserted (1, asynchronously) to transfer one or more program commands to the switch core. The programming information that is shifted in during the write cycle is repeated back to the SDOUT (ADDR/DATA[2]) pin, but delayed by 22 clock cycles. This allows for easy confirmation of the previous programming step. The output field is 11 bits long, representing the binary numerical identifier of the output to be programmed. The input field is also 11 bits long, representing the numerical identifier of the input that will be connected to the specified output.

Figure 7 on page 30 shows the programming sequence for serial mode write operations. During normal Serial port operations, the ALE pin must be held LOW. Setting ALE HIGH is used in Serial Multicast programming mode.

#### Serial Mode—Read Operation

During serial mode read back, the sense of the  $\overline{\text{RD}}$  pin is inverted from its operation during parallel mode. To read back information about a specific output connection, the address corresponding to the output of interest is shifted in while  $\overline{\text{RD}}$  is held LOW.  $\overline{\text{RD}}$  is set HIGH with the last bit of the output address and is held HIGH for three clock cycles thereafter. The data begins to be shifted out on the SDOUT pin beginning four SCLK cycles after  $\overline{\text{RD}}$  was initially set HIGH and for the following 11 clock cycles.

Figure 6 on page 30 shows the programming sequence for serial mode read operations.

#### INIT

Asserting the  $\overline{\text{INIT}}$  pin or the  $\overline{\text{INIT}}$  bit in the Control register activates a preset connection matrix. The  $\overline{\text{INIT}}$  feature connects the inputs to the outputs in a "straight-through" fashion. Each input is connected to the output of the same value. For example, A0 -> Y0, A1 -> Y1 ... A71 -> Y71. Asserting  $\overline{\text{INIT}}$  will program all connections without exception.

To prevent accidental activation of this feature, disable the  $\overline{INIT}$  function in the Setup register.

Note that using the INIT feature to program the VSC3139 into a "straight-through" configuration may cause excessive power supply droop due to the large transient currents when the switch is re-configured in this manner. Adequate power supply filtering/decoupling must be implemented close to the VSC3139 to prevent activation of the power-on RESET circuitry. Power supply transients/droop must be kept above 2.2VDC.

#### Software Power-Down

With this feature, unused outputs may be disabled using software controls. This is accomplished by programming each unused output with a power-down code. Programming a valid input address will reactivate the channel.

It is recommended that any changes in power programming be executed only as part of an initialization sequence. This will guard against the effects of any switching transients that might result from changing the power supply current suddenly.

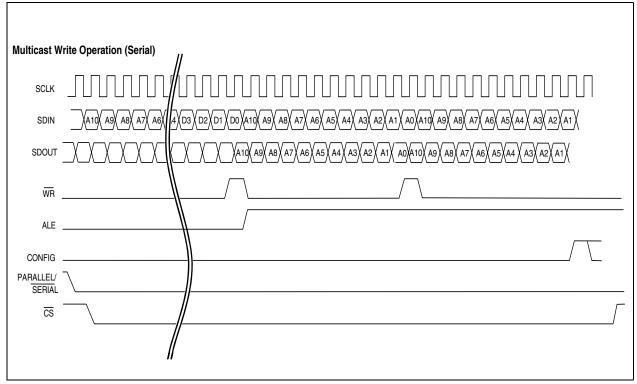

#### **Multicasting Mode**

Multicast mode provides programming efficiency when a single input is to be connected to multiple outputs. By modifying the use of the ALE bit, it is possible to latch the DATA[10:0] value, and use it to represent the input value in subsequent programming steps.

To use multicast mode, ALE is held LOW while the input to be multicasted is written to the data word space of the Switch Array Connection register (or the multicast input storage register). ALE is then raised and held HIGH for programming steps to follow. Connections to the saved input value are programmed solely with the rising edge of the  $\overline{WR}$  control signal.

Figure 7 on page 30 shows the programming sequence in parallel mode.

Normal programming is resumed by following the standard programming sequence. The input value is retained as long as ALE remains HIGH but will change once ALE is brought LOW. The input value will also be cleared when information is read from the control interface regardless of the value of ALE.

Multicast is also available in serial programming mode. ALE is held LOW during normal operation of the serial port. To initiate Multicast during serial programming, the first connection is made in the regular manner by first shifting in the 11-bit address and then the 11-bit DATA. The  $\overline{WR}$  signal is raised HIGH to clock in the last bit and then negated at the next falling edge of SCLK. As the  $\overline{WR}$  signal is negated, the ALE control is raised, prior to the next rising edge of SCLK. As long as ALE is held HIGH, the input port that was designated in the data portion of the first programming sequence will be retained. To configure the outputs after the first connection, only the ADDR value is shifted in and written. The value will also be cleared during a read instruction regardless of the sense of ALE.

Figure 8 on page 31 shows the programming sequence in serial mode.

#### **Address Striping Mode**

Setting bit 5 of the Switch Configuration register enables striping mode, which allows groups of four inputs to be connected to four outputs with a single programming instruction.

The groups are predetermined and have been selected according to the physical locations of their pins on the package and their numerical ordering. Because even and odd inputs and outputs are on opposite sides of the chip, the groups consist of consecutively numbered even and odd inputs or outputs. The end result is that the inputs and outputs are arranged in 18 "stripes", and any of the 18 input stripes can be connected to any of the 18 output stripes.

Programming of the connections is accomplished by using only the nine MSBs of the ADDR/DATA bus. The two LSBs of the each address or data word should be ignored. For example, the ADDR/DATA word '00000010000'b' specifies stripe 4, which includes inputs or outputs 16, 18, 20, and 22.

A complete list of the ADDR/DATA words is shown in Table 2 on page 10.

G52415 Revision 4.1 October 9, 2003

In Striping mode, the only functionality that is striped is the switch core programming. All other functions such as readback, SENSE control, DRIVE control, precompensation, and output drive level select are accessed and programmed individually.

| Group<br>Number | Input/Output<br>Designations | Group Address | Group<br>Number | Input/Output<br>Designations | Group Address |

|-----------------|------------------------------|---------------|-----------------|------------------------------|---------------|

| 0               | 0, 2, 4, 6                   | 0000000000    | 1               | 1, 3, 5, 7                   | 0000000100    |

| 2               | 8, 10, 12, 14                | 0000001000    | 3               | 9, 11, 13, 15                | 0000001100    |

| 4               | 16, 18, 20, 22               | 00000010000   | 5               | 17, 19, 21, 23               | 0000010100    |

| 6               | 24, 26, 28, 30               | 00000011000   | 7               | 25, 27, 29, 31               | 00000011100   |

| 8               | 32, 34, 36, 38               | 00000100000   | 9               | 33, 35, 37, 39               | 00000100100   |

| 10              | 40, 42, 44, 46               | 00000101000   | 11              | 41, 43, 45, 47               | 00000101100   |

| 12              | 48, 50, 52, 54               | 00000110000   | 13              | 49, 51, 53, 55               | 00000110100   |

| 14              | 56, 58, 60, 62               | 00000111000   | 15              | 57, 59, 61, 63               | 00000111100   |

| 16              | 64, 66, 68, 70               | 00001000000   | 17              | 65, 67, 69, 71               | 00001000100   |

Table 2. Address Striping Mode I/O Grouping

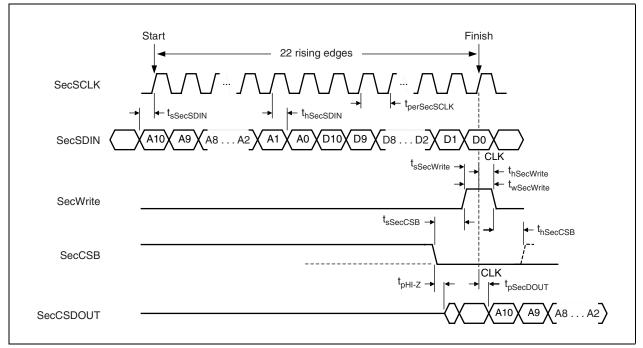

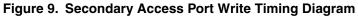

#### **Secondary Access Port**

The Secondary Access Port is an interface to the VSC3139 registers that operates concurrently with the primary programming interface. The main purpose of the Secondary Access Port is to facilitate monitoring and to maintain the operational state of the switch (verify and monitor port connections, die temperature, set drive and equalization levels, and so on) without interrupting the primary port programming operations. The Secondary Access Port allows the primary port to focus strictly on establishing connections while the secondary port performs all other operations "off line".

Before it can be used, the Secondary Access Port must be enabled using the Secondary Access Port Enable bit [7] in the Switch Configuration register (281'h). This bit allows the primary port controller to grant or deny access of the Secondary Access Port as required. If the intention is to have the Secondary Access Port enabled continously, then this bit only needs to be set once during intialization.

To protect the integrity of the Primary Port programming operations, there are two areas of the VSC3139 that are not writeable by the Secondary Access Port. The Switch Connection registers at addresses 000h to 08Fh, and the first two Configuration registers at addresses 280'h and 281'h (register 1 and register 2) may be read by the Secondary Access Port but can only be written to through the Primary Port.

The two interfaces share some logic, therefore care should be exercised when executing certain concurrent operations. In the event that coincident operations are in conflict, an arbitration circuit will grant control as appropriate. A conflict is defined as an overlap of an  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$  assertion on the primary port with an assertion of the SecRead or SecWrite signals on the Secondary Access Port. There is one exception to this rule, and that is when the primary port writes a switch connection. The Secondary Access Port cannot write switch connections, so there is never conflict when the primary port writes a connection, regardless of the activity on the Secondary Access Port.

The Secondary Access Port provides an indication when a read or write operation has been overridden by a Primary Port operation. Upon completion of a successful write operation, the Secondary Access Port echoes back the address and data bits following the SecWrite pulse. In the event of a failed write operation on the Secondary Access Port, the echoed data stream is fully or partially inverted.

For a Secondary Access Port read, the 12<sup>th</sup> bit (the bit after the last bit of valid data) indicates the status of the read. If the bit is a 1, then the previous 11 bits are correct. If the 12<sup>th</sup> bit is a 0, the last read operation was interrupted by an operation on the primary port and the data is corrupt. The primary port is only overridden when a read operation conflicts with a write operation on the Secondary Access Port. In this case, there is no indication of the failed read. In the event the primary port needs to perform uninterrupted read operations, the Secondary Access Port can be disabled.

Table 3 shows the decision matrix for conflicts between the primary and secondary ports.

| Conflict Combinations | Primary Port Write                                                                                                                                                                                                               | Primary Port Read                                                                                                    |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Secondary Port Write  | Result: Priority given to primary port.<br>Indication: SecWrite echoed on SecSDOUT will<br>be fully or partially inverted.<br>Exception: Primary port writes to connection<br>matric do not conflict with secondary port writes. | Result: Priority given to secondary port.<br>Indication: None                                                        |

| Secondary Port Read   | <b>Result:</b> Priority given to primary port.<br><b>Indication:</b> 13 <sup>th</sup> bit of the SecSDOUT will be 0.                                                                                                             | <b>Result:</b> Priority given to primary port.<br><b>Indication:</b> 13 <sup>th</sup> bit of the SecSDOUT will be 0. |

Table 3. Programming Port Conflict Resolution Decision Matrix

#### Table 4. VSC3139 Register Map

| Register Name                                     | ADDR[10:0]       |             | DATA[10:0]     |                       |                                            |                 |                           |                               |                              |                                              |                              |                        |

|---------------------------------------------------|------------------|-------------|----------------|-----------------------|--------------------------------------------|-----------------|---------------------------|-------------------------------|------------------------------|----------------------------------------------|------------------------------|------------------------|

|                                                   |                  | Bit 10      | Bit 9          | Bit 8                 | Bit 7                                      | Bit 6           | Bit 5                     | Bit 4                         | Bit 3                        | Bit 2                                        | Bit 1                        | Bit 0                  |

| Switch Array<br>Connection                        | 0'h - 47'h       |             |                |                       | Input C                                    | Connection      | s 0'h Throu               | ugh 47'h                      | •                            | •                                            |                              |                        |

| Switch Setup                                      | 280'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Not<br>Used                                | Not<br>Used     | Not<br>Used               | Not<br>Used                   | CON-<br>FIG<br>Regis-<br>ter | INITB<br>Regis-<br>ter                       | CON-<br>FIG<br>Disable       | INITB<br>Disable       |

| Switch Configura-<br>tion                         | 281'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Sec-<br>ondary<br>Access                   | Not<br>Used     | Addres<br>s Strip-<br>ing | Stag-<br>ing<br>Read-<br>back | Switch<br>State<br>Store     | User<br>INITB                                | Soft-<br>ware<br>CON-<br>FIG | Soft-<br>ware<br>INITB |

| DRIVE/SENSE<br>Control                            | 282'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Not<br>Used                                | Global<br>SENSE | Global<br>DRIVE           |                               | DRI                          | DRIVE Input Select                           |                              |                        |

| SENSE Connection                                  | 300'h            | Not<br>Used | Drive<br>Level | Power-<br>On<br>State | Address of Output Port Connection to SENSE |                 |                           |                               |                              |                                              |                              |                        |

| Temperature Sen-<br>sor                           | 28B'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Cı                                         | urrent Chip     | Temperati                 | ure                           | Alar                         | m Thresho                                    | ld Tempera                   | ature                  |

| Global Input<br>Channel Configu-<br>ration        | 283'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Not<br>Used                                | Not<br>Used     | Not<br>Used               | Not<br>Used                   |                              | Global Clear for Global Set for Equalization |                              |                        |

| Individual Input<br>Channel Configu-<br>ration    | 600'h -<br>647'h | Not<br>Used | Not<br>Used    | Scan<br>State         |                                            | ization<br>ate  |                           | Input<br>ion State            | Drive Input<br>Source Select |                                              |                              |                        |

| PRBS Generator<br>Configuration                   | 284'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Not<br>Used                                | Not<br>Used     | Not<br>Used               | PRBS<br>Control               | -                            |                                              |                              | Invert<br>Clock        |

| PRBS Receiver/<br>Error Detector<br>Configuration | 285'h            | Not<br>Used | Not<br>Used    | Not<br>Used           | Receiv<br>er Con-<br>trol                  |                 | r Pattern<br>Control      | Input<br>Pattern              | Detec-<br>tor<br>Reset       |                                              | n Pattern<br>Control         | Error<br>Run<br>Length |

| Register Name                      | ADDR[10:0]                           |             | DATA[10:0]  |             |             |                 |             |                 |                        |                         |                         |                                 |

|------------------------------------|--------------------------------------|-------------|-------------|-------------|-------------|-----------------|-------------|-----------------|------------------------|-------------------------|-------------------------|---------------------------------|

|                                    |                                      | Bit 10      | Bit 9       | Bit 8       | Bit 7       | Bit 6           | Bit 5       | Bit 4           | Bit 3                  | Bit 2                   | Bit 1                   | Bit 0                           |

| PRBS Receiver/<br>Error Count Read | 286'h=LS<br>Byte<br>287'h=M<br>SByte | Not<br>Used | Not<br>Used | Not<br>Used |             |                 |             | Error           | Count                  |                         |                         |                                 |

| PRBS Error Status                  | 288'h                                | Not<br>Used | Not<br>Used | Not<br>Used | Not<br>Used | Not<br>Used     | Not<br>Used | Not<br>Used     | Not<br>Used            | Pattern<br>Search       | Count<br>Period         | Error<br>Flag                   |

| Global Output<br>Level Control     | 28A'h                                | Not<br>Used | Not<br>Used | Not<br>Used | Not<br>Used | Not<br>Used     | Not<br>Used | Not<br>Used     | Not<br>Used            | Not<br>Used             | Output<br>Level<br>HIGH | Output<br>Level<br>Nomi-<br>nal |

| Individual Output<br>Level Control | 400'h -<br>447'h                     | Not<br>Used | Not<br>Used | Not<br>Used | Not<br>Used | Not<br>Used     | Not<br>Used | Not<br>Used     | Over-<br>ride<br>Value | Output<br>Over-<br>ride | Output<br>Control       | Output<br>Status                |

| Boundary Scan<br>Control           | 289'h                                | Not<br>Used | Not<br>Used | Not<br>Used |             | Override<br>lue |             | Output<br>rride | Not<br>Used            | Not<br>Used             | Not<br>Used             | Latch<br>Input                  |

| User Status                        | 28C'h -<br>28F'h                     |             |             | Storage     | Registers   | for Transfe     | r Between   | Primary ar      | nd Second              | ary Ports               | •                       |                                 |

# REGISTERS

## Switch Setup and Configuration

#### **Register 1: Switch Setup**

| Reg Name:    | Switch Setup Reg. Address:                                                                                              | 280'h       |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-------------|-----|

| Reg Type:    | R/W                                                                                                                     |             |     |

| Description: | Configuration for various modes of operation.                                                                           |             |     |

| Bit(s)       | Bit Description                                                                                                         | Reset Value | R/W |

| 10-4         | Not used                                                                                                                |             |     |

| 3            | Input pin or software control for CONFIG<br>0 = Use input pin for CONFIG control<br>1 = Use register for CONFIG control | 0           | R/W |

| 2            | Input pin or software control for INIT<br>0 = Use input pin for INIT control<br>1 = Use register for INIT control       | 0           | R/W |

| 1            | CONFIG lockout<br>0 = CONFIG function enable<br>1 = CONFIG function disable (overrides bit 3)                           | 0           | R/W |

| 0            | INITlockout $0 = \overline{INIT}$ function enable $1 = \overline{INIT}$ function disable (overrides bit 2)              | 0           | R/W |

#### **INIT** Lockout

In order to prevent accidental reprogramming of the switch interconnects, the VSC3139 programming interface provides the option of disabling this feature through software. Setting this bit in the Switch Setup register to a 1 will inhibit the use of either the external  $\overline{\text{INIT}}$  pin or the  $\overline{\text{INIT}}$  bit in the Switch Configuration register from reprogramming the interconnects.

On power-up, this bit is 0 and  $\overline{\text{INIT}}$  is enabled.

#### **CONFIG Disable**

In order to prevent accidental reprogramming of the switch interconnects, the VSC3139 programming interface provides the option of disabling the CONFIG feature using the software. Setting the CONFIG bit in the Setup register to a 1 inhibits the use of either the external CONFIG pin or the CONFIG bit in the Control register from reprogramming the interconnects.

On power-up, this bit is 0; CONFIG is enabled.

#### **Register 2: Switch Configuration**

| Reg Name:    | Switch Configuration Reg. Address:                                                                                                                                                                                          | 281'h              |          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|

| Reg Type:    | R/W                                                                                                                                                                                                                         |                    |          |

| Description: | Provides access to features and external pin functions via the programming intervalue and reading returns the current settings.                                                                                             | rface. Writing upd | ates the |

| Bit(s)       | Bit Description                                                                                                                                                                                                             | Reset Value        | R/W      |

| 10-8         | Not used                                                                                                                                                                                                                    |                    |          |

| 7            | Secondary access port enable<br>0 = Disable secondary access port<br>1 = Enable secondary access port                                                                                                                       | 0                  | R/W      |

| 6            | Not Used                                                                                                                                                                                                                    |                    |          |

| 5            | Address stripping mode select<br>0 = Standard address mode<br>1 = Address stripping mode                                                                                                                                    | 0                  | R/W      |

| 4            | Staging readback select<br>0 = Read present switch configuration<br>1 = Read pending switch configuration                                                                                                                   | 0                  | R/W      |

| 3            | Save User INIT<br>The rising edge of the signal stores the user programmed switch configuration in<br>the user programming registers                                                                                        | 0                  | R/W      |

| 2            | User INIT programming<br>0 = Straight-through configuration upon INIT asserted LOW<br>1 = User programmed switch configuration upon INIT asserted LOW, stored<br>using bit 3 of this register                               | 0                  | R/W      |

| 1            | Software programmable CONFIG<br>0 = CONFIG LOW when bit 3 of Switch Setup register, address 280'h, is 1<br>1 = CONFIG HIGH when bit 3 of Switch Setup register, address 280'h, is 1                                         | 0                  | R/W      |

| 0            | Software programmable $\overline{INIT}$<br>0 = $\overline{INIT}$ active when bit 3 of Switch Setup register, address 280'h, is 1<br>1 = $\overline{INIT}$ inactive when bit 3 of Switch Setup register, address 280'h, is 1 | 0                  | R/W      |

#### CONFIG and INIT

The functionality of the CONFIG and  $\overline{INIT}$  pins is duplicated in the two LSBs of the Control register. Writing to either of these bits has the same effect as driving the external pins to the same value. These bits are multiplexed with the external pins through logic and initialize to the state that uses the external pins. The states are therefore mutually exclusive. In order to pulse CONFIG or  $\overline{INIT}$ , write an active signal and then an inactive signal to the register bit of interest. Holding CONFIG HIGH causes the programming to be active upon asserting load. Holding  $\overline{INIT}$  LOW locks the initial programming configuration, whether it be the straight through or the user-defined configuration, as set by bit 2 of the Switch Configuration register.

#### **Staging Register Readback**

When the CONFIG control is used to accumulate a number of program steps and execute them simultaneously, it is possible to verify the pending switch programming prior to asserting the CONFIG control. Setting the staging readback pin to a 1 and reading the programming information from the switch returns configuration information about the pending switch programming rather than the current connections.

If CONFIG is 1, all programming propagates directly to the switch matrix, and the information returned during a readback is the same regardless of the setting of the Staging register readback bit.

### Save User INIT

The VSC3139 provides an alternate set of user-programmable registers that can save and recall the current programming of the staging registers. The programming information in these registers is activated with the  $\overline{\text{INIT}}$  control.

When the Save User  $\overline{\text{INIT}}$  bit is set to 0, the current programming held in the staging registers is transferred into the User Programming registers. Asserting the Save User bit (1) latches the programming information for future use. This switch programming may be recalled by asserting the User  $\overline{\text{INIT}}$  bit (see below).

The Save User  $\overline{INIT}$  bit in the Control register saves the current programming of the VSC3139 switch into the User Programming register(s). The values in the User Programming register(s) are retained until the Save User  $\overline{INIT}$  bit is set to 0 or until power to the device is removed. If the Save User  $\overline{INIT}$  bit is asserted while the User  $\overline{INIT}$  Programming bit is 1, the switch assumes an undefined configuration. On power-up, these registers are in an unknown state.

### User INIT

Asserting the Save User  $\overline{\text{INIT}}$  bit in the Switch Configuration register, address 281'h, selects the User Programming registers as the source for switch programming with the  $\overline{\text{INIT}}$  control. With this bit set, if the  $\overline{\text{INIT}}$  pin or bit is asserted, the switch is programmed to reflect the switch connections saved in the User Programming registers.

Because the User  $\overline{\text{INIT}}$  feature is used in conjunction with the  $\overline{\text{INIT}}$  bit or pin, it can also be disabled using the  $\overline{\text{INIT}}$  Lockout bit in the Switch Setup register, address 280'h.

When activated, the User  $\overline{\text{INIT}}$  Programming bit makes the programming in the user register available to the switch fabric. However, programming does not take place until the Software Programmable  $\overline{\text{INIT}}$  bit or the  $\overline{\text{INIT}}$  pin is asserted. Asserting the  $\overline{\text{INIT}}$  Lockout bit HIGH inhibits any programming of the switch fabric using either the normal or user  $\overline{\text{INIT}}$  registers.

To read back programming information from the User Memory, both the Staging Readback and the User  $\overline{INIT}$  Programming bit must be set. In this configuration, any information read from a specific output represents the programming stored in the User Memory.

## Switch Connection Register

| Table 5. Switch Array Connection Examples | Table 5. | Switch | Array | Connection | Examples |

|-------------------------------------------|----------|--------|-------|------------|----------|

|-------------------------------------------|----------|--------|-------|------------|----------|

| Output ADDR[10:0] | Input ADDR[10:0] | Description                     | Reset Value <sup>(1)</sup> | R/W |

|-------------------|------------------|---------------------------------|----------------------------|-----|

| 000000000,p       | 000000000'b      | Program output Y0 to input A0   | 7FF                        | R/W |

| 000000001'b       | d,000000000,p    | Program output Y1 to input A0   | 7FF                        | R/W |

| 000000010'b       | 000000000'b      | Program output Y2 to input A0   | 7FF                        | R/W |

| 000000011'b       | 000000000'b      | Program output Y3 to input A0   | 7FF                        | R/W |

| 000000100'b       | d,000000000,p    | Program output Y4 to input A0   | 7FF                        | R/W |

| 000000101'b       | 000000000'b      | Program output Y5 to input A0   | 7FF                        | R/W |

|                   |                  |                                 |                            |     |

| 0001000111'b      | 000000000'b      | Program output Y71 to input A0  | 7FF                        | R/W |

|                   |                  |                                 |                            |     |

| 000000000,p       | 0001000111'b     | Program output Y0 to input A71  | 7FF                        | R/W |

| 000000001'b       | 0001000111'b     | Program output Y1 to input A71  | 7FF                        | R/W |

| 000000010'b       | 0001000111'b     | Program output Y2 to input A71  | 7FF                        | R/W |

| 000000011'b       | 0001000111'b     | Program output Y3 to input A71  | 7FF                        | R/W |

| 000000100'b       | 0001000111'b     | Program output Y4 to input A71  | 7FF                        | R/W |

| 000000101'b       | 0001000111'b     | Program output Y5 to input A71  | 7FF                        | R/W |

|                   |                  |                                 |                            |     |

| 0001000111'b      | 0001000111'b     | Program output Y71 to input A71 | 7FF                        | R/W |

1. 7FF is the power-down code.

### **Drive/Sense Control**

### Register 3: DRIVE/SENSE Control

| Reg Name:    | DRIVE/SENSE Control                                                                                                                                                                                                 | Reg. Address: | 282'h       |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-----|

| Reg Type:    | R/W                                                                                                                                                                                                                 |               |             |     |

| Description: | Controls the DRIVE input and SENSE output functions.                                                                                                                                                                |               |             |     |

| Bit(s)       | Bit Description                                                                                                                                                                                                     |               | Reset Value | R/W |

| 10-7         | Not used                                                                                                                                                                                                            |               |             |     |

| 6            | Global SENSE control<br>0 = No effect on existing state of SENSE control signals<br>1 = Clear SENSE connection and turns off output buffer                                                                          |               | 0           | R/W |

| 5-4          | Global DRIVE control<br>00 = maintains current connection state<br>01 = activates connection to DRIVE input selected with bits 3-0<br>10 = clears DRIVE connection state<br>11 = maintains current connection state |               | 00          | R/W |

| 3-0          | DRIVE input source select<br>0000 = input channel connected to DRIVE input                                                                                                                                          |               | 0'h         | R/W |

| Reg Name:    | SENSE Reg                                                                                                       | . Address: | 300'h       |              |

|--------------|-----------------------------------------------------------------------------------------------------------------|------------|-------------|--------------|

| Reg Type:    | R/W                                                                                                             |            |             |              |

| Description: | Controls the operating mode of SENSE output bit.                                                                |            |             |              |

| Bit(s)       | Bit Description                                                                                                 |            | Reset Value | R/W          |

| 10           | Not used                                                                                                        |            |             |              |

| 9            | Drive level for SENSE output. Always returns 1 when bit 8 = 1.<br>0 = nominal drive mode<br>1 = high drive mode |            | 0           | R/W          |

| 8            | Power-on state of SENSE output.<br>0 = on<br>1 = off                                                            |            | 0           | Read<br>only |

| 7-0          | Address of output port connection to SENSE (0 to 47'h for Y0 to Y71) FF'h when SENSE is powered off.            | , returns  | FF'h        | R/W          |

### **Register 4: SENSE Connection**

### **Temperature Sensor/Alarm**

The VSC3139 has circuitry that detects the approximate temperature of the die and flags temperatures exceeding a user-selected, preset range. Register 5 at address 28B'h allows the user to read the die temperature sensor value (an uncalibrated, approximate temperature), and set a temperature threshold at which to assert an alarm.

There are 15, read only temperature ranges for the sensor, and 15 alarm threshold settings.

When the detected die temperature exceeds the user-set threshold, the temperature alarm is asserted.

| Reg Name:    | Temperature Sensor Reg. Ac                               | ddress: | 28B'h       |      |

|--------------|----------------------------------------------------------|---------|-------------|------|

| Reg Type:    | R/W                                                      |         |             |      |

| Description: | User-controllable on-board temperature sensing function. |         |             |      |

| Bit(s)       | Bit Description                                          |         | Reset Value | R/W  |

| 10-8         | Not used                                                 |         |             |      |

| 7-4          | Approximate die temperature (not a calibrated value)     |         |             | Read |

|              | 0000 = 23°C to 41°C                                      |         |             | Only |

|              | 0001 = 33°C to 50°C                                      |         |             |      |

|              | $0010 = 42^{\circ}C \text{ to } 60^{\circ}C$             |         |             |      |

|              | $0011 = 52^{\circ}C \text{ to } 69^{\circ}C$             |         |             |      |

|              | 0100 = 61°C to 78°C                                      |         |             |      |

|              | 0101 = 70°C to 88°C                                      |         |             |      |

|              | 0110 = 80°C to 97°C                                      |         |             |      |

|              | 0111 = 89°C to 106°C                                     |         |             |      |

|              | 1000 = 98°C to 116°C                                     |         |             |      |

|              | 1001 = 108°C to 125°C                                    |         |             |      |

|              | 1010 = 117°C to 135°C                                    |         |             |      |

|              | 1011 = 127°C to 144°C                                    |         |             |      |

|              | 1100 = 136°C to 153°C                                    |         |             |      |

|              | 1101 = 145°C to 163°C                                    |         |             |      |

|              | 1110 = 155°C to 172°C                                    |         |             |      |

|              | 1111 = 164°C to 181°C                                    |         |             |      |

| 3-0          | Temperature alarm threshold                              |         | 00          | R/W  |

|              | 0000 = 23°C to 41°C                                      |         |             |      |

|              | 0001 = 33°C to 50°C                                      |         |             |      |

|              | $0010 = 42^{\circ}C \text{ to } 60^{\circ}C$             |         |             |      |

|              | 0011 = 52°C to 69°C                                      |         |             |      |

|              | 0100 = 61°C to 78°C                                      |         |             |      |

|              | 0101 = 70°C to 88°C                                      |         |             |      |

|              | 0110 = 80°C to 97°C                                      |         |             |      |

|              | 0111 = 89°C to 106°C                                     |         |             |      |

|              | 1000 = 98°C to 116°C                                     |         |             |      |

|              | 1001 = 108°C to 125°C                                    |         |             |      |

|              | 1010 = 117°C to 135°C                                    |         |             |      |

|              | 1011 = 127°C to 144°C                                    |         |             |      |

|              | 1100 = 136°C to 153°C                                    |         |             |      |

|              | 1101 = 145°C to 163°C                                    |         |             |      |

|              | 1110 = 155°C to 172°C                                    |         |             |      |

|              | 1111 = 164°C to 181°C                                    |         |             |      |

**Register 5: Temperature Sensor**

# Input Configuration

The following registers are used to configure the properties of the high-speed data inputs. The two primary properties that can be set for the inputs are the Input Signal Equalization (ISE) and the Drive assignment. These properties can be set both globally and individually on a per input basis. When a property is set globally, it affects the setting for all inputs without exception. When a bit is set in the global registers, that state overrides any attempts to change the setting on an individual basis. It forces the global setting until the bit in the global register is cleared.

The Individual Input Configuration registers also serve a function that is not available in the global registers; the Scan register table. Bit 8 of each Individual Input Configuration register reflects the latched state of the associated high-speed input at the time that bit 0 of register 14 is set to 1.

| Reg Name:    | Global Input Channel Configuration Reg. Addre                                                                                                                                                                                                                                                                                                     | ess: | 283'h       |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-----|

| Reg Type:    | R/W                                                                                                                                                                                                                                                                                                                                               |      |             |     |

| Description: | Global input channel configuration control.                                                                                                                                                                                                                                                                                                       |      |             |     |

| Bit(s)       | Bit Description                                                                                                                                                                                                                                                                                                                                   |      | Reset Value | R/W |

| 10-4         | Not used                                                                                                                                                                                                                                                                                                                                          |      |             |     |

| 3-2          | Global clear for ISE setting.<br>00 = bits 6 and 7 of Individual Input Configuration registers are writeable<br>01 = bit 6 of all Individual Input Configuration registers forced to 0<br>10 = bit 7 of all Individual Input Configuration registers forced to 0<br>11 = bits 6 and 7 of all Individual Input Configuration registers forced to 0 |      | 00          | R/W |

| 1-0          | Global set for ISE setting.<br>00 = bits 6 and 7 of Individual Input Configuration registers are writeable<br>01 = bit 6 of all Individual Input Configuration registers forced to 1<br>10 = bit 7 of all Individual Input Configuration registers forced to 1<br>11 = bits 6 and 7 of all Individual Input Configuration registers forced to 1   |      | 00          | R/W |

### **Register 6: Global Input Channel Configuration**

#### **Register 7: Individual Input Channel Configuration**

| Reg Name:    | Individual Input Channel Configuration                                                                                                                                                                                               | Reg. Address: | 600'h = A0  |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-----|

| Reg Type:    | R/W                                                                                                                                                                                                                                  |               | 601'h = A1  |     |

| Description: | Individual input channel configuration control.                                                                                                                                                                                      |               | 0           |     |

|              |                                                                                                                                                                                                                                      |               | 647'h = A71 |     |

| Bit(s)       | Bit Description                                                                                                                                                                                                                      |               | Reset Value | R/W |

| 10-9         | Not used                                                                                                                                                                                                                             |               |             |     |

| 8            | A[0:71] scan register table (values latched using register 14, bit 0.                                                                                                                                                                |               |             |     |

| 7-6          | ISE setting.<br>00 = ISE disabled<br>01 = Iow ISE<br>10 = medium ISE<br>11 = high ISE                                                                                                                                                |               | 00          |     |

| 5-4          | DRIVE input connection state.<br>00 = maintains current connection state<br>01 = activates connection to DRIVE input as selected by bits 3 thro<br>10 = removes DRIVE connection to input<br>11 = maintains current connection state | ough 0        | 00          | R/W |

| 3-0          | DRIVE input source select.<br>0000 = input channel connected to DRIVE input                                                                                                                                                          |               | 0'h         | R/W |

## **PRBS CONTROL**

The PRBS Generator/Detector is capable of generating and detecting four NRZ patterns:  $2^{7}$ -1,  $2^{9}$ -1,  $2^{10}$ -1, and  $2^{11}$ -1. The main purpose of PRBS Generator/Detector is to be used for switch diagnostics and signal tracing. See the block diagram of the PRBS Generator in Figure 1 on page 5. The data rate of the Generator/Detector is determined by the external clock signal to a maximum 400Mb/s. The PRBS output data is clocked on the rising edge of the clock. The PRBS function controls are located in the PRBS Configuration register 0x284'h. The PRBS Generator is enabled by writing 1 into bit 4 of register 0x284'h. Pattern length is selected via register 0x284'h bit 3 and 2. Selecting 00 will generate pattern  $2^{7}$ -1,  $01 = 2^{9}$ -1,  $10 = 2^{10}$ -1,  $11 = 2^{11}$ -1. It is possible to invert the pattern by writing 1 into register 0x284'h bit 1.

The PRBS Detector uses the same clock as the Generator. See the block diagram of the PRBS Detector in Figure 2 on page 5.

The clock used by the Detector can be inverted by setting bit 0 of register 284'h to 1. It may be necessary to invert CLK in order to compensate for the phase difference between data input and clock.

The PRBS Detector is enabled by writing a 1 into bit 4 of register 285'h. The detector pattern length is selected by bit 6 and bit 5 of register 0x285'h, respectively, 00 represents pattern  $2^{7}$ -1,  $01 = 2^{9}$ -1,  $10 = 2^{10}$ -1,  $11 = 2^{11}$ -1. The error counter is not enabled until the pattern detector matches the pattern coming into the Detector. It can take up to 30 clock cycles to match the pattern, and once the pattern has been detected, bit 2 of register 288'h goes to 1. This enables the error counter and fixed\_error\_count counter. The user has an option to choose the error count period by setting bits 2 and 1 of register 285'h. Respectively, bits 2 and 1 represent the following count lengths:  $00 = 2^{7}$ ,  $01 = 2^{9}$ ,  $10 = 2^{11}$ ,  $11 = 2^{15}$ . When any one of the above periods is selected, error count will continue until that period has elapsed. At that time, the error counter is disabled and the fixed\_error\_count flag will be set to 1 in register 288'h bit 1.

If the errors\_detected flag in register 288'h bit 0 is set to 1, it means that during above set time period, errors occurred and the user can read the error count from registers 267'h and 287'h. After the error count has been read, the error counter can be reset by setting bit 3 of register 285'h to 0. Upon reset, the error counter, errors\_detected, and fixed\_error\_count counter will be set to 0. If the user is not interested in setting any of the above count periods, it is possible to overwrite them by setting bit 0 of register 285'h to 0. This will provide a free-running error count without a predetermined count period. It should be noted though, if error count from 0. It is possible to invert the PRBS pattern that is coming into pattern detector by asserting 1 in register 285'h bit 4. This can be used to detect an inverted pattern from the PRBS Generator.

| Reg Name:    | PRBS Generator/Detector Configuration R                                                                                          | leg. Address: | 284'h       |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-----|

| Reg Type:    | R/W                                                                                                                              |               |             |     |

| Description: | Configures the operating mode of the on-board PRBS Generator/De                                                                  | etector.      |             |     |

| Bit(s)       | Bit Description                                                                                                                  |               | Reset Value | R/W |

| 10-5         | Not used                                                                                                                         |               |             |     |

| 4            | PRBS Generator enable.<br>0 = Disable PRBS generator<br>1 = Enable PRBS generator                                                |               | 0           | R/W |

| 3-2          | PRBS Generator pattern length selection.<br>$11 = 2^{11}-1$<br>$10 = 2^{10}-1$<br>$01 = 2^9-1$<br>$00 = 2^7-1$                   |               | 00          | R/W |

| 1            | PRBS output pattern.<br>0 = Non-inverted pattern<br>1 = Inverted pattern                                                         |               | 0           | R/W |

| 0            | PRBS Error Detector clock phase selection (to correct for timing ske<br>0 = Non-inverted clock phase<br>1 = Inverted clock phase | ews).         | 0           | R/W |

# **Register 8: PRBS Generator Configuration**

### **Register 9: PRBS Error Status**

| Reg Name:    | PRBS Error Status                                                                                                                                                                | Reg. Address: | 288'h       |              |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|--------------|

| Reg Type:    | R/W                                                                                                                                                                              |               |             |              |

| Description: | Report error status from the on-board PRBS detector.                                                                                                                             |               |             |              |

| Bit(s)       | Bit Description                                                                                                                                                                  |               | Reset Value | R/W          |

| 10-3         | Not used                                                                                                                                                                         |               |             |              |

| 2            | Error Detector search status<br>0 = Error Detector has not locked onto a valid PRBS pattern<br>1 = PRBS pattern detected. Detector is counting errors.                           |               | 0           | Read<br>Only |

| 1            | Error count period indicator (not valid if register 10, bit 0 = 0)<br>0 = Fixed error count period has not yet been completed<br>1 = Fixed error count period has been completed |               | 0           | Read<br>Only |

| 0            | Error flag bit (reset when read)<br>0 = No errors detected since last reset<br>1 = Errors detected since last reset                                                              |               | 0           | Read<br>Only |

| Reg Name:    | PRBS Receiver/Error Detector Configuration Reg. Address:                                                                                            | 285'h       |     |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|--|--|

| Reg Type:    | R/W                                                                                                                                                 |             |     |  |  |

| Description: | Configures the operating mode of the on-board PRBS receiver/error detector.                                                                         |             |     |  |  |

| Bit(s)       | Bit Description                                                                                                                                     | Reset Value | R/W |  |  |

| 10-8         | Not used                                                                                                                                            |             |     |  |  |

| 7            | PRBS receiver enable<br>0 = Disable PRBS<br>1 = Enable PRBS detector                                                                                | 0           | R/W |  |  |

| 6-5          | Select receiver/error detector pattern length<br>(to match PRBS generator)<br>$11 = 2^{11}-1$<br>$10 = 2^{10}-1$<br>$01 = 2^9-1$<br>$00 = 2^7-1$    | 00          | R/W |  |  |

| 4            | PRBS input pattern<br>0 = Non-inverted PRBS input<br>1 = Inverted PRBS input                                                                        | 0           | R/W |  |  |

| 3            | Error detector reset<br>0 = Resets error count<br>1 = Enables error count                                                                           | 0           | R/W |  |  |

| 2-1          | Error counter length control (dependent on bit 0)<br>$11 = 2^{15} \cdot 1$<br>$10 = 2^{11} \cdot 1$<br>$01 = 2^{9} \cdot 1$<br>$00 = 2^{7} \cdot 1$ | 00          | R/W |  |  |

| 0            | Error detection run length<br>0 = No stop length, free running error detection<br>1 = Run and stop at count length                                  | 0           | R/W |  |  |

### **Register 10: PRBS Receiver/Error Detector Configuration**

### Register 11: PRBS Error Count Read

| Reg Name:    | PRBS Error Count Read Reg. Address:                  | 286'h = LSB R<br>287'h = MSB F | 0         |

|--------------|------------------------------------------------------|--------------------------------|-----------|

| Reg Type:    | R/W                                                  |                                |           |

| Description: | Provides Error Count report.                         |                                |           |

| Bit(s)       | Bit Description                                      | Reset Value                    | R/W       |

| 10-8         | Not used                                             |                                |           |

| 7-0          | Number of errors since start of count or last reset. | 00'h                           | Read only |

## **Programmable Output Drive Levels**

Two output drive levels can be set using the Output Level Control register. Output drive level can be controlled both globally and on a per-channel basis through either the primary programming port or the Secondary Access Port. If both HIGH and LOW output bits are enabled simultaneously, LOW output level mode takes precedence.

### **Register 12: Global Output Level Control**

| Reg Name:    | Global Output Level Control                                                           | leg. Address: | 28A'h       |     |

|--------------|---------------------------------------------------------------------------------------|---------------|-------------|-----|

| Reg Type:    | R/W                                                                                   |               |             |     |

| Description: | Enables global output high drive/nominal drive mode.                                  |               |             |     |

| Bit(s)       | Bit Description                                                                       |               | Reset Value | R/W |

| 10-8         | Not used                                                                              |               |             |     |

| 7-4          | Internal use only                                                                     |               |             |     |

| 3-2          | Not used                                                                              |               |             |     |

| 1            | High output level mode<br>0 = No change<br>1 = Force all outputs to high drive mode   |               | 0           | R/W |

| 0            | Low output level mode<br>0 = No change<br>1 = Force all outputs to nominal drive mode |               | 0           | R/W |

#### **Register 13: Individual Output Level Control**

| Reg Name:    | Individual Output Level Control Reg                                                                                                                                            | g. Address:  | 400'h = Y0        |              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|--------------|

| Reg Type:    | R/W                                                                                                                                                                            |              | 401'h = Y1        |              |

| Description: | Enables individual output high drive/nominal drive mode.                                                                                                                       |              | to<br>447'h = Y71 |              |

| Bit(s)       | Bit Description                                                                                                                                                                |              | Reset Value       | R/W          |

| 10-9         | Internal use only                                                                                                                                                              |              | 00                |              |

| 8-4          | Not used                                                                                                                                                                       |              |                   |              |

| 3            | Override output value<br>0 = Force the addressed Y output value to 0 when bit 2 is HIGH<br>1 = Force the addressed Y output value to 1 when bit 2 is HIGH                      |              | 0                 | R/W          |

| 2            | Output override mode (boundary scan support) control<br>0 = Disable output override mode<br>1 = Enable output override mode. Y output forced to value stored in bi<br>register | it 3 of this | 0                 | R/W          |

| 1            | Individual output level control<br>0 = Set output level nominal<br>1 = Set output level HIGH                                                                                   |              | 0                 | R/W          |

| 0            | Individual output status<br>0 = Y output OFF<br>1 = Y output ON                                                                                                                |              | 0                 | Read<br>Only |

## **Boundary Scan Support**

The VSC3139 has provisions for sampling the current state of the high-speed data inputs, as well as driving the high-speed data outputs with a static value.

To reduce power consumption, the input buffers for the boundary scan are powered off after reset. Prior to using the Scanning feature, these buffers must be energized by setting bit 1 of the Boundary Scan Control register to 1. Once the boundary scan input feature is no longer in use, this bit can once again be set to 0 to reduce power consumption.

Sampling of the high-speed data inputs is triggered by writing a 1 to bit 0 of the Boundary Scan Control register. This bit is self-clearing; it does not need to be cleared prior to the next operation, as it returns a 0 when read. This operation latches the current value of the high-speed inputs into bit 8 of each respective Input Channel Configuration register (600'h - 647'h). These registers can be read one by one to determine the state of each input.