# **High-Side TMOS Driver**

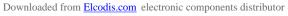

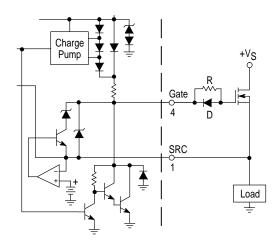

The MC33091A is a High–Side TMOS Driver designed for use in harsh automotive switching applications requiring the capability of handling high voltages attributed to load and field dump transients, as well as reverse and double battery conditions. Few external components are required to drive a wide variety of N–Channel TMOS devices. The MC33091A, driving an appropriate TMOS device, offers economical system solutions for high–side switching large currents. The MC33091A has CMOS compatible input control, charge pump to drive the TMOS power transistor, basic fault detection circuit,  $V_{DS}$  monitoring circuit used to detect a shorted TMOS load, and overcurrent protection timer with associated current squaring circuitry.

Short circuit protection is made possible by having a unique  $V_{DS}$  voltage to current converter drive an externally programmable integrator circuit. This circuit affords fast detection of a shorted load while allowing difficult loads, such as <u>lamps</u> having high in–rush currents, additional time to turn on.

The Fault output is comprised of an open collector NPN transistor requiring a single pull–up resistor for operation. A fault is reported whenever the MOSFET on–current exceeds an externally programmed set level.

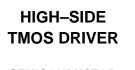

The MC33091A is available in the plastic 8–Pin DIP package as well as the plastic 8–Pin surface mount package.

- Designed for Automotive High–Side Driver Applications

- Works with a Wide Variety of N-Channel Power MOSFETs

- Drives Inductive Loads with No External Clamp Circuitry Required

- CMOS Logic Compatible Input Control

- On–Board Charge Pump with No External Components Required

- Shorted Load Detection and Protection

- Forward Overvoltage and Reverse Battery Protection

- Load and Field Dump Protection

- Extended Operating Temperature Range

- Fault Output to Report a MOSFET Overcurrent Condition

SEMICONDUCTOR TECHNICAL DATA

### **ORDERING INFORMATION**

| Device    | Operating<br>Temperature Range   | Package     |  |

|-----------|----------------------------------|-------------|--|

| MC33091AD | T <sub>Δ</sub> = – 40° to +125°C | SO–8        |  |

| MC33091AP | $T_{A} = -40 \ 10 + 125 \ C$     | Plastic DIP |  |

© Motorola, Inc. 1996

### MAXIMUM RATINGS

| Rating                                                                                       | Symbol           | Value                   | Unit |

|----------------------------------------------------------------------------------------------|------------------|-------------------------|------|

| Supply Voltage (Pin 5) (Note 1)<br>Continuous (Without Activating Clamp)                     | VCC              | -0.7 to 28<br>7.0 to 28 | V    |

| Continuous Supply Clamp Current (Pin 5)<br>DIP Package (Case 626)<br>SO–8 Package (Case 751) | IC               | 10<br>1.0               | mA   |

| Input Control Voltage Range (Pin 7)<br>Continuous                                            | V <sub>in</sub>  | -0.7 to 28              | V    |

| Fault Pull–Up Voltage Range (Pin 6)<br>Continuous                                            | Vout             | -0.7 to 28              | V    |

| Minimum ESD Voltage Capability (Note 2)                                                      | ESD              | 2000                    | V    |

| Operating Junction Temperature                                                               | Тј               | 150                     | °C   |

| Storage Temperature                                                                          | T <sub>stg</sub> | -65 to +150             | °C   |

| Operating Ambient Temperature Range                                                          | Т <sub>А</sub>   | -40 to +125             | °C   |

| Thermal Resistance, Junction-to-Ambient<br>DIP Package (Case 626)<br>SO-8 Package (Case 751) | R <sub>θJA</sub> | 100<br>145              | °C/W |

NOTES: 1. An internal zener diode is incorporated to protect the device from overvoltage transients in excess of 30 V. 2. ESD testing performed in accordance with Human Body Model (C = 100 pF, R = 1500  $\Omega$ ).

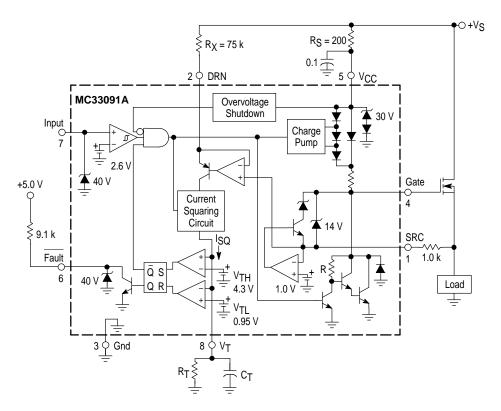

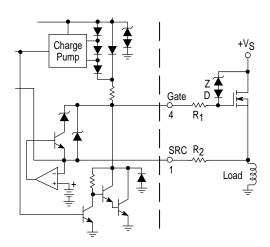

### **Figure 1. Typical Application**

| Characteristics                                                                                       | Symbol                             | Min        | Тур         | Max        | Unit     |

|-------------------------------------------------------------------------------------------------------|------------------------------------|------------|-------------|------------|----------|

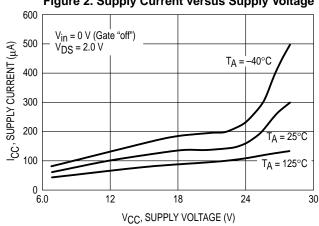

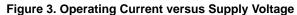

| Supply Current (Note 1)<br>$V_{in} = 0 V$<br>$V_{in} = 5.0 V (R_X = 100 k)$                           | ICC                                | _          | 160<br>2.5  | 300<br>6.0 | μA<br>mA |

| Supply Clamp Voltage (Note 2)                                                                         | VZ                                 | 29         | -           | 35         | V        |

| Gate-to-Source Voltage Range (Pin 4)                                                                  | VGS                                | 8.0        | 12          | 15         | V        |

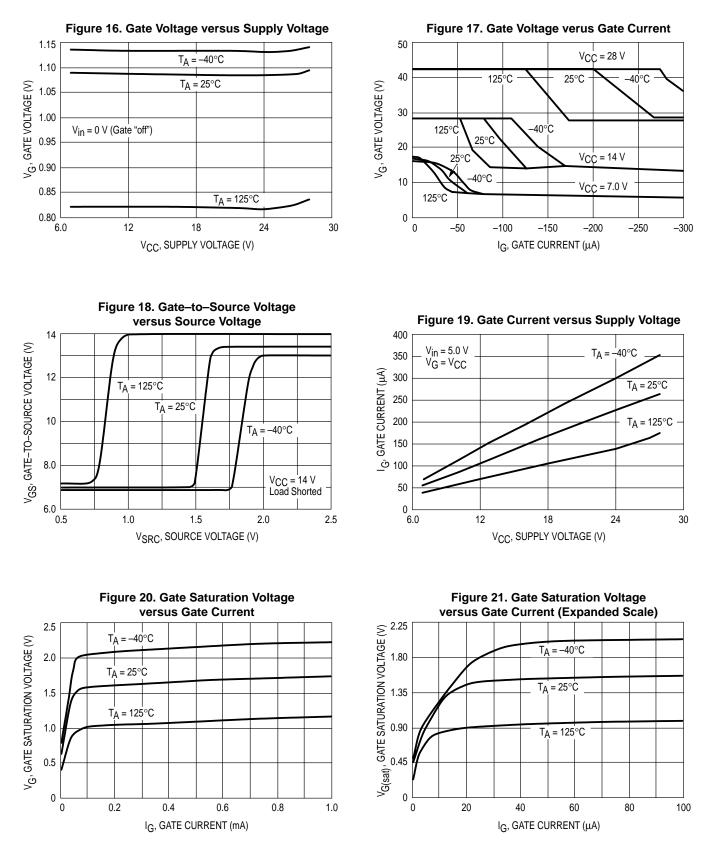

| Gate Current (Pin 4)<br>$V_G = V_{CC}$                                                                | IG                                 | 30         | _           | 400        | μA       |

| Gate Saturation Voltage (I <sub>G</sub> = 10 $\mu$ A)                                                 | V <sub>G(sat)</sub>                | 0          | 1.2         | 1.4        | V        |

| Short Circuit Gate Voltage (Note 4)                                                                   | IGC                                | 6.4        | 7.0         | 7.7        | V        |

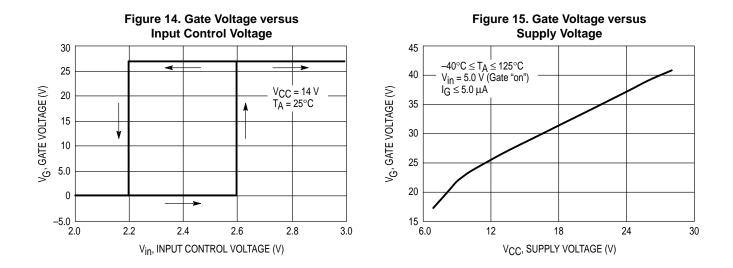

| Input Control Threshold Voltage (Pin 7)                                                               | V <sub>IL</sub><br>V <sub>IH</sub> | _<br>3.5   | 2.7<br>2.7  | 1.5<br>-   | V        |

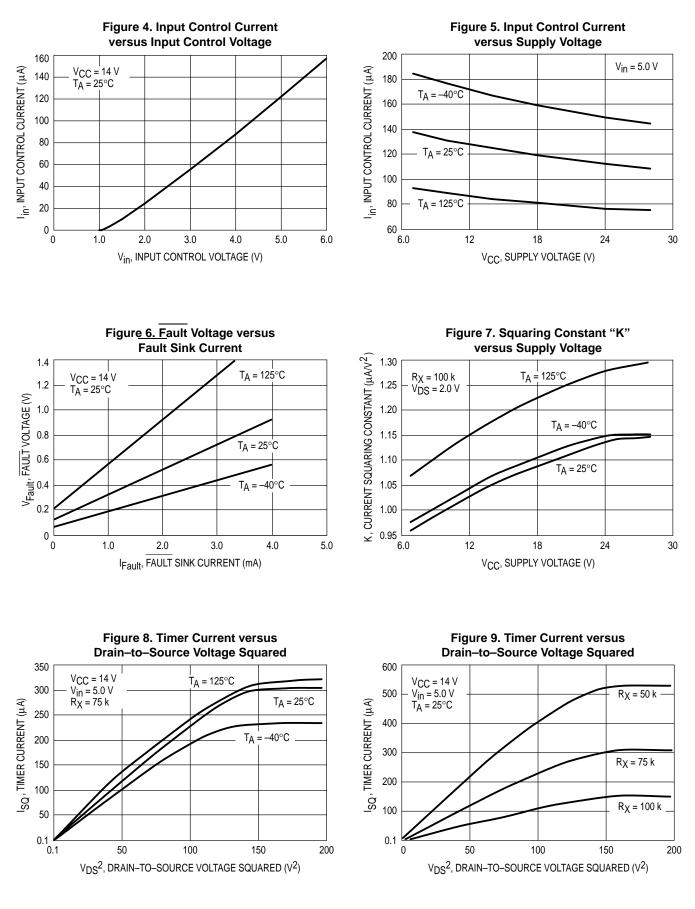

| Input Control Current (Pin 7) (V <sub>in</sub> = 5.0 V)                                               | l <sub>in</sub>                    | -          | 100         | 250        | μA       |

| Timer Current Constant (Pin 8)<br>( $R_X = 100 \text{ k}, V_T = 0, V_{DS} = 1.0 \text{ V}$ ) (Note 3) | К                                  | 0.7        | 1.1         | 1.5        | μA/V2    |

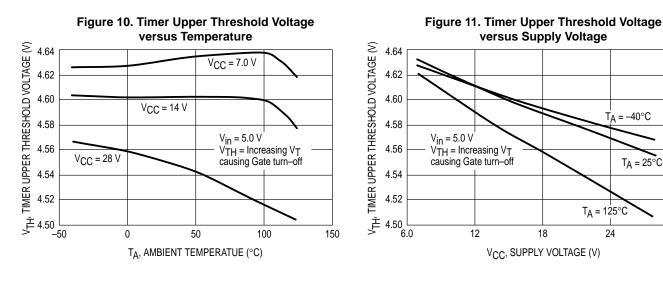

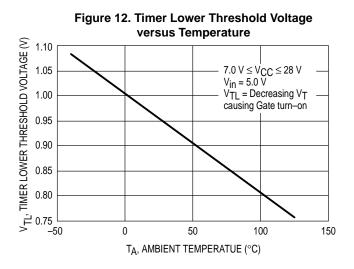

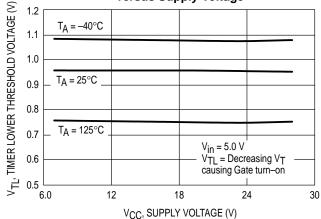

| Timer (Pin 8)<br>Lower Threshold Voltage<br>Upper Threshold Voltage                                   | VTL<br>VTH                         | 0.4<br>4.3 | 0.95<br>4.6 | 1.2<br>5.2 | V        |

| Fault Sink Current (Pin 6)<br>$V_F = 5.0 V$<br>$V_F = 0$                                              | I <sub>OL</sub><br>I <sub>OH</sub> | 500<br>-   | _<br>2.0    | _<br>100   | μA<br>nA |

| Fault Saturation Voltage (Pin 6) (I <sub>F</sub> = 500 μA)                                            | V <sub>OL</sub>                    | -          | 0.2         | 0.8        | V        |

**ELECTRICAL CHARACTERISTICS** (Values are noted under conditions of 7.0 V  $\leq$  V<sub>CC</sub>  $\leq$  24 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C, unless otherwise noted. Typical values reflect approximate mean at T<sub>A</sub> = 25°C at time of device characterization.)

**NOTES:** 1. The total supply current into Pin 2 and Pin 5 with  $R_X = 100 \text{ k}$  (from Pin 2 to supply) and 45 k pull–up resistor from Pin 6 to supply. 2. An internal zener clamp is provided to protect the device from overvoltage transients on the supply line.

3. The timer current constant is the proportionality constant of the voltage to current converter used to monitor the VDS voltage developed across the FET (from Pin 1 to the supply).

4. The gate voltage will be clamped at approximately 7.0 V above the source voltage whenever the source voltage is less than approximately 1.0 V above ground.

### Figure 2. Supply Current versus Supply Voltage

### MOTOROLA ANALOG IC DEVICE DATA

30

t, TIME (µs)

t, TIME (µs)

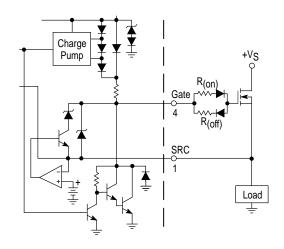

## Figure 28. Descriptive Waveform Diagram

# MC33091A FUNCTIONAL DESCRIPTION

#### Introduction

The MC33091A is designed to drive a wide variety of N-channel TMOS transistors in high-side configured, low frequency switching applications. The MC33091A has an internal charge pump to fully enhance the on-state of the TMOS device. The MC33091A protects the TMOS device from shorts to ground and provides a Fault output to report the presence of an overcurrent condition. The few additional external components required allow tailoring of the application's protection level. The protection scheme of the MC33091A uses an externally programmable, nonlinear timer that disables the TMOS device in the event the drain to source voltage exceeds a specified value for a specified duration. Both the value and duration are externally programmable allowing for flexibility in applications.

#### **Description of Pins**

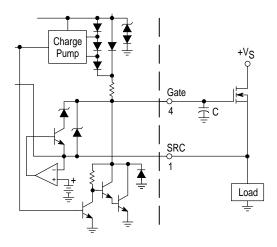

Figure 1 shows a typical application as well as the internal functional blocks of the MC33091A. The discussion to follow references this figure.

**Input (Pin 7):** The logic levels of the Input are compatible with CMOS logic families. The Input enables the protection and charge pump circuitry. With the Input in a logic low state the MC33091A draws only leakage current of less than 300  $\mu$ A and in this condition the associated TMOS device will be in the "off" state. When the Input is in a logic high state, the Gate voltage (Pin 4) rise is limited to a maximum of 14 V above SRC (Pin 1), due to an internal clamp diode being used and the TMOS device is enhanced full on.

**Fault (Pin 6):** The Fault output is comprised of an open collector NPN transistor capable of sinking at least 500  $\mu$ A when the TMOS gate is disabled due to an overcurrent condition. When the <u>TMOS</u> device experiences an overcurrent condition, the Fault pin is pulled low.

**SRC (Pin 1):** The SRC pin senses the TMOS source voltage and is the input to the  $V_{DS}$  buffer used in conjunction with the DRN pin in monitoring the drain to source voltage developed across the TMOS device. The purpose of the 1.0 k resistor connected to this pin is to protect the SRC input from overvoltage as a result of flyback voltage produced when the TMOS device is used to switch large inductive loads. This resistor can be eliminated when switching noninductive loads.

**DRN (Pin 2):** The DRN is used in conjunction with the SRC pin and together constitute a V<sub>DS</sub> monitor of the TMOS drain to source voltage. Feedback from the SRC pin will maintain a voltage across the resistor,  $R_X$ , equal to the V<sub>DS</sub> voltage developed across the TMOS device. The series resistor,  $R_X$ , connected between the drain of the TMOS device and DRN of the MC33091A is used in conjunction with the feedback buffer and associated PNP transistor to establish a current proportional to the drain to source voltage, V<sub>DS</sub>, of the TMOS device. This proportional current, acted upon by the current squaring circuit of the MC33091A, is an important part of the TMOS protection scheme.

V<sub>CC</sub> (Pin 5): The V<sub>CC</sub> pin supplies operational power to the MC33091A. An internal 30 V zener clamp connected to this

pin provides overvoltage protection of the MC33091A. When the zener is activated, the MC33091A disables the T<u>MOS</u> device only for the duration of the overvoltage but <u>the Fault</u> output (Pin 6) does not change logic states. The Fault pin does not go to a logic low state during the overvoltage duration since this is not an MC33091A device fault, but an external system fault.

**Gate (Pin 4):** The Gate pin of the MC33091A is the output of the internal charge pump which controls the TMOS device. The charge pump is a voltage tripler and requires no additional external components for operation. When the Input is at a logic low state, the charge pump will be turned off. When the Input is pulled to a logic high state, with no load fault existing, the charge pump turns on and pumps the TMOS gate voltage to at least 8.0 V, typically 10 to 14 V, above V<sub>CC</sub>. An internal zener clamp is incorporated to limit the Gate to approximately 14 V above the source and prevent rupture of the TMOS gate.

**V**<sub>T</sub> (**Pin 8**): The Timer pin (V<sub>T</sub>) is both an input to the timer window comparators and an output of the current squaring circuit. An external resistor ( $R_T$ ) and capacitor ( $C_T$ ) are tied to this node so as to afford programing the characteristics necessary for protection of the TMOS device.

#### **Overcurrent Protection Timer**

The MC33091A protection scheme is based on the ability of the MC33091A to constantly sense the voltage drop developed across the TMOS device. A low voltage drop is indicative of normal TMOS "on" operation while a large voltage drop represents the existence of an overcurrent condition. By monitoring the TMOS drain to source voltage (V<sub>DS</sub>) the MC33091A is able to detect a shorted load and react to disable the TMOS device. The circuit protection scheme is essentially based on a timer whose rate is dependent on the magnitude of V<sub>DS</sub>. If the drain to source voltage drive very quickly. If V<sub>DS</sub> is only slightly above the normal operating level, the timer will take much longer to disable the gate drive.

Since the power dissipated in the TMOS device is proportional to  $V_{DS}^2$ , low  $V_{DS}$  conditions can be tolerated for a longer time than high  $V_{DS}$  conditions. To enhance the system application, the timer time–out of the MC33091A is inversely proportional to  $V_{DS}^2$ . This approach maximizes the TMOS operating range. The timer parameters are completely user programmable through the use of external components affording application usage of a wide variety of TMOS devices. This is intended to model the generation and dissipation of heat within the TMOS device.

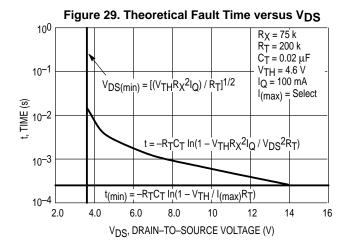

The external components R<sub>X</sub>, R<sub>T</sub> and C<sub>T</sub> determine the timer characteristics. Once enabled, the MC33091A will source a current, I<sub>SQ</sub>, from the timer pin that is proportional to  $V_{DS}^2$  such that:

$$I_{SQ} = KV_{DS}^{2}$$

(1)

where: K = 1/(R $\chi^{2}I_{Q}$ )

IQ is an internal current source parameter of the MC33091A that has a nominal value of 100  $\mu$ A and R $\chi$  is the external resistor in series with the drain of the TMOS device that establishes the value of the voltage to current proportionality constant. Since the parallel combination of RT and CT appear at the timer pin (VT), the timer pin voltage, VT, can be written as:

$$V_{T}(t) = I_{SQ}R_{T}[1 - e^{-t/(R_{T}C_{T})}]$$

<sup>(2)</sup>

With the Input (Pin 7) in a logic high state and no overcurrent condition exists, the TMOS device will be in the "on" state. If the TMOS device experiences an overcurrent condition,  $I_{SQ}$  flowing through  $R_T$  will increase causing  $C_T$  to charge up, in turn causing the timer voltage,  $V_T$ , to exceed the threshold,  $V_{TH}$ , of the upper comparator. This sets the latch causing the Q output of the latch to go high (and the Q output to go low), causing the TMOS gate and Fault output (Pin 6) to be pulled low, disabling the TMOS device. Both the current squaring circuit ( $I_{SQ}$ ) and the charge pump are disabled whenever the Q output of the latch goes low. Using Equation 2, the fault time response for an overcurrent condition can be written as:

$$t = -R_T C_T \ln(1 - V_{TH} / I_{SQ} R_T)$$

(3)

Using Equation 1 and substituting for ISQ in Equation 3:

$$t = -R_T C_T \ln[1 - (V_{TH} R_X^2 I_Q) / (V_{DS}^2 R_T)]$$

(4)

When the timer current (I<sub>SQ</sub>) is disabled, the attained V<sub>TH</sub> voltage at Pin 8 decays according to the R<sub>T</sub>C<sub>T</sub> time constant until the V<sub>TL</sub> threshold of the lower comparator is reached. At this point the latch is reset and the TMOS gate, charge pump and the current squaring circuit are again enabled, again turning on the TMOS device. The MC33091A will repeatedly duty cycle the TMOS gate in this manner so long as the overcurrent condition exists an<u>d the</u> input control signal remains in a high logic state. The Fault output (Pin 6) will likewise duty cycle.

Consider the case where in Equation 4 the term  $(V_{TH}R_X^{2I}Q) / (V_{DS}^{2}R_{T}) \ge 1$  such that the time period is undefined. Solving for  $V_{DS}$  for this case yields the *minimum* drain to source voltage necessary which will *not* allow V<sub>T</sub> to charge to the V<sub>TH</sub> threshold of the upper comparator. In other words, whenever the TMOS on-time period is infinite, *no* TMOS overcurrent condition exists. The minimum drain to source voltage required for uninterrupted continuous TMOS operation is:

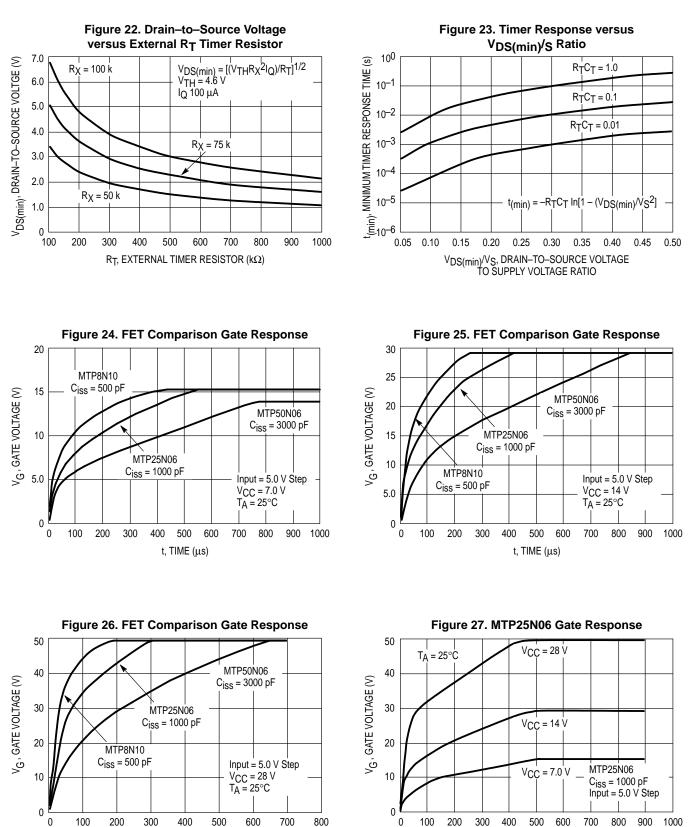

$$V_{DS(min)} = [(V_{TH}R\chi^2 I_Q)/R_T]^{1/2} = (V_{TH}/KR_T)^{1/2}$$

(5)

Under *normal* operating steady state TMOS "on" conditions; the values chosen for  $R_X$  and  $R_T$  should be such that the upper comparator threshold voltage is *never* reached. This insures the TMOS device will always be in operation so long as the  $V_{DS(min)}$  is not exceeded.

The minimum time required for the capacitor  $C_T$  to charge up to upper comparator threshold voltage occurs when the TMOS device experiences maximum current ( $I_{max}$ ). This will occur when the load, and in turn the source, are shorted to ground resulting in the full battery voltage (V<sub>S</sub>) to appear directly across the TMOS device. This condition causes maximum  $I_{SQ}$  current to be produced by the current squaring circuit. The maximum  $I_{SQ}$  current experienced is:

$$I_{SQ(max)} = KV_S^2 = (V_S/R_X)^2/I_Q$$

(6)

An expression for the minimum time–out is obtained by substituting  $I_{\mbox{\scriptsize Q}}$  of Equation 6 into Equation 3:

$$t_{(min)} = -R_T C_T \ln[1 - V_{TH} / (I_{SQ(max)} R_T)]$$

(7)

Equation 4 is shown graphically along with the asymptotic limits imposed by Equations 5 and 7 in Figure 29.

When driving incandescent lamp loads, the minimum timer time-out (time required for the V<sub>T</sub> voltage to reach V<sub>TH</sub> threshold of the upper comparator) should be set long enough so as to *not* allow the in-rush current of incandescent lamp to cause a false trigger, yet short enough to afford the TMOS device survival protection against direct shorts under worst case supply and temperature conditions.

#### **TMOS Driver Power Dissipation**

Under load short conditions, the MC33091A will duty cycle the TMOS gate. The power dissipation in this mode can be significant. For this reason proper heatsinking of the TMOS device is essential as is the selection of compatible external components so as to protect the TMOS device from destruction. In most cases, the heatsink required to handle the TMOS power dissipation under normal operating conditions will be adequate to insure the device survives a short circuit for an indefinite time under worst case conditions.

The MC33091A can protect the TMOS device under a direct load short condition. If the source voltage is less than about 1.5 V above ground, which will normally be the case in the event of a dead short, the MC33091A will clamp the gate to source voltage at 7.0 V. This action will limit the TMOS current and power dissipated under a direct load short condition.

The data sheet for the particular TMOS device being used will normally reveal the current value,  $I_{DS(max)}$ , to be expected under a dead short condition. TMOS data sheets normally depict graphs of drain current versus drain to source voltage for various gate to source voltages from which the drain current at 7.0 V V<sub>GS</sub>,  $I_{DS(max)}$ , can reasonably be approximated. Using this information, the peak TMOS power dissipation under a dead short condition is approximated to be:

$$P_{D(peak)} = V_{S(max)}I_{DS(max)}$$

(8)

The average power is equal to the peak power dissipation multiplied by the duty cycle (DC):

$$P_{D(avg)} = P_{D(peak)}DC$$

(9)

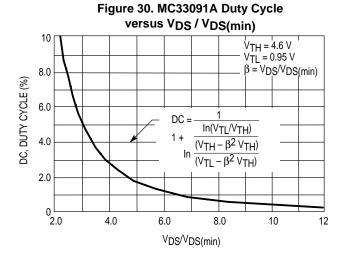

As long as the average power, in Equation 9, is less than the maximum power dissipation of the TMOS device under normal conditions, the short circuit protection scheme of the MC33091A will adequately protect the TMOS device. The duty cycle at which the MC33091A controls the gate can be determined by using Figure 30.

As previously discussed, ISQ is externally dependant on the sensed V<sub>DS</sub> voltage developed across the TMOS device and R<sub>X</sub> in accordance with Equations 1 and 2. At the onset of an overload condition, the voltage across C<sub>T</sub> will be less than the V<sub>TH</sub> threshold voltage of the upper comparator with the TMOS device in an "on" state. I<sub>SQ</sub> current will increase dramatically and the timing capacitor C<sub>T</sub> charges toward V<sub>TH</sub>. When the voltage on C<sub>T</sub> reaches the V<sub>TH</sub> threshold voltage of the upper comparator, the upper comparator output goes high setting the latch output (Q) high, t<u>urning</u> on the open collector NPN transistor and pulling the Fault output low. At the same time, I<sub>SQ</sub> is switched off, allowing C<sub>T</sub> to discharge through resistor R<sub>T</sub> to V<sub>TL</sub>, at which time the TMOS device is again switched on. This action is repeated so long as the overload condition exists. The V<sub>TL</sub> and V<sub>TH</sub> thresholds are internally set to approximately 0.95 V and 4.6 V respectively. The charge time (t<sub>c</sub>) of C<sub>T</sub> can be shown as:

$t_{c} = -R_{T}C_{T} \ln[1 - (V_{TH} - V_{TL})/(I_{SQ}R_{T} - V_{TL})]$ (10)

The discharge time  $(t_d)$  of  $C_T$  can be shown as:

$$t_{d} = -R_{T}C_{T} \ln(V_{TL}/V_{TH})$$

(11)

The duty cycle is defined as charge time divided by the charge plus discharge time and represented by:

$$DC = t_C / (t_C + t_d)$$

(12)

Substituting Equations 10 and 11 into 12:

$DC = \frac{1}{1 + \ln(V_{TL}/V_{TH})} / \ln\{(V_{TH} - \beta^2 V_{TH}) / (V_{TL} - \beta^2 V_{TH})\} (13)$

where:

$$\beta = V_{DS}/V_{DS}(min)$$

Notice the duty cycle is dependent *only* on the ratio of the drain to source voltage,  $V_{DS}$ , of the TMOS device to the minimum drain to source voltage,  $V_{DS}(min)$ , allowing uninterrupted continuous TMOS operation as calculated in Equation 5. A graph of Equation 13 is shown in Figure 30 and is valid for any ratio of  $V_{DS}$  to  $V_{DS}(min)$ . Knowing this ratio, the duty cycle can be determined by using Figure 30 or Equation 13 and knowing the duty cycle, the average power dissipation can be calculated by using Equation 9.

If the TMOS device experiences a hard load short to ground a minimum duty cycle will be experienced which can be calculated. When this condition exists, the TMOS device experiences a V<sub>DS</sub> voltage of V<sub>S</sub> which is sensed by the MC33091A. The MC33091A very rapidly charges the timing capacitor C<sub>T</sub> to V<sub>TH</sub> shutting down the TMOS device. This condition produces the minimum duty cycle for the specific system conditions. The minimum duty cycle can be calculated for any valid V<sub>S</sub> voltage by substituting the value of V<sub>S</sub> used for V<sub>DS</sub> in Equation 13 and solving for the duty cycle.

Knowing the duty cycle and peak power allows determination of the average power as was pointed out in Equation 9. TMOS data sheets specify the maximum allowable junction temperature and thermal resistance, junction-to-case, at which the device may be operated. Knowing the average power and the device thermal information, proper heatsinking of the TMOS device can be determined.

The duty cycle graph (Figure 30) reveals lower values of  $V_{DS}(min)$  produce shorter duty cycles, for given  $V_{DS}$  voltages. The minimum duty cycle, being limited to the case where  $V_{DS} = V_S$ , increases as higher values of  $V_S$  are used.

# MC33091A APPLICATION

The following design approach will simplify application of the MC33091A and will insure the components chosen to be optimal for a specific application.

1. Characterize the load impedance and determine the maximum load current possible for the load supply voltage used.

2. Select a TMOS device capable of handling the maximum load current. Though the MC33091A will equally drive our competitors products, it is hoped you will select one of the many TMOS devices listed in Motorola's *Power MOSFET Transistor Data Book*.

3. Determine the maximum steady state VDS voltage the TMOS device will experience under normal operating conditions. Typically, this is the maximum load current multiplied by the specified RDS(on) of the TMOS device. Junction temperature considerations should be taken into account for the RDS(on) value since it is significantly temperature dependent. Normally, TMOS data sheets depict the effect of junction temperature on RDS(on) and an RDS(on) value at some considered maximum junction temperature should be used. Various graphs relating to RDS(on) are depicted in Motorola TMOS data sheets. Though Motorola TMOS devices typically specify a maximum allowable junction temperature of 150°C, in a practical sense, the user should strive to keep junction temperature as low as possible so as to enhance the applications long term reliability. The maximum steady state VDS voltage the TMOS device will experience under *normal* operating conditions is thus:

$$V_{DS(norm)} = I_{L(max)}R_{DS(on)}$$

(14)

4. Calculate the maximum power dissipation of the TMOS device under *normal* operating conditions:

$$P_{D(max)} = V_{DS(on)}I_{L(max)}$$

(15)

5. The calculated maximum power dissipation of the TMOS device dictates the required thermal impedance for the application. Knowing this, the selection of an appropriate heatsink to maintain the junction temperature below the maximum specified by the TMOS manufacture for operation can be made. The required overall thermal impedance is:

$$TR_{JA} = (T_{J(max)} - T_{A(max)})/P_{D(max)}$$

(16)

Where  $T_{J(max)}$ , the maximum allowable junction temperature, is found on the TMOS data sheet and  $T_{A(max)}$ , the maximum ambient temperature, is dictated by the application itself.

6. The thermal resistance, TRJA, represents the maximum overall or total thermal resistance, from junction to the surrounding ambient, allowable to insure the TMOS manufactures maximum junction temperature will not be exceeded. In general, this overall thermal resistance can be considered as being made up of several separate minor thermal resistance interfaces comprised of TRJC, TRCS and TRSA such that:

$$TR_{JA} = TR_{JC} + TR_{CS} + TR_{SA}$$

(17)

Where TR<sub>JC</sub>, TR<sub>CS</sub> and TR<sub>SA</sub> represent the junction-tocase, case-to-heatsink and heatsink-to-ambient thermal resistances respectively. TR<sub>CS</sub> and TR<sub>SA</sub> are the only parameters the device user can influence. The case-to-heatsink thermal resistance,  $TR_{CS}$ , is material dependent and can be expressed as:

$$TR_{CS} = \rho \times t/A \tag{18}$$

Where " $\rho$ " is the thermal resistivity of the heatsink material (expressed in °C/Watt/Unit Thickness), "t" is the thickness of heatsink material, and "A" is the contact area of the case–to–heatsink. Heatsink manufactures specify the value of TR<sub>CS</sub> for standard heatsinks. For nonstandard heatsinks, the user is required to calculate TR<sub>CS</sub> using some form of the basic Equation 18.

The required heatsink–to–ambient thermal resistance, TR<sub>SA</sub>, can easily be calculated once the terms of Equation 17 are known. Substituting TR<sub>JA</sub> of Equation 16 into Equation 17 and solving for TR<sub>SA</sub> produces:

$$TR_{SA} = (T_{J(max)} - T_{A(max)})/P_{D(max)} - (TR_{JC} + TR_{CS})$$

(19)

Consulting the heatsink manufactures catalog will provide TR<sub>CS</sub> information for various heatsinks under various mounting conditions so as to allow easy calculation of TR<sub>SA</sub> in units of °C/W (or when multiplied by the power dissipation produces the heatsink mounting surface temperature rise). Furthermore, heatsink manufactures typically specify for various heatsinks, heatsink efficiency in the form of mounting surface temperature rise above the ambient conditions for various power dissipation levels. The user should insure that the heatsink selected will provide a surface temperature rise somewhat less than the maximum capability of the heatsink so that the device junction temperature will not be exceeded. The user should consult the heatsink manufacturers catalog for this information.

7. Set the value of  $V_{DS(min)}$  to something greater than the normal operating drain to source voltage,  $V_{DS(norm)}$ , the TMOS device will experience as calculated in Step 3 above (Equation 14). From a practical standpoint, a value two or three times  $V_{DS(norm)}$  expected under normal operation will prove to be a good starting point for  $V_{DS(min)}$ .

8. Select a value of R<sub>T</sub> less than 1.0 M $\hat{\Omega}$  for minimal timing error whose value is compatible with R<sub>X</sub> (R<sub>X</sub> will be selected in Step 9 below). A recommended starting value to use for R<sub>T</sub> would be 470 k. The consideration here is that the input impedance of the threshold comparators are approximately 10 M $\Omega$  and if R<sub>T</sub> values greater than 1.0 M $\Omega$  are used, significant timing errors may be experienced as a result of input bias current variations of the threshold comparators.

9. Select a value of R<sub>X</sub> which is compatible with R<sub>T</sub>. The value of R<sub>X</sub> should be between 50 k and 100 k. Recall in Equation 5 that V<sub>DS</sub>(min) was determined by the combined selection of R<sub>X</sub> and R<sub>T</sub>. Low values of R<sub>X</sub> will give large values for K (K = 4.0  $\mu$ A/V<sup>2</sup> for R<sub>X</sub> = 50 k) causing I<sub>SQ</sub> to be very sensitive to V<sub>DS</sub> variations (see Equation 1). This is desirable if a minimum V<sub>DS</sub> trip point is needed in the 1.0 V range since small V<sub>DS</sub> values will generate measurable currents. However, at high V<sub>DS</sub> values, TMOS device currents become excessively large and the current squaring function begins to deviate slightly from the predicted value due to high level injection effects occurring in the output PNP of the current squaring circuit. These effects can be seen when I<sub>SQ</sub> exceeds several hundred microamps. See Figure 22 for graphical aid in the selection of R<sub>T</sub> and R<sub>X</sub>.

10. Calculate the shorted load average power dissipation for the application using Equations 8 and 9. This involves determining the peak shorted load power dissipation of the TMOS device and gate duty cycle. The duty cycle is based on  $V_{DS}(min)$ , the value of  $V_{DS}$  under shorted conditions (i.e.  $V_{S}(max)$ ).

11. The calculated shorted load average power dissipation of Step 10 should be less than the maximum power dissipation under *normal* operating conditions calculated in Step 4. If this is not the case, there are two options.

**Option one** is to reduce the thermal resistance of the TMOS device heatsink, in other words, use a larger or better heatsink. This though, is not always practical to do particularly if restricted by size.

**Option two** is to set  $V_{DS(min)}$  to the lowest practical value. If for instance  $V_{DS(min)}$  is set to 4.0 V when only 2.0 V are needed, the short circuit duty cycle will be over twice as large, resulting in double the TMOS device power dissipated. Keeping  $V_{DS(min)}$  to a minimum, reduces the shorted load average power.

12. Choose a value of C<sub>T</sub>. The value of C<sub>T</sub> can be determined either by trial and error or by characterizing the V<sub>DS</sub> waveform for the load and selecting a capacitor value that generates a minimum fault time curve (see Equation 4) that encompasses the V<sub>DS</sub> versus time waveform. The value of C<sub>T</sub> has *no* effect on the duty cycle itself as was pointed out earlier. See Figure 23 for a graphical selection of C<sub>T</sub>.

#### Inductive Loads

The TMOS device is turned off by pulling the gate to near ground potential. Turning off an inductive load will cause the source of the TMOS device to go below ground due to flyback voltage to the point where the TMOS device may become biased on again allowing the inductive energy to be dissipated through the load. An internal 14 V zener diode clamp from the gate to source pin limits how far the source pin can be pulled below ground. For high inductive loads, it may be necessary to have an external 10 k current limiting resistor in series with the source pin to limit the clamp current in the event the source pin is pulled more than 14 V below ground.

### **Transient Faults**

The MC33091A is not able to withstand automotive voltage transients directly. By correctly sizing resistor R<sub>S</sub> and capacitor C<sub>S</sub>, the MC33091A can withstand load dump and other automotive type transients. The V<sub>CC</sub> voltage is clamped at approximately 30 V through the use of an internal zener diode.

Under reverse battery conditions, the load will be energized in reverse due to the parasitic body diode inherent in the TMOS device. Under this condition, the drain is grounded and the MC33091A clamps the gate at 0.7 V below the battery potential. This turns the TMOS device on in reverse and minimizes the voltage across the TMOS device resulting in minimal power dissipation. Neither the MC33091A nor the TMOS device will be damaged under such a condition. In addition, if the load can tolerate a reverse polarity, the load will not be damaged. Caution; some sensitive applications may not tolerate a reverse polarity load condition with reverse battery polarity.

There is no protection of the TMOS device during a reverse battery condition if the load itself is already shorted to ground. The MC33091A will not incur damage under this specialized reverse battery condition but the TMOS device may be damaged since there could be significant energy available from the battery to be dissipated in the TMOS device.

The MC33091A will withstand a maximum V<sub>CC</sub> voltage of 28 V and with the proper TMOS device used, the system can withstand a double battery condition.

Figure 36 depicts a method of protecting the FET from positive transient voltages in excess of the rated FET breakdown voltage. The zener voltage, in this case, should be less than the FET breakdown voltage. The diode, D, is necessary where reverse battery protection of the gate of the FET is required.

### EMI Concern

The gate capacitance and thus the size of the TMOS device used will determine the turn–on and turn–off times experienced. In a practical sense, smaller TMOS devices have smaller gate capacitances and give rise to higher slew rates. By way of example, the turn–on of an MPT50N06 TMOS device might be of the order of 80  $\mu$ s while that of an MPT8N10 might be 10  $\mu$ s (see Figure 25). The speed of turn–on or turn–off can be calculated by assuming the charge pump to supply approximately 100  $\mu$ A over the time the gate capacitance will transition a V<sub>GS</sub> voltage of 0 V to 10 V. In reality, the V<sub>GS</sub> voltage will be greater than 10 V, but the additional increase in TMOS drain current will be minimal for V<sub>GS</sub> voltages greater than 10 V.

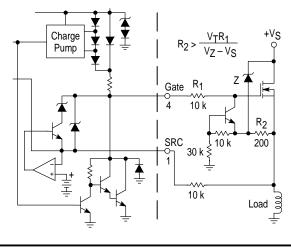

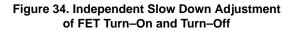

The charge pump current is sized so that turn-on time need not be of concern in all but the most critical of applications. Where limiting of EMI is of concern, the charge pump of the MC33091A may be slew rate limited by adding an external feedback capacitor from the gate-to-source of the TMOS device for slow down adjustment of both turn-on and turn-off times (see Figure 33). Figures 31 through 35 depict various methods of modifying the turn-on or turn-off times.

Figure 35 depicts a method of using only six external components to decrease turn-off time and clamp the flyback voltage associated with switching inductive loads. VGS(th) used in the critical component selection criteria refers to the gate-to-source threshold voltage of the FET used in the application.

Caution should be exercised when slowing down the switching transition time since doing so can greatly increase the average power dissipation of the TMOS device. The resulting increase in power dissipation should be taken into account when selecting the  $R_TC_T$  time constant values in order to protect the TMOS device from any overcurrent condition.

### Figure 31. Slow Down FET Turn-On

Figure 32. Slow Down FET Turn-Off

Figure 33. Slow Down Turn–On and Turn–Off of FET

Figure 35. Decreased FET Turn–Off Time with Inductive Flyback Voltage Clamp

Figure 36. Overvoltage Protection of FET

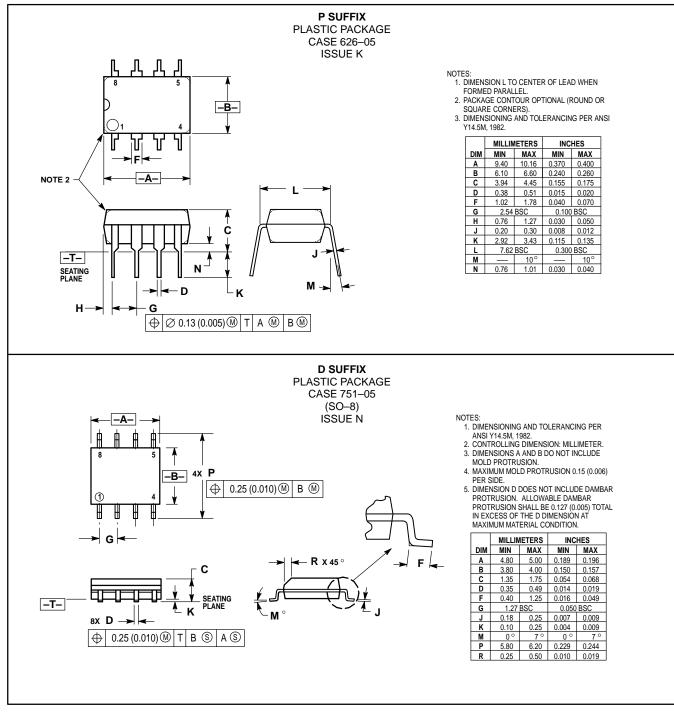

### OUTLINE DIMENSIONS

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola and Is officers engligent regarding the design or manufacture of the part. Motorola and Is officers of Motorola, Inc. Is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

MASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, I51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

$\Diamond$

MC33091A/D