### **General Description**

The MAX8632 integrates a synchronous-buck PWM controller to generate  $V_{DDQ}$ , a sourcing and sinking LDO linear regulator to generate  $V_{TT}$ , and a 10mA reference output buffer to generate  $V_{TTR}$ . The buck controller drives two external n-channel MOSFETs to generate output voltages down to 0.7V from a 2V to 28V input with output currents up to 15A. The LDO can sink or source up to 1.5A continuous and 3A peak current. Both the LDO output and the 10mA reference buffer output can be made to track the REFIN voltage. These features make the MAX8632 ideally suited for DDR memory applications in desktops, notebooks, and graphic cards.

The PWM controller in the MAX8632 utilizes Maxim's proprietary Quick-PWM<sup>™</sup> architecture with programmable switching frequencies of up to 600kHz. This control scheme handles wide input/output voltage ratios with ease and provides 100ns response to load transients while maintaining high efficiency and a relatively constant switching frequency. The MAX8632 offers fully programmable UVP/OVP and skip-mode options ideal in portable applications. Skip mode allows for improved efficiency at lighter loads.

The VTT and VTTR outputs track to within 1% of V<sub>REFIN</sub> / 2. The high bandwidth of this LDO regulator allows excellent transient response without the need for bulk capacitors, thus reducing cost and size.

The buck controller and LDO regulators are provided with independent current limits. Adjustable lossless foldback current limit for the buck regulator is achieved by monitoring the drain-to-source voltage drop of the low-side MOSFET. Additionally, overvoltage and undervoltage protection mechanisms are built in. Once the overcurrent condition is removed, the regulator is allowed to enter soft-start again. This helps minimize power dissipation during a short-circuit condition. The MAX8632 allows flexible sequencing and standby power management using the SHDN and STBY inputs, which support all DDR operating states.

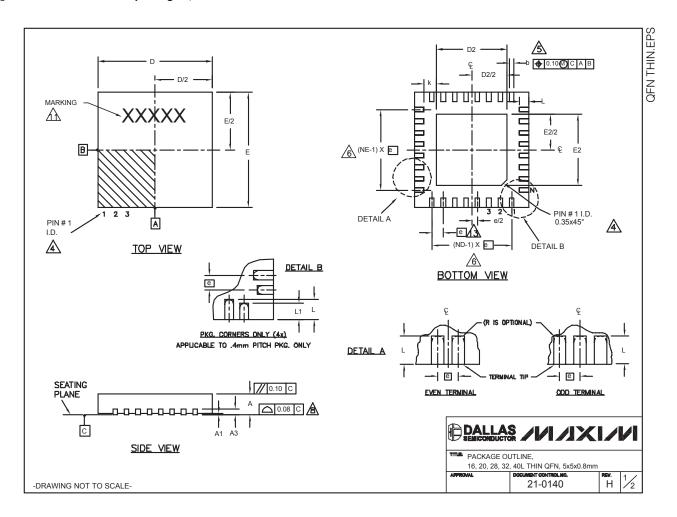

The MAX8632 is available in a small 5mm  $\times$  5mm, 28-pin thin QFN package.

### **Applications**

DDR I and DDR II Memory Power Supplies Desktop Computers Notebooks and Desknotes Graphic Cards Game Consoles RAID Networking

### **Buck Controller**

- Quick-PWM with 100ns Load-Step Response

- Up to 95% Efficiency

- 2V to 28V Input Voltage Range

- ◆ 1.8V/2.5V Fixed or 0.7V to 5.5V Adjustable Output

- ♦ Up to 600kHz Selectable Switching Frequency

- Programmable Current Limit with Foldback Capability

- ♦ 1.7ms Digital Soft-Start

- Independent Shutdown and Standby Controls

- Overvoltage-/Undervoltage-Protection Option

- Power-Good Window Comparator LDO Section

- Fully Integrated VTT and VTTR Capability

- ♦ VTT Has ±3A Sourcing/Sinking Capability

- Only 20µF Ceramic Capacitance Required for VTT

- ♦ VTT and VTTR Outputs Track VREFIN / 2

- ♦ All-Ceramic Output-Capacitor Designs

- 1.0V to 2.8V Input Voltage Range

- Power-Good Window Comparator

### **\_Ordering Information**

| PART                         | TEMP RANGE     | PIN-PACKAGE                  |  |  |  |  |

|------------------------------|----------------|------------------------------|--|--|--|--|

| MAX8632ETI+                  | -40°C to +85°C | 28 Thin QFN 5mm $\times$ 5mm |  |  |  |  |

| +Denotes lead-free packaging |                |                              |  |  |  |  |

### Pin Configuration

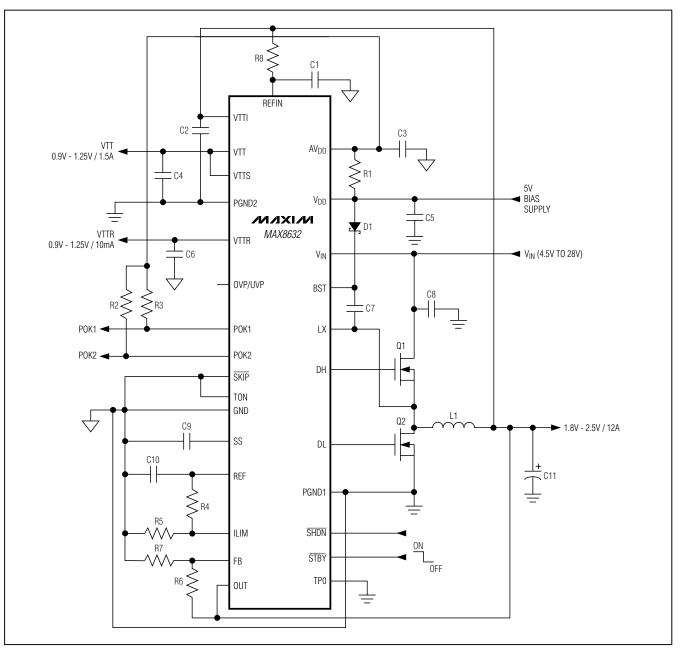

Typical Operating Circuit appears at end of data sheet.

### Quick-PWM is a trademark of Maxim Integrated Products, Inc.

### \_\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Features

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub> to GND                          | 0.3V to +30V                       |

|-------------------------------------------------|------------------------------------|

| V <sub>DD.</sub> AV <sub>DD</sub> , VTTI to GND | 0.3V to +6V                        |

| SHDN, REFIN to GND                              | 0.3V to +6V                        |

| SS, POK1, POK2, SKIP, ILIM, FB to GN            |                                    |

| STBY, TON, REF, UVP/OVP to GND                  | 0.3V to (AV <sub>DD</sub> + 0.3V)  |

| OUT, VTTR to GND                                | 0.3V to (AV <sub>DD</sub> + 0.3V)  |

| DL to PGND1                                     | 0.3V to (V <sub>DD</sub> + 0.3V)   |

| DH to LX                                        | 0.3V to $(V_{BST} + 0.3V)$         |

| LX to BST                                       | 6V to +0.3V                        |

| LX to GND                                       | 2V to +30V                         |

| VTT to GND                                      | 0.3V to (V <sub>VTTI</sub> + 0.3V) |

| VTTS to GND                               | 0.3V to (AV <sub>DD</sub> + 0.3V) |

|-------------------------------------------|-----------------------------------|

| PGND1, PGND2, TP0 to GND                  | 0.3V to +0.3V                     |

| REF Short Circuit to GND                  | Continuous                        |

| Continuous Power Dissipation ( $T_A = +7$ | Ό°C)                              |

| 28-Pin 5mm x 5mm Thin QFN (derate         | e 35.7mW/°C                       |

| above +70°C)                              | 2.86W                             |

| Operating Temperature Range               | 40°C to +85°C                     |

| Junction Temperature                      | +150°C                            |

| Storage Temperature Range                 |                                   |

| Lead Temperature (soldering, 10s)         | +300°C                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +15V, V_{DD} = AV_{DD} = V_{\overline{SHDN}} = \overline{STBY} = V_{BST} = V_{ILIM} = 5V, V_{OUT} = V_{REFIN} = V_{VTTI} = 2.5V, UVP/OVP = TP0 = FB = \overline{SKIP} = GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V_{VTTS} = V_{VTT}, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                                                     | SYMBOL                                                               | BOL CONDITIONS                                                |                                  | MIN   | ТҮР  | MAX   | UNITS |  |

|---------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-------|------|-------|-------|--|

| MAIN PWM CONTROLLER                                           |                                                                      |                                                               |                                  |       |      |       |       |  |

| Input Veltage Denge                                           | VIN                                                                  |                                                               |                                  | 2     |      | 28    | V     |  |

| Input Voltage Range                                           | V <sub>DD</sub> , AV <sub>DD</sub>                                   |                                                               |                                  | 4.5   |      | 5.5   | V     |  |

| Output Adjust Range                                           | Vout                                                                 |                                                               |                                  | 0.7   |      | 5.5   | V     |  |

|                                                               |                                                                      | FB = OUT                                                      |                                  | 0.693 | 0.7  | 0.707 |       |  |

| Output Voltage Accuracy<br>(Note 2)                           |                                                                      | FB = GND                                                      |                                  | 2.47  | 2.5  | 2.53  | V     |  |

| (Note 2)                                                      |                                                                      | $FB = V_{DD}$                                                 |                                  | 1.78  | 1.8  | 1.82  |       |  |

| Soft-Start Ramp Time                                          | tss                                                                  | Rising edge of SH                                             | IDN to full current limit        |       | 1.7  |       | ms    |  |

| On-Time                                                       | ton                                                                  | V <sub>IN</sub> = 15V,<br>V <sub>OUT</sub> = 1.5V<br>(Note 3) | TON = GND (600kHz)               | 170   | 194  | 219   | ns    |  |

|                                                               |                                                                      |                                                               | TON = REF (450kHz)               | 213   | 243  | 273   |       |  |

|                                                               |                                                                      |                                                               | TON = open (300kHz)              | 316   | 352  | 389   |       |  |

|                                                               |                                                                      |                                                               | $TON = AV_{DD} (200 \text{kHz})$ | 461   | 516  | 571   |       |  |

| Minimum Off-Time                                              | toff_min                                                             | (Note 3)                                                      | ÷                                | 200   | 300  | 450   | ns    |  |

| VIN Quiescent Supply Current                                  | l <sub>IN</sub>                                                      |                                                               |                                  |       | 25   | 40    | μA    |  |

| VIN Shutdown Supply Current                                   |                                                                      | SHDN = GND                                                    |                                  |       | 1    | 5     | μA    |  |

|                                                               |                                                                      | All on (PWM, VTT                                              | , and VTTR on)                   |       | 2.5  | 5     |       |  |

| AV <sub>DD</sub> Quiescent Supply Current                     | IAVDD                                                                | STBY = GND (only VTTR and PWM on)                             |                                  |       | 1    | 2     | mA    |  |

| AV <sub>DD</sub> + V <sub>DD</sub> Shutdown Supply<br>Current |                                                                      | SHDN = GND                                                    |                                  |       |      | 20    | μA    |  |

| AV <sub>DD</sub> Undervoltage-Lockout                         | AV <sub>DD</sub> Undervoltage-Lockout Rising edge of V <sub>IN</sub> |                                                               | N                                | 4.05  | 4.25 | 4.40  | V     |  |

| Threshold                                                     |                                                                      | Hysteresis                                                    |                                  |       | 50   |       | mV    |  |

| V <sub>DD</sub> Quiescent Supply Current                      | IVDD                                                                 | Set V <sub>FB</sub> = 0.8V                                    |                                  |       | 1    | 5     | μA    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +15V, V_{DD} = AV_{DD} = V_{\overline{SHDN}} = \overline{STBY} = V_{BST} = V_{ILIM} = 5V, V_{OUT} = V_{REFIN} = V_{VTTI} = 2.5V, UVP/OVP = TP0 = FB = \overline{SKIP} = GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V_{VTTS} = V_{VTT}, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                                                                  | SYMBOL | CONDITIONS                                                                           | MIN   | ТҮР  | MAX   | UNITS |

|----------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------|-------|------|-------|-------|

| REFERENCE                                                                  |        | ·                                                                                    |       |      |       |       |

| Reference Voltage                                                          | VREF   | $AV_{DD} = 4.5V$ to 5.5V; $I_{REF} = 0$                                              | 1.98  | 2    | 2.02  | V     |

| Reference Load Regulation                                                  |        | $I_{REF} = 0$ to $50\mu A$                                                           |       |      | 0.01  | V     |

|                                                                            |        | V <sub>REF</sub> rising                                                              |       | 1.93 |       | V     |

| REF Undervoltage Lockout                                                   |        | Hysteresis                                                                           |       | 300  |       | mV    |

| FAULT DETECTION                                                            |        |                                                                                      |       |      |       |       |

| OVP Trip Threshold<br>(Referred to Nominal V <sub>OUT</sub> )              |        | $UVP/OVP = AV_{DD}$                                                                  | 112   | 116  | 120   | %     |

| UVP Trip Threshold<br>(Referred to Nominal V <sub>OUT</sub> )              |        |                                                                                      | 65    | 70   | 75    | %     |

| POK1 Trip Threshold                                                        |        | Lower level, falling edge, 1% hysteresis                                             | 87    | 90   | 93    | 0/    |

| (Referred to Nominal V <sub>OUT</sub> )                                    |        | Upper level, rising edge, 1% hysteresis                                              | 107   | 110  | 113   | %     |

| POK2 Trip Threshold<br>(Referred to Nominal VvTTS                          |        | Lower level, falling edge, 1% hysteresis                                             | 87.5  | 90   | 92.5  | %     |

| and V <sub>VTTR</sub> )                                                    |        | Upper level, rising edge, 1% hysteresis                                              | 107.5 | 110  | 112.5 | 70    |

| POK2 Disable Threshold<br>(Measured at REFIN)                              |        | V <sub>REFIN</sub> rising (hysteresis = 75mV typ)                                    | 0.7   |      | 0.9   | V     |

| UVP Blanking Time                                                          |        | From rising edge of SHDN                                                             | 10    | 20   | 40    | ms    |

| OVP, UVP, POK_ Propagation<br>Delay                                        |        |                                                                                      |       | 10   |       | μs    |

| POK_ Output Low Voltage                                                    |        | I <sub>SINK</sub> = 4mA                                                              |       |      | 0.3   | V     |

| POK_ Leakage Current                                                       |        | V <sub>POK</sub> = 5.5V, V <sub>FB</sub> = 0.8V, V <sub>VTTS</sub> = 1.3V            |       |      | 1     | μA    |

| ILIM Adjustment Range                                                      | VILIM  |                                                                                      | 0.25  |      | 2.00  | V     |

| ILIM Input Leakage Current                                                 |        |                                                                                      |       |      | 0.1   | μA    |

| Current-Limit Threshold (Fixed)<br>PGND1 to LX                             |        |                                                                                      | 45    | 50   | 55    | mV    |

| Current-Limit Threshold<br>(Adjustable) PGND1 to LX                        |        | V <sub>ILIM</sub> = 2V                                                               | 170   | 200  | 235   | mV    |

| Current-Limit Threshold (Fixed,<br>Negative Direction) PGND1 to LX         |        | $\overline{\text{SKIP}} = \text{AV}_{\text{DD}}$                                     | -75   | -60  | -45   | mV    |

| Current-Limit Threshold<br>(Adjustable, Negative Direction)<br>PGND1 to LX |        | $\overline{\text{SKIP}} = \text{AV}_{\text{DD}}, \text{V}_{\text{ILIM}} = 2\text{V}$ |       | -250 |       | mV    |

| Zero-Crossing Detection<br>Threshold PGND1 to LX                           |        |                                                                                      |       | 3    |       | mV    |

| Thermal-Shutdown Threshold                                                 |        |                                                                                      |       | +160 |       | °C    |

| Thermal-Shutdown Hysteresis                                                |        |                                                                                      |       | 15   |       | °C    |

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = +15V, V_{DD} = AV_{DD} = V_{\overline{SHDN}} = \overline{STBY} = V_{BST} = V_{ILIM} = 5V, V_{OUT} = V_{REFIN} = V_{VTTI} = 2.5V, UVP/OVP = TP0 = FB = \overline{SKIP} = GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V_{VTTS} = V_{VTT}, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                      | SYMBOL | CONDITIONS              | MIN                       | ТҮР | MAX  | UNITS |

|----------------------------------------------------------------|--------|-------------------------|---------------------------|-----|------|-------|

| MOSFET DRIVERS                                                 |        | •                       | ·                         |     |      | •     |

| DH Gate-Driver On-Resistance                                   |        | $V_{BST} - V_{LX} = 5V$ |                           | 1   | 4    | Ω     |

| DL Gate-Driver On-Resistance in<br>High State                  |        |                         |                           | 1   | 4    | Ω     |

| DL Gate-Driver On-Resistance in Low State                      |        |                         |                           | 0.5 | 3    | Ω     |

| Dead Time (Additional to                                       |        | DH falling to DL rising |                           | 30  |      |       |

| Adaptive Delay)                                                |        | DL falling to DH rising |                           | 50  |      | ns    |

| INPUTS AND OUTPUTS                                             |        |                         |                           |     |      |       |

| Logic Input Threshold                                          |        | Rising edge             | 1.20                      | 1.7 | 2.20 | V     |

| (SHDN, STBY, SKIP)                                             |        | Hysteresis              |                           | 225 |      | mV    |

| Logic Input Current<br>(SHDN, STBY, SKIP)                      |        |                         | -1                        |     | +1   | μA    |

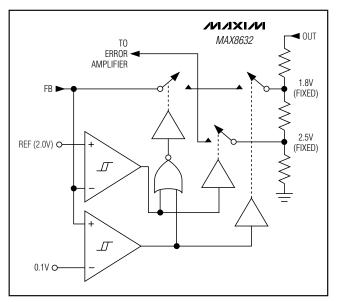

| Dual-Mode™ Input Logic                                         |        | Low (2.5V output)       |                           |     | 0.05 | V     |

| Levels (FB)                                                    |        | High (1.8V output)      | 2.1                       |     |      |       |

| Input Bias Current (FB)                                        |        |                         | -0.1                      |     | +0.1 | μA    |

|                                                                |        | High                    | AV <sub>DD</sub> -<br>0.4 |     |      |       |

| Four-Level Input Logic Levels<br>(TON, OVP/UVP)                |        | Floating                | 3.15                      |     | 3.85 | V     |

|                                                                |        | REF                     | 1.65                      |     | 2.35 |       |

|                                                                |        | Low                     |                           |     | 0.5  |       |

| Logic Input Current<br>(TON, OVP/UVP)                          |        |                         | -3                        |     | +3   | μA    |

|                                                                |        | FB = GND                | 90                        | 175 | 350  |       |

| OUT Input Resistance                                           |        | $FB = AV_{DD}$          | 70                        | 135 | 270  | kΩ    |

|                                                                |        | FB adjustable mode      | 400                       | 800 | 1600 | 1     |

| OUT Discharge-Mode<br>On-Resistance                            |        |                         |                           | 10  | 25   | Ω     |

| DL Turn-On Level During<br>Discharge Mode<br>(Measured at OUT) |        |                         | 0.01                      | 0.1 | 0.20 | V     |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = +15V, V_{DD} = AV_{DD} = V_{\overline{SHDN}} = \overline{STBY} = V_{BST} = V_{ILIM} = 5V, V_{OUT} = V_{REFIN} = V_{VTTI} = 2.5V, UVP/OVP = TP0 = FB = \overline{SKIP} = GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V_{VTTS} = V_{VTT}, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                   | SYMBOL          | CONDITIONS                                                                      | MIN  | TYP  | MAX  | UNITS |  |  |

|-------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------|------|------|------|-------|--|--|

| LINEAR REGULATORS (VTTR AND VTT)                            |                 |                                                                                 |      |      |      |       |  |  |

| VTTI Input Voltage Range                                    | Vvtti           | VTTI                                                                            |      |      | 2.8  | V     |  |  |

| VTTI Supply Current                                         | Ιντι            | I <sub>VTT</sub> = I <sub>VTTR</sub> = 0                                        |      | <0.1 | 1    | mA    |  |  |

| VTTI Shutdown Current                                       |                 | SHDN = GND                                                                      |      |      | 10   | μA    |  |  |

| REFIN Input Impedance                                       |                 | $V_{\text{REFIN}} = 2.5V$                                                       | 12   | 20   | 30   | kΩ    |  |  |

| REFIN Range                                                 | VREFIN          |                                                                                 | 1    |      | 2.8  | V     |  |  |

| VTT, VTTR UVLO Threshold<br>(Measured at OUT)               |                 |                                                                                 | 0.01 | 0.1  | 0.20 | V     |  |  |

| Soft-Start Charge Current                                   | I <sub>SS</sub> | $V_{SS} = 0$                                                                    |      | 4    |      | μA    |  |  |

| VTT Internal MOSFET High-Side<br>On-Resistance              |                 | I <sub>VTT</sub> = -100mA, V <sub>VTTI</sub> = 1.5V,<br>AV <sub>DD</sub> = 4.5V |      |      | 0.3  | Ω     |  |  |

| VTT Internal MOSFET Low-Side<br>On-Resistance               |                 | I <sub>VTT</sub> = 100mA, AV <sub>DD</sub> = 4.5V                               |      |      | 0.3  | Ω     |  |  |

| VTT Output Accuracy<br>(Referred to V <sub>REFIN</sub> / 2) |                 | VREFIN = 1.5V or 2.5V, IVTT = 1mA                                               | -1   |      | +1   | %     |  |  |

| VITT Load Degulation                                        |                 | $V_{\text{REFIN}} = 2.5V$ , $I_{\text{VTT}} = 0$ to $\pm 1.5A$                  |      | 1.3  |      | 0/    |  |  |

| VTT Load Regulation                                         |                 | $V_{\text{REFIN}} = 1.5V$ , $I_{\text{VTT}} = 0$ to $\pm 1A$                    |      | 1.3  |      | %     |  |  |

| VTT Current Limit                                           |                 | VTT = 0 or VTTI                                                                 | ±3   | ±5   | ±6.5 | А     |  |  |

| VTTS Input Current                                          | IVTTS           | V <sub>VTTS</sub> = 1.5V, VTT open                                              |      | 0.1  | 1    | μA    |  |  |

| VTTR Output Error<br>(Referred to V <sub>REFIN</sub> / 2)   |                 | $V_{\text{REFIN}} = 1.5V \text{ or } 2.5V, I_{\text{VTTR}} = 0$                 | -1   |      | +1   | %     |  |  |

| VTTR Current Limit                                          |                 | V <sub>VTTR</sub> = 0 or V <sub>VTTI</sub>                                      | ±18  | ±32  | ±50  | mA    |  |  |

| VTTR Bias Current V <sub>F</sub>                            |                 | V <sub>REFIN</sub> = V <sub>VTTI</sub> = 0                                      |      | 0.6  | 4    | μA    |  |  |

Note 1: Specifications to -40°C are guaranteed by design, not production tested.

**Note 2:** When the inductor is in continuous conduction, the output voltage has a DC regulation level higher than the error-comparator threshold by 50% of the ripple. In discontinuous conduction, the output voltage has a DC regulation level higher than the trip level by approximately 1.5% due to slope compensation.

**Note 3:** On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with LX = GND, V<sub>BST</sub> = 5V, and a 250pF capacitor connected from DH to LX. Actual in-circuit times may differ due to MOSFET switching speeds.

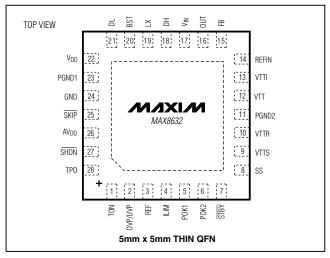

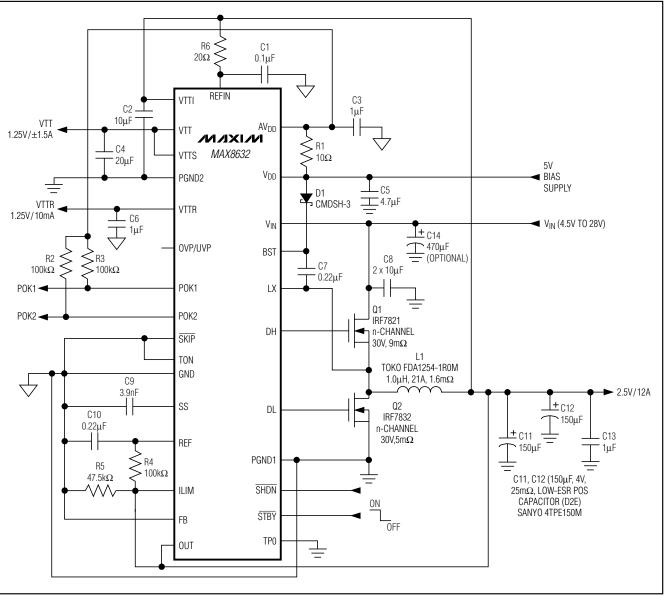

Typical Operating Characteristics

(V<sub>VIN</sub> = 12V, V<sub>OUT</sub> = 2.5V, TON = GND, SKIP = AV<sub>DD</sub>, circuit of Figure 8, T<sub>A</sub> = +25°C, unless otherwise noted.)

6

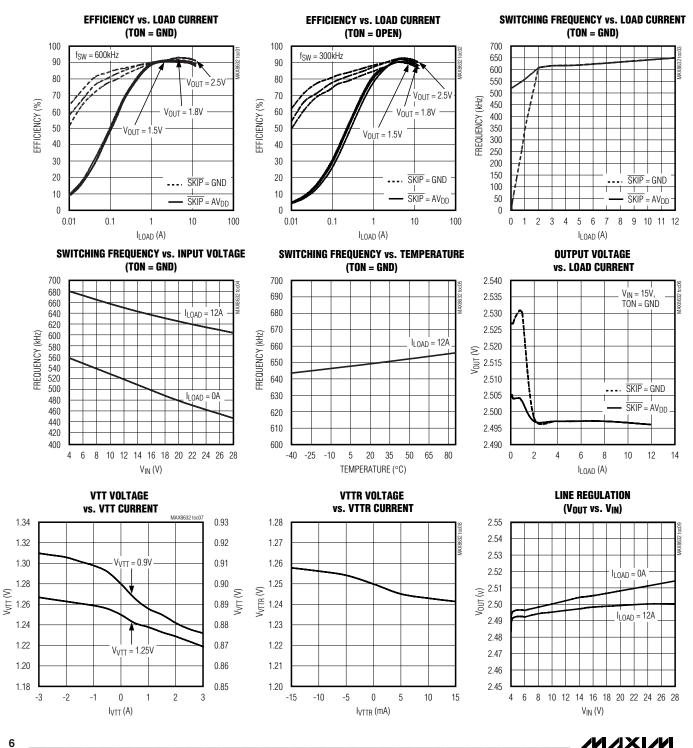

### **Typical Operating Characteristics (continued)**

(V<sub>VIN</sub> = 12V, V<sub>OUT</sub> = 2.5V, TON = GND, SKIP = AV<sub>DD</sub>, circuit of Figure 8, T<sub>A</sub> = +25°C, unless otherwise noted.)

**MAX8632**

### \_Typical Operating Characteristics (continued)

(V<sub>VIN</sub> = 12V, V<sub>OUT</sub> = 2.5V, TON = GND, SKIP = AV<sub>DD</sub>, circuit of Figure 8, T<sub>A</sub> = +25°C, unless otherwise noted.)

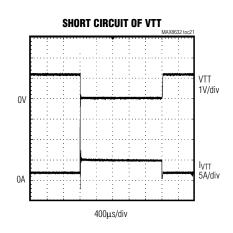

SHORT CIRCUIT AND

\_Pin Description

| PIN | NAME        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TON         | On-Time Selection-Control Input. This four-level logic input sets the nominal DH on-time. Connect to GND, REF, $AV_{DD}$ , or leave TON unconnected to select the following nominal switching frequencies:<br>TON = $AV_{DD}$ (200kHz)<br>TON = open (300kHz)<br>TON = REF (450kHz)<br>TON = GND (600kHz)                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | OVP/<br>UVP | Overvoltage-/Undervoltage-Protection Control Input. This four-level logic input enables or disables the overvoltage and/or undervoltage protection. The overvoltage limit is 116% of the nominal output voltage. The undervoltage limit is 70% of the nominal output voltage. Discharge mode is enabled when OVP is also enabled. Connect the OVP/UVP pin to the following pins for the desired function:<br>OVP/UVP = AV <sub>DD</sub> (Enable OVP and discharge mode, enable UVP.)<br>OVP/UVP = open (Enable OVP and discharge mode, disable UVP.)<br>OVP/UVP = REF (Disable OVP and discharge mode, enable UVP.)<br>OVP/UVP = GND (Disable OVP and discharge mode, disable UVP.) |

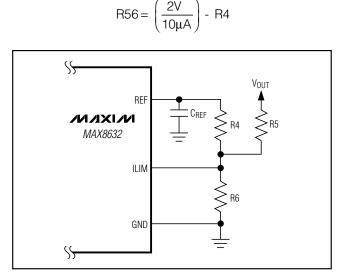

| 3   | REF         | +2.0V Reference Voltage Output. Bypass to GND with a $0.1\mu$ F (min) capacitor. REF can supply $50\mu$ A for external loads. Can be used for setting voltage for ILIM. REF turns off when SHDN is low and OUT < $0.1$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | ILIM        | Valley Current-Limit Threshold Adjustment for Buck Regulator. The current-limit threshold across PGND and LX is 0.1 times the voltage at ILIM. Connect ILIM to a resistive divider, typically from REF to GND, to set the current-limit threshold between 25mV and 200mV. This corresponds to a 0.25V to 2V range at ILIM. Connect ILIM to AV <sub>DD</sub> to select the 50mV default current-limit threshold. See the <i>Setting the Current Limit (Buck)</i> section.                                                                                                                                                                                                            |

| 5   | POK1        | Buck Power-Good Open-Drain Output. POK1 is low when the buck output voltage is more than 10% above or below the normal regulation point or during soft-start. POK1 is high impedance when the output is in regulation and the soft-start circuit has terminated. POK1 is low in shutdown.                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | POK2        | LDO Power-Good Open-Drain Output. In normal mode, POK2 is low when either VTTR or VTTS is more than 10% above or below the normal regulation point, which is typically REFIN / 2. In standby mode, POK2 responds only to the VTTR input. POK2 is low in shutdown, and when V <sub>REFIN</sub> is less than 0.8V.                                                                                                                                                                                                                                                                                                                                                                    |

| 7   | STBY        | Standby. Connect to GND for low-quiescent mode where the VTT output is open circuit. POK2 takes input from only VTTR in this mode. PWM output can be on or off, depending on the state of SHDN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8   | SS          | Soft-Start Control for VTT. Connect a capacitor (C9 in the Typical Applications Circuit of Figure 8) from SS to ground. Leave SS open to disable soft-start. SS discharges to ground when VTT is off. See the <i>POR, UVLO, and Soft-Start</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9   | VTTS        | Sensing Pin for Termination Supply Output. Normally connected to VTT pin to allow accurate regulation to half the REFIN voltage. Connected to a resistive divider from VTT to GND to regulate VTT to higher than half the REFIN voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10  | VTTR        | Termination Reference Voltage. VTTR tracks V <sub>REFIN</sub> / 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## **Pin Description (continued)**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 11  | PGND2            | Power Ground for VTT and VTTR. Connect PGND2 externally to the underside of the exposed pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 12  | VTT              | Termination Power-Supply Output. Connect VTT to VTTS to regulate to V <sub>REFIN</sub> / 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 13  | VTTI             | Power-Supply Input Voltage for VTT and VTTR. Normally connected to the output of the buck regulator for DDR application.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 14  | REFIN            | External Reference Input. This is used to regulate the VTT and VTTR outputs to VREFIN / 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 15  | FB               | Feedback Input for Buck Output. Connect to AV <sub>DD</sub> for a +1.8V fixed output or to GND for a +2.5V fixed output. For an adjustable output (0.7V to 5.5V), connect FB to a resistive divider from the output voltage. FB regulates to +0.7V.                                                                                                                                                                                                                                                                                                  |  |  |

| 16  | OUT              | Output-Voltage Sense Connection. Connect to the positive terminal of the buck output filter capacitor. OUT senses the output voltage to determine the on-time for the high-side switching MOSFET (Q1 in the Typical Applications Circuit of Figure 8). OUT also serves as the buck output's feedback input in fixed-output modes. When discharge mode is enabled by OVP/UVP, the output capacitor is discharged through an internal $10\Omega$ resistor connected between OUT and GND. OUT also acts as the input to the VTT and VTTR UVLO detector. |  |  |

| 17  | V <sub>IN</sub>  | Input-Voltage Sense Connection. Connect to input power source. V <sub>IN</sub> is used only to set the PWM's on-<br>time one-shot timer. IN voltage range is from 2V to 28V.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 18  | DH               | High-Side Gate-Driver Output. Swings from LX to BST. DH is low when in shutdown or UVLO.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 19  | LX               | External Inductor Connection. Connect LX to the input side of the inductor. LX is used for both current limit and the return supply of the DH driver.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 20  | BST              | Boost Flying-Capacitor Connection. Connect to an external capacitor and diode according to the <i>Typical Applications Circuit</i> (Figure 8). See the <i>Boost-Supply Diode and Capacitor Selection</i> section.                                                                                                                                                                                                                                                                                                                                    |  |  |

| 21  | DL               | Synchronous-Rectifier Gate-Driver Output. Swings from PGND to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 22  | V <sub>DD</sub>  | Supply Input for the DL Gate Drive. Connect to the +4.5V to +5.5V system supply voltage. Bypass to PGND1 with a $1\mu$ F (min) ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 23  | PGND1            | Power Ground for Buck Controller. Connect PGND1 externally to the underside of the exposed pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 24  | GND              | Analog Ground for Both Buck and LDO. Connect GND externally to the underside of the exposed pad                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 25  | SKIP             | Pulse-Skipping Control Input. Connect to AV <sub>DD</sub> for low-noise, forced-PWM mode. Connect to GND to enable pulse-skipping operation.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 26  | AV <sub>DD</sub> | Analog Supply Input for Both Buck and LDO. Connect to the $\pm 4.5$ V to $\pm 5.5$ V system supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 27  | SHDN             | Shutdown Control Input. Use to control buck output. A rising edge on SHDN clears the overvoltage-<br>and undervoltage-protection fault latches (see Tables 2 and 3). Connect to AV <sub>DD</sub> for normal operation.                                                                                                                                                                                                                                                                                                                               |  |  |

| 28  | TP0              | This is a test pin. Must connect to GND externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|     | EP               | Exposed pad. The exposed pad must be star-connected to GND and PGND2. See <i>Special Layout Considerations for LDO Section</i> for more details.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

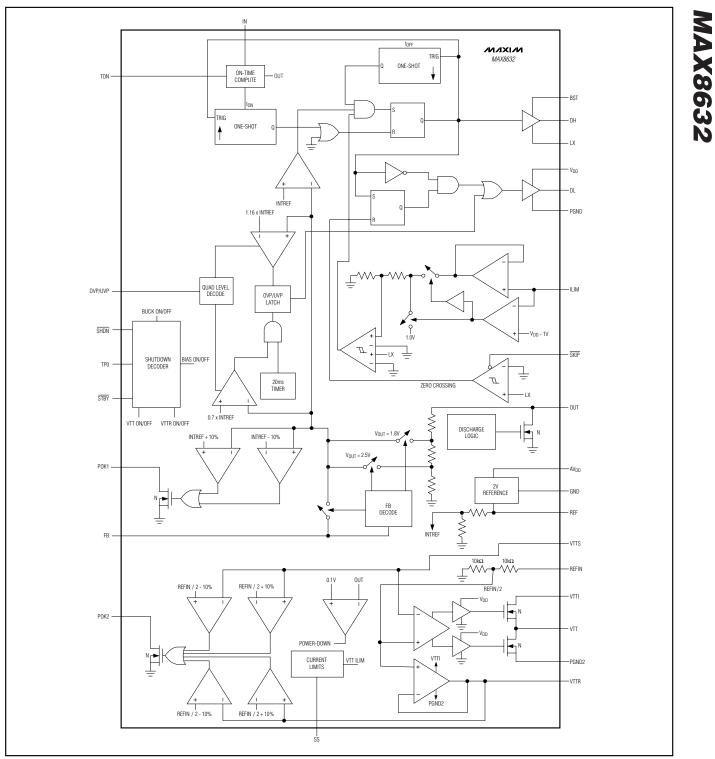

Figure 1. Functional Diagram

### \_Detailed Description

The MAX8632 combines a synchronous-buck PWM controller, an LDO linear regulator, and a 10mA reference output buffer. The buck controller drives two external n-channel MOSFETs to deliver load currents up to 12A and generate voltages down to 0.7V from a +2V to +28V input. The LDO linear regulator can sink and source up to 1.5A continuous and 3A peak current with relatively fast response. These features make the MAX8632 ideally suited for DDR memory applications.

The MAX8632 buck regulator is equipped with a fixed switching frequency of up to 600kHz using Maxim's proprietary constant on-time Quick-PWM architecture. This control scheme handles wide input/output voltage ratios with ease, and provides 100ns "instant-on" response to load transients, while maintaining high efficiency with relatively constant switching frequency.

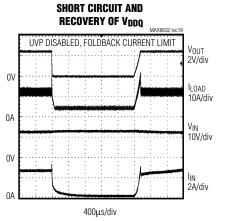

The buck controller, LDO, and a reference output buffer are provided with independent current limits. Lossless foldback current limit in the buck regulator is achieved by monitoring the drain-to-source voltage drop of the low-side FET. The ILIM input is used to adjust this current limit. Overvoltage protection, if selected, is achieved by latching the low-side synchronous FET on and the high-side FET off when the output voltage is over 116% of its set output. It also features an optional undervoltage protection by latching the MOSFET drivers to the OFF state during an overcurrent condition, when the output voltage is lower than 70% of the regulated output. This helps minimize power dissipation during a short-circuit condition.

The current limit in the LDO and buffered reference output buffer is  $\pm 5A$  and  $\pm 32mA$ , respectively, and neither have the over- or undervoltage protection. When the current limit in either output is reached, the output no longer regulates the voltage, but regulates the current to the value of the current limit.

### +5V Bias Supply (V<sub>DD</sub> and AV<sub>DD</sub>)

The MAX8632 requires an external +5V bias supply in addition to the input voltage (VIN). Keeping the bias supply external to the IC improves the efficiency and eliminates the cost associated with the +5V linear regulator that would otherwise be needed to supply the PWM circuit and the gate drivers. If stand-alone capability is needed, then the +5V supply can be generated with an external linear regulator such as the MAX1615. VDD, AVDD, and IN can be connected together if the input source is a fixed +4.5V to +5.5V supply.

$V_{\text{DD}}$  is the supply input for the buck regulator's MOSFET drivers, and AV\_{\text{DD}} supplies the power for the rest of

the IC. The current from the AV<sub>DD</sub> and V<sub>DD</sub> power supply must supply the current for the IC and the gate drive for the MOSFETs. This maximum current can be estimated as:

$I_{BIAS} = I_{VDD} + I_{AVDD} + f_{SW} \times (Q_{G1} + Q_{G2})$

where  $I_{VDD} + I_{AVDD}$  are the quiescent supply currents into  $V_{DD}$  and  $AV_{DD}$ ,  $Q_{G1}$  and  $Q_{G2}$  are the total gate charges of MOSFETs Q1 and Q2 (at  $V_{GS} = 5V$ ) in the Typical Applications Circuit of Figure 8, and f<sub>SW</sub> is the switching frequency.

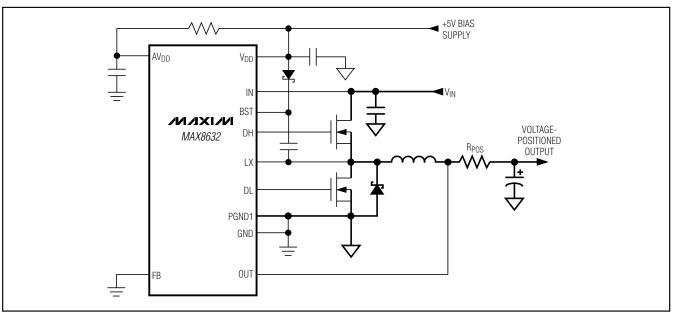

**Free-Running Constant-On-Time PWM** The Quick-PWM control architecture is a pseudo-fixedfrequency, constant on-time, current-mode regulator with voltage feed-forward (Figure 1). This architecture relies on the output filter capacitor's ESR to act as a current-sense resistor, so the output ripple voltage provides the PWM ramp signal. The control algorithm is simple: the high-side switch on-time is determined solely by a one-shot whose pulse width is inversely proportional to input voltage and directly proportional to the output voltage. Another one-shot sets a minimum off-time of 300ns (typ). The on-time one-shot is triggered if the error comparator is low, the low-side switch current is below the valley current-limit threshold, and the minimum off-time one-shot has timed out.

### **On-Time One-Shot (TON)**

The heart of the PWM core is the one-shot that sets the high-side switch on-time. This fast, low-jitter, adjustable one-shot includes circuitry that varies the on-time in response to input and output voltages. The high-side switch on-time is inversely proportional to the input voltage  $(V_{IN})$  and is proportional to the output voltage:

$$t_{ON} = K \times \frac{\left(V_{OUT} + I_{LOAD} \times R_{DS(ON)Q2}\right)}{V_{IN}}$$

where K (the switching period) is set by the TON input connection (Table 1) and R<sub>DS(ON)Q2</sub> is the on-resistance of the synchronous rectifier (Q2) in the *Typical Applications Circuit* (Figure 8). This algorithm results in a nearly constant switching frequency despite the lack of a fixed-frequency clock generator. The benefits of a constant switching frequency are twofold:

- 1) The frequency can be selected to avoid noise-sensitive regions such as the 455kHz IF band.

- 2) The inductor ripple-current operating point remains relatively constant, resulting in an easy design methodology and predictable output voltage ripple.

The on-time one-shot has good accuracy at the operating points specified in the *Electrical Characteristics* table (approximately  $\pm 12.5\%$  at 600kHz and 450kHz, and  $\pm 10\%$  at 200kHz and 300kHz). On-times at operating points far removed from the conditions specified in the *Electrical Characteristics* table can vary over a wider range. For example, the 600kHz setting typically runs approximately 10% slower with inputs much greater than 5V due to the very short on-times required.

The constant on-time translates only roughly to a constant switching frequency. The on-times guaranteed in the *Electrical Characteristics* table are influenced by resistive losses and by switching delays in the highside MOSFET. Resistive losses, which include the inductor, both MOSFETs, the output capacitor's ESR, and any PC board copper losses in the output and ground, tend to raise the switching frequency as the load increases. The dead-time effect increases the effective on-time, reducing the switching frequency as one or both dead times are added to the effective ontime. The dead time occurs only in PWM mode ( $\overline{SKIP}$  = V<sub>DD</sub>) and during dynamic output-voltage transitions when the inductor current reverses at light or negative load currents. With reversed inductor current, the inductor's EMF causes LX to go high earlier than normal, extending the on-time by a period equal to the DH-rising dead time. For loads above the critical conduction point, where the dead-time effect is no longer a factor, the actual switching frequency is:

$$f_{SW} = \frac{V_{OUT} + V_{DROP1}}{t_{ON}(V_{IN} + V_{DROP2})}$$

where  $V_{DROP1}$  is the sum of the parasitic voltage drops in the inductor discharge path, including the synchronous rectifier, the inductor, and any PC board resistances;  $V_{DROP2}$  is the sum of the resistances in the charging path, including the high-side switch (Q1 in the Typical Applications Circuit of Figure 8), the inductor, and any PC board resistances, and ton is the one-shot on-time (see the *On-Time One-Shot (TON)* section.

### Automatic Pulse-Skipping Mode (SKIP = GND)

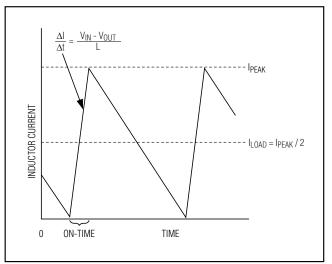

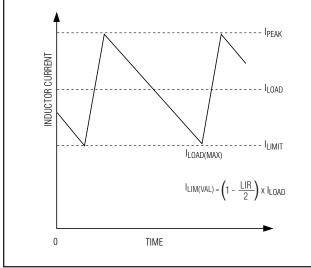

In skip mode ( $\overline{\text{SKIP}}$  = GND), an inherent automatic switchover to PFM takes place at light loads (Figure 2). This switchover is affected by a comparator that truncates the low-side switch on-time at the inductor current's zero crossing. The zero-crossing comparator differentially senses the inductor current across the synchronous-rectifier MOSFET (Q2 in the Typical Applications Circuit of Figure 8). Once VPGND - VLX drops below 5% of the current-limit threshold (2.5mV

M/X/M

for the default 50mV current-limit threshold), the comparator forces DL low (Figure 1). This mechanism causes the threshold between pulse-skipping PFM and nonskipping PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation (also known as the critical conduction point). The load-current level at which PFM/PWM crossover occurs, ILOAD(SKIP), is equal to half the peak-to-peak ripple current, which is a function of the inductor value (Figure 2). This threshold is relatively constant, with only a minor dependence on the input voltage (VIN):

$$I_{\text{LOAD(SKIP)}} = \left(\frac{V_{\text{OUT}} \times K}{2L}\right) \left(\frac{V_{\text{IN}} - V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

where K is the on-time scale factor (see Table 1). For example, in the Typical Applications Circuit of Figure 8 (K = 1.7 $\mu$ s, V<sub>OUT</sub> = 2.5V, V<sub>IN</sub> = 12V, and L = 1 $\mu$ H), the pulse-skipping switchover occurs at:

$$\left(\frac{2.5V \times 1.7\mu s}{2 \times 1\mu H}\right)\left(\frac{12V - 2.5V}{12V}\right) = 1.68A$$

The crossover point occurs at an even lower value if a swinging (soft-saturation) inductor is used. The switching waveforms can appear noisy and asynchronous when light loading causes pulse-skipping operation, but this is a normal operating condition that results in high lightload efficiency. Trade-offs in PFM noise vs. light-load efficiency are made by varying the inductor value. Generally, low inductor values produce a broader efficiency vs. load curve, while higher values result in higher full-load efficiency (assuming that the coil resistance

### **Table 1. Approximate K-Factor Errors**

| TON SETTING                      | TYPICAL<br>K-FACTOR<br>(μs) | K-FACTOR<br>ERROR<br>(%) | MINIMUM V <sub>IN</sub> AT<br>V <sub>OUT</sub> = 2.5V<br>(h = 1.5; SEE THE<br><i>DROPOUT</i><br><i>PERFORMANCE</i><br>( <i>BUCK</i> ) SECTION) |

|----------------------------------|-----------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 200<br>(TON = AV <sub>DD</sub> ) | 5.0                         | ±10                      | 3.15                                                                                                                                           |

| 300<br>(TON = open)              | 3.3                         | ±10                      | 3.47                                                                                                                                           |

| 450<br>(TON = REF)               | 2.2                         | ±12.5                    | 4.13                                                                                                                                           |

| 600<br>(TON = GND)               | 1.7                         | ±12.5                    | 5.61                                                                                                                                           |

remains fixed) and less output voltage ripple. Penalties for using higher inductor values include larger physical size and degraded load-transient response, especially at low input-voltage levels.

DC output accuracy specifications refer to the threshold of the error comparator. When the inductor is in continuous conduction, the MAX8632 regulates the valley of the output ripple, so the actual DC output voltage is higher than the trip level by 50% of the output ripple voltage. In discontinuous conduction (SKIP = GND and I<sub>LOAD</sub> < I<sub>LOAD</sub>(SKIP)), the output voltage has a DC regulation level higher than the error-comparator threshold by approximately 1.5% due to slope compensation.

### Forced-PWM Mode (SKIP = AVDD)

The low-noise forced-PWM mode ( $\overline{SKIP} = AV_{DD}$ ) disables the zero-crossing comparator, which controls the low-side switch on-time. This forces the low-side gate-drive waveform to constantly be the complement of the high-side gate-drive waveform, so the inductor current reverses at light loads while DH maintains a duty factor of V<sub>OUT</sub> / V<sub>IN</sub>. Forced-PWM mode keeps the switching frequency fairly constant. However, forced-PWM operation comes at a cost where the no-load V<sub>DD</sub> bias current remains between 2mA and 20mA due to the external MOSFET's gate charge and switching frequency. Forced-PWM mode is most useful for reducing audio frequency noise, improving load-transient response, and providing sink-current capability for dynamic output-voltage adjustment.

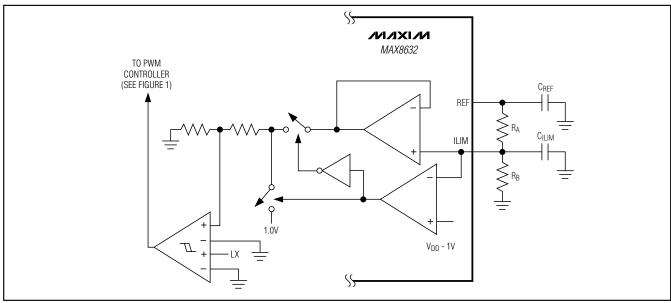

### Current-Limit Buck Regulator (ILIM) Valley Current Limit

The current-limit circuit for the buck regulator portion of the MAX8632 employs a unique "valley" current-sensing algorithm that senses the voltage drop across LX and PGND1 and uses the on-resistance of the rectifying MOSFET (Q2 in the Typical Applications Circuit of Figure 8) as the current-sensing element. If the magnitude of the current-sense signal is above the valley current-limit threshold, the PWM controller is not allowed to initiate a new cycle (Figure 4). With valley current-limit sensing, the actual peak current is greater than the valley current-limit threshold by an amount equal to the inductor current ripple. Therefore, the exact current-limit characteristic and maximum load capability are a function of the current-sense resistance, inductor value, and input voltage. When combined with the undervoltageprotection circuit, this current-limit method is effective in almost every circumstance.

In forced-PWM mode, the MAX8632 also implements a negative current limit to prevent excessive reverse inductor currents when the buck regulator output is sinking current. The negative current-limit threshold is set to approximately 120% of the positive current limit and tracks the positive current limit when  $V_{\rm ILIM}$  is adjusted. The current-limit threshold is adjusted with an external resistor-divider at ILIM. A 2µA to 20µA divider current is recommended for accuracy and noise immunity.

The current-limit threshold adjustment range is from 25mV to 200mV. In the adjustable mode, the current-limit threshold voltage (from PGND1 to LX) is precisely 1/10th the voltage seen at ILIM. The threshold defaults to 50mV when ILIM is connected to AV<sub>DD</sub>. The logic threshold for switchover to the 50mV default value is approximately AV<sub>DD</sub> - 1V.

Carefully observe the PC board layout guidelines to ensure that noise and DC errors do not corrupt the differential current-sense signals seen between LX and GND.

### POR, UVLO, and Soft-Start

Internal power-on reset (POR) occurs when AV<sub>DD</sub> rises above approximately 2V, resetting the fault latch and the soft-start counter, powering up the reference, and preparing the buck regulator for operation. Until AV<sub>DD</sub> reaches 4.25V (typ), AV<sub>DD</sub> undervoltage-lockout

Figure 2. Pulse-Skipping/Discontinuous Crossover Point

M/IXI/M

Figure 3. Adjustable Current-Limit Threshold

Figure 4. Valley Current-Limit Threshold

(UVLO) circuitry inhibits switching. The controller inhibits switching by pulling DH low and holding DL low when OVP and shutdown discharge are disabled (OVP/UVP = REF or GND) or forcing DL high when OVP and shutdown discharge are enabled (OVP/UVP = AV<sub>DD</sub> or OPEN). See Table 3 for a detailed truth table for OVP/UVP and shutdown settings. When AV<sub>DD</sub> rises above 4.25V, the controller activates the buck regulator and initializes the internal soft-start. The buck regulator's internal soft-start allows a gradual increase of the current-limit level during startup to reduce the input surge currents. The MAX8632 divides the soft-start period into five phases. During the first phase, the controller limits the current limit to only 20% of the full current limit. If the output does not reach regulation within 425µs, soft-start enters the second phase, and the current limit is increased by another 20%. This process repeats until the maximum current limit is reached, after 1.7ms, or when the output reaches the nominal regulation voltage, whichever occurs first. Adding a capacitor in parallel with the external ILIM resistors creates a continuously adjustable analog soft-start function for the buck regulator's output.

Soft-start in the LDO section can be realized by connecting a capacitor between the SS pin and ground. When VTT is turned off or placed in standby mode, or during thermal shutdown of the LDOs, the SS capacitor is discharged. When VTT is turned on or when the thermal limit is removed, an internal 4 $\mu$ A (typ) current charges the SS capacitor. The resulting ramp voltage on SS linearly increases the current-limit comparator threshold to the VTT output, until full current limit is attained when SS reaches approximately 1.6V. This lowering of the current limit during startup limits the initial inrush current peaks, particularly when driving capacitors. Choose the value of the SS capacitor appropriately to set the soft-start time window. Leave SS floating to disable the soft-start feature.

**MAX8632**

# **MAX8632**

# Integrated DDR Power-Supply Solution for Desktops, Notebooks, and Graphic Cards

Power-OK (POK1)

POK1 is an open-drain output for a window comparator that continuously monitors VOUT. POK1 is actively held low when SHDN is low and during the buck regulator output's soft-start. After the digital soft-start terminates, POK1 becomes high impedance as long as the output voltage is within ±10% of the nominal regulation voltage set by FB. When VOUT drops 10% below or rises 10% above the nominal regulation voltage, the MAX8632 pulls POK1 low. Any fault condition forces POK1 low until the fault latch is cleared by toggling SHDN or cycling AV<sub>DD</sub> power below 1V. For logic-level output voltages, connect an external pullup resistor between POK1 and AV<sub>DD</sub>. A 100k $\Omega$  resistor works well in most applications. Note that the POK1 window detector is completely independent of the overvoltage- and undervoltage-protection fault detectors and the state of VTTS and VTTR.

### **SHDN** and Output Discharge

The SHDN input corresponds to the buck regulator and places the buck regulator's portion of the IC in a low-power mode (see the *Electrical Characteristics* table). SHDN is also used to reset a fault signal such as an overvoltage or undervoltage fault.

When output discharge is enabled, (OVP/UVP = AV<sub>DD</sub> or open) and SHDN is pulled low, or if UVP is enabled (OVP/UVP = AV<sub>DD</sub>) and V<sub>OUT</sub> falls to 70% of its regulation set point, the MAX8632 discharges the buck regulator output (through the OUT input) through an internal 10 $\Omega$  switch to ground. While the output is discharging, DL is forced low and the PWM controller is disabled but the reference remains active to provide an accurate threshold. Once the output voltage drops below 0.1V, the MAX8632 shuts down the reference and DL remains low.

When output discharge is disabled (OVP/UVP = REF or GND), the controller does not actively discharge the buck output and the DL driver remains low. Under these conditions, the buck output discharge rate is determined

by the load current and its output capacitance. The buck regulator detects and latches the discharge-mode state set by the OVP/UVP setting on startup.

When OUT is discharging, both VTT and VTTR outputs remain alive and continue to track REFIN until OUT drops to 0.1V.

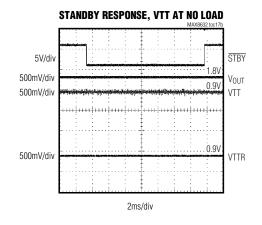

### STBY

The STBY input is an active-low input that is used to shut down only the VTT output. When STBY is low, VTT is high impedance.

### Power-OK (POK2)

POK2 is the open-drain output for a window comparator that continuously monitors the VTTS input and VTTR output. POK2 is pulled low when REFIN is less than 0.8V. POK2 is high impedance as long as the output voltage is within  $\pm 10\%$  of the nominal regulation voltage as set by REFIN. When V<sub>VTTS</sub> or V<sub>VTTR</sub> rises 10% above or 10% below its nominal regulation voltage, the MAX8632 pulls POK2 low. For logic-level output voltages, connect an external pullup resistor between POK2 and AV<sub>DD</sub>. A 100k $\Omega$  resistor works well in most applications.

### Current Limit (LDO for VTT and VTTR Buffer)

The VTT output is a linear regulator that regulates the input (VTTI) to half the V<sub>REFIN</sub> voltage. The feedback point for VTT is at the VTTS input (Figure 1). VTT is capable of sinking and sourcing at least 1.5A of continuous current and 3A peak current. The current limit for VTT and VTTR is typically  $\pm$ 5A and  $\pm$ 32mA, respectively. When the current limit for either output is reached, the outputs regulate the current, not the voltage.

### **Fault Protection**

The MAX8632 provides overvoltage/undervoltage fault protection in the buck controller. Select OVP/UVP to enable and disable fault protection as shown in Table 3. Once activated, the controller continuously monitors the output for undervoltage and overvoltage fault conditions.

| SHDN                | STBY BUCK OUTPUT (V <sub>DDQ</sub> ) |     | VTT                      | VTTR                     |

|---------------------|--------------------------------------|-----|--------------------------|--------------------------|

| AV <sub>DD</sub> *  | AV <sub>DD</sub> *                   | ON  | ON                       | ON                       |

| AV <sub>DD</sub> ** | GND**                                | ON  | OFF (high impedance)     | ON                       |

| GND***              | Х                                    | OFF | OFF (tracking 0.5 REFIN) | OFF (tracking 0.5 REFIN) |

\*For DDR application, this is referred as S0 state, where all outputs are on.

\*\*For DDR application, this is referred as S3 state, where V<sub>DDQ</sub> and VTTR are kept on, but VTT is turned off (high impedance).

\*\*\*For DDR application, this is referred as S4/S5 states, where all outputs are off. Discharge mode should be selected (OVP/UVP = AV<sub>DD</sub> or OPEN, see Table 3) to discharge the outputs.

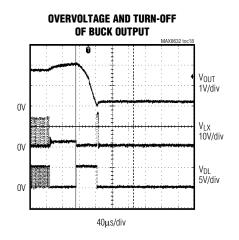

### Overvoltage Protection (OVP)

When the output voltage rises above 116% of the nominal regulation voltage and OVP is enabled (OVP/UVP = AV<sub>DD</sub> or open), the OVP circuit sets the fault latch, shuts down the PWM controller, and immediately pulls DH low and forces DL high. This turns on the synchronous-rectifier MOSFET (Q2 in the Typical Applications Circuit of Figure 8) with a 100% duty cycle, rapidly discharging the output capacitor and clamping the output to ground. Once the output reaches 0.1V, DL is switched off, preventing the possibility of a negative voltage on the output. Toggle SHDN or cycle AVDD below 1V to clear the fault latch and restart the controller. OVP is disabled when OVP/UVP is connected to REF or GND (see Table 3). OVP only applies to the buck output. The VTT and VTTR outputs do not have overvoltage protection.

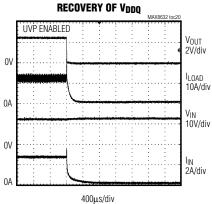

### Undervoltage Protection (UVP)

When the output voltage drops below 70% of its regulation voltage while UVP is enabled, the controller sets the fault latch and begins the discharge mode (see the SHDN and Output Discharge section). When the output voltage drops to 0.1V, the synchronous rectifier (Q2 in the *Typical Applications Circuit*) turns on and clamps the buck output to GND. UVP is ignored for at least 10ms (min) after startup or after a rising edge on SHDN. Toggle SHDN or cycle AV<sub>DD</sub> power below 1V to clear the fault latch and restart the controller. UVP is disabled when OVP/UVP is left open or connected to GND (see Table 3). UVP only applies to the buck output. The VTT and VTTR outputs do not have undervoltage protection.

### **Thermal Fault Protection**

The MAX8632 features two thermal-fault-protection circuits. One monitors the buck-regulator portion of the IC and the other monitors the linear regulator (VTT) and the reference buffer output (VTTR). When the junction temperature of the buck-regulator portion of the MAX8632 rises above +160°C, a thermal sensor activates the fault latch, pulls POK1 low, and shuts down the buck-controller output using discharge mode regardless of the OVP/UVP setting. Toggle SHDN or cycle AV<sub>DD</sub> below 1V to reactivate the controller after the junction temperature cools by 15°C. If the VTT and VTTR regulator portion of the IC has its die temperature rise above +160°C, then VTT and VTTR shut off, go high impedance, and restart after the die portion of the IC cools by 15°C. Both thermal faults are independent. For example, if the VTT output is overloaded to the point that it triggers its thermal fault, the buck regulator continues to function.

### Design Procedure

Firmly establish the input voltage range (V<sub>IN</sub>) and maximum load current ( $I_{LOAD}$ ) in the buck regulator before choosing a switching frequency and inductor operating point (ripple current ratio or LIR). The primary design trade-off lies in choosing a good switching frequency and inductor operating point, and the following four factors dictate the rest of the design:

Input Voltage Range. The maximum value (VIN(MAX)) must accommodate the worst-case voltage. The minimum value (VIN(MIN)) must account for the lowest voltage after drops due to connectors and fuses. If there is a choice, lower input voltages result in better efficiency.

| OVP/UVP          | DISCHARGE                                                            | UVP PROTECTION | OVP PROTECTION |

|------------------|----------------------------------------------------------------------|----------------|----------------|

| AV <sub>DD</sub> | Yes. Output is discharged through an internal $10\Omega$ resistance. | Enabled        | Enabled        |

| OPEN             | Yes. Output is discharged through an internal $10\Omega$ resistance. | Disabled       | Enabled        |

| REF              | No.<br>DL forced low when SHDN is low.                               | Enabled        | Disabled       |

| GND              | No.<br>DL forced low when SHDN is low.                               | Disabled       | Disabled       |

### **Table 3. OVP/UVP Fault Protection**

- Maximum Load Current. There are two values to consider. The peak load current (IPEAK) determines the instantaneous component stresses and filtering requirements and thus drives output capacitor selection, inductor saturation rating, and the design of the current-limit circuit. The continuous load current (ILOAD) determines the thermal stresses and thus drives the selection of input capacitors, MOSFETs, and other critical heat-contributing components.

- Switching Frequency. This choice determines the basic trade-off between size and efficiency. The optimal frequency is largely a function of maximum input voltage, due to MOSFET switching losses proportional to frequency and V<sub>IN</sub><sup>2</sup>. The optimum frequency is also a moving target due to rapid improvements in MOSFET technology that are making higher frequencies more practical.

- Inductor Operating Point. This choice provides tradeoffs: size vs. efficiency and transient response vs. output ripple. Low inductor values provide better transient response and smaller physical size but also result in lower efficiency and higher output ripple due to increased ripple currents. The minimum practical inductor value is one that causes the circuit to operate at the edge of critical conduction (where the inductor current just touches zero with every cycle at maximum load). Inductor values lower than this grant no further size-reduction benefit. The optimum operating point is usually found between 20% and 50% ripple current. When pulse skipping (SKIP = low at light loads), the inductor value also determines the load-current value at which PFM/PWM switchover occurs.

### Setting the Output Voltage (Buck)

### Preset Output Voltages

The MAX8632 dual-mode operation allows the selection of common voltages without requiring external components (Figure 5). Connect FB to GND for a fixed 2.5V output, to AV<sub>DD</sub> for a fixed 1.8V output, or connect FB directly to OUT for a fixed 0.7V output.

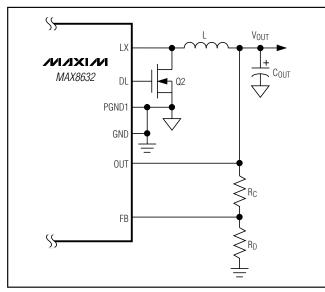

### Setting the Buck Regulator Output (VOUT) with a Resistive Voltage-Divider at FB

The buck-regulator output voltage can be adjusted from 0.7V to 5.5V using a resistive voltage-divider (Figure 6). The MAX8632 regulates FB to a fixed reference voltage (0.7V). The adjusted output voltage is:

$$V_{OUT} = V_{FB} \left(1 + \frac{R_C}{R_D}\right) + \frac{V_{RIPPLE}}{2}$$

where  $V_{\text{FB}}$  is 0.7V,  $R_{C}$  and  $R_{D}$  are shown in Figure 6, and  $V_{\text{RIPPLE}}$  is:

$V_{\text{RIPPLE}} = \text{LIR} \times I_{\text{LOAD}(\text{MAX})} \times R_{\text{ESR}}$

Setting the VTT and VTTR Voltages (LDO)

The termination power-supply output (VTT) can be set by two different methods. First, the VTT output can be connected directly to the VTTS input to force VTT to regulate to V<sub>REFIN</sub> / 2. Secondly, VTT can be forced to regulate higher than V<sub>REFIN</sub> / 2 by connecting a resistive divider from VTT to VTTS. The maximum value for VTT is V<sub>VTTI</sub> - V<sub>DROPOUT</sub> where V<sub>DROPOUT</sub> = I<sub>VTT</sub> × 0.3 $\Omega$  (max) at T<sub>A</sub> = +85°C.

The termination reference voltage (VTTR) tracks 0.5  $\ensuremath{\mathsf{VREFIN}}$

### Inductor Selection (Buck)

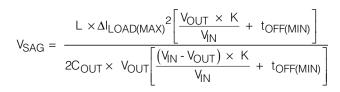

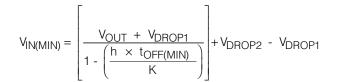

The switching frequency and inductor operating point determine the inductor value as follows: