Preliminary Product Overview, Rev. 2.0, May 2004

# VINETIC®

Voice and Internet Enhanced Telephony Interface Concept

PEB 3324 PEB 3322 PEB 3332 PEB 3320 PEB 3314 PEB 3394 PEB 3304 PEB 4264/-2 PEB 4364 PEB 4265/-2 PEB 4365 PEB 4266 PEB 4262 PEB 4268

Wireline Communications

Never stop thinking.

ABM<sup>®</sup>, ACE<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ASM<sup>®</sup>, ASP<sup>®</sup>, DigiTape<sup>®</sup>, DuSLIC<sup>®</sup>, EPIC<sup>®</sup>, ELIC<sup>®</sup>, FALC<sup>®</sup>, GEMINAX<sup>®</sup>, IDEC<sup>®</sup>, INCA<sup>®</sup>, IOM<sup>®</sup>, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>, ITAC<sup>®</sup>, IWE<sup>®</sup>, IWORX<sup>®</sup>, MUSAC<sup>®</sup>, MuSLIC<sup>®</sup>, OCTAT<sup>®</sup>, OptiPort<sup>®</sup>, POTSWIRE<sup>®</sup>, QUAT<sup>®</sup>, QuadFALC<sup>®</sup>, SCOUT<sup>®</sup>, SICAT<sup>®</sup>, SICOFI<sup>®</sup>, SIDEC<sup>®</sup>, SLICOFI<sup>®</sup>, SMINT<sup>®</sup>, SOCRATES<sup>®</sup>, VINETIC<sup>®</sup>, 10BaseV<sup>®</sup>, 10BaseVX<sup>®</sup> are registered trademarks of Infineon Technologies AG. 10BaseS<sup>™</sup>, EasyPort<sup>™</sup>, VDSLite<sup>™</sup> are trademarks of Infineon Technologies AG. Microsoft<sup>®</sup> is a registered trademark of Microsoft Corporation. Linux<sup>®</sup> is a registered trademark of Linus Torvalds.

The information in this document is subject to change without notice.

Edition 2004-05-11 Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 5/14/04. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## Preliminary Product Overview

| <b>Revision</b> H | listory:      | 2004-05-11                        | Rev. 2.0 |

|-------------------|---------------|-----------------------------------|----------|

| Previous Version: |               | none                              |          |

| Page              | Subjects (n   | ajor changes since last revision) |          |

|                   | VINETIC-20    | PE added                          |          |

|                   | Featurelist u | pdated                            |          |

|                   |               |                                   |          |

## Preface

This Preliminary Product Overview describes the Voice and Internet Enhanced Telephony Interface Concept (VINETIC<sup>®</sup>) chip set family. For more VINETIC<sup>®</sup> related documents, please see our webpage at http://www.infineon.com/vinetic.

To simplify matters, the following synonyms are used:

- Synonym used for all codec versions VINETIC<sup>®</sup>-4VIP, VINETIC<sup>®</sup>-2VIP, VINETIC<sup>®</sup>-x: VINETIC<sup>®</sup>-2CPE, VINETIC<sup>®</sup>-4C, VINETIC<sup>®</sup>-4M, VINETIC<sup>®</sup>-4S, VINETIC<sup>®</sup>-8S and VINETIC<sup>®</sup>-8M.

- Synonym used for 4-channel versions of the VINETIC<sup>®</sup> family. To VINETIC<sup>®</sup>-4x: simplify matters only the 4-channel versions are depicted in this document in most cases.

- SLIC: Synonym used for all SLIC versions SLIC-S/-S2, TSLIC-S, SLIC-E/-E2, TSLIC-E, SLIC-P, SLIC-LCP and SLIC-DC.

- Attention: The TSLIC-S (PEB 4364) and TSLIC-E (PEB 4365) chips are dual channel versions of the SLIC-S (PEB 4264) and SLIC-E (PEB 4265) with identical technical specifications for each channel. Therefore whenever SLIC-S or SLIC-E are mentioned in the specification, also TSLIC-S and TSLIC-E can be deployed.

#### **Organization of this Document**

This Preliminary Product Overview is divided into 11 chapters. It is organized as follows:

- Chapter 1, Family Overview A general description of the chip set, the key features, and some typical applications.

- Chapter 2, VINETIC<sup>®</sup> Host Interface Description Connection information including the different interface types.

- Chapter 3, Codec/SLIC Features (BORSCHT Functions) The main functions of the chip set are presented with functional block diagrams.

- Chapter 6, Operating Modes A brief description of the operating modes and the integrated test and diagnostic functions.

- Chapter 4, Signalprocessing Capabilities of the VINETIC<sup>®</sup> A short overview of DSP performance necessary for different algorithms.

- Chapter 5, Programming of the VINETIC<sup>®</sup> A general description of the *VINETIC<sup>®</sup>-x* command structure.

- Chapter 7, Firmware Architecture A general description of the VINETIC<sup>®</sup>-x software system

• Chapter 8, Electrical Characteristics

Parameters, symbols, and limit values are provided for the chip set.

- Chapter 9, Application Circuits External components are identified. Illustrations of balanced ringing, unbalanced ringing, and protection circuits are included.

- Chapter 10, Package Outlines Illustrations and dimensions of the package outlines.

- Chapter 11, Terminology List of abbreviations and descriptions of symbols.

- Chapter 12, Index

Attention: This document is a pre release version of the VINETIC<sup>®</sup> product overview.

#### **Related Documentation**

in preparation

| Table of Contents | I | ab | e | of | Со | nt | en | ts |

|-------------------|---|----|---|----|----|----|----|----|

|-------------------|---|----|---|----|----|----|----|----|

|                                                                      |                                                                                                                                                                                                                                                                                                                         | -                                      |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7            | Family OverviewPin Diagram VINETIC®-4xP-LQFP-176-2 Pin DiagramP-LBGA-176-3 Pin DiagramPG-LBGA-144 Pin Diagram (4-channel devices)PG-LBGA-144 Pin Diagram (2-channel devices)Logic Symbol VINETIC®-4xTypical Applications                                                                                                | 17<br>17<br>18<br>19<br>20<br>21       |

| <b>2</b><br>2.1                                                      | VINETIC <sup>®</sup> Host Interface Description                                                                                                                                                                                                                                                                         |                                        |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2<br>3.2.3           | Codec/SLIC Features (BORSCHT Functions)<br>BORSCHT functions<br>Advanced Integrated Test and Diagnostic Functions (AITDF)<br>Introduction<br>VINETIC <sup>®</sup> Line Testing<br>Board and Production Testing                                                                                                          | 28<br>29<br>29<br>29                   |

| 4                                                                    | Signalprocessing Capabilities of the VINETIC <sup>®</sup>                                                                                                                                                                                                                                                               | 31                                     |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.5<br>5.6 | Programming of the VINETIC®<br>Command/Data Structure in Downstream Direction<br>Command/Data Structure in Upstream Direction<br>First Command Word .<br>Second Command Word .<br>Second Command Word in Case of SOP, COP and IOP<br>Second Command Word in Case of EOP, EVT and VOP<br>Data Words .<br>Data Handling . | 33<br>35<br>36<br>36<br>36<br>37<br>37 |

| <b>6</b><br>6.1<br>6.2                                               | Operating Modes                                                                                                                                                                                                                                                                                                         | 39                                     |

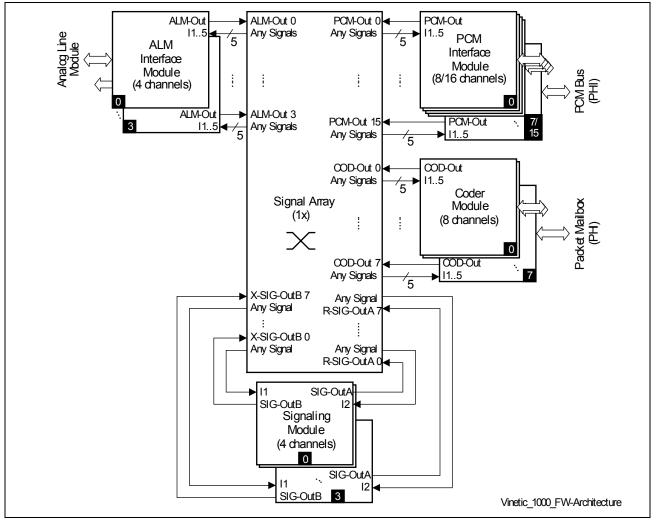

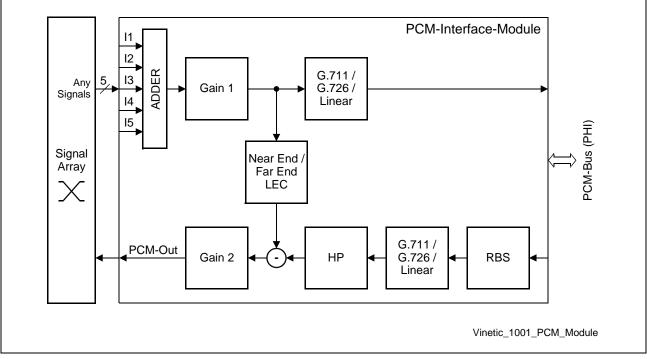

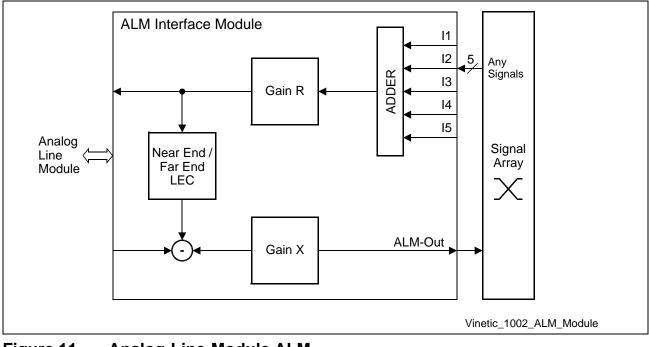

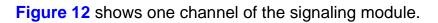

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                   | Firmware Architecture         Module Concept         PCM-Interface Module         Analog-Line-Module ALM         Signaling Module         Coder Module         Test Features                                                                                                                                            | 42<br>44<br>45<br>46<br>49             |

| <b>8</b><br>8.1                                                      | Electrical Characteristics                                                                                                                                                                                                                                                                                              |                                        |

#### **Table of Contents**

| 8.1.1<br>8.1.2<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8 | Power Consumption VINETIC®54Power-Up Sequence VINETIC®55Operating Range SLIC-S/-S257Operating Range SLIC-E/-E258Operating Range SLIC-P59Operating Range SLIC-DC60Operating Range SLIC-LCP61AC Transmission VINETIC®62DC Characteristics63 |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>9</b><br>9.1                                                 | Application Circuits       65         Internal Ringing (Balanced/Unbalanced)       65         Application Circuits for Internal Ringing       65                                                                                          |

| 9.1.1<br>9.1.2<br>9.1.3<br>9.2                                  | Application Circuits for Internal Ringing       65         Bill of Materials       68         Application Circuits for Internal Ringing with DC/DC       69         External Ringing       71                                             |

| 9.1.2<br>9.1.3                                                  | Bill of Materials       68         Application Circuits for Internal Ringing with DC/DC       69                                                                                                                                          |

| 9.1.2<br>9.1.3<br>9.2                                           | Bill of Materials68Application Circuits for Internal Ringing with DC/DC69External Ringing71                                                                                                                                               |

## **VINETIC**<sup>®</sup>

## List of Figures

| Figure 1<br>Figure 2<br>Figure 3<br>Figure 4<br>Figure 5<br>Figure 6<br>Figure 7<br>Figure 8<br>Figure 9 | Block Diagram VINETIC <sup>®</sup> -4x .<br>P-LQFP-176-2 Pin Diagram .<br>P-LBGA-176-3 Pin Diagram .<br>Logic Symbol VINETIC <sup>®</sup> -4x .<br>Residential Gateway / ATA / VoIP Router .<br>IAD serving POTS and ISDN (European Version) .<br>Cable Modem / Settop Box / SMTA / EMTA .<br>Next Generation Access Network Linecard .<br>Module Concept . | 17<br>18<br>21<br>22<br>23<br>24<br>25 |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Figure 10                                                                                                | PCM-Interface Module                                                                                                                                                                                                                                                                                                                                        | 44                                     |

| Figure 11                                                                                                | Analog-Line-Module ALM                                                                                                                                                                                                                                                                                                                                      | 45                                     |

| Figure 12                                                                                                | Signaling Module                                                                                                                                                                                                                                                                                                                                            |                                        |

| Figure 13                                                                                                | Coder Channel Module                                                                                                                                                                                                                                                                                                                                        |                                        |

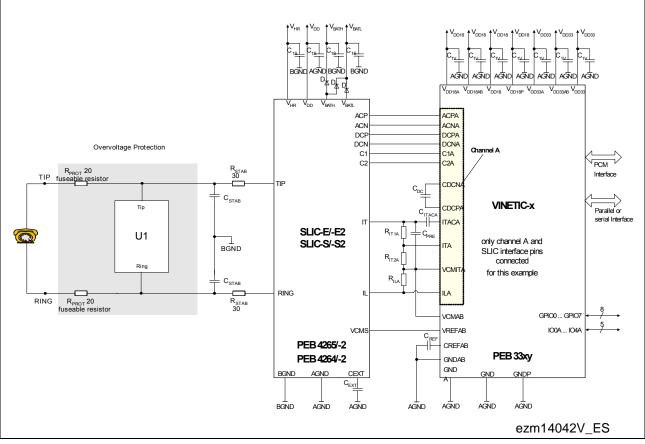

| Figure 14                                                                                                | Application Circuit Internal Ringing (balanced) for SLIC-E/-S                                                                                                                                                                                                                                                                                               | 65                                     |

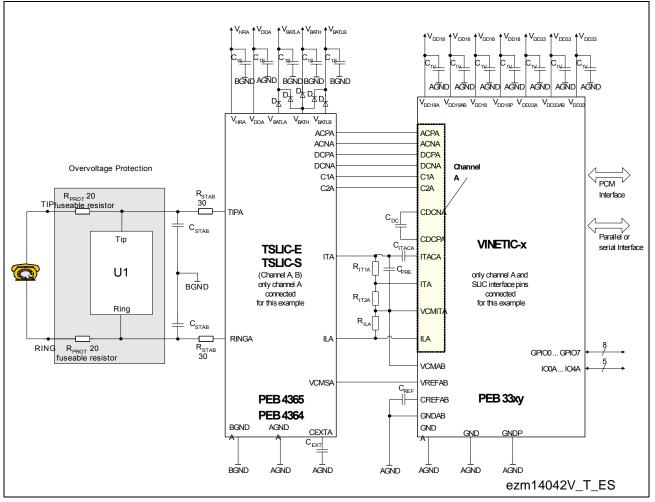

| Figure 15                                                                                                | Application Circuit Internal Ringing (balanced) for TSLIC-E/-S                                                                                                                                                                                                                                                                                              | 66                                     |

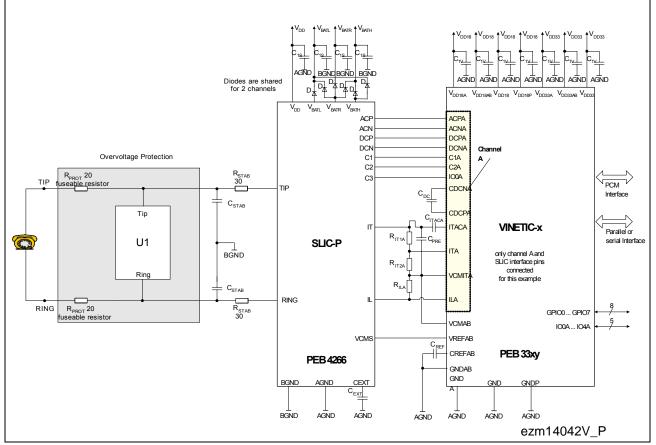

| Figure 16                                                                                                | Application Circuit Internal Ringing (bal. & unbal.) for SLIC-P                                                                                                                                                                                                                                                                                             |                                        |

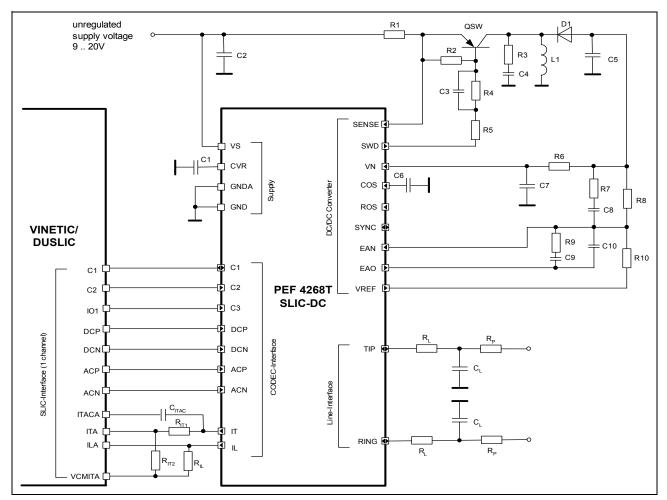

| Figure 17                                                                                                | Application Circuit Internal Ringing with DC/DC                                                                                                                                                                                                                                                                                                             | 69                                     |

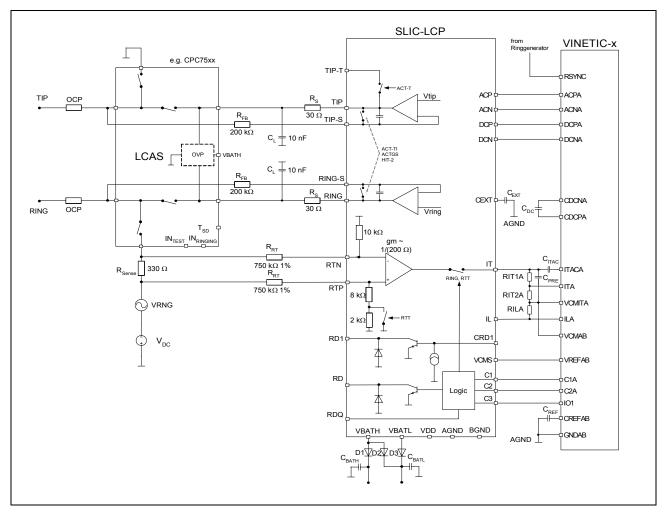

| Figure 18                                                                                                | Application Circuit External Ringing for SLIC-LCP                                                                                                                                                                                                                                                                                                           |                                        |

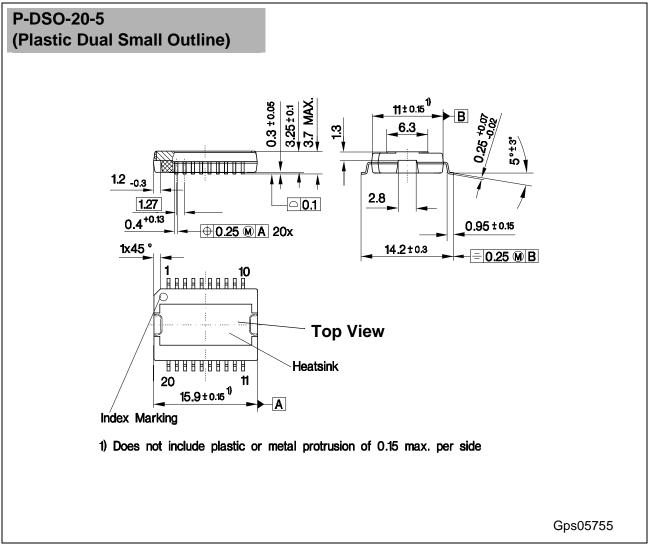

| Figure 19                                                                                                | SLIC-S/-S2, SLIC-E/-E2, SLIC-P (PEB 426x)                                                                                                                                                                                                                                                                                                                   | 73                                     |

| Figure 20                                                                                                | SLIC-S/-S2, SLIC-E/-E2, SLIC-P (PEB426x), SLIC-LCP (PEB 4262).                                                                                                                                                                                                                                                                                              | 74                                     |

| Figure 21                                                                                                | TSLIC-S (PEB 4364), TSLIC-E (PEB 4365)                                                                                                                                                                                                                                                                                                                      |                                        |

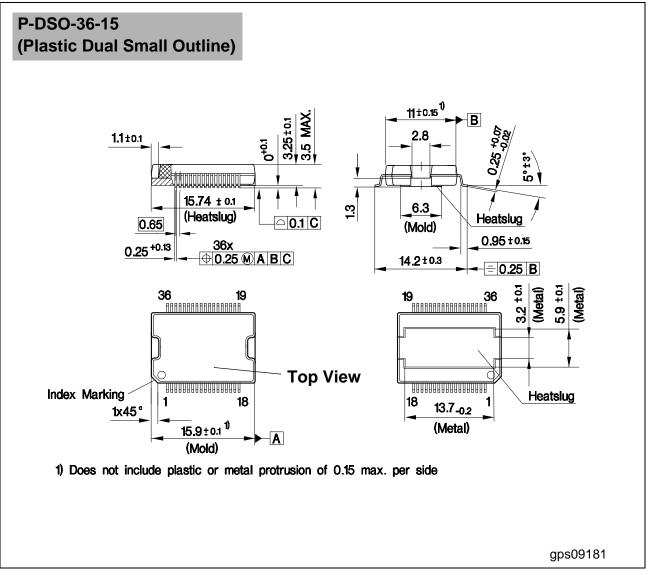

| Figure 22                                                                                                | SLIC-DC (PEB 4268)                                                                                                                                                                                                                                                                                                                                          |                                        |

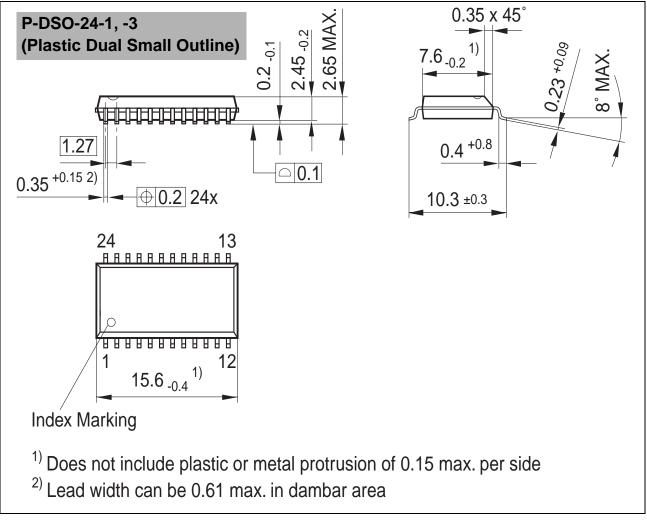

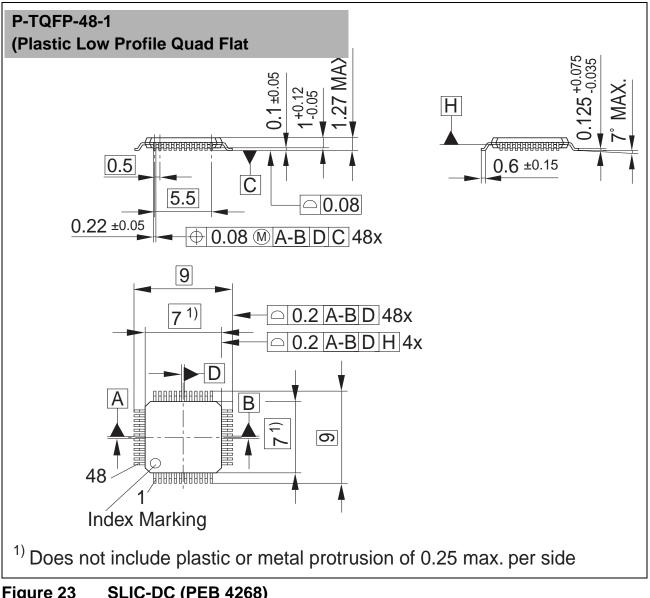

| Figure 23                                                                                                | SLIC-DC (PEB 4268)                                                                                                                                                                                                                                                                                                                                          | 77                                     |

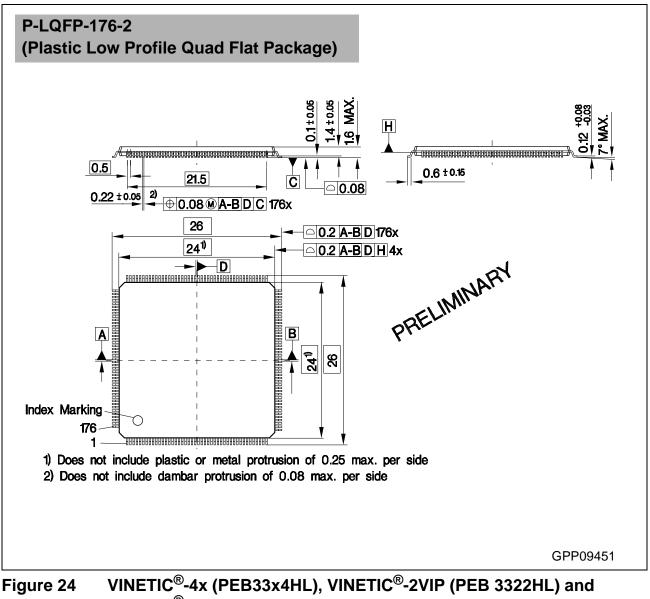

| Figure 24                                                                                                | VINETIC <sup>®</sup> -4x (PEB33x4HL), VINETIC <sup>®</sup> -2VIP (PEB 3322HL) and                                                                                                                                                                                                                                                                           |                                        |

|                                                                                                          | VINETIC <sup>®</sup> -0 (PEB3320HL) $\dots$                                                                                                                                                                                                                                                                                                                 | 78                                     |

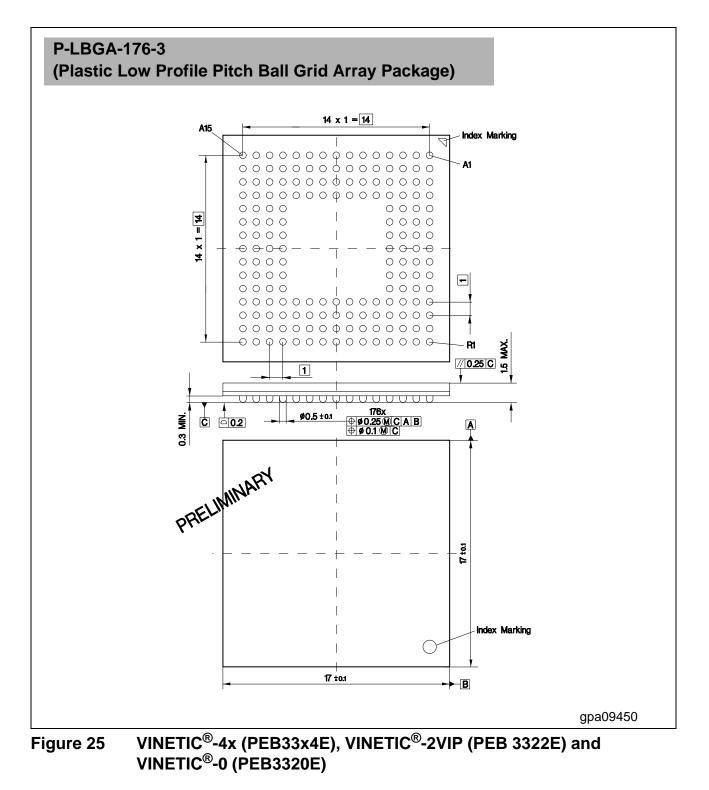

| Figure 25                                                                                                | VINETIC <sup>®</sup> -4x (PEB33x4E), VINETIC <sup>®</sup> -2VIP (PEB 3322E) and                                                                                                                                                                                                                                                                             |                                        |

|                                                                                                          | VINETIC <sup>®</sup> -0 (PEB3320E)                                                                                                                                                                                                                                                                                                                          | 79                                     |

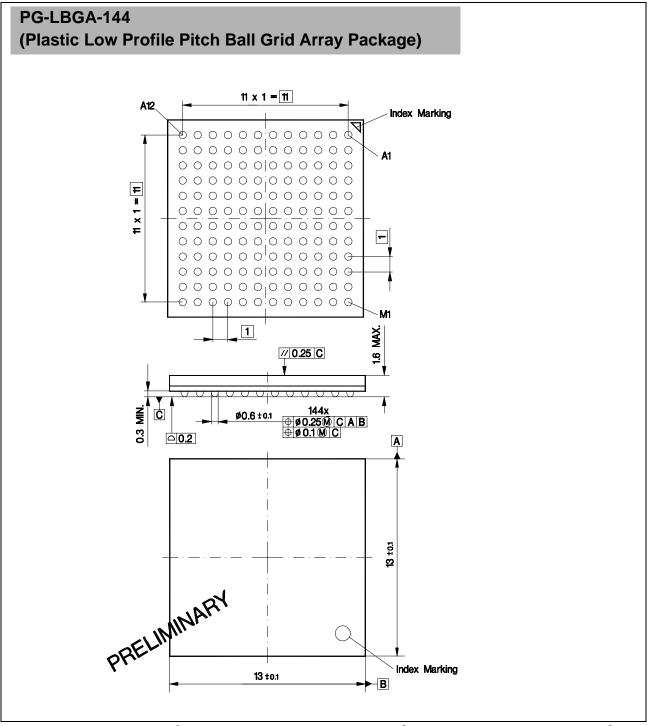

| Figure 26                                                                                                | VINETIC <sup>®</sup> -2CPE (PEB 3332), VINETIC <sup>®</sup> -4M (PEB 3314),                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                          | VINETIC <sup>®</sup> -4C (PEB 3394), VINETIC <sup>®</sup> -4S(PEB 3304)                                                                                                                                                                                                                                                                                     | 80                                     |

## **VINETIC**<sup>®</sup>

#### List of Tables

| Table 1  | VINETIC <sup>®</sup> -x Versions                          | 12 |

|----------|-----------------------------------------------------------|----|

| Table 2  | SLIC Versions                                             | 12 |

| Table 3  | VINETIC <sup>®</sup> Features                             | 13 |

| Table 4  | Provided Algorithms for VINETIC <sup>®</sup>              | 31 |

| Table 5  | Operating Range VINETIC <sup>®</sup>                      | 52 |

| Table 6  | Power Consumption VINETIC <sup>®</sup>                    | 54 |

| Table 7  | Power-Up Sequence VINETIC <sup>®</sup>                    | 55 |

| Table 8  | Operating Range SLIC-S/-S2                                | 57 |

| Table 9  | Operating Range SLIC-E/-E2                                | 58 |

| Table 10 | Operating Range SLIC-P                                    | 59 |

| Table 11 | Operating Range SLIC-DC                                   | 60 |

| Table 12 | Operating Range SLIC-LCP                                  | 61 |

| Table 13 | AC Transmission                                           |    |

| Table 14 | DC Characteristics                                        | 63 |

| Table 15 | External Components in Application Circuit for 4 Channels | 68 |

| Table 16 | Components for SLIC-DC Application Circuit                | 69 |

| Table 17 | External Components                                       | 71 |

|          |                                                           |    |

## VINETIC®

#### **Family Overview**

## 1 Family Overview

The VINETIC<sup>®</sup> is a family of devices for analog telephone line provision. VINETIC<sup>®</sup> devices are available in different granularity (0, 2, 4 and 8 analog voice channels) and also with different levels of DSP performance (VIP, CPE, M, C, S). The seamless connection to a broad range of SLICs provides the most effective solution for a wide range of applications, from high density CO/DLC/PBX linecards to low-cost CPE applications. Significant boardspace reduction can be achieved through the integrated DSP for voice processing and packetization.

The VINETIC<sup>®</sup> provides system solutions for the following applications:

- Access Network:

- Central Office TDM

- Digital Loop Carrier TDM, VoATM, VoIP

- FTTH TDM, VoATM, VoIP

- WLL TDM, VoIP

- PBX:

- Analog Linecard TDM, VoIP

- Customer Premises Equipment:

- Residential Gateway / Home Gateway / Internet Telephony Gateway (ITG) VoIP

- Integrated Access Device (IAD) VoIP, VoATM

- Cable Modems / Media Terminal Adapter (MTA) VoIP

- Analog Telephony Adapter (ATA) VoIP

To cover these applications, the VINETIC<sup>®</sup> devices are pin- and software-compatible, allowing the maximum flexibility while offering the optimized feature set per application.

## Voice and Internet Enhanced Telephony Interface Concept VINETIC<sup>®</sup>

#### **Executive Summary**

The VINETIC<sup>®</sup> family integrates the DSP and RAM for voice processing into the codec/SLIC chip set, thereby offering a unique set of features for voice over packet:

- Cost and Boardspace Reduction codec, DSP and RAM are integrated into one small package providing significant cost and boardspace advantages.

- Scalability VINETIC<sup>®</sup> supports each voice channel with the necessary amount of DSP performance due to the encapsulation of codec and DSP.

- Flexibility the VINETIC<sup>®</sup> family offers 2 to 8 analog ports and various level of DSP performance, while remaining pin- and software-compatible.

- World-Wide-Usage The VINETIC<sup>®</sup> can be adapted to different country requirements without a hardware change (AC and DC path, ringing, metering, etc. are programmable).

- Future Proof the integrated RAM for downloading advanced codecs or Infineon DSP software guarantees that for future remote updates the system will remain state-of-the-art technology.

- Designed for Voice over Packet (VoIP, VoDSL, Cable, VoATM)

P-DSO-36-15

| Туре                                                                       | Package                                    |

|----------------------------------------------------------------------------|--------------------------------------------|

| PEB 3324, PEB 3322, PEB 3332,<br>PEB 3320, PEB 3314, PEB 3394,<br>PEB 3304 | P-LQFP-176-2, P-LBGA-176-3,<br>PG-LBGA-144 |

| PEB 4364, PEB 4365                                                         | P-DSO-36-15                                |

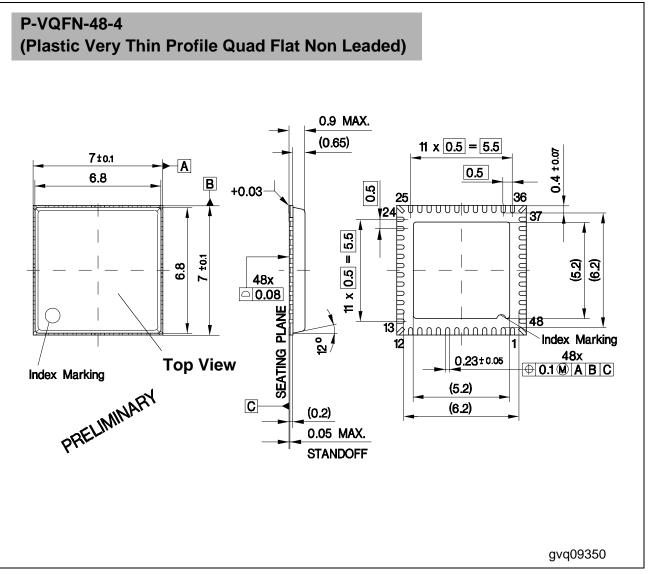

| PEB 4264/-2, PEB 4265/-2, PEB 4266                                         | P-DSO-20-5, P-VQFN-48-4                    |

| PEF 4268                                                                   | P-DSO-24-1, -3, P-TQFP-48-1                |

## **VINETIC**<sup>®</sup>

#### **Family Overview**

| Chip Set <sup>1)</sup>                                               | VINETIC <sup>®</sup> -<br>4VIP | VINETIC <sup>®</sup> -<br>2VIP | VINETIC <sup>®</sup> -<br>2CPE | VINETIC <sup>®</sup> -<br>0 | VINETIC <sup>®</sup> -<br>4M/-8M | VINETIC <sup>®</sup> -<br>4C | VINETIC <sup>®</sup> -<br>4S/-8S |

|----------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|-----------------------------|----------------------------------|------------------------------|----------------------------------|

| Product ID                                                           | PEB 3324                       | PEB 3322                       | PEB 3332                       | PEB 3320                    | PEB 3314/<br>PEB 3318            | PEB 3394                     | PEB 3304/<br>PEB 3308            |

| Analog Channels                                                      | 4                              | 2                              | 2                              | 0                           | 4/8                              | 4                            | 4/8                              |

| Echo Cancellation (G.165,<br>G.168)                                  | up to<br>128 ms                | up to<br>128 ms                | up to<br>16 ms                 | up to<br>128 ms             | up to 16 ms                      | up to 16 ms                  | No                               |

| ADPCM (G.726)                                                        | Yes                            | Yes                            | Yes                            | Yes                         | Yes                              | Yes                          | No                               |

| Complex Voice Codecs<br>(G.723, G.728, G.729) <sup>2)</sup>          | Yes                            | Yes                            | Yes                            | Yes                         | No                               | No                           | No                               |

| Fax Relay T.38                                                       | Yes                            | Yes                            | Yes                            | Yes                         | No                               | No                           | No                               |

| Signal processing functions <sup>3)</sup>                            | Yes                            | Yes                            | Yes                            | Yes                         | Yes                              | Yes                          | No                               |

| AAL2, RTP packetization,<br>Jitter Buffer                            | Yes                            | Yes                            | RTP only                       | Yes                         | Yes                              | No                           | No                               |

| Integrated Code RAM for<br>Firmware Download                         | Yes                            | Yes                            | Yes                            | Yes                         | Yes                              | No <sup>6)</sup>             | No <sup>´6)</sup>                |

| Line testing AITDF <sup>4)</sup>                                     | Yes                            | Yes                            | GR909 only                     | Yes                         | Yes                              | Yes                          | Yes                              |

| World wide programmability of analog BORSCHT <sup>5)</sup> functions | Yes                            | Yes                            | Yes                            | -                           | Yes                              | Yes                          | Yes                              |

## Table 1*VINETIC*<sup>®</sup>-x Versions

All 4-, 2- and 0-channel devices are pin- and software compatible, except the VINETIC-2CPE that is optimized for CPE market; for 8-channel codecs contact local sales.

<sup>2)</sup> Patent indemnification available.

<sup>3)</sup> e.g. DTMF generation and detection, Caller ID (CLIP) generation (FSK), Universal Tone Detection (UTD), Answering Tone Detection (ATD). Caller-ID detection. Universal Tone Generator (covering Japanese Tones). Call Progress Tone detector.

- <sup>4)</sup> Advanced Integrated Test and Diagnosis Functions.

- <sup>5)</sup> Battery feed, Ringing, Signaling (supervision), Coding, Hybrid for 2/4-wire conversion, Testing, Hook thresholds, Teletax metering.

- <sup>6)</sup> Versions up to v1.4 provide also RAM for firmware download

| Marketing<br>Name        | SLIC-S              | TSLIC-S             | SLIC-S2                      | SLIC-E              | TSLIC-E             | SLIC-E2                      | SLIC-P                                | SLIC-LCP                                                | SLIC-DC                                  |

|--------------------------|---------------------|---------------------|------------------------------|---------------------|---------------------|------------------------------|---------------------------------------|---------------------------------------------------------|------------------------------------------|

| Product ID               | PEB 4264            | PEB 4364            | PEB 4264<br>-2 <sup>2)</sup> | PEB 4265            | PEB 4365            | PEB 4265<br>-2 <sup>3)</sup> | PEB 4266                              | PEB 4262                                                | PEB 4268                                 |

| Channels                 | 1                   | 2                   | 1                            | 1                   | 2                   | 1                            | 1                                     | 1                                                       | 1                                        |

| Internal<br>Ringing      | 45 Vrms<br>balanced | 45 Vrms<br>balanced | 45 Vrms<br>balanced          | 85 Vrms<br>balanced | 85 Vrms<br>balanced | 85 Vrms<br>balanced          | 85 Vrms<br>bal.,<br>50 Vrms<br>unbal. | external<br>ringing                                     | DC/DC<br>generator<br>included<br>60Vrms |

| Longitudinal<br>Balance  | 53 dB               | 53 dB               | 60 dB                        | 53 dB               | 53 dB               | 60 dB                        | 53 dB                                 | 60dB with<br>adaption<br>to external<br>compon-<br>ents | 48 dB                                    |

| Maximum<br>DC feeding    | 32 mA               | 32 mA               | 50 mA                        | 32 mA               | 32 mA               | 50 mA                        | 32 mA                                 | 50 mA                                                   | 32 mA                                    |

| Neg. Battery<br>Voltages | 2                   | 2                   | 2                            | 2                   | 2                   | 2                            | 2/3                                   | 2                                                       | 0                                        |

#### Table 2 SLIC Versions<sup>1)</sup>

#### **Family Overview**

## Table 2SLIC Versions<sup>1)</sup> (cont'd)

| Add. positive<br>Voltages | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 1<br>(unreg.<br>12-35V) |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------|

| Technology                | 90 V  | 90 V  | 90 V  | 170 V | 170 V | 170 V | 170 V | 170 V | 170 V                   |

|                           | Smart                   |

|                           | Power                   |

<sup>1)</sup> For broadband SLICs for the Infineon ADSL combo solution (Integrated Voice and Data IVD - GEMINAX-S PEB 4561 and GEMINAX-S MAX PEF 55801), please contact local sales.

<sup>2)</sup> Chip marked as PEB 4264

3) Chip marked as PEB 4265

## Table 3VINETIC<sup>®</sup> Features

|         |     |      | 1  |    |    |                               |

|---------|-----|------|----|----|----|-------------------------------|

| -VIP    | -2  | -M   | -C | -S | -0 | VINETIC <sup>®</sup> Features |

| - • • • |     | -141 | -0 | -0 | -0 |                               |

|         | CPE |      |    |    |    |                               |

|         |     |      |    |    |    |                               |

#### **Common Features**

| 2/4 | 2 | 4/8 | 4 | 4/8 | 0 | Number of fully programmable codecs with enhanced signal processing capabilities <sup>1)</sup>                                                                  |

|-----|---|-----|---|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ٠   |   | •   | • | •   | • | Pin-compatible and software compatible                                                                                                                          |

| •   | • | •   | • | •   |   | Glueless interface to Infineon SLICs family: SLIC-S/-S2, TSLIC-S, SLIC-E/-E2, TSLIC-E and SLIC-P, SLIC-LCP and SLIC-DC <sup>2)</sup> , GEMINAX-S, GEMINAX-S MAX |

#### Integrated DSP Features

| • | • | • |   |   | • | Integrated DSP<br>— with RAM for VoIP/VoDSL/VoATM and software download capability <sup>3)</sup>                   |

|---|---|---|---|---|---|--------------------------------------------------------------------------------------------------------------------|

| • | • | • | • |   | • | <ul> <li>for enhanced signal processing</li> </ul>                                                                 |

| • | • | • |   |   | • | RTP packetization & jitter buffer (adaptive and fixed; 200ms)                                                      |

| • | • | • |   |   | • | RTCP support                                                                                                       |

| • |   | • |   |   | • | AAL2 cell generation & jitter buffer (adaptive and fixed; 200ms)                                                   |

| • |   | • |   |   | • | Compatible with ITU-T I.366.2                                                                                      |

| • | • | • |   |   | • | Compatible with RFC 1889 specification                                                                             |

| • | • | • |   |   | • | Compatible with Packet Cable specification                                                                         |

| • |   | • |   |   | • | PacketOverPCM functionality                                                                                        |

| • | • | • | • | • | • | Integrated DTMF generator                                                                                          |

| • | • | • | • |   | • | Integrated DTMF decoder                                                                                            |

| • | • | • | • |   | • | Integrated Caller ID (FSK) generator, according to Bellcore 202 and V.23                                           |

| • | • | • | • |   | • | Integrated Caller ID (FSK) detector, according to Bellcore 202 and V.23                                            |

| • | • | • | • |   | • | Integrated fax/modem detection by Universal Tone Detection unit (UTD), In-band tone detection                      |

| • | • | • | • |   | • | Integrated Universal Tone Generator (UTG) including holwer tone and japanese tone generation                       |

| • | • | • | • |   | • | Call Progress Tone (CPT) Detector                                                                                  |

| • |   | • | • | • |   | Optimized filter structure for modem transmission, enhanced modem performance for improvement of V.90 transmission |

|   |   |   |   |   |   |                                                                                                                    |

## Family Overview

| -VIP | -2<br>CPE | -M | -C | -S | -0 | VINETIC <sup>®</sup> Features                                                                                                                    |

|------|-----------|----|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| •    | •         | •  | •  |    | •  | Multi-party conferencing                                                                                                                         |

| ٠    | •         | •  |    |    | •  | 3-Party conferencing via packet network                                                                                                          |

| •    | •         | •  | •  | •  | •  | G.711                                                                                                                                            |

| •    | •         | •  |    |    | •  | G.711 Annex I (Packet Loss Concealment), G.711 Annex II (VAD + CNG)                                                                              |

| •    | •         | •  | •  |    | •  | G.726 ADPCM                                                                                                                                      |

| ٠    | •         |    |    |    | •  | G.729 A, B                                                                                                                                       |

| ٠    | •         |    |    |    | •  | G.723.1                                                                                                                                          |

| ٠    | •         |    |    |    | •  | G.728, G.728 Annex I (Packet Loss Concealment)                                                                                                   |

| ٠    | •         |    |    |    | •  | G.729 E                                                                                                                                          |

| ٠    | •         |    |    |    | •  | iLBC <sup>4)</sup>                                                                                                                               |

| ٠    | •         | •  |    |    | •  | Voice Activity Detection (VAD)                                                                                                                   |

| ٠    | •         | •  |    |    | •  | Comfort Noise Generation (CNG)                                                                                                                   |

| •    | •         | •  | •  |    | •  | Algorithms for Line Echo Cancellation exceeding G.165, G.168, G.168-2000, G.168-2002:<br>– up to 128 ms tail length<br>– up to 16 ms tail length |

| •    | •         | •  |    |    | •  | Voice Play Out (reordering, fixed and adaptive jitter buffer, clock synchronization)                                                             |

| ٠    | •         |    |    |    | •  | T.38 Fax Relay Support including all required datapump algorithms V.17, V.21, V.27ter, V.29                                                      |

| •    | •         |    |    |    | •  | Text phone support V.18                                                                                                                          |

## Table 3VINETIC<sup>®</sup> Features (cont'd)

#### Codec/SLIC Features

| ٠ | • | • | • | • | Worldwide programmability for AC and DC parameters                                                                                                                                           |

|---|---|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | • | • | • | • | Specification in accordance with ITU-T Recommendation Q.552 for interface Z                                                                                                                  |

| • |   | • | • | • | Specification in accordance with ITU-T Recommendation G.712,<br>and applicable LSSGR(GR-506/507 etc.), GR-57, EIA/TIA-464 and other applicable<br>worldwide standards.                       |

| • | • | • | • | • | Integrated balanced/unbalanced ringing capability fully software programmable up to 85 Vrms ringing voltage, Crest-factor selection between 1.2 and 1.6, frequency range between 15 and 75Hz |

| • |   | • | ٠ | • | External ringing support                                                                                                                                                                     |

| • |   | • | • | • | Programmable 12/16 kHz teletax generation (metering) and integrated notch filtering                                                                                                          |

| • | • | • | • | • | Programmable battery feeding with capability for driving longer loops                                                                                                                        |

| • | • | • | ٠ | • | Ground/loop start signaling                                                                                                                                                                  |

| • |   | • | • | • | Ground key detection                                                                                                                                                                         |

| • | • | • | • | • | Polarity reversal                                                                                                                                                                            |

| • | • | • | • | • | Message Waiting Indication                                                                                                                                                                   |

| • | • | • | • | • | Automatic modes for POTS signaling and Power Management                                                                                                                                      |

| • | • | • | • | • | Advanced Integrated Test and Diagnostic Functions (AITDF) for local loop monitoring (including GR-909) and board production test capabilities.                                               |

| • | • | • | • | • | On-hook transmission                                                                                                                                                                         |

## **VINETIC**<sup>®</sup>

#### **Family Overview**

## Table 3VINETIC<sup>®</sup> Features (cont'd)

| -VIP | -2<br>CPE | -М | -C | -S | -0 | VINETIC <sup>®</sup> Features                                                               |

|------|-----------|----|----|----|----|---------------------------------------------------------------------------------------------|

| •    | •         | •  | •  | •  |    | Power optimized architecture with power management capability (integrated battery switches) |

| ٠    |           | •  | •  | •  | •  | Part of ADSL IVD and IPVD solution                                                          |

| ٠    | •         | •  | •  | •  |    | Direct connection of Clare Litelink III device                                              |

#### Interface Features

| ٠ | • | • | • | • | • | PCM/µC interface selectable                                         |  |  |  |

|---|---|---|---|---|---|---------------------------------------------------------------------|--|--|--|

| 2 | 1 | 2 | 2 | 2 | 2 | PCM interface (number of highways)                                  |  |  |  |

| ٠ | • | • | • | • | • | Parallel Host interface: Intel/Motorola compatible                  |  |  |  |

| ٠ | • | • | • | • | • | Serial control interface, SCI (Infineon) compatible, SPI compatible |  |  |  |

| ٠ | • | ٠ | • | • |   | SLIC interface compatible with DuSLIC <sup>®</sup> SLICs            |  |  |  |

| • | • | • | • | • | • | AG interface for boundary scan                                      |  |  |  |

#### Available Packages<sup>5)</sup>

| • | • | •               | •   | •   | • | P-LQFP-176  |

|---|---|-----------------|-----|-----|---|-------------|

| ٠ | • | •               | •   | •   | • | P-LBGA-176  |

|   | • | • <sup>6)</sup> | •)6 | •)6 |   | PG-LBGA-144 |

#### **Additional Features**

| • | • | • | • | • | • | SW compatible between different VINETIC devices |

|---|---|---|---|---|---|-------------------------------------------------|

| ٠ |   | • | • | • | • | HW compatible between different VINETIC devices |

| ٠ | • | • | • | • | • | Driver and API for Linux and VxWorks            |

1) 8-channel devices in preparation

2) In preparation.

$^{3)}$  All VINETIC  $^{\textcircled{B}}$  devices up to version v1.4 include RAM for download

- 4) in preparation

- <sup>5)</sup> Green Packages in preparation. contact local sales for details

<sup>6)</sup> only available for production from v2.1 onwards

## **VINETIC**<sup>®</sup>

#### **Family Overview**

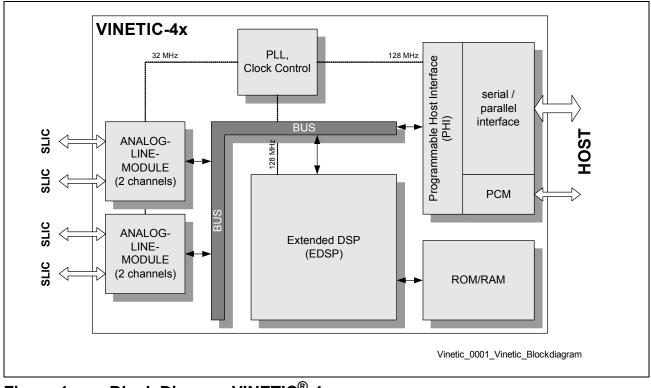

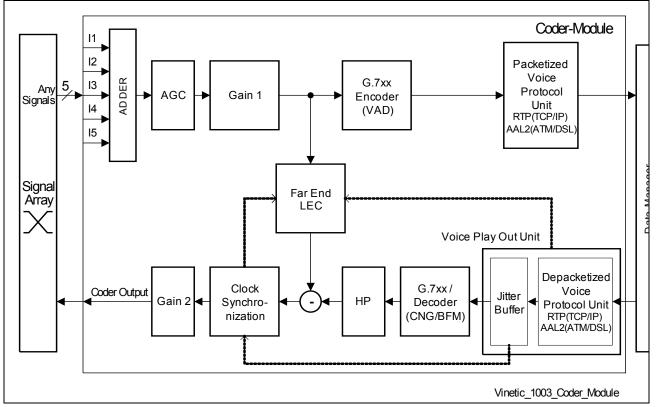

## Figure 1 Block Diagram VINETIC<sup>®</sup>-4x

Figure 1 shows the typical block diagram of a VINETIC<sup>®</sup> 4-channel device.

#### **Family Overview**

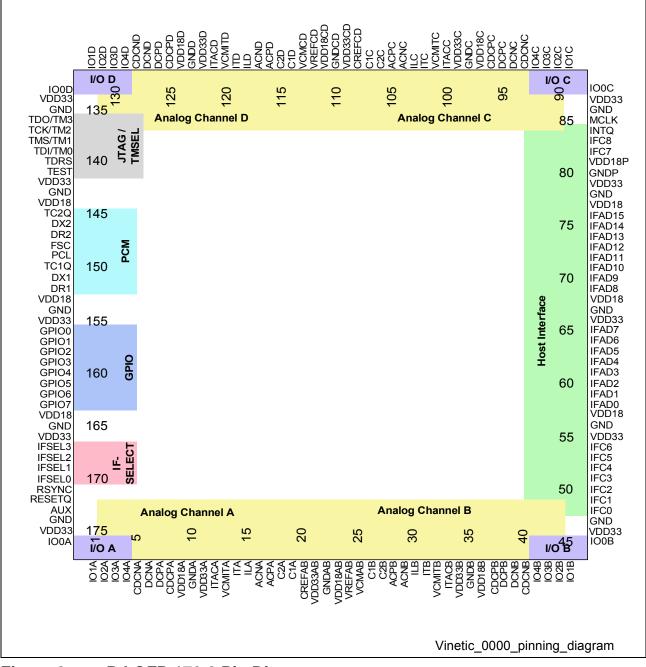

## 1.1 Pin Diagram VINETIC<sup>®</sup>-4x

#### 1.2 P-LQFP-176-2 Pin Diagram

Figure 2 P-LQFP-176-2 Pin Diagram

## **VINETIC**<sup>®</sup>

## Family Overview

## 1.3 P-LBGA-176-3 Pin Diagram

|       | IO1D   |        |        | VDD33D | F<br>D<br>O | C1D  |         | C1C<br>O |                          |        |        |        | 104C   |         |

|-------|--------|--------|--------|--------|-------------|------|---------|----------|--------------------------|--------|--------|--------|--------|---------|

|       |        | IO2D   |        |        |             |      | VREFCD  |          |                          | VDD33C |        |        |        |         |

|       | VDD33  |        |        | VDD18D |             | ACPD | VDD18CD |          | ACNC                     |        | CDCPC  | VSS    | VDD33  |         |

|       |        | TEST   | IO4D   |        |             | ACND |         | VDD33CD  | ACPC                     |        | VDD18C | VDD18P |        | IFC7    |

|       | VSS    | VDD18  | TC2Q   |        |             |      |         |          |                          |        |        | VSSP   | VSS    | VDD33   |

|       | DR2    | FSC    |        |        |             |      |         |          |                          |        | VDD18  | IFAD15 | IFAD13 | IFAD14  |

|       |        | DR1    | VDD18  |        |             |      |         |          |                          |        | IFAD12 | IFAD11 |        | IFAD10  |

|       | GPIO0  | VSS    | GPIO1  |        |             |      |         |          |                          |        |        | VDD18  | VDD33  | VSS     |

| GPIO3 | GPIO2  | GPIO4  | GPIO5  |        |             |      |         |          |                          |        | IFAD7  |        |        | IFAD5   |

| GPI07 | GPIO6  | VDD18  | VSS    |        |             |      |         |          |                          |        | IFAD4  |        |        | IFAD1   |

|       | IFSEL3 | IFSEL2 | IFSEL1 |        |             |      |         |          |                          |        | VDD18  | VSS    | IFC6   | VDD33   |

|       |        |        | VDD18A |        | ACPA        |      | GNDAB   | ACPB     | $\bigcirc^{\mathbb{IB}}$ | VDD33B |        | IFC5   | IFC4   | IFC3    |

| 3 O   |        |        |        |        | ACNA        |      | VCMAB   | ACNB     | ITACB                    | CDCPB  | DCPB   | VDD33  | VSS    | IFC2    |

|       |        |        |        | VDD33A |             | C1A  | VREFAB  | C1B      | VCMITB                   | VDD18B |        | IO1B   |        | IFC1    |

|       |        |        |        | GNDA   |             |      | VDD18AB | C2B      |                          |        |        |        |        | IFC0    |

|       |        |        |        |        |             |      |         |          | Vineti                   | c_000( | Da_LB  | GA_pii | nning  | diagram |

Figure 3 P-LBGA-176-3 Pin Diagram

## Family Overview

## 1.4 PG-LBGA-144 Pin Diagram (4-channel devices)

|    | Α              | В              | С              | D         | E      | F      | G         | Н      | IJ     | K        |         | M        |

|----|----------------|----------------|----------------|-----------|--------|--------|-----------|--------|--------|----------|---------|----------|

| 12 |                | IO2D           |                |           |        | ACPD   | ACPC      | ACNC   |        |          |         |          |

| 11 | IO4D           |                |                |           | VDD33A | C2D    | VDD18A    | VDD33A |        |          |         |          |

| 10 | C1D            |                |                |           |        |        |           |        |        |          |         | C1C<br>O |

| 9  |                |                |                | TEST<br>O |        |        |           |        | ТООТМЗ |          |         | VDD18P   |

| в  | VDD33          | VDD18          | TC2Q           | тск/тм2   | Dx2    |        |           | IFC8   |        | IFAD4    | IFAD7   | VDD33    |

| 7  | DR1            | DX1            | FSC            | DR2       |        |        |           | IFC7   | IFC4   |          | IFAD5   | VDD18    |

| 6  | GPIO0/<br>SCDO | GPIO1/<br>SCDI | GPIO2/<br>SCCK | GPIO3     | GPIO4  |        |           | GPI07  | IFC0   | IFAD2    |         | VDD18    |

| 5  | VDD33          | VDD18          | GPIO6          | RSYNC     | AUX    |        |           | GPIO5  | IFC2   |          | IFAD1   | VDD33    |

| 4  | IFSEL2         |                | IFSEL1         | RESETQ    |        | CREFAB |           |        | IFC3   | IFC1     | IFC5    | IFC6     |

| 3  | C1A            |                |                |           |        | C2A    | VREFAB    |        |        |          |         | C1B      |

| 2  |                |                |                |           | VDD33A | VDD18A | C2B       | VDD33A |        |          |         |          |

|    |                |                |                |           | ACNA   | ACPA   | ACPB      | ACNB   | DCPB   | CDCPB    |         | IO1B     |

|    |                |                |                |           |        | Vine   | etic_0000 | a_HDLC | LBGA_  | 144_pinn | ing_dia | gram_21  |

Family Overview

## 1.5 PG-LBGA-144 Pin Diagram (2-channel devices)

|    | Α      | В     | С       | D      | E          | F                 | G      | Н      |                     | K                      |      | M      |

|----|--------|-------|---------|--------|------------|-------------------|--------|--------|---------------------|------------------------|------|--------|

| 12 | dhc    | dnc   | dhc     | drc    | drc        | dhc               | drc    | drc    | drc                 | drc                    | dhc  | dnc    |

| 11 | drc    | drc   | drc     |        | VDD33A     | drc               | VDD18A | VDD33A |                     | drc                    | dnc  | dnc    |

| 10 | duc    |       | drc     |        | $\bigcirc$ | drc               | drc    |        |                     | drc                    |      | dr:C   |

| 9  | TDRSQ  |       | TMS/TM1 | TEST   | dnc        | drc               | drc    | dhc    | TDO/TM3             |                        |      | VDD18P |

| 8  | VDD33  | VDD18 | dnc     |        |            | GNDA              | GNDA   | IFC8   | Pal                 | IFAD4                  |      | VDD33  |

| 7  |        | DX1   | FSC     | DX1    | drc        |                   |        | IFC7   | IFC4                |                        |      | VDD18  |

| 6  | GPIO0  | GPIO1 | GPIO2   | GPIO3  | GPIO4      |                   |        | GPIO7  | IFC0                |                        |      | VDD18  |

| 5  | VDD33  | VDD18 |         | RSYNC  | AUX        | GNDA              | GNDA   | GPIO5  | IFC2                |                        |      | VDD33  |

|    | IFSEL2 |       | IFSEL1  | RESETQ |            | OREFAB            |        |        | IFC3                |                        | IFC5 |        |

| 3  | C1A    |       |         |        |            | C2A               |        |        |                     |                        | ITB  | C1B    |

| 2  |        |       |         |        | VDD33A     | VDD18A            | С2В    | VDD33A |                     |                        | ЮЗВ  |        |

|    | IO1A   |       | CDOPA   | DOPA   | AONA       | ACPA<br>O<br>Vine | ACPB   | ACNB   | DOPB<br>O<br>LBGA_1 | CDCPB<br>O<br>44_pinni | IO2B | am     |

## **VINETIC**<sup>®</sup>

#### **Family Overview**

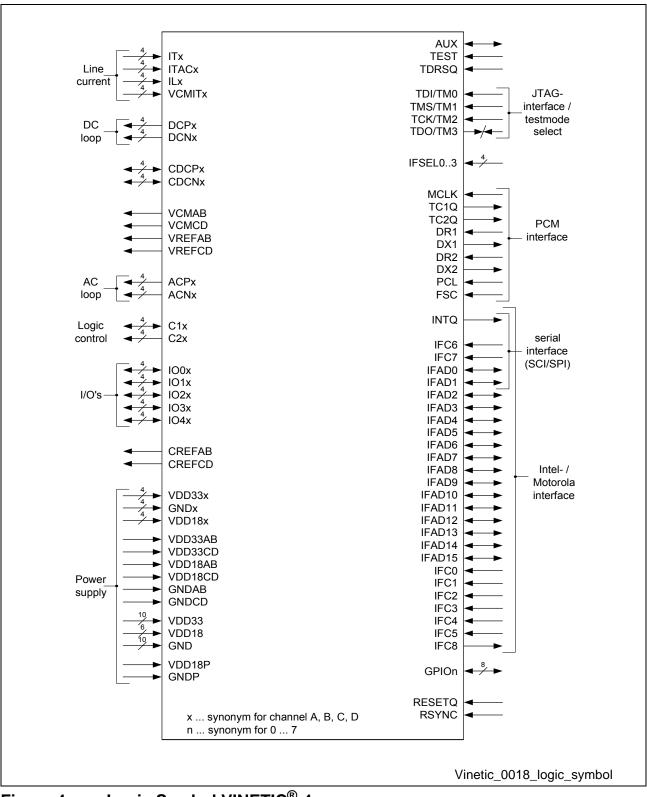

Figure 4 Logic Symbol VINETIC<sup>®</sup>-4x

#### **Family Overview**

## 1.7 Typical Applications

The following applications are only a small part of the numerous possibilities when using the VINETIC<sup>®</sup> chip set:

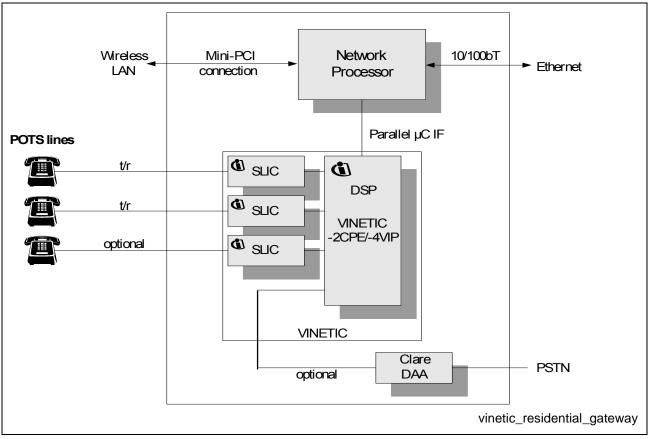

#### Figure 5 Residential Gateway / ATA / VoIP Router

**Figure 5** shows a residential gateway that allows to extend the home network by introducing VoIP and a wireless data connection to it. The existing Ethernet connection is terminated by a network processor that enables additional functionality like firewalling, routing, and other data services as well as the voice call control. To keep the network as optimized as possible, the VINETIC<sup>®</sup>-2CPE for two voice channels or the VINETIC<sup>®</sup>-4VIP for four channels takes care of all the functionality that is voice related. All jitter buffering, RTP packetization, tone generation and detection including event handling and voice processing (compression G.72x, T.38 fax relay modern modulations, line echo cancellation) is handled within the DSP of the VINETIC<sup>®</sup>. No external memory or other components is needed. All the analog functionality is covered at the same time, including ringing, feeding, line testing, and supervision. The number of POTS lines can easily be increased by adding more VINETIC<sup>®</sup> devices if desired.

For an FXO operation to connect to the PSTN network, the VINETIC<sup>®</sup> devices allow direct connection to DAAs and provide all necessary signal processing functionality like Caller-ID detection.

## VINETIC®

#### **Family Overview**

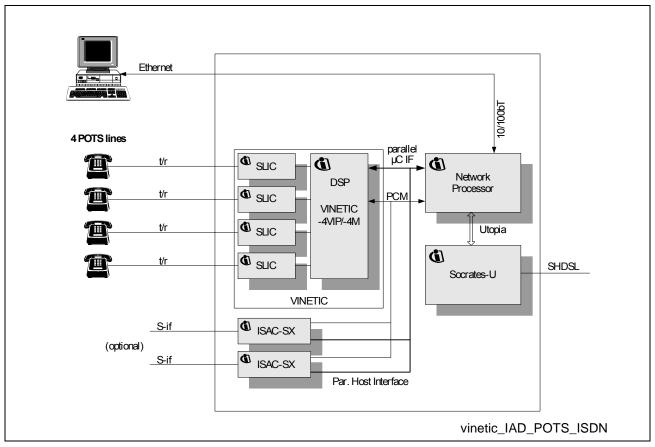

#### Figure 6 IAD serving POTS and ISDN (European Version)

**Figure 6** shows an highly integrated G.SHDSL Integrated Access Device (IAD). The application consists of four major blocks: the SHDSL-transceiver, the network controller, the ISDN S-transceiver (the ISAC-SX devices are an option for european IADs), and the POTS part including voice processing (VINETIC<sup>®</sup>).

Analog signals from the POTS telephones are terminated within the VINETIC<sup>®</sup> chip set and then digitized. In a next step these signals are packetized and sent via tha microprocessor interfaces to the host controller. All necessary fucntions for AAL2 or RTP packetization including jitter buffer and compression are executed within the VINETIC<sup>®</sup>.

Additionally voice and tone processing like DTMF, CLIP and line echo cancellation (LEC) is also performed within the VINETIC<sup>®</sup> chip set.

When using the optional ISDN transceivers it is also possible to apply the LEC and compression features of the VINETIC<sup>®</sup> chip set to the ISDN channels. Voice from the ISAC-SX is transferred via PCM to the DSP of the VINETIC<sup>®</sup>, where the voice processing is performed. The VINETIC<sup>®</sup> is able to handle both voice compression (G.723.1, G.728 or G.729) and Near End LEC for up to 4 channels simultaneously or G.726 and LEC for up to 8 channels. In the application above all voice channels could be operated with ADPCM compression and line echo cancellation with a single VINETIC<sup>®</sup> chip set without external memory.

## VINETIC®

#### **Family Overview**

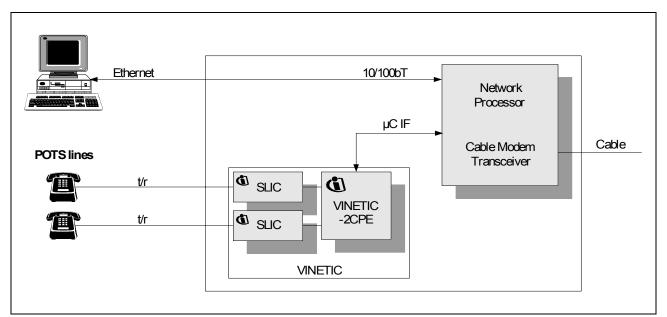

#### Figure 7 Cable Modem / Settop Box / SMTA / EMTA

The VINETIC<sup>®</sup> chip set fulfills all requirements for packetized voice over cable (see **Figure 7**). The voice data is transferred in RTP packets, allowing the network processor an easy packetization for transmitting it via VoIP over the cable network. The VINETIC<sup>®</sup> system is conform to PacketCable specification.

Fax-relay T.38 is also supported by the VINETIC<sup>®</sup> chip set. No additional DSP for voice processing or fax termination is needed in the system.

#### **Family Overview**

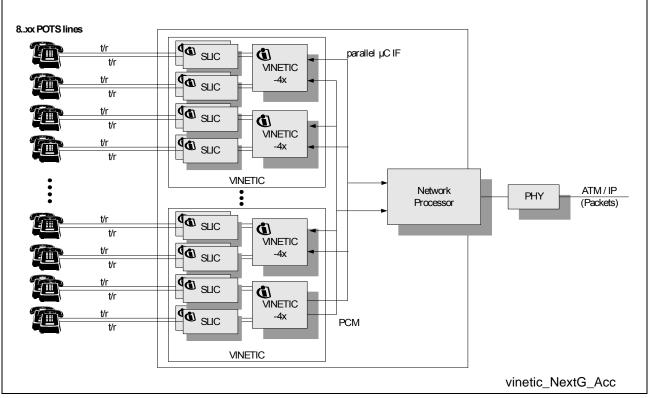

Figure 8 Next Generation Access Network Linecard

Next generation Access Networks / DLCs are using ATM or IP networks to transmit data and voice. VINETIC<sup>®</sup> is highly scalable and allows to install as many codecs in parallel as required by the linecard design. The integrated line testing, ring generation and small footprint SLIC chips makes VINETIC<sup>®</sup> an optimum fit for these high density applications.

Both RTP and AAL2 are supported by VINETIC<sup>®</sup> enabling the network processor to have either an IP or an ATM backbone.

## VINETIC<sup>®</sup> Host Interface Description

## 2 VINETIC<sup>®</sup> Host Interface Description

The host interface of the VINETIC<sup>®</sup> is operated by a programmable host interface controller (PHI) which allows a flexible and easy adaption to various interface types. For programming the VINETIC<sup>®</sup> and performing data/packet transfer from/to VINETIC<sup>®</sup> a parallel interface or a serial microcontroller interface can be used. Additionally VINETIC<sup>®</sup> has an interface to PCM data.

#### VINETIC<sup>®</sup> 8/16-Bit Parallel Interfaces

The parallel interface can be operated in Intel 8/16-bit mode (multiplexed/demultiplexed) or in 8/16-bit Motorola mode.

#### VINETIC<sup>®</sup> Serial Interfaces

The VINETIC<sup>®</sup> serial microcontroller interface ( $\mu$ C interface = SCI) is compatible with Motorola SPI and is electrically compatible with DuSLIC<sup>®</sup>. The PCM interface has 2 PCM highways and can be operated together with the serial  $\mu$ C interface or the parallel interface.

Note: VINETIC<sup>®</sup>-2CPE only supports one PCM interface

## 2.1 VINETIC<sup>®</sup> Host Interface Configurations

The VINETIC<sup>®</sup> host interface can be set into one of the following modes:

- 8-bit INTEL multiplexed mode + PCM interface (2 PCM highways)

- 8-bit INTEL demultiplexed mode + PCM interface (2 PCM highways)

- 16-bit INTEL multiplexed mode + PCM interface (2 PCM highways)

- 16-bit INTEL demultiplexed mode + PCM interface (2 PCM highways)

- 8-bit MOTOROLA mode + PCM interface (2 PCM highways)

- 16-bit MOTOROLA mode + PCM interface (2 PCM highways)

- VINETIC<sup>®</sup> serial µC interface (compatible with Motorola SPI and DuSLIC<sup>®</sup>) + PCM interface (2 PCM highways)

- Note: VINETIC<sup>®</sup>-2CPE only supports 8-bit and serial interfaces with only one PCM highway

#### Note: VINETIC<sup>®</sup> devices with PG-LBGA-144 package only support 8-bit interfaces

Data transfers to and from the VINETIC<sup>®</sup> are either performed via a mailbox system and via the controller interface, or via PacketOverPCM.

The VINETIC<sup>®</sup> supports the widely used microcontrollers: e.g. ADM 5120, MPC850, MPC860, MPC8260, C165UTAH, ARM and MIPS based processors, etc.

Note: VINETIC<sup>®</sup>-2CPE and VINETIC<sup>®</sup> devices with PG-LBGA-144 package only support 8-bit interfaces

## VINETIC<sup>®</sup> Host Interface Description

All parallel and serial interfaces (host interfaces) use the same (multiplexed) pins. The desired interface type is selected by means of pin strapping.

#### **Codec/SLIC Features (BORSCHT Functions)**

## 3 Codec/SLIC Features (BORSCHT Functions)

#### 3.1 BORSCHT functions

Battery Feed

The DC battery feed for the subscriber equipment has to be adapted to different applications and country specific requirements. With the VINETIC<sup>®</sup> chip set, the feed characteristic is programmable in a wide range without any hardware change.

Overvoltage Protection

Overvoltage protection is indispensable to prevent damage to the line circuit if the system is exposed to high voltages that can result from power lines crossing or lightning strikes.

The robust high voltage SLIC technology together with low cost external protection components, form a reliable overvoltage protection solution for the SLIC against overvoltages from the Tip and Ring lines.

Ringing

The VINETIC<sup>®</sup> chip set integrates the ringing generator thus reducing the BOM by obsoleting the ring relay and ring generator. VINETIC<sup>®</sup> supports unbalanced and balanced ringing up to 85  $V_{RMS}$ . With balanced ringing, the ringing voltage is applied differentially to the Tip and Ring lines. With unbalanced ringing, the ringing voltage is applied single-ended to either the Tip or Ring line. Balanced ringing is generated by SLIC-E/-E2 and SLIC-S, while SLIC-P can generate both balanced and unbalanced ringing. In addition the SLIC-DC integrates a DC/DC converter and simplifies CPE applications significantly while reducing BOM cost at the same time.

• Signaling (Supervision)

VINETIC<sup>®</sup> detects off-hook in both non-ringing (hook switch detection) and ringing modes (ring trip detection). The thresholds for ring trip detection within VINETIC<sup>®</sup>-4x can be programmed without changes to external components.

Coding

VINETIC<sup>®</sup>-4x encodes an analog input signal to a digital PCM signal and decodes a PCM signal to an analog signal. Both A-law and  $\mu$ -law coding is supported and can be selected via software.

Some members of the  $\mathsf{VINETIC}^{\texttt{R}}$  family also add ADPCM coding and low-bitrate vocoders

• Hybrid for 2/4-wire Conversion

The subscriber equipment is connected to a 2-wire interface (Tip and Ring) where information is transmitted bidirectionally. For digital transmission through the switching (PSTN) network, the information must be split into separate transmit and receive paths (4 wires). To avoid generating echoes, the hybrid function requires a balanced network

#### **Codec/SLIC Features (BORSCHT Functions)**

matched to the line impedance. Hybrid balancing can be programmed in the VINETIC<sup>®</sup> device without any external components.

Testing

In conventional solutions, testing of local loop and linecard requires a remote test unit and test relays. VINETIC<sup>®</sup>, however, internally offers the possibility of accurate line and board testing, thus avoiding the need for external test unit and relays.

#### Programmability

One of the main advantages of VINETIC<sup>®</sup> is that all SLIC and codec functions are programmable through software. The configuration software VINETICOS can be used to program at each port indepenently the following functions:

- DC (battery) feed characteristics

- AC impedance matching

- Transmit gain

- Receive gain

- Hybrid balance

- Frequency response in transmit and receive direction

- Ring frequency and amplitude, waveform (sinusoidal, trapezoidal, crest factor)

- Hook thresholds

- TTX modes

## 3.2 Advanced Integrated Test and Diagnostic Functions (AITDF)

#### 3.2.1 Introduction

Subscriber loops are affected by a variety of failures and thus must be monitored. This requires access to the subscriber loop as well as specific test equipment. The tests involve measurements of resistance, capacitance, leakage, and any interfering currents and voltages.Traditionally up to 2 relays, and a test unit was necessary to perform such tests. VINETIC<sup>®</sup> integrates both the generation and detection of the test signals as well as the functionality of the relays.

## 3.2.2 VINETIC<sup>®</sup> Line Testing

The VINETIC<sup>®</sup> chip set uses its Advanced Integrated Test and Diagnostic Functions (AITDF) to perform all tests necessary for monitoring the local loop. The measurements can be accomplished not only on a channel specific basis, but also concurrently on all channels. This allows a strong reduction of the testing time compared to conventional test methods. Thus VINETIC<sup>®</sup> helps to increase quality of service and to reduce costs.

The VINETIC<sup>®</sup> line testing supports GR-909 line testing requirements.

#### Codec/SLIC Features (BORSCHT Functions)

#### Line Test Capabilities

The line test comprises the following functions:

• Loop resistance measurement:

The DC loop resistance can be determined by supplying a constant DC voltage  $V_{TR DC}$  to the Ring- and Tip line and measuring the DC loop current via the IT pin.

- Leakage current:

- Leakage current Tip/Ring

- Leakage current Tip/GND

- Leakage current Ring/GND

- Ringer/Line capacitance:

Capacitance measurements can be performed by using the integrated ramp generator function. Loading a capacitor  $C_{Measure}$  with a constant voltage ramp results in a constant current which is proportional to  $C_{Measure}$ .

- Line capacitance Tip/GND

- Line capacitance Ring/GND

- Foreign voltage measurement:

Three analog input pins per voice channel can be used for direct and differential measurement of external voltages.

- Foreign voltage measurement Tip/GND

- Foreign voltage measurement Ring/GND

- Foreign voltage measurement Tip/Ring

- Supervision of Battery voltages

- Measurement of ringing voltage

- Measurement of line feed current

- Measurement of supply voltage V<sub>DD</sub> of the VINETIC<sup>®</sup>-4x

- Measurement of transversal- and longitudinal current.

- Noise Measurement

## 3.2.3 Board and Production Testing

The VINETIC<sup>®</sup> chip set has a set of signal generators and features implemented to accomplish a variety of diagnostic functions that can be used in production tests. Various test loops and measurement features are completing this tool suite.

## Signalprocessing Capabilities of the VINETIC®

## 4 Signalprocessing Capabilities of the VINETIC<sup>®</sup>

The VINETIC<sup>®</sup>-VIP, -M and -C versions are equiped with an EDSP module (Enhanced Digital Signal Processor module) to perform voice and tone processing functions.

The maximum available signal processing capability of the EDSP is limited by the 128 MCycles/s and the internal RAM.

**Table 4** gives an overview on the performance demands of the different algorithms/ functions available and how many resources of them can be activated. As each FW version offers a different subset, a document is available that lists the available resources per firmware version. For further description of the functions refer to **Chapter 7** or the VINETIC<sup>®</sup> documentation available.

#### Table 4Provided Algorithms for VINETIC<sup>®1)</sup>

| Algorithm/Function                                                                                                                                 | Module <sup>2)</sup> | MCycle/s             | max. # of<br>ressources<br>available <sup>3)</sup> |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------------------------------------|

| Operating System<br>(Base load of internal control, Command<br>Mailbox handling,)                                                                  |                      | typ. 15              | 1                                                  |

| DTMF Receiver                                                                                                                                      | Signaling            | 1.0                  | 4                                                  |

| Caller ID Transmission                                                                                                                             | Signaling            | 1.5                  | 4                                                  |

| Universal Tone Detection (UTD) / V.18                                                                                                              | Signaling            | 1.2                  | 4                                                  |

| ATD 2.1 kHz, Modem Tone Detection with<br>Phaseshift (phase reversal, amplitude<br>modulation) / DIS                                               | Signaling            | 1.3                  | 4                                                  |

| DTMF generation <sup>4)</sup>                                                                                                                      | Signaling            | 1.8                  | 4                                                  |

| Near End Line Echo Cancellation (LEC),<br>G.165/G.168 (NLP included):<br>– LEC 8 ms<br>– LEC 16 ms                                                 | PCM, ALM,<br>Coder   | 4.4<br>5.4           | 4                                                  |

| Far End Line Echo Cancellation, G.168 (NLP<br>incl.):<br>– LEC 32 ms<br>– LEC 64 ms<br>– LEC 128 ms                                                | PCM, ALM,<br>Coder   | 11.0<br>17.0<br>29.0 | 4                                                  |

| G.711 (block based [5,5ms]):<br>G.711, G.711 Annex I (BFI), G.711 Annex II<br>(VAD, CNG), jitter buffer, protocol handling<br>G.711 (sample based) | Coder<br>PCM         | 5.0 <sup>5)</sup>    | 8                                                  |

#### Signalprocessing Capabilities of the VINETIC®

#### Table 4Provided Algorithms for VINETIC<sup>®1</sup> (cont'd)

| Algorithm/Function                                                                    | Module <sup>2)</sup> | MCycle/s           | max. # of<br>ressources<br>available <sup>3)</sup> |

|---------------------------------------------------------------------------------------|----------------------|--------------------|----------------------------------------------------|

| G.711 Annex I (BFM)                                                                   | Coder                | 0.6                | 8                                                  |

| G.711 Annex II (VAD + CNG)                                                            | Coder                | 0.7                | 8                                                  |

| G.726 for Coder Module (block based [11ms])<br>G.726 for PCM Module (sample based)    | Coder                | 11.4 <sup>5)</sup> | 8                                                  |

|                                                                                       | PCM                  | 5.5                |                                                    |

| G.723.1 (packet size 30 ms)                                                           | Coder                | 12.4 <sup>5)</sup> | 4                                                  |

| G.729 A, B (packet size 10, 20 ms)                                                    | Coder                | 10.7 <sup>5)</sup> | 4                                                  |

| G.729 A, B, E (packet size 10, 20 ms)                                                 | Coder                | 20.9 <sup>5)</sup> | 4                                                  |

| G.728 (packet size 5, 10, 15, 20 ms) incl.<br>G.728 Annex I (Packet Loss Concealment) | Coder                | 19.5 <sup>5)</sup> | 4                                                  |

| Automatic Gain Control AGC                                                            | Coder                | 0.7                | 8                                                  |

| T.38                                                                                  | Coder                | (typ. 10)          | 4                                                  |

<sup>1)</sup> not all algorithms/functions are supported with all devices. See **Table 3 on Page 13** for details.

<sup>2)</sup> Refer to **Chapter 7** for the definition of the modules

<sup>3)</sup> not all devices and all firmware versions support all the given number of resources. A firmware status sheet is available showing the exact number of resources available per version.

<sup>4)</sup> DTMF generation can be realized by using EDSP ressources or by using the integrated ALM tone generators. Using the integrated ALM tone generators doesn't allocate EDSP ressources.