**Data Sheet**

November 2006

**Features**

- Meets requirements of GR-253 for SONET Stratum 3 and SONET Minimum Clocks (SMC)

- Meets requirements of GR-1244 for Stratum 3

- Meets requirements of G.813 Option 1 and 2 for SDH Equipment Clocks (SEC)

- Generates clocks for ST-BUS, DS1, DS2, DS3, OC-3, E1, E3, STM-1 and 19.44 MHz

- Holdover accuracy of 4x10 <sup>-12</sup> meets GR-1244 Stratum 3E and ITU-T G.812 requirements

- Continuously monitors both references for frequency accuracy exceeding ±12 ppm

- · Provides "hit-less" reference switching

- Compensates for Master Clock Oscillator accuracy

- Automatically detects frequency of both reference clocks and synchronizes to any combination of 8 kHz, 1.544 MHz, 2.048 MHz and 19.44 MHz reference frequencies

- Allows Hardware or Microprocessor control

- Pin compatible with ZL30410, ZL30402 and MT90401

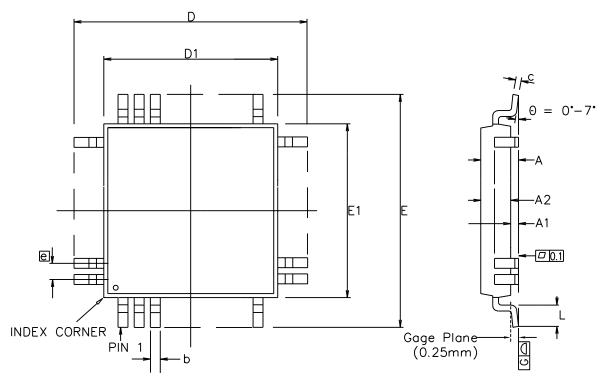

#### Ordering Information

ZL30407QCC 80 Pin LQFP Trays ZL30407QCG1 80 Pin LQFP\* Trays, Bake & Drypack

\*Pb Free Matte Tin

-40°C to +85°C

### **Applications**

- Synchronization for SDH and SONET Network Elements

- · Clock generation for ST-BUS and GCI backplanes

## **Description**

The ZL30407 is a Network Element Phase-Locked Loop designed to synchronize SDH and SONET systems. In addition, it generates multiple clocks for legacy PDH equipment and provides timing for ST-BUS and GCI backplanes.

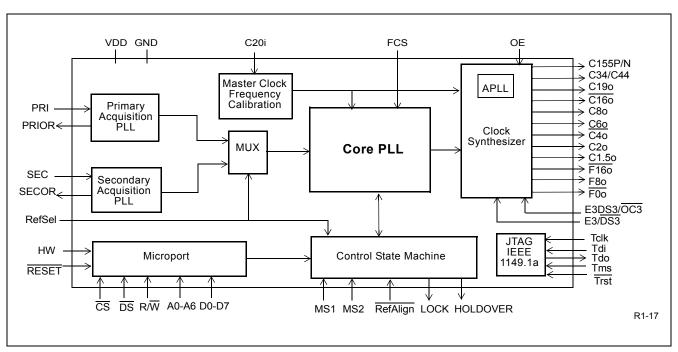

Figure 1 - Functional Block Diagram

The ZL30407 operates in NORMAL (LOCKED), HOLDOVER and FREE-RUN modes to ensure that in the presence of jitter, wander and interruptions to the reference signals, the generated clocks meet international standards. The filtering characteristics of the PLL are hardware or software selectable and they do not require any external adjustable components. The ZL30407 uses an external 20 MHz Master Clock Oscillator to provide a stable timing source for the HOLDOVER operation.

The ZL30407 operates from a single 3.3 V power supply and offers a 5 V tolerant microprocessor interface.

## **Table of Contents**

|            | Change Summary                                                               |     |

|------------|------------------------------------------------------------------------------|-----|

| 2.0        | ZL30407 Pinout                                                               | 6   |

|            | 2.1 Pin Connections                                                          |     |

| 3 N        | Functional Description                                                       |     |

|            | 3.1 Acquisition PLLs                                                         |     |

|            | 3.2 Core PLL                                                                 |     |

|            | 3.2.1 Digitally Controlled Oscillator (DCO)                                  |     |

|            | 3.2.2 Filters                                                                |     |

|            | 3.2.3 Phase Slope Limiters                                                   |     |

|            |                                                                              |     |

|            | 3.2.4 Lock Indicator (LOCK)                                                  |     |

|            | 3.2.5 Reference Alignment (RefAlign)                                         | 14  |

|            | 3.2.5.1 Using RefAlign with 1.544 MHz, 2.048 MHz or 19.44 MHz Reference      |     |

|            | 3.2.5.2 Using RefAlign with an 8 kHz Reference                               |     |

|            | 3.3 Clock Synthesizer                                                        |     |

|            | 3.3.1 Output Clocks                                                          |     |

|            | 3.3.2 Output Clocks Phase Adjustment                                         |     |

|            | 3.4 Control State Machine                                                    |     |

|            | 3.4.1 Clock Modes                                                            |     |

|            | 3.4.2 ZL30407 State Machine                                                  | 17  |

|            | 3.4.2.1 Reset State                                                          | 18  |

|            | 3.4.2.2 Free-Run State (Free-Run mode)                                       | 18  |

|            | 3.4.2.3 Normal State (Normal Mode or Locked Mode)                            | 18  |

|            | 3.4.2.4 Holdover State (Holdover Mode)                                       |     |

|            | 3.4.2.5 Auto Holdover State                                                  |     |

|            | 3.4.3 State Transitions                                                      |     |

|            | 3.5 Master Clock Frequency Calibration Circuit                               |     |

|            | 3.6 Microprocessor Interface                                                 |     |

|            | 3.7 JTAG Interface                                                           |     |

| 4 0        | Hardware and Software Control                                                |     |

| 4.0        | 4.1 Hardware Control                                                         |     |

|            |                                                                              |     |

|            | 4.1.1 Control Pins                                                           |     |

|            | 4.1.2 Status Pins                                                            |     |

|            | 4.2 Software Control                                                         |     |

|            | 4.2.1 Control Bits.                                                          |     |

|            | 4.2.2 ZL30407 Register Map                                                   |     |

| <b>5.0</b> | Applications                                                                 |     |

|            | 5.1 ZL30407 Mode Switching - Examples                                        |     |

|            | 5.1.1 System Start-up Sequence: FREE-RUN> HOLDOVER> NORMAL                   |     |

|            | 5.1.2 Single Reference Operation: NORMAL> AUTO HOLDOVER> NORMAL              | 35  |

|            | 5.1.3 Single 8 kHz Reference Operation: NORMAL> AUTO HOLDOVER> HOLDOVER> NOR | MAL |

|            | 36                                                                           |     |

|            | 5.1.4 Dual Reference Operation: NORMAL> AUTO HOLDOVER> HOLDOVER> NORMAL      | 37  |

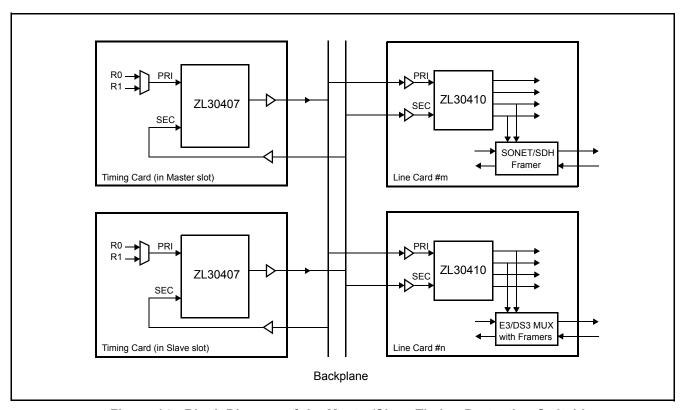

|            | 5.2 Master/Slave Timing Protection Switching                                 |     |

|            | 5.3 Programming Master Clock Oscillator Frequency Calibration Register       |     |

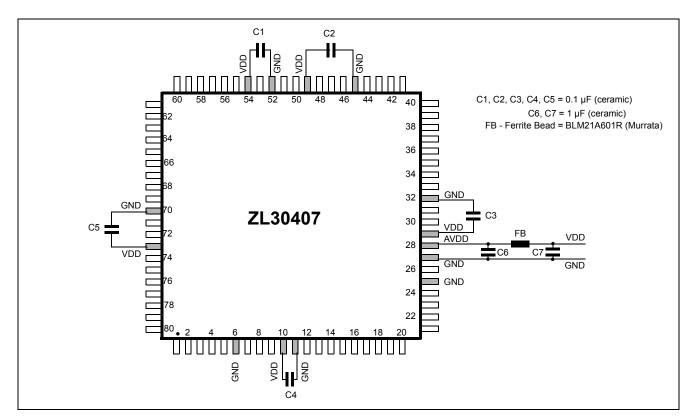

|            | 5.4 Power supply filtering                                                   |     |

| e 0        | Characteristics                                                              |     |

| u.U        | 6.1 AC and DC Electrical Characteristics                                     |     |

|            | 6.1 AC and DC Electrical Characteristics                                     | 41  |

|            |                                                                              |     |

## ZL30407

# **List of Figures**

| Figure 1 - Functional Block Diagram                                                                    | 1     |

|--------------------------------------------------------------------------------------------------------|-------|

| Figure 2 - Pin Connections for 80-pin LQFP package                                                     |       |

| Figure 3 - Core PLL Functional Block Diagram                                                           |       |

| Figure 4 - C34/C44, C155o Clock Generation Options                                                     | 17    |

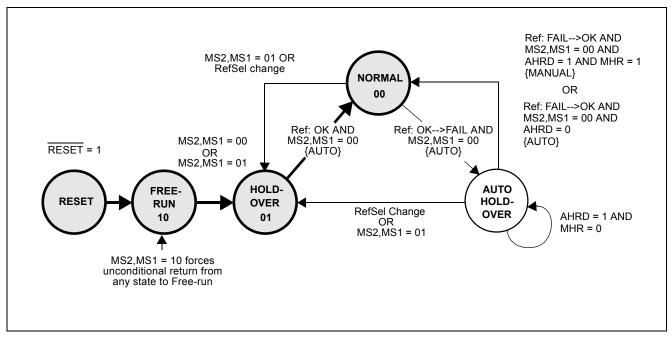

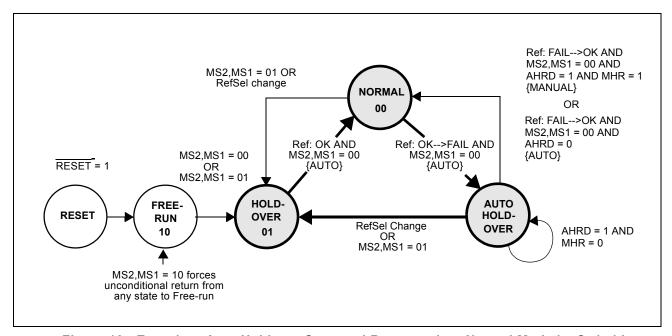

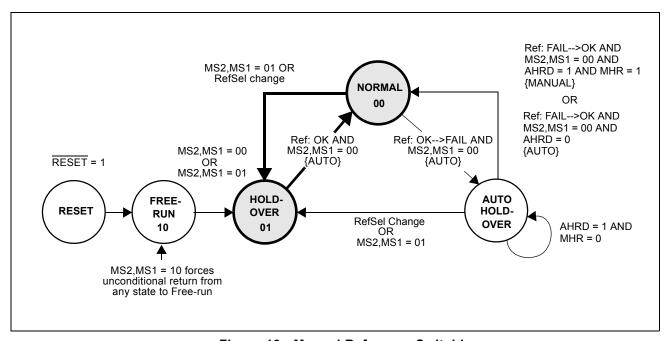

| Figure 5 - ZL30407 State Machine in Software Control configuration                                     | 18    |

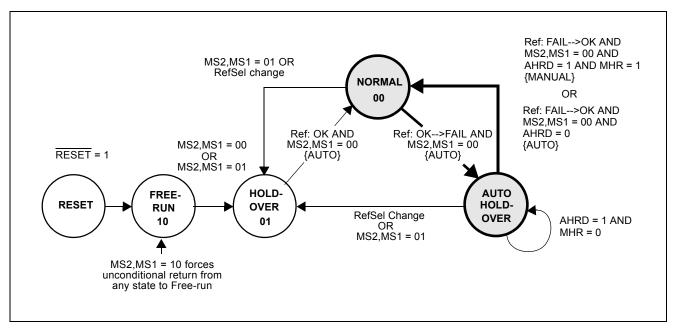

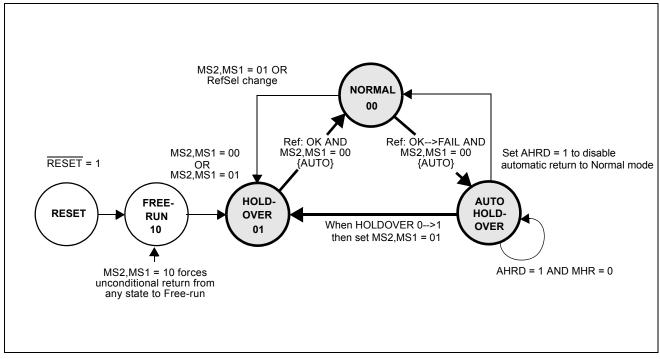

| Figure 6 - ZL30407 State Machine in Hardware Control configuration                                     | 19    |

| Figure 7 - Hardware and Software Control Options                                                       | 22    |

| Figure 8 - Primary and Secondary Reference Out of Range Thresholds                                     | 27    |

| Figure 9 - Transition From Free-run to Normal Mode                                                     | 34    |

| Figure 10 - Automatic Entry into Auto Holdover State and Recovery into Normal Mode                     | 35    |

| Figure 11 - Recovery Procedure From a Single 8 kHz Reference Failure by Transitioning Through the Hold | dover |

| State                                                                                                  | 36    |

| Figure 12 - Entry into Auto Holdover State and Recovery into Normal Mode by Switching References       | 37    |

| Figure 13 - Manual Reference Switching                                                                 | 38    |

| Figure 14 - Block Diagram of the Master/Slave Timing Protection Switching                              | 39    |

| Figure 15 - Power Supply Filtering                                                                     | 40    |

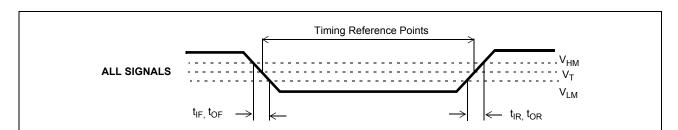

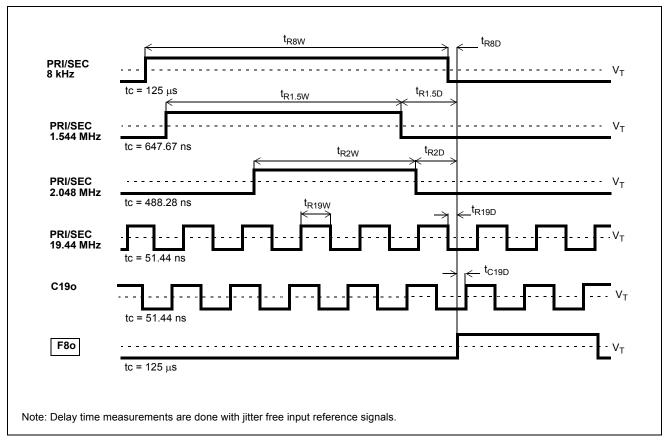

| Figure 16 - Timing Parameters Measurement Voltage Levels                                               |       |

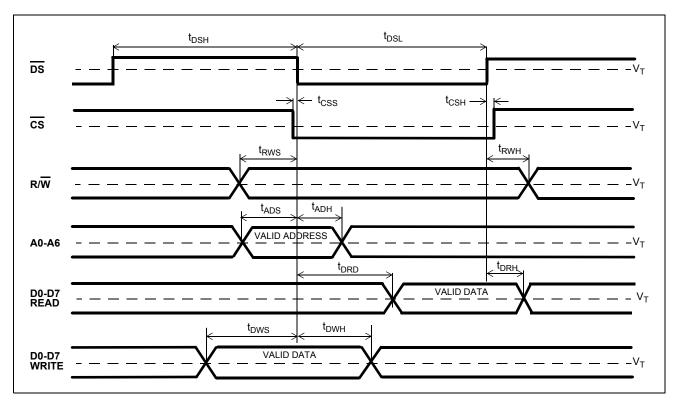

| Figure 17 - Microport Timing                                                                           | 43    |

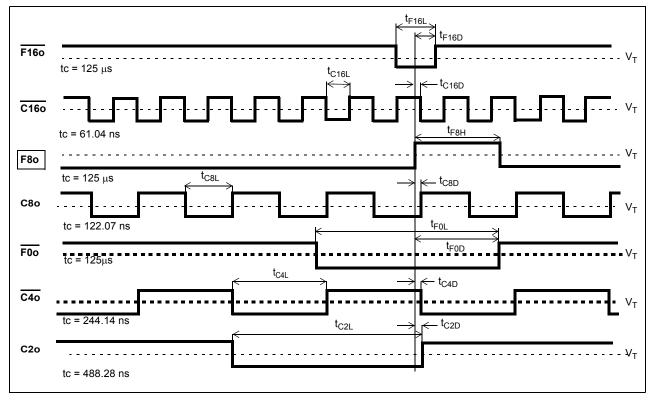

| Figure 18 - ST-BUS and GCI Output Timing                                                               | 44    |

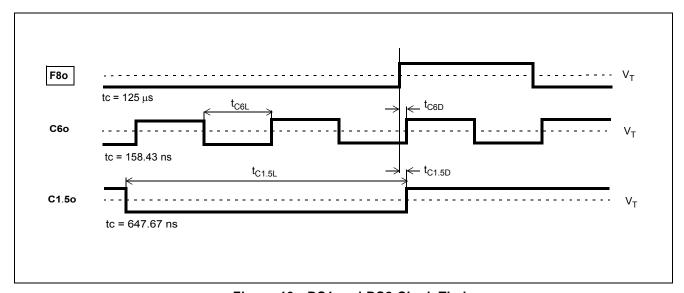

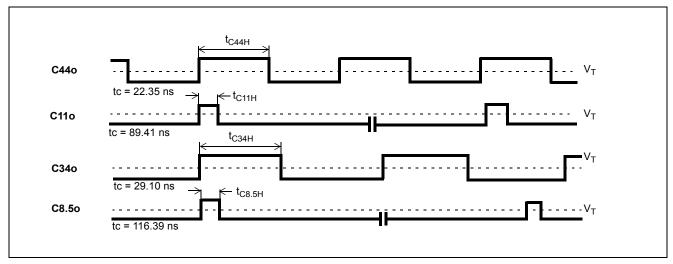

| Figure 19 - DS1 and DS2 Clock Timing                                                                   | 45    |

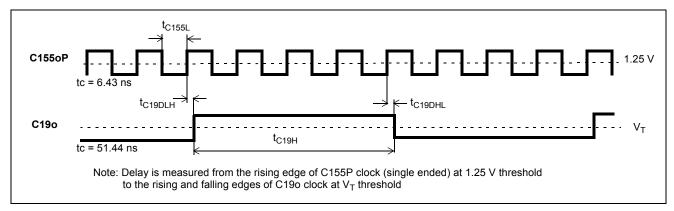

| Figure 20 - C155o and C19o Timing                                                                      | 46    |

| Figure 21 - Input Reference to Output Clock Phase Offset                                               | 47    |

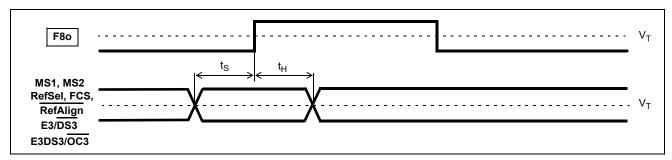

| Figure 22 - Input Control Signal Setup and Hold Time                                                   | 48    |

| Figure 23 - E3 and DS3 Output Timing                                                                   | 48    |

## **List of Tables**

| Table 1 - Loop Filter Selection                                | . 13 |

|----------------------------------------------------------------|------|

| Table 2 - Operating Modes and States                           | . 22 |

| Table 3 - Filter Characteristic Selection                      |      |

| Table 4 - Reference Source Select                              | . 23 |

| Table 5 - ZL30407 Register Map                                 | . 24 |

| Table 6 - Control Register 1 (R/W)                             | . 25 |

| Table 7 - Status Register 1 (R)                                | . 26 |

| Table 8 - Control Register 2 (R/W)                             | . 27 |

| Table 9 - Phase Offset Register 2 (R/W)                        | . 28 |

| Table 10 - Phase Offset Register 1 (R/W)                       | . 28 |

| Table 11 - Device ID Register (R)                              | . 28 |

| Table 12 - Control Register 3 (R/W)                            | . 29 |

| Table 13 - Clock Disable Register 1 (R/W)                      | . 29 |

| Table 14 - Clock Disable Register 2 (R/W)                      | . 30 |

| Table 15 - Core PLL Control Register (R/W)                     | . 30 |

| Table 16 - Fine Phase Offset Register (R/W)                    | . 31 |

| Table 17 - Primary Acquisition PLL Status Register (R)         | . 31 |

| Table 18 - Secondary Acquisition PLL Status Register (R)       | . 32 |

| Table 19 - Master Clock Frequency Calibration Register 4 (R/W) | . 32 |

| Table 20 - Master Clock Frequency Calibration Register 3 (R/W) | . 32 |

| Table 21 - Master Clock Frequency Calibration Register 2 (R/W) | . 32 |

| Table 22 - Master Clock Frequency Calibration Register 1 (R/W) | 33   |

## 1.0 Change Summary

Changes from March 2006 Issue to November 2006 Issue. Page, section, figure and table numbers refer to this current issue.

| Page | Item      | Change            |

|------|-----------|-------------------|

| 47   | Figure 21 | Adjusted drawing. |

Changes from November 2004 Issue to March 2006 Issue. Page, section, figure and table numbers refer to this current issue.

| Page | Item | Change                       |

|------|------|------------------------------|

|      |      | Updated Ordering Information |

### 2.0 ZL30407 Pinout

#### 2.1 Pin Connections

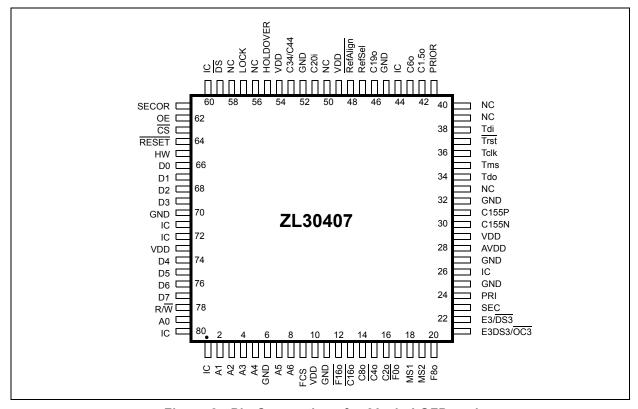

Figure 2 - Pin Connections for 80-pin LQFP package

## **Pin Description**

| Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IC    | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                        |

| 2-5   | A1-A4 | Address 1 to 4 (5 V tolerant input). Address inputs for the parallel processor interface. Connect to ground in Hardware Control.                                                                                                                                                                                                                                                                                               |

| 6     | GND   | Ground. Negative power supply.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7-8   | A5-A6 | Address 5 to 6 (5 V tolerant input). Address inputs for the parallel processor interface. Connect to ground in Hardware Control.                                                                                                                                                                                                                                                                                               |

| 9     | FCS   | <b>Filter Characteristic Select</b> (Input). In Hardware Control, FCS selects the filtering characteristics of the ZL30407. Set this pin high to have a loop filter corner frequency of 0.1 Hz and limit the phase slope to 885 ns/sec. Set this pin low to have corner frequency of 1.5 Hz and limit the phase slope to 41 ns per 1.326 ms. Connect to ground in Software Control. This pin is internally pulled down to GND. |

| 10    | VDD   | Positive Power Supply                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11    | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12    | F160  | <b>Frame Pulse ST-BUS 8.192 Mbps</b> (CMOS tristate output). This is an 8 kHz, 61 ns wide, active low framing pulse, which marks beginning of a ST-BUS frame. This frame pulse is typically used for ST-BUS operation at 8.192 Mbps.                                                                                                                                                                                           |

| 13    | C160  | Clock 16.384 MHz (CMOS tristate output). This clock is used for ST-BUS operation at 8.192 Mbps.                                                                                                                                                                                                                                                                                                                                |

| 14    | C8o   | Clock 8.192 MHz (CMOS tristate output). This clock is used for ST-BUS operation at 8.192 Mbps.                                                                                                                                                                                                                                                                                                                                 |

| 15    | C4o   | Clock 4.096 MHz (CMOS tristate output). This clock is used for ST-BUS operation at 2.048 Mbps.                                                                                                                                                                                                                                                                                                                                 |

| 16    | C2o   | Clock 2.048 MHz (CMOS tristate output). This clock is used for ST-BUS operation at 2.048 Mbps.                                                                                                                                                                                                                                                                                                                                 |

| 17    | F0o   | <b>Frame Pulse ST-BUS 2.048 Mbps</b> (CMOS tristate output). This is an 8 kHz, 244 ns, active low framing pulse, which marks the beginning of a ST-BUS frame. This is typically used for ST-BUS operation at 2.048 Mbps and 4.096 Mbps.                                                                                                                                                                                        |

| 18    | MS1   | Mode Select 1 (Input). The MS1 and MS2 pins select the ZL30407 mode of operation (Normal, Holdover or Free-run), see Table 2 on page 22 for details. The logic level at this input is sampled by the rising edge of the F80 frame pulse. Connect to ground in Software Control.                                                                                                                                                |

| 19    | MS2   | Mode Select 2 (Input). The MS2 and MS1 pins select the ZL30407 mode of operation (Normal, Holdover or Free-run), see Table 2 on page 22 for details. The logic level at this input is sampled by the rising edge of the F80 frame pulse. Connect to ground in Software Control.                                                                                                                                                |

| Pin#     | Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20       | F8o            | Frame Pulse ST-BUS/GCI 8.192 Mbps (CMOS tristate output). This is an 8 kHz, 122 ns, active high framing pulse, which marks the beginning of a ST-BUS/GCI frame. This is typically used for ST-BUS/GCI operation at 8.192 Mbps. See Figure 18 for details.                                                                                                                                                                                             |

| 21       | E3DS3/OC3      | <b>E3DS3 or OC3 Selection</b> (Input). In Hardware Control, a logic low on this pin enables the C155P/N outputs (pin 30 and pin 31) and sets the C34/C44 output (pin 53) to provide C8 or C11 clocks. Logic high at this input disables the C155 clock outputs (high impedance) and sets C34/C44 output to provide C34 and C44 clocks. In Software Control connect this pin to ground.                                                                |

| 22       | E3/DS3         | E3 or DS3 Selection (Input). In Hardware Control, when the E3DS3/OC3 pin is set high, logic low on E3/DS3 pin selects a 44.736 MHz clock on C34/C44 output and logic high selects 34.368 MHz clock. When E3DS3/OC3 pin is set low, logic low on E3/DS3 pin selects 11.184 MHz clock on C34/C44 output and logic high selects 8.592 MHz clock. Connect this input to ground in Software Control.                                                       |

| 23       | SEC            | Secondary Reference (Input). This input is used as a secondary reference source for synchronization. The ZL30407 can synchronize to the falling edge of the 8 kHz, 1.544 MHz or 2.048 MHz clocks and the rising edge of the 19.44 MHz clock. In Hardware Control, selection of the input reference is based upon the RefSel control input. This pin is internally pulled up to VDD.                                                                   |

| 24       | PRI            | <b>Primary Reference</b> (Input). This input is used as a primary reference source for synchronization. The ZL30407 can synchronize to the falling edge of the 8 kHz, 1.544 MHz or 2.048 MHz clocks and the rising edge of the 19.44 MHz clock. In Hardware Control, selection of the input reference is based upon the RefSel control input. This pin is internally pulled up to VDD.                                                                |

| 25       | GND            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 26       | IC             | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 27       | GND            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28       | AVDD           | Positive Analog Power Supply. Connect this pin to VDD.                                                                                                                                                                                                                                                                                                                                                                                                |

| 29       | VDD            | Positive Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30<br>31 | C155N<br>C155P | Clock 155.52 MHz (LVDS output). Differential outputs for the $155.52$ MHz clock. These outputs are enabled by applying logic low to E3DS3/OC3 input or they can be disabled by applying logic high. In the disabled state the LVDS outputs are internally terminated with an integrated $100\Omega$ resistor (two $50\Omega$ resistors connected in series). The middle point of these resistors is internally biased from a 1.25 V LVDS bias source. |

| 32       | GND            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 33       | NC             | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin # | Name     | Description                                                                                                                                                                                                                                                                                                                                             |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34    | Tdo      | <b>IEEE1149.1a Test Data Output</b> (CMOS output). JTAG serial data is output on this pin on the falling edge of Tclk clock. If not used, this pin should be left unconnected.                                                                                                                                                                          |

| 35    | Tms      | <b>IEEE1149.1a Test Mode Selection</b> (3.3 V input). JTAG signal that controls the state transition on the TAP controller. This pin is internally pulled up to VDD. If not used, this pin should be left unconnected.                                                                                                                                  |

| 36    | Tclk     | <b>IEEE1149.1a Test Clock Signal</b> (5 V tolerant input). Input clock for the JTAG test logic. If not used, this pin should be pulled up to VDD.                                                                                                                                                                                                       |

| 37    | Trst     | <b>IEEE1149.1a Reset Signal</b> (3.3 V input). Asynchronous reset for the JTAG TAP controller. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to VDD. If this pin is not used then it should be connected to GND.                                              |

| 38    | Tdi      | <b>IEEE1149.1a Test Data Input</b> (3.3 V input). Input for JTAG serial test instructions and data. This pin is internally pulled up to VDD. If not used, this pin should be left unconnected.                                                                                                                                                          |

| 39    | NC       | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                      |

| 40    | NC       | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                      |

| 41    | PRIOR    | <b>Primary Reference Out of Range</b> (Output). Logic high at this pin indicates that the Primary Reference is off the PLL centre frequency by more than ±12ppm. These thresholds support Stratum 3 applications. See PRIOR bit description in Status Register 1 for details.                                                                           |

| 42    | C1.50    | Clock 1.544 MHz (CMOS tristate output). This output provides a 1.544 MHz DS1 rate clock.                                                                                                                                                                                                                                                                |

| 43    | C6o      | Clock 6.312 MHz (CMOS tristate output). This output provides a 6.312 MHz DS2 rate clock.                                                                                                                                                                                                                                                                |

| 44    | IC       | Internal Connection. Connect this pin to Ground.                                                                                                                                                                                                                                                                                                        |

| 45    | GND      | Ground                                                                                                                                                                                                                                                                                                                                                  |

| 46    | C19o     | Clock 19.44 MHz (CMOS tristate output). This output provides a 19.44 MHz clock.                                                                                                                                                                                                                                                                         |

| 47    | RefSel   | Reference Source Select (Input). A logic low selects the PRI (primary) reference source as the input reference signal and logic high selects the SEC (secondary) input. The logic level at this input is sampled at the rising edge of F8o. This pin is internally pulled down to GND.                                                                  |

| 48    | RefAlign | Reference Alignment (Input). In Hardware Control pulling this pin low for 250 $\mu$ s initiates phase realignment between the input reference and the generated output clocks. This pin should never be tied low permanently. Please see Section 3.2.5, Reference Alignment (RefAlign) for more information. Internally this pin is pulled down to GND. |

| Pin# | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49   | VDD      | Positive Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 50   | NC       | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 51   | C20i     | Clock 20 MHz (5 V tolerant input). This pin is the input for the 20 MHz Master Clock Oscillator. The clock oscillator should be connected directly (not AC coupled) to the C20i input and it must supply clock with duty cycle that is not worse than 40/60%.                                                                                                                                                                                      |

| 52   | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 53   | C34/C44  | Clock 34.368 MHz / clock 44.736 MHz (CMOS Output). This clock is programmable to be either 34.368 MHz (for E3 applications) or 44.736 MHz (for DS3 applications) when E3DS3/OC3 is high, or to be either 8.592 MHz or 11.184 MHz when E3DS3/OC3 is low. See description of E3DS3/OC3 and E3/DS3 inputs for details. In Software Control the functionality of this output is controlled by Control Register 2 (Table 8 "Control Register 2 (R/W)"). |

| 54   | VDD      | Positive Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 55   | HOLDOVER | <b>Holdover Indicator</b> (CMOS output). Logic high at this output indicates that the device is in Holdover mode.                                                                                                                                                                                                                                                                                                                                  |

| 56   | NC       | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 57   | LOCK     | <b>Lock Indicator</b> (CMOS output). Logic high at this output indicates that ZL30407 is locked to the input reference. See LOCK bit description in Status Register 1 and Section 3.2.4, Lock Indicator (LOCK) for details.                                                                                                                                                                                                                        |

| 58   | NC       | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 59   | DS       | <b>Data Strobe</b> (5 V tolerant input). This input is the active low data strobe of the processor interface.                                                                                                                                                                                                                                                                                                                                      |

| 60   | IC       | Internal Connection. Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 61   | SECOR    | Secondary Reference Out of Range (Output). Logic high at this pin indicates that the Secondary Reference is off the PLL centre frequency by more than ±12 ppm. These thresholds support Stratum 3 applications. See SECOR bit description in Status Register 1 for details.                                                                                                                                                                        |

| 62   | OE       | Output Enable (Input). Logic high on this input enables C19, F16, C16, C8, C6, C4, C2, C1.5, F8 and F0 signals. Pulling this input low will force the output clocks pins into a high impedance state.                                                                                                                                                                                                                                              |

| 63   | CS       | Chip Select (5 V tolerant input). This active low input enables the microprocessor interface. When CS is set to high, the microprocessor interface is idle and all Data Bus I/O pins will be in a high impedance state.                                                                                                                                                                                                                            |

| Pin#    | Name    | Description                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64      | RESET   | <b>RESET</b> (5 V tolerant input). The ZL30407 must be reset after power-up in order to set internal registers into a default state. The internal reset is performed by forcing RESET pin low for a minimum of 1 $\mu$ s after the C20 Master Clock is applied to pin C20i. This operation forces the ZL30407 internal state machine into a RESET state for a duration of 625 $\mu$ s. |

| 65      | HW      | Hardware/Software Control (Input). If this pin it tied low, the ZL30407 is controlled via the microport. If it is tied high, the ZL30407 is controlled via the control pins MS1, MS2, FCS, RefSel, RefAlign, E3/DS3 and E3DS3/OC3.                                                                                                                                                     |

| 66-69   | D0 - D3 | <b>Data 0 to Data 3</b> (5 V tolerant three-state I/O). These ports combined with D4 - D7 ports form the bi-directional data bus of the microprocessor interface (D0 is the least significant bit).                                                                                                                                                                                    |

| 70      | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                 |

| 71      | IC      | Internal Connection (Input). Connect this pin to ground.                                                                                                                                                                                                                                                                                                                               |

| 72      | IC      | Internal Connection (Input). Connect this pin to ground.                                                                                                                                                                                                                                                                                                                               |

| 73      | VDD     | Positive Power Supply                                                                                                                                                                                                                                                                                                                                                                  |

| 74 - 77 | D4 - D7 | <b>Data 4 to Data 7</b> (5 V tolerant three-state I/O). These ports combined with D0 - D3 ports form the bi-directional data bus of the processor interface (D7 is the most significant bit).                                                                                                                                                                                          |

| 78      | R/W     | <b>Read/Write Strobe</b> (5 V tolerant input). This input controls the direction of the data bus D[0-7] during a microprocessor access. When R/W is high, the parallel processor is reading data from the ZL30407. When low, the parallel processor is writing data to the ZL30407.                                                                                                    |

| 79      | A0      | Address 0 (5 V tolerant input). Address input for the microprocessor interface. A0 is the least significant input.                                                                                                                                                                                                                                                                     |

| 80      | IC      | Internal Connection (Input). Connect this pin to ground.                                                                                                                                                                                                                                                                                                                               |

## 3.0 Functional Description

The ZL30407 is a Network Element PLL designed to provide timing for SDH and SONET equipment conforming to ITU-T, ANSI, ETSI and Telcordia recommendations. In addition, it generates clocks for legacy PDH equipment operating at DS1, DS2, DS3, E1, and E3 rates. The ZL30407 provides clocks for industry standard ST-BUS and GCI backplanes, and it also supports H.110 timing requirements. The functional block diagram of the ZL30407 is shown in the "Functional Block Diagram" on page 1 and its operation is described in the following sections.

## 3.1 Acquisition PLLs

The ZL30407 has two Acquisition PLLs for monitoring the availability and quality of the Primary (PRI) and Secondary (SEC) reference clocks. Each Acquisition PLL operates independently and locks to the falling edges of one of the three input reference frequencies: 8 kHz, 1.544 MHz, 2.048 MHz or to the rising edges of 19.44 MHz. The reference frequency is continuously measured and its current frequency can be determined from reading the Acquisition PLL Status Register bits InpFreq1 and InpFreq0 (see Table 17 "Primary Acquisition PLL Status Register (R)" and Table 18 "Secondary Acquisition PLL Status Register (R)").

The Primary and Secondary Acquisition PLLs are designed to provide status information that identifies two levels of reference clock quality. For clarity, only the Primary Acquisition PLL is referenced in the text, but the same applies to the Secondary Acquisition PLL.

- Reference frequency drifts more than ±12 ppm. In response, the PRIOR (Primary Reference Out of Range) bit and pin change state to high, in conformance with Stratum 3 requirements defined in GR-1244-CORE. The PRIOR bit is part of Status Register 1 (Table 7 "Status Register 1 (R)").

- Reference frequency drifted more than ±30000 ppm or that the reference has been lost completely. In response, the Primary Acquisition PLL enters its own Holdover mode and indicates this by asserting the HOLDOVER bit in the Primary Acquisition PLL Status Register (Table 17 "Primary Acquisition PLL Status Register (R)"). Entry into Holdover forces the Core PLL into the Auto Holdover state.

Outputs of both Acquisition PLLs are connected to a multiplexer (MUX), which allows selection of the desired reference. This multiplexer channels binary words to the Core PLL digital phase detector (instead of analog signals) which eliminates quantization errors and improves phase alignment accuracy. The bandwidth of the Acquisition PLL is much wider than the bandwidth of the following Core PLL. This feature allows cascading Acquisition and Core PLLs without altering the transfer function of the Core PLL.

## 3.2 Core PLL

The most critical element of the ZL30407 is its Core PLL, which generates a phase-locked clock, filters jitter and wander and suppresses input phase transients. All of these features are in agreement with international standards:

- G.813 Option 1 and 2 clocks for SDH equipment

- GR-253 for SONET Stratum 3 and SONET Minimum Clocks (SMC)

- · GR-1244 for Stratum 3 Clock

The Core PLL supports three mandatory modes of operation: Free-run, Normal (Locked) and Holdover. Each of these modes places specific requirements on the building blocks of the Core PLL.

- In Free-run Mode, the Core PLL derives its output clock from the 20 MHz Master Clock Oscillator connected to pin C20i. The stability of the generated clocks remain the same as the stability of the Master Clock Oscillator.

- In Normal Mode, the Core PLL locks to one of the Acquisition PLLs. Both Acquisition PLLs provide preprocessed phase data to the Core PLL including detection of reference clock quality.

- In Holdover mode, the Core PLL generates a clock based on data collected from past reference signals. The

Core PLL enters Holdover mode if the attached Acquisition PLL switches into the Holdover state or under

external software or hardware control.

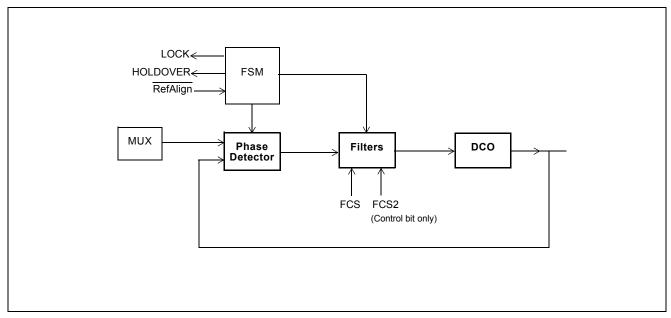

Some of the key elements of the Core PLL are shown in Figure 3 "Core PLL Functional Block Diagram".

Figure 3 - Core PLL Functional Block Diagram

### 3.2.1 Digitally Controlled Oscillator (DCO)

The DCO is an arithmetic unit that continuously generates a stream of numbers that represent the phase-locked clock. These numbers are passed to the Clock Synthesizer (see section 3.3) where they are converted into electrical clock signals of various frequencies

#### 3.2.2 Filters

In Normal mode, the clock generated by the DCO is phase-locked to the input reference signal and band-limited to meet network synchronization standards. The ZL30407 provides four software programmable (FCS bit in Control Reg 1 and FCS2 bit in Control Reg 3) and two hardware selectable (FCS pin) filtering options. The filtering characteristics are similar to a first order low pass filter with corner frequencies that support international standards:

| FCS2<br>(bit) | FCS<br>(pin/bit) | Filter | Conformance                                                                                                                                                                   |

|---------------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0                | 1.5 Hz | Meets requirements of G.813 Option 1 and GR-1244 stratum 3 clocks. The maximum phase slope is limited to 41 ns in 1.326 ms.                                                   |

| 0             | 1                | 0.1 Hz | Meets requirements of G.813 Option 2, GR-253 for SONET stratum 3 and GR-253 for SONET Minimum Clocks (SMC). The maximum phase slope is limited to 885 ns in one second.       |

| 1             | 0                | 12 Hz  | There is no phase slope limiter active in this application.                                                                                                                   |

| 1             | 1                | 6 Hz   | Meets requirements of G.813 Option 1 for SDH Equipment Clocks (SEC) and GR-1244 for Stratum 4 and Stratum 4E clocks. The maximum phase slope is limited to 50 ns in 1.326 ms. |

**Table 1 - Loop Filter Selection**

#### 3.2.3 Phase Slope Limiters

Phase slope limiting is achieved by clamping the size of the error term from the phase detector. Limiting the size of the error term means that the output clocks move slowly in phase as the PLL aligns to phase transients on the input reference or transients caused by reference rearrangement. This increases the time required to achieve phase lock, but it is necessary to allow for downstream adjustments and so is called for in network standards such as G.813, GR-1244 and GR-253. Because the ZL30407 nulls out the phase offset between the output clocks and the selected reference upon reference rearrangement or return from holdover, the phase slope limiting feature will generally not come into play. If the pin RefAlign is pulled low to align the equivalent ZL30407 output clock to the selected reference, a large phase error will have to be corrected. In this case phase slope limiting will be active, limiting the output phase slope to 0.727 ppm for the 0.1 Hz filter mode, 31 ppm for the 1.5 Hz and the 6 Hz filter mode. In the 12 Hz mode there is no phase slope limiting. Consequently an output phase slope greater than 31 ppm may occur, for example, in locking to an orthogonal 8 kHz reference.

#### 3.2.4 Lock Indicator (LOCK)

The ZL30407 is considered locked (LOCK = 1) when the residual phase movement after declaring locked condition does not exceed standard wander generation MTIE and TDEV tests. The ZL30407's phase locking mechanism allows it to lock within the specified locking times to references with a fractional frequency offset of up to  $\pm 20$  ppm. Locking time for different filters and pulling ranges is listed in "Performance Characteristics\*" on page 49.

## 3.2.5 Reference Alignment (RefAlign)

When the ZL30407 finishes locking to a reference an arbitrary phase difference will remain between its output clocks and its reference; this phase difference is part of the normal operation of the ZL30407. If so desired, the output clocks can be brought into phase alignment with the PLL reference (see Figure 21 on page 47) by using the RefAlign control bit/pin.

## 3.2.5.1 Using RefAlign with 1.544 MHz, 2.048 MHz or 19.44 MHz Reference

If the ZL30407 is locked to a 1.544 MHz, 2.048 MHz or 19.44 MHz reference, then the output clocks can be brought into phase alignment with the PLL reference by using the RefAlign control bit/pin according to one of the procedures below:

#### 1. For 0.1 Hz filtering applications (FCS = 1, FCS2 = 0)

- Wait until the ZL30407 LOCK indicator is high, indicating that it is locked

- Pull FCS low

- Pull Ref/Align low

- Hold RefAlign low for 250 μs

- Pull RefAlign high

- Wait until the LOCK indicator goes high

- Pull FCS high

After initiating a reference realignment the PLL will enter Holdover mode for 200ns while aligning the internal clocks to remove the static phase error. The PLL will then begin the normal locking procedure. The LOCK pin will go low 5 sec after the reference realignment is initiated and will remain low for 10 sec.

#### 2. For 1.5 Hz filtering applications (FCS = 0, FCS2 = 0)

- Wait until the ZL30407 LOCK indication is high, indicating that it is locked

- Pull RefAlign low

- Hold RefAlign low for 250 μs

- Pull RefAlign high

After initiating a reference realignment the PLL will enter Holdover mode for 200ns while aligning the internal clocks to remove the static phase error. The PLL will then begin the normal locking procedure. The LOCK pin will go low 5 sec after the reference realignment is initiated and will remain low for 10 sec

### 3. For 6 Hz and 12 Hz filtering applications (FCS = 1, FCS2 = 1 or FCS = 0, FCS2 = 1)

- Wait until the ZL30407 LOCK indication is high, indicating that it is locked

- Pull RefAlign low

- Hold RefAlign low for 250 μs

- Pull RefAlign high

After initiating a reference realignment the PLL will enter Holdover mode for 200 ns while aligning the internal clocks to remove the static phase error. The PLL will then begin the normal locking procedure. The LOCK pin will remain high during the realignment process.

## 3.2.5.2 Using RefAlign with an 8 kHz Reference

If the ZL30407 is locked to an 8 kHz reference, then the output clocks can be brought into phase alignment with the PLL reference by using the RefAlign control bit/pin according to one of the procedures below:

#### 1. For 0.1 Hz filtering applications (FCS = 1, FCS2 = 0)

- Wait until the ZL30407 LOCK indicator is high, indicating that it is locked

- Pull FCS low

- Pull Ref/Align low

- Hold RefAlign low for 10 sec

- Pull RefAlign high

- Wait until the LOCK indicator goes high

- Pull FCS high

After initiating a reference realignment the PLL will enter Holdover mode for 200ns while aligning the internal clocks to remove the static phase error. The PLL will then begin the normal locking procedure. The LOCK pin will go low 5 sec after the reference realignment is initiated and will remain low for 10 sec.

#### 2. For 1.5 Hz filtering applications (FCS = 0, FCS2 = 0)

- Wait until the ZL30407 LOCK indication is high, indicating that it is locked

- Pull RefAlign low

- Hold RefAlign low for 10 sec

- Pull RefAlign high

After initiating a reference realignment the PLL will enter Holdover mode for 200ns while aligning the internal clocks to remove the static phase error. The PLL will then begin the normal locking procedure. The LOCK pin will go low 5 sec after the reference realignment is initiated and will remain low for 10 sec.

#### 3. For 6 Hz and 12 Hz filtering applications (FCS = 1, FCS2 = 1 or FCS = 0, FCS2 = 1)

- Wait until the ZL30407 LOCK indication is high, indicating that it is locked

- Pull RefAlign low

- Hold RefAlign low for 3 sec

- Pull RefAlign high

After initiating a reference realignment the PLL will enter Holdover mode for 200ns while aligning the internal clocks to remove the static phase error. The PLL will then begin the normal locking procedure. The LOCK pin will remain high during the realignment process.

#### 3.3 Clock Synthesizer

The output of the Core PLL is connected to the Clock Synthesizer that generates twelve clocks and three frame pulses.

#### 3.3.1 Output Clocks

The ZL30407 provides the following clocks (see Figure 18 "ST-BUS and GCI Output Timing", Figure 19 "DS1 and DS2 Clock Timing", Figure 20 "C1550 and C190 Timing", and Figure 23 "E3 and DS3 Output Timing" for details):

C1.50 : 1.544 MHz clock with nominal 50% duty cycle C<sub>2</sub>o : 2.048 MHz clock with nominal 50% duty cycle C40 : 4.096 MHz clock with nominal 50% duty cycle C<sub>6</sub>o : 6.312 MHz clock with nominal 50% duty cycle C8o : 8.192 MHz clock with nominal 50% duty cycle C8.50 : 8.592 MHz clock with duty cycle from 30 to 70%. C110 : 11.184 MHz clock with duty cycle from 30 to 70%. C160 : 16.384 MHz clock with nominal 50% duty cycle - C19o : 19.44 MHz clock with nominal 50% duty cycle : 34.368 MHz clock with nominal 50% duty cycle - C340 : 44.736 MHz clock with nominal 50% duty cycle C440 C155 : 155.52 MHz clock with nominal 50% duty cycle.

The ZL30407 provides the following frame pulses (see Figure 18 "ST-BUS and GCI Output Timing" for details). All frame pulses have the same 125  $\mu$ s period (8kHz frequency):

F0o: 244 ns wide, logic low frame pulse

F8o: 122 ns wide, logic high frame pulse

F16o: 61 ns wide, logic low frame pulse

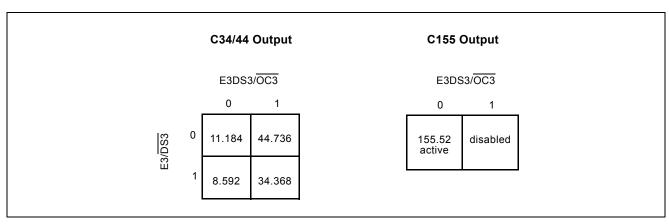

The combination of two pins, E3DS3/OC3 and E3/DS3, controls the selection of different clock configurations. When the E3DS3/OC3 pin is high then the C155o (155.52 MHz) clock is disabled and the C34/44 clock is output at its nominal frequency. The logic level on the E3/DS3 input determines if the output clock on the C34/44 output is 34.368 MHz (E3) or 44.736 MHz (DS3) (see Figure 4, "C34/C44, C155o Clock Generation Options," on page 17 for details).

Figure 4 - C34/C44, C155o Clock Generation Options

All clocks and frame pulses (except the C155) are output with CMOS logic levels. The C155 clock (155.52 MHz) is output in a standard LVDS format.

## 3.3.2 Output Clocks Phase Adjustment

The ZL30407 provides three control registers dedicated to programming the output clock phase offset. Clocks C16o, C8o, C4o and C2o and frame pulses F16o, F8o, F0o are derived from 16.384 MHz and can be jointly shifted with respect to an active reference clock by up to 125  $\mu$ s with a step size of 61 ns. The required phase shift of clocks is programmable by writing to the Phase Offset Register 2 ("Table 9") and to the Phase Offset Register 1 ("Table 10"). The C1.5o clock can be shifted as well in step sizes of 81 ns by programming C1.5POA bits in Control Register 3 ("Table 12").

The coarse phase adjustment is augmented with a very fine phase offset control on the order of 477 ps per step. This fine adjustment is programmable by writing to the Fine Phase Offset Register (Table 16 "Fine Phase Offset Register (R/W)"). The offset moves all clocks and frame pulses generated by ZL30407 including the C155 clock.

#### 3.4 Control State Machine

#### 3.4.1 Clock Modes

Any Network Element that operates in a synchronous network must support three Clock Modes: Free-run, Normal (Locked) and Holdover. A network clock will usually operate in Normal mode. The Holdover and Free-run modes are used to cope with impairments in the synchronization hierarchy. Requirements for Clock Modes are defined in the international standards e.g.: G.813, GR-1244-CORE and GR-253-CORE and they are enforced by network operators. The ZL30407 supports all clock modes and each of these modes have a corresponding state in the Control State Machine.

#### 3.4.2 ZL30407 State Machine

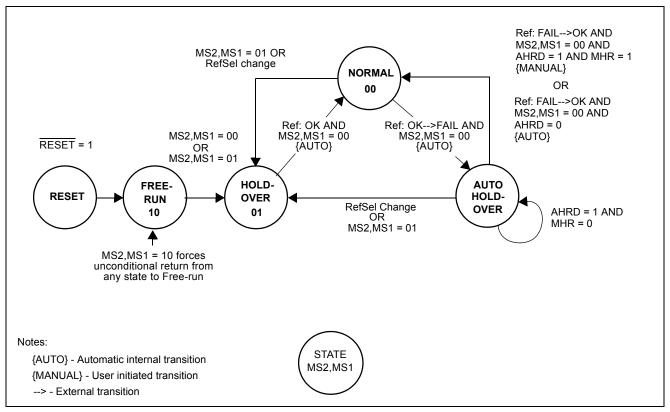

The ZL30407 Control State Machine is a combination of many internal states supporting the three mandatory clock modes. A simplified version of this state machine is shown in Figure 5; it includes the mandatory states: Free-run, Normal and Holdover. These three states are complemented by two additional states: Reset and Auto Holdover, which are critical to the ZL30407 operation under changing external conditions.

Figure 5 - ZL30407 State Machine in Software Control configuration

#### 3.4.2.1 Reset State

The Reset State must be entered when ZL30407 is powered-up. In this state, all arithmetic calculations are halted, clocks are stopped, the microprocessor <u>port is disabled</u> and all internal registers are res<u>et to their default values</u>. The Reset state is entered by pulling the RESET pin low for a minimum of  $\mu$ 1 s. When the RESET pin is pulled back high, internal logic starts a 625  $\mu$ s initialization process before switching into the Free-run state (MS2, MS1 = 10).

#### 3.4.2.2 Free-Run State (Free-Run mode)

The Free-run state is entered when synchronization to the network is not required or is not possible. Typically this occurs during installation, repairs or when a Network Element operates as a master node in an isolated network. In the Free-run state, the accuracy of the generated clocks is determined by the accuracy and stability of the ZL30407 Master Crystal Oscillator. When equipment is installed for the first time (or periodically maintained) the accuracy of the Free-run clocks can be adjusted to within 1x10<sup>-12</sup> by setting the offset frequency in the Master Clock Frequency Calibration Register.

#### 3.4.2.3 Normal State (Normal Mode or Locked Mode)

The Normal State is entered when a good quality reference clock from the network is available for synchronization. The ZL30407 automatically detects the frequency of the reference clock (8 kHz, 1.544 MHz, 2.048 MHz or 19.44 MHz) and sets the LOCK status bit and pin high after acquiring synchronization. In the Normal state all generated clocks (C1.5o, C2o, C4o, C6o, C8o, C16o, C19o, C34/C44 and C155) and frame pulses (F0o, F8o, F16o) are derived from network timing. To guarantee uninterrupted synchronization, the ZL30407 has two Acquisition PLLs that continuously monitor the quality of the incoming reference clocks. This dual architecture enables quick replacement of a poor or failed reference and minimizes the time spent in other states.

#### 3.4.2.4 Holdover State (Holdover Mode)

The Holdover State is typically entered for short durations while network synchronization is temporarily disrupted. In Holdover Mode, the ZL30407 generates clocks, which are not locked to an external reference signal but their frequencies are based on stored coefficients in memory that were determined while the PLL was in Normal Mode and locked to an external reference signal.

The initial frequency offset of the ZL30407 in Holdover Mode is  $4x10^{-12}$  (see table Performance Characteristics\* on page 49 for details). This is more accurate than Telcordia's GR-1244-CORE Stratum 3E requirement of  $\pm 1x10^{-9}$ . Once the ZL30407 has transitioned into Holdover Mode, holdover stability is determined by the stability of the 20 MHz Master Clock Oscillator. Selection of the oscillator requires close examination of the crystal oscillator temperature sensitivity and frequency drift caused by aging.

#### 3.4.2.5 Auto Holdover State

The Auto Holdover state is a transitional state that the ZL30407 enters automatically when the active reference fails unexpectedly. When the ZL30407 detects loss of reference it sets the HOLDOVER status bit and waits in Auto Holdover state until the failed reference recovers. Recovery from Auto Holdover for 8 kHz, 1.544 MHz, 2.048 MHz and 19.44 MHz reference clocks is fully automatic, however recovery for an 8 kHz reference clock requires additional transitioning through the Holdover state to guarantee compliance with network synchronization standards (for details see Section 5.1.3 on page 36 and Section 5.1.2 on page 35). The HOLDOVER status may alert the control processor about the failure and in response the control processor may switch to the secondary reference clock. The Auto Holdover and Holdover States are internally combined together and they are output as a HOLDOVER status on pin 55 and bit 4 in Status Register 1 (Table 7 on page 26).

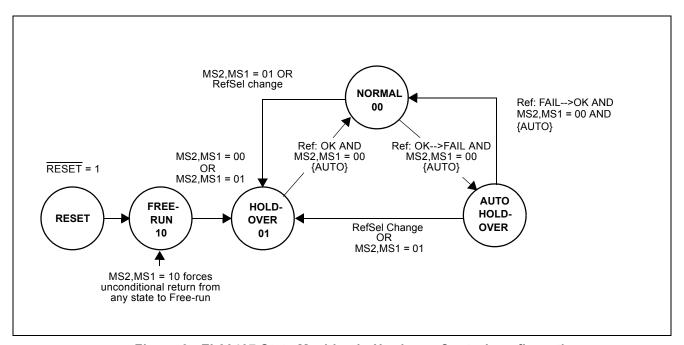

In less demanding clocking arrangements (e.g. Line Cards), the ZL30407 can be configured to operate in the Hardware Control mode which does not require a microprocessor. Under the Hardware Control mode the ZL30407 maintains most of its State Machine functionality as is shown in Figure 6.

Figure 6 - ZL30407 State Machine in Hardware Control configuration

#### 3.4.3 State Transitions

In a typical Network Element application, the ZL30407 will most of the time operate in Normal mode (MS2, MS1 == 00) generating synchronous clocks. Its two Acquisition PLLs will continuously monitor the input references for signs of degraded quality and output status information for further processing. The status information from the Acquisition PLLs and the CORE PLL combined with status information from line interfaces and framers (as listed below) forms the basis for creating reliable network synchronization.

- Acquisition PLLs (PRIOR, SECOR, PAH, PAFL, SAH, SAFL)

- Core PLL (LOCK, HOLDOVER, FLIM)

- Line interfaces (e.g. LOS Loss of Signal, AIS Alarm Indication Signal)

- Framers (e.g. LOF Loss of frame or Synchronization Status Messages carried over SONET S1 byte or ESF-DS1 Facility Data Link).

The ZL30407 State Machine is designed to perform some transitions automatically, leaving other less time dependent tasks to the control processor. The state machine includes two stimulus signals which are critical to automatic operation: "OK --> FAIL" and "FAIL --> OK" that represent loss (and recovery) of reference signal or its drift by more than ±30000 ppm. Both of them force the Core PLL to transition into and out of the Auto Holdover state. In case when the reference clock on the PRI (or SEC) input is externally selected from multiple clock sources with different frequencies then the Acquisition PLL will automatically detect this change as a reference clock failure. In response, the Acquisition PLL will force Core PLL into Auto-Holdover state until the frequency of a new reference is determined. This process may take up to 35 ms after which a normal locking procedure will be initiated.

The ZL30407 State Machine is controlled by the mode select pins or bits MS2, MS1. In order to avoid network synchronization problems, the State Machine has built-in basic protection that does not allow switching the Core PLL into a state where it cannot operate correctly e.g., it is not possible to force the Core PLL into Normal mode when all references are lost.

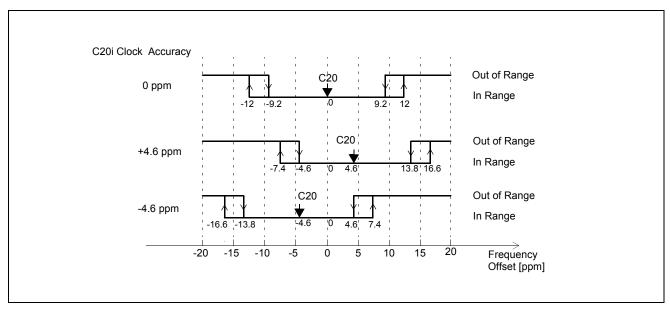

#### 3.5 Master Clock Frequency Calibration Circuit

In an ordinary timing generation module, the Free-run mode accuracy of generated clocks is determined by the accuracy of the Master Crystal Oscillator. If the Master Crystal Oscillator has a manufacturing tolerance of  $\pm 4.6$  ppm, the generated clocks will have no better accuracy.

The ZL30407 eliminates Crystal Oscillator tolerance problem by providing a programmable Master Clock Frequency Calibration circuit, which can reduce oscillator manufacturing tolerance to near zero. However this feature does not eliminate oscillator frequency drift. The value stored in the Master Clock Calibration Register can be periodically updated to compensate for oscillator frequency drift due to ageing or due to temperature effects. The compensation value for the Master Clock Calibration Register (MCFC3 to MCFC0) can be calculated from the following equation:

MCFC =

$$45036 * (-f_{offset})$$

where:  $f_{offset} = f_{m} - 20\ 000\ 000\ Hz$

The  $f_m$  frequency should only be measured after the Master Crystal Oscillator has been mounted inside a system and powered long enough for the Master Crystal Oscillator to reach a steady operating temperature. Section 5.3 on page 40 provides two examples of how to calculate an offset frequency and convert the decimal value to a binary format. The maximum frequency compensation range of the MCFC register is equal to  $\pm$  2384 ppm ( $\pm$ 47680 Hz).

Changes to the Master Clock Calibration Register cause immediate changes in the frequency of the output clocks. Care should be taken to ensure that changes to the Master Clock Calibration Register are made in small increments so the frequency steps can be tolerated by downstream equipment. A rate of frequency change below 2.9 ppm/sec is suggested.

All memory in the ZL30407 is volatile; so any settings of the Master Clock Calibration Register need to be reloaded after each RESET.

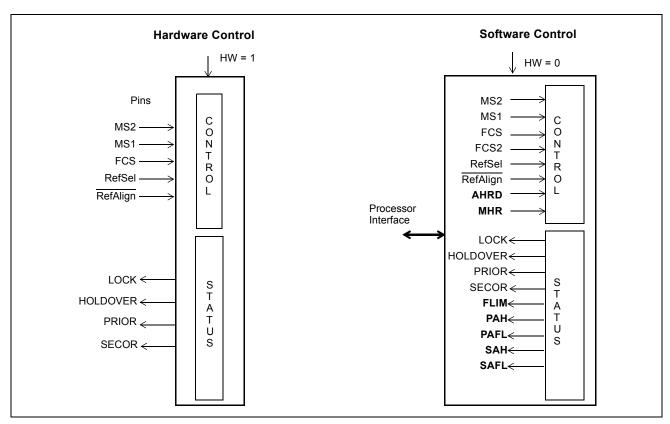

#### 3.6 Microprocessor Interface

The ZL30407 can be controlled by a microprocessor or by an ASIC type of device that is connected directly to the hardware control pins. If the HW pin is tied low (see Figure 7 "Hardware and Software Control Options"), an 8-bit Motorola type microprocessor may be used to control PLL operation and check its status. Under software control, the control pins MS2, MS1, FCS, RefSel, RefAlign are disabled and they are replaced by the equivalent control bits. The output pins LOCK, HOLDOVER, PRIOR and SECOR are always active and they provide current status information whether the device is in microprocessor or hardware control. Software (microprocessor) control provides additional functionality that is not available in hardware control such as:

- 6 Hz and 12 Hz PLL loop filter selection

- · output clock phase adjustment

- · master clock frequency calibration

- extended access to status registers. These registers are also accessible when the ZL30407 operates under Hardware control.

#### 3.7 JTAG Interface

The ZL30407 JTAG (Joint Test Action Group) interface conforms to the Boundary-Scan standard IEEE1149.1-1990, which specifies a design-for-testability technique called Boundary-Scan Test (BST). The BST architecture is made up of four basic elements, Test Access Port (TAP), TAP Controller, Instruction Register (IR) and Test Data Registers (TDR) and all these elements are implemented on the ZL30407.

Zarlink Semiconductor provides a Boundary Scan Description Language (BSDL) file that contains all the information required for a JTAG test system to access the ZL30407's boundary scan circuitry. The file is available for download from the Zarlink Semiconductor web site: www.zarlink.com.

#### 4.0 Hardware and Software Control

The ZL30407 offers Hardware and Software Control options that simplify the design of basic or complex clock synchronization modules. Hardware control offers fewer features but still allows for building of sophisticated timing cards without extensive programming. The complete set of control and status functions for each mode are shown in Figure 7 "Hardware and Software Control Options".

Figure 7 - Hardware and Software Control Options

#### 4.1 Hardware Control

The Hardware control is a subset of software control and it will only be briefly described with cross-referencing to Software control programmable registers.

#### 4.1.1 Control Pins

The ZL30407 has five dedicated control pins for selecting modes of operation and activating different functions. These pins are listed below:

**MS2** and **MS1** pins: **Mode Select**: The MS2 (pin 19) and MS1 (pin 18) inputs select the PLL mode of operation. See Table 2 for details. The logic level at these inputs is sampled by the rising edge of the F80 frame pulse.

| MS2 | MS1 | Mode of Operation |

|-----|-----|-------------------|

| 0   | 0   | Normal mode       |

| 0   | 1   | Holdover mode     |

| 1   | 0   | Free-run          |

| 1   | 1   | Reserved          |

**Table 2 - Operating Modes and States**

FCS pin: Filter Characteristic Select. The FCS (pin 9) input is used to select the filtering characteristics of the Core PLL. See Table 1, "Loop Filter Selection" on page 13 for details.

| FCS | Filtering Characteristic              |

|-----|---------------------------------------|

| 0   | Filter corner frequency set to 1.5 Hz |

| 1   | Filter corner frequency set to 0.1 Hz |

Table 3 - Filter Characteristic Selection

**RefSel**: **Reference Source Select**. The RefSel (pin 47) input selects the PRI (primary) or SEC (secondary) input as the reference clock for the Core PLL. The logic level at this input is sampled by the rising edge of F8o.

| RefSel | Input Reference                                     |

|--------|-----------------------------------------------------|

| 0      | Core PLL connected to the Primary Acquisition PLL   |

| 1      | Core PLL connected to the Secondary Acquisition PLL |

Table 4 - Reference Source Select

**RefAlign: Reference Alignment**. The RefAlign (pin 48) input controls phase realignment between the input reference and the generated output clocks.

#### 4.1.2 Status Pins

The ZL30407 has four dedicated status pins for indicating modes of operation and quality of the Primary and Secondary reference clocks. These pins are listed below:

LOCK - This output goes high after the ZL30407 has completed its locking sequence (see section 2.2.3 for details).

**HOLDOVER** - This output goes high when the Core PLL enters Holdover mode. The Core PLL will switch to Holdover mode if the respective Acquisition PLL enters Holdover mode or if the mode select pins or bits are set to Holdover (MS2, MS1 = 01).

**PRIOR** - This output goes high when the primary reference frequency deviates from the PLL center frequency by more than ±12 ppm. See PRIOR pin description for details.

**SECOR -** This output goes high when the secondary reference frequency deviates from the PLL center frequency by more than ±12 ppm. See SECOR pin description for details.

#### 4.2 Software Control

Software control is enabled by setting the HW pin to logic zero (HW = 0). In this mode all hardware control pins (inputs) are disabled and all status pins remain enabled. The ZL30407 has a number of registers that provide all the functionality available in Hardware control and in addition they offer advanced control and monitoring that is only available in Software control (see Figure 7 "Hardware and Software Control Options").

#### 4.2.1 Control Bits

The ZL30407 has a number of registers that provide greater operational flexibility than available pins in Hardware control (see Figure 7 "Hardware and Software Control Options"). The MS2, MS1, FCS2, FCS, RefSel and RefAlign bits perform the same function as the corresponding pins. Two additional bits AHRD and MHR support recovery from Auto Holdover mode and they are described in section 3.2.4.

In addition to the Control bits shown in Figure 7 "Hardware and Software Control Options", the ZL30407 has a number of bits and registers that are accessed infrequently e.g., 6 Hz and 12 Hz PLL loop filter selection, Phase Offset Adjustment or Master Clock Frequency Calibration. These additional control options add flexibility to the ZL30407.