## eZ80Acclaim!® Flash Microcontrollers

# eZ80F91 MCU

#### **Product Brief**

PB013505-0607

## **Product Block Diagram**

|                                 | eZ80F91 MCU |                                                 |                  |  |                    |  |

|---------------------------------|-------------|-------------------------------------------------|------------------|--|--------------------|--|

| 256 KB<br>512 B                 |             | 32-Bit GPIO                                     |                  |  |                    |  |

| 8 KB :                          | λM          | 10/100 Mbps<br>Ethernet MAC<br>8KB Frame Buffer |                  |  |                    |  |

| Infrared<br>Encoder/<br>Decoder | 21          | JART                                            | I <sup>2</sup> C |  | SPI                |  |

| 4 PRT                           | 4 PRT W     |                                                 | )                |  | teal Time<br>Clock |  |

| 4 CS<br>+WSG                    | J           | TAG                                             | ZDI              |  | PLL                |  |

## **Key Features**

The eZ80F91 MCU is a member of ZiLOG's eZ80Acclaim!<sup>®</sup> product family which offers on-chip Flash versions of ZiLOG's eZ80<sup>®</sup> processor core. The eZ80F91 MCU offers the following features:

- 50 MHz high-performance eZ80<sup>®</sup> CPU

- 256 KB Flash Program Memory and extra

512 B device configuration Flash Memory

- 32 bits of General-Purpose Input/Output (GPIO)

- 16 KB total on-chip high-speed SRAM:

- 8 KB for general-purpose use

- 8 KB for 10/100BaseT Ethernet Media Access Controller (EMAC) high-speed frame buffer

- IrDA-compatible infrared encoder/decoder

- Two universal asynchronous receiver/ transmitter (UARTs) with independent baud rate generators

- Inter-integrated circuit (I<sup>2</sup>C) and serial peripheral interface (SPI) with independent clock rate generator

- Four counter/timers with prescalers supporting event counting, input capture, output compare, and Pulse Width Modulator (PWM) modes

- Watchdog Timer (WDT) with internal RC clocking option

- Real time clock (RTC) with on-chip 32 KHz oscillator, selectable 50/60 Hz input, and separate RTC\_V<sub>DD</sub> pin for battery backup

- Glueless external memory interface with 4 Chip-Selects/Wait-State Generators and external WAIT input pin. It also supports Intel® and Motorola® buses

- JTAG and ZiLOG Debug Interface (ZDI) supporting emulation features

- Low-power PLL and on-chip oscillator

- Programmable-priority vectored interrupts, non-maskable interrupts, and interrupt controller

- New DMA-like eZ80® CPU instructions

- Power management features supporting HALT/SLEEP modes and selective peripheral power-down controls

- 144-pin BGA package or 144-pin LQFP package

- 3.0 V to 3.6 V supply voltage with 5 V tolerant inputs

Copyright ©2007 by ZiLOG, Inc. All rights reserved. www.zilog.com

- Operating temperature ranges:

- Standard, 0 °C to +70 °C

- Extended, -40 °C to +105 °C

## **General Description**

The eZ80F91 MCU is industry's first MCU featuring a high-performance 8-bit microcontroller with an integrated 10/100BaseT EMAC. It is a power-efficient, optimized pipeline architecture microcontroller with a maximum operating speed of 50 MHz. Offering on-chip Flash Memory, SRAM, Ethernet MAC, and rich peripherals, the eZ80F91 is well-suited for industrial, communication, automation, security, and embedded Internet applications.

#### eZ80® CPU Core

The eZ80 $^{\mathbb{R}}$  CPU operates either in Z80-compatible (64 KB) mode or full 24-bit (16 MB) addressing mode. Considering both the increased clock speed and processor efficiency, the processing power of eZ80 $^{\mathbb{R}}$  competes with the performance of 16-bit microprocessors. The eZ80 $^{\mathbb{R}}$  improves on the world-famous Z80 $^{\mathbb{R}}$  architecture. Like Z80 $^{\mathbb{R}}$ , eZ80 $^{\mathbb{R}}$  CPU features dual bank registers for fast context switching.

# eZ80F91 MCU Peripherals Description

The peripherals of eZ80F91 MCU includes the following:

#### **On-Chip Memory**

The eZ80F91 device offers 256 KB of Flash Program Memory. A separate page of 512-bytes Flash Memory is available for general device configuration data. Other on-chip memory features include:

- Single power supply operation

- Page erase feature, 2048 bytes/page

- Fast page erase and byte program operation

- 78 ns minimum read cycle

- Endurance, 10,000 write cycles (typical)

- The data can be retained for more than 100 years at room temperature

In addition, 16 KB of high-speed, relocatable SRAM is available and 8 KB is for general-purpose use. Another 8 KB is used by the EMAC for Ethernet operation, but is also user-accessible when Ethernet functionality is not required.

#### **General-Purpose Input/Output**

There are 32 bits of GPIO. All GPIO pins are individually programmable and support the following I/O modes: input, output, open drain, open source, level-triggered interrupts (High or Low), edge-triggered interrupts (High or Low), dual edge-triggered interrupts, and alternate function. Eight of the output pins can drive 10 mA each (Port A), while 16 other pins feature Schmitt-trigger input buffers (Port B and Port C).

#### 10/100 BaseT Ethernet MAC

The eZ80F91 MCU features an integrated IEEE 802.3 Ethernet controller with 8 KB of dynamically-configurable Tx/Rx frame buffer. It supports speed of 10 Mbps and 100 Mbps, full duplex operation, and an industry-standard Media Independent Interface (MII) for simple connection to an external Physical Layer interface (PHY) device. The eZ80F91 delivers high performance and overall cost effectiveness as an embedded network microcontroller.

High performance is achieved by optimizing the internal bus design of the eZ80<sup>®</sup> CPU with shared memories, dedicated Ethernet Tx/Rx DMAs, and Tx/Rx FIFOs. This bus design provides the highest data throughput over the Ethernet interface, yet requires minimum eZ80<sup>®</sup> CPU intervention and minimizes system loading.

#### Infrared Encoder/Decoder

- Supports IrDA SIR format

- Operates seamlessly with on-chip UART

- Interfaces with IrDA-compliant transceivers

- Supports transmit/receive to 115 Kbps

#### **Universal Asynchronous Receiver/Transmitter**

Each of the two UART channels contains a transmitter, a receiver, control logic/registers, and a Baud Rate Generator (BRG).

- The BRG produces a lower-frequency bit clock from the system clock. All standard baud rates up to 115 Kbps (and higher) are supported.

- The UART module implements the logic required to support asynchronous communications, hardware flow control, and 9-bit character format. The module also contains separate 16-byte-deep transmit and receive FIFOs.

#### **Inter-Integrated Circuit**

The I<sup>2</sup>C channel contains control registers and a clock rate generator. The I<sup>2</sup>C interface operates in four modes: Master Transmit or Receive and Slave Transmit or Receive. A standard and fast I<sup>2</sup>C speed of 100 kbps and 400 kbps are supported.

#### **Serial Peripheral Interface**

The SPI channel contains control registers and a clock rate generator. The SPI is a synchronous serial interface allowing multiple SPI devices to be interconnected. The SPI interface is configured to function either as a master or a slave.

#### **Programmable Reload Timers**

The eZ80F91 MCU provides four independent Programmable Reloadable Counter Timers (PRT) to handle complex timing functions. Each timer is a 16-bit downcounter and offers a 4-bit clock prescaler with four selectable taps for CLK÷4, CLK÷16, CLK÷64 and CLK÷256. The timers operates in basic mode supporting SINGLE-PASS or CONTINUOUS count. Additional features include 4 input captures, 4 output compares, 2 external event counters, and 4 PWMs that can operate independently or in unison. Any one of the input capture pins can be programmed as master PWM power-trip inputs.

#### **Watchdog Timer**

The WDT features four programmable time-out periods. It operates either from the main system clock, the on-chip 32 KHz oscillator (from the RTC), or the internal RC oscillator. The time-out

action of the WDT is user-programmable for either a hardware reset or a non-maskable interrupt to the eZ80<sup>®</sup> CPU. The source of action taken after a WDT time-out is indicated by a WDT status bit.

#### **Real Time Clock**

The RTC allows counting of seconds, minutes, hours, day-of-the-week, day-of-the-month, month, year, and century. Alarms and interrupts can be set for seconds, minutes, hours, and day-of-the-week. The RTC input is taken either from the on-chip 32 KHz oscillator or from a 50/60 Hz input. The RTC operates from an isolated RTC\_V<sub>DD</sub> pin to allow constant operation from a battery.

#### **Chip-Select/Wait State Generator and WAIT Pin**

Four independent chip selects facilitate glueless interface to system memory and external devices. Each chip-select can be configured for up to 7 wait states and supports either memory or I/O space. Memory chip selects can be individually programmed on a 64 KB boundary. I/O chip selects can choose a 256 byte section of I/O space. The WAIT input pin allows interface with slow peripherals. It also supports Z80<sup>®</sup>, Intel<sup>®</sup>, and Motorola<sup>®</sup> bus modes.

#### **JTAG Interface**

An IEEE 1149.1-compatible five-pin test access port (TAP) is provided to interface with on-chip test logic defined by IEEE standard. The TAP also includes Boundary Scan functions and is used to control on-chip emulation/debugging capabilities. Some features include software break points, 64-word trace buffer, complex break points using address and data masks, and cascadable triggers.

#### **PLL and On-Chip Crystal Oscillator**

The eZ80F91 MCU features a low-power, programmable PLL that can be selected to generate the system clock. Taking the input from the on-chip crystal oscillator, the PLL generates system clock speed up to 50 MHz from low-cost, low-frequency external crystals in the range of 1 MHz to 10 MHz.

#### **ZiLOG Debug Interface**

The ZiLOG Debug Interface (ZDI) incorporates the functions of an in-circuit emulator. ZDI allows you to single-step code, change registers, edit programs, and view status of the internal registers.

#### **Block Transfer Instructions**

Block transfer instructions with expanded repeat capability are added to the eZ80<sup>®</sup> CPU. They provide high-performance data transfer similar to hardware DMAs.

## **Power Management**

The eZ80F91 MCU supports several power management features. Two peripheral Power-Down Registers allow independent clock gating of on-chip peripherals under software control while operating under normal conditions. The eZ80® CPU writes to the control registers to disable the clock from driving any one of the peripherals while they are inactive.

In addition, execution of the HALT instruction suspends eZ80<sup>®</sup> CPU operation and eliminates clock power associated with the eZ80<sup>®</sup> CPU core. Normal operation is restored via external and peripheral interrupts or hardware reset.

Execution of a sleep (SLP) instruction provides the lowest power consumption. In SLEEP mode, only the on-chip RTC 32 KHz crystal oscillator remains active to drive the RTC and the WDT. Other peripherals like the system clock, and the primary oscillator are disabled. You can reset the device by RTC alarm, a WDT time-out, or hardware reset.

### **Electrical Features Summary**

- Power supply, 3.3 V  $\pm$  0.3 V

- Standard temperature, 0 °C to 70 °C

- Extended temperature, -40 °C to +105 °C

- Supply current at 50 MHz; 50 mA (typical)

- Supply current in HALT mode with peripherals powered down; <5 mA (typical)

- Supply current in SLEEP mode; <50 μA (typical)

## **Support Tools**

The following development tools are available to program and debug the eZ80F91 MCU:

#### **Hardware**

• eZ80<sup>®</sup> Development Platform with plug-in eZ80F91 Module

#### Software

- ZiLOG TCP/IP (ZTP) software suite

- ANSI C-Compiler

- ZiLOG Developer's Studio Integrated Development Environment (ZDS II IDE) including assembler, linker, debugger, and simulator

## **Related Products**

Other integrated devices of interest are:

| eZ80190       | 50 MHz eZ80 <sup>®</sup> CPU, 8 KB SRAM, 16x16 multiply with 40-bit accumulators, 32 bits GPIO, 6 Counter Timers with prescalers, WDT, 4 channel CS+WSG, 2 Channel DMA, 2 UZI Channels, ZDI, On-Chip Oscillator. |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eZ80L92       | 20 MHz and 50 MHz eZ80 <sup>®</sup> CPU, low-power modes, 24 bits GPIO, IrDA, 2 UART, I <sup>2</sup> C, SPI, 6 Counter Timers with I/O features, WDT, RTC, 4 channel CS, JTAG, ZDI.                              |

| eZ80F92       | 20 MHz eZ80 $^{\circledR}$ CPU, low-power modes, 128 KB+256 B Flash, 8 KB SRAM, 24 bits GPIO, IrDA, 2 UART, I $^2$ C, SPI, 6 Counter Timers with I/O features, WDT, RTC, 4 channel CS+WSG, JTAG, ZDI, PLL.       |

| eZ80F93       | 20 MHz eZ80 <sup>®</sup> CPU, low-power modes, 64 KB+256 B Flash, 4 KB SRAM, 24 bits GPIO, IrDA, 2 UART, I <sup>2</sup> C, SPI, 6 Counter Timers with I/O features, WDT, RTC, 4 channel CS+WSG, JTAG, ZDI.       |

| Z80S180™      | Improved Z80 CPU, 1 MB MMU, 2 DMA, 2 16-bit PRTs, 2 UARTs, CSIO, up to 33 MHz clock speed.                                                                                                                       |

| Z80181        | Z8S180 CPU, SCC, CTC, 16-bit GPIO, up to 33 MHz clock speed.                                                                                                                                                     |

| Z80182        | Z8S180 CPU, 2 ESCC, 24-bit GPIO, 16550 Mimic interface, up to 33 MHz clock speed.                                                                                                                                |

| Z84C00        | Z80 <sup>®</sup> CPU (up to 20 MHz).                                                                                                                                                                             |

| Z84C15        | Z80 <sup>®</sup> CPU, 2 SIO, 4x8 CTC, 2 PIO, WDT, up to 16 MHz clock speed.                                                                                                                                      |

| · <del></del> |                                                                                                                                                                                                                  |

## **Block Diagram**

Figure 1 illustrates the block diagram of eZ80F91 MCU.

Figure 1. eZ80F91 Block Diagram

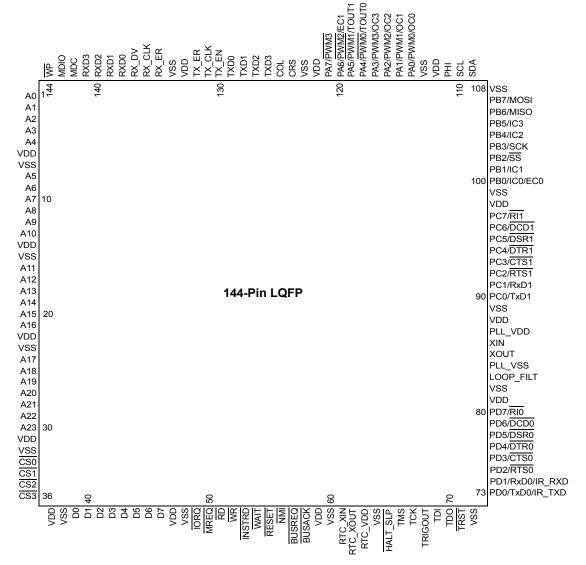

## **Pin Diagrams**

Figure 2 illustrates the 144-pin LQFP pin configuration of eZ80F91 MCU.

Figure 2. eZ80F91 MCU 144-Pin LQFP Pin Configuration

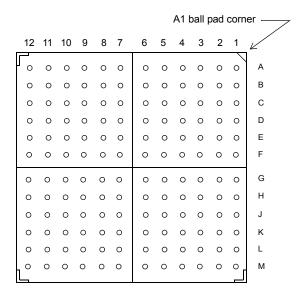

Table 1 lists the 144-pin BGA pin configuration of eZ80F91 MCU.

Table 1. eZ80F91 144-Pin BGA Pin Configuration

|   | 12       | 11       | 10                      | 9               | 8            | 7                       | 6        | 5          | 4        | 3        | 2        | 1               |

|---|----------|----------|-------------------------|-----------------|--------------|-------------------------|----------|------------|----------|----------|----------|-----------------|

| Α | SDA      | SCL      | PA0                     | PA4             | PA7          | COL                     | TxD0     | $V_{DD}$   | Rx_DV    | MDC      | WPn      | A0              |

| В | $V_{SS}$ | PHI      | PA1                     | PA3             | $V_{DD}$     | TxD3                    | Tx_EN    | $V_{SS}$   | RxD1     | MDIO     | A2       | A1              |

| С | PB6      | PB7      | $V_{DD}$                | PA5             | $V_{SS}$     | TxD2                    | Tx_CLK   | Rx_<br>CLK | RxD3     | A3       | $V_{SS}$ | $V_{DD}$        |

| D | PB1      | PB3      | PB5                     | $V_{SS}$        | CRS          | TxD1                    | Rx_ER    | RxD2       | A4       | A8       | A6       | A7              |

| Ε | PC7      | $V_{DD}$ | PB0                     | PB4             | PA2          | Tx_ER                   | RxD0     | A5         | A11      | $V_{SS}$ | $V_{DD}$ | A10             |

| F | PC3      | PC4      | PC5                     | V <sub>SS</sub> | PB2          | PA6                     | A9       | A17        | A15      | A14      | A13      | A12             |

| G | $V_{SS}$ | PC0      | PC1                     | PC2             | PC6          | PLL_<br>V <sub>SS</sub> | $V_{SS}$ | A23        | A20      | $V_{SS}$ | $V_{DD}$ | A16             |

| Н | XOUT     | XIN      | PLL_<br>V <sub>DD</sub> | $V_{DD}$        | PD7          | TMS                     | $V_{SS}$ | D5         | $V_{SS}$ | A21      | A19      | A18             |

| J | $V_{SS}$ | $V_{DD}$ | LOOP<br>FILT_<br>OUT    | PD4             | TRIGOUT      | RTC_<br>V <sub>DD</sub> | NMIn     | WRn        | D2       | CS0n     | $V_{DD}$ | A22             |

| K | PD5      | PD6      | PD3                     | TDI             | $V_{SS}$     | $V_{DD}$                | RESETn   | RDn        | $V_{DD}$ | D1       | CS2n     | CS1n            |

| L | PD1      | PD2      | TRSTn                   | TCK             | RTC_<br>XOUT | BUSACKn                 | WAITn    | MREQn      | D6       | D4       | D0       | CS3n            |

| M | PD0      | $V_{SS}$ | TDO                     | HALT_<br>SLPn   | RTC_<br>XIN  | BUSREQn                 | INSTRDn  | IORQn      | D7       | D3       | $V_{SS}$ | V <sub>DD</sub> |

Figure 3 illustrates the bottom view of 144-pin eZ80F91 BGA Device.

Figure 3. Bottom View of 144-Pin eZ80F91 BGA Device

## **Ordering Information**

You can order the eZ80F91 MCU from ZiLOG, using the part numbers in the table below. For more information regarding ordering, please consult your local ZiLOG sales office. The ZiLOG website <a href="https://www.zilog.com">www.zilog.com</a> lists all regional offices, as well as additional eZ80Acclaim! product information.

| Part Number     | Description                                  | Package  |  |  |  |

|-----------------|----------------------------------------------|----------|--|--|--|

| eZ80F91AZA50SG  | eZ80F91 device, 50 MHz, Standard Temperature | 144-LQFP |  |  |  |

| eZ80F91AZA50EG  | eZ80F91 device, 50 MHz, Extended Temperature | 144-LQFP |  |  |  |

| eZ80F91NAA50SG  | eZ80F91 device, 50 MHz, Standard Temperature | 144-BGA  |  |  |  |

| eZ80F91NAA50EG  | eZ80F91 device, 50 MHz, Extended Temperature | 144-BGA  |  |  |  |

| eZ80F91AZ050SG* | eZ80F91 device, 50 MHz, Standard Temperature | 144-LQFP |  |  |  |

| eZ80F91AZ050EG* | eZ80F91 device, 50 MHz, Extended Temperature | 144-LQFP |  |  |  |

| eZ80F91NA050SG* | eZ80F91 device, 50 MHz, Standard Temperature | 144-BGA  |  |  |  |

| eZ80F91NA050EG* | eZ80F91 device, 50 MHz, Extended Temperature | 144-BGA  |  |  |  |

| eZ80F910300ZCOG | eZ80F91 Development Kit                      |          |  |  |  |

| eZ80F910200KITG | eZ80F91 Modular Development Kit              |          |  |  |  |

| eZ80F916050MODG | Ethernet Module                              |          |  |  |  |

| eZ80F916005MODG | Mini-Ethernet Module                         |          |  |  |  |

| ZUSBSC00100ZACG | USB Smart Cable Accessory Kit                |          |  |  |  |

| ZENETSC0100ZACG | Ethernet Smart Cable Accessory Kit           |          |  |  |  |

<sup>\*</sup> Denotes parts not recommended for new designs.

Warning:

DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness

#### **Document Disclaimer**

©2007 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, eZ80Acclaim! and ZNEO are trademarks or registered trademarks of ZiLOG, Inc. All other product or service names are the property of their respective owners.