# PEX 8112

#### Features

- General Features

- Forward and Reverse bridging

- 0 144-ball BGA package with standard

1.0 mm pitch (13mm x 13mm)

- 0 161-ball BGA package with fine

0.65 mm pitch (10mm x 10mm)

- o Low power 400 milliwatts

- EEPROM configuration option with SPI

- O Internal 8Kbyte shared RAM

- o 1.5 V core supply voltage

- o JTAG

- Four (4) GPIO pins for maximum design flexibility

- $\circ$  Extensive PME support including D0 and D0<sub>Active</sub>, D1, D2 and D3<sub>Hot</sub> and D3<sub>Cold</sub>

- Leaded and Lead-free standard pitch packaging available

- o Lead-free fine pitch packaging only

- o Industrial Temperature: -40 to +85°C

#### Integrated PCI Express Interface

- PCI Express Base 1.0a compliant

- x1 Link, dual-simplex, 2.5 Gbps per direction

- o One virtual channel

- o Automatic LVDS polarity reversal

- o 128 byte maximum payload size

- o Link CRC

- o Link power management

- Flow control buffering

- PCI Express transaction queues for eight (8) outstanding TLPs

- PCI Interface

- o PCI v.3.0: 32 bits, up to 66 MHz

- o PCI Power Management 1.1

- Internal arbiter supports up to 4 external masters; REQ#/GNT# signals

- $\circ~3.3V$  I/O and 5V tolerant PCI

- Message Signal Interrupt (MSI) support

- o Provides PCI clock output

- o Four mailbox registers for messaging

- VGA and ISA Enable registers for legacy operation

## ExpressLane<sup>TM</sup> PCI Express to PCI Bridge

## **Reversible Bridge in a Tiny Package**

The PLX Technology PEX 8112 bridge enables designers to migrate legacy PCI bus interfaces to the new advanced serial PCI Express. This is ideal for including existing PCI ICs on a PCI Express<sup>TM</sup> Adapter Board, such as the new ExpressCard<sup>TM</sup> or AdvancedMC<sup>TM</sup> standards. The 13mm x 13mm standard BGA package or 10mm x 10mm fine BGA package offerings makes the PEX 8112 bridge well suited for applications where board real estate is at a premium. With its low power 0.15 micron CMOS design, the PEX 8112 consumes only about 400 mW of power.

## Forward and Reverse Bridging

The PEX 8112 supports **forward and reverse bridging** as defined by the PCI Express-to-PCI/PCI-X Bridge Specification 1.0. In forward mode, the bridge allows legacy PCI chips and adapters to be used with new PCI Express processor systems. Reverse bridge operation allows conventional PCI processors and chipsets to configure and control advanced PCI Express switches and endpoints. The reverse PEX 8112 not only allows complete configuration of a downstream PCI Express system from the PCI bus, but it also handles limited PCI Express root functions for reverse interrupt and Power Management Events.

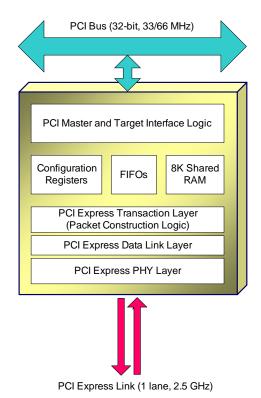

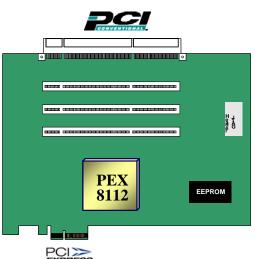

## **Block Diagram**

The PEX 8112 is equipped with a standard PCI Express port that operates as a single, x1 link with a maximum of 250 Megabytes per second of throughput per transmit and receive direction. The single 2.5 Gbps integrated SerDes delivers the highest bandwidth with the lowest possible pin count using LVDS technology.

The PEX 8112 has a single parallel bus segment supporting the PCI v.3.0 protocol, and a 32-bit wide parallel data path running up to 66MHz.

The device supports internal queues with flow control features to optimize throughput and traffic flow.

Figure 1. PEX 8112 Block Diagram

## **Design Applications**

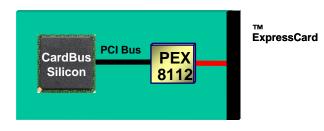

### ExpressCard<sup>™</sup> Adapter – Forward Bridge

The PEX 8112 can be used to quickly upgrade legacy PCI adapter board designs to be compatible with PCI Express standard interface slots. In Figure 2, an existing CardBus<sup>™</sup> IC is converted for use on an ExpressCard<sup>™</sup> with the addition of the single-chip PEX 8112.

Figure 2. Forward Bridge in ExpressCard™

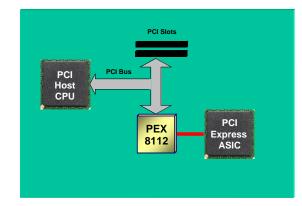

#### Embedded Host Platform – Reverse Bridge

The PEX 8112 supports Reverse bridging, enabling designers to utilize the latest PCI Express silicon with widely entrenched PCI host systems. Reverse bridging allows the host processor to reside on the PCI bus; the PEX 8112 will accept configuration cycles from the PCI side and manage the PCI Express interface as a secondary entity within the PCI software model as in Figure 3.

Figure 3. Reverse Bridge with PCI CPU

## **Development Tools**

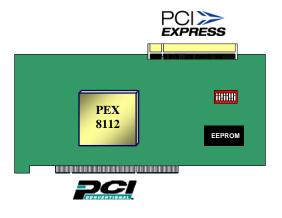

**PEX 8112 Reference Design Kits (RDK)** enable rapid customer design. The Reverse Bridge RDK (Figure 4) includes a standard PCI connector (card-edge) and a standard PCI Express slot on the secondary side. The Forward Bridge RDK (Figure 5) includes the PEX 8112 with a single x1 PCI Express port (card-edge) and four PCI slots on the secondary side. Each PEX 8112RDK can be installed in a motherboard to evaluate PEX 8112 features and validate customer software.

Figure 4. Reverse Bridge RDK

Figure 5. Forward Bridge RDK

PLX Technology, Inc. 870 Maude Ave. Sunnyvale, CA 94085 USA Tel: 1-408-774-9060 Fax: 1-408-774-2169 Email: info@plxtech.com Web Site: www.plxtech.com

## **Product Ordering Information**

| Part Number       | Description                                                      |

|-------------------|------------------------------------------------------------------|

| PEX8112-AA66BI    | PCI Express to PCI Bridge, Standard-Pitch BGA Package, Leaded    |

| PEX8112-AA66BI F  | PCI Express to PCI Bridge, Standard-Pitch BGA Package, Lead Free |

| PEX8112-AA66FBI F | PCI Express to PCI Bridge, Fine-Pitch BGA Package, Lead-Free     |

| PEX8112RDK-F      | Forward Bridge Reference Design Kit                              |

| PEX8112RDK-R      | Reverse Bridge Reference Design Kit                              |

Please visit the PLX Web site at http://www.plxtech.com or contact PLX sales at 408-774-9060 for sampling.

© 2007 PLX Technology, Inc. All rights reserved. PLX and the PLX logo are registered trademarks of PLX Technology, Inc. ExpressLane is a trademark of PLX Technology, Inc., which may be registered under some jurisdiction. All other product names that appear in this material are for identification purposes only and are acknowledged to be trademarks or registered trademarks of their respective companies. Information supplied by PLX is believed to be accurate and reliable, but PLX Technology, Inc. assumes no responsibility for any errors that may appear in this material. PLX Technology, Inc. reserves the right, without notice, to make changes in product design or specification.