# Si5356

## I<sup>2</sup>C Programmable, Any-Frequency 1-200 MHz, QUAD FREQUENCY 8-OUTPUT CLOCK GENERATOR

OEB pin disables all outputs or per

Low jitter: 50 ps pk-pk (typ), 100 ps

eliminates need for external power

bank OEB control via I<sup>2</sup>C

pk-pk period jitter (max)

supply filtering

-40 to +85 °C

Storage area networks

Switches/routers

Servers

Low power: 45 mA

Excellent PSRR performance

Core VDD: 1.8, 2.5, or 3.3 V

Small size: 4x4 mm 24-QFN

Industrial temperature range:

outputs: 1.8, 2.5, or 3.3 V

Separate VDDO for each bank of

#### Features

- Generates any frequency from 1 to 200 MHz on each of the 4 output banks

- Programmable frequency configuration

- Guaranteed 0 ppm frequency synthesis error for any combination of frequencies

- 25 or 27 MHz xtal or 5-200 MHz input clk

- Eight CMOS clock outputs

SILICON LABS

- Easy to use programming software

- Configurable "triple A" spread spectrum: any clock, any frequency, and with any spread amount

- Programmable output phase adjustment with <20 ps error

- Interrupt pin indicates LOS or LOL

#### Applications

- Printers

- Audio/video

- DSLAM

#### Description

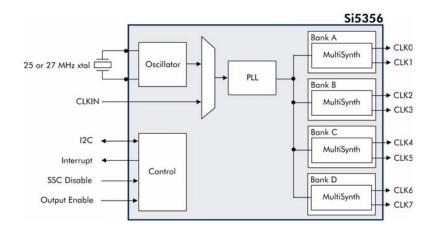

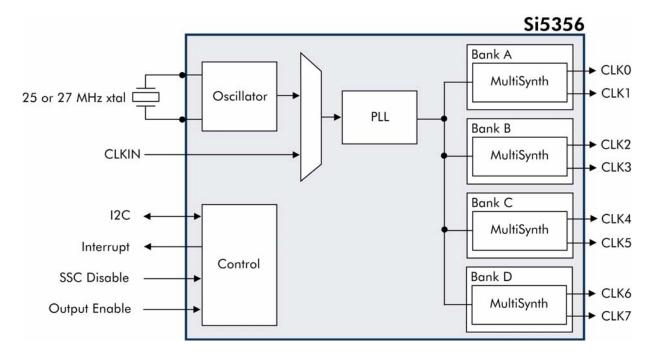

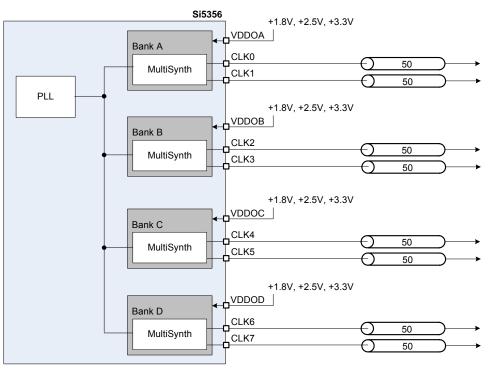

The Si5356 is a highly flexible, I<sup>2</sup>C programmable clock generator capable of synthesizing four completely non-integer related frequencies up to 200 MHz. The device has four banks of outputs with each bank supporting two CMOS outputs at the same frequency. Using Silicon Laboratories' patented MultiSynth fractional divider technology, all outputs are guaranteed to have 0 ppm frequency synthesis error regardless of configuration, enabling the replacement of multiple clock ICs and crystal oscillators with a single device. Each output bank is independently configurable to support 1.8, 2.5, or 3.3 V. The device is programmable via an I<sup>2</sup>C/ SMBus-compatible serial interface and supports operation from a 1.8, 2.5, or 3.3 V core supply.

#### **Functional Block Diagram**

Preliminary Rev. 0.3 2/11

#### Copyright © 2011 by Silicon Laboratories This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Si5356

# TABLE OF CONTENTS

### Section

### <u>Page</u>

| 1. Electrical Specifications            | .4 |

|-----------------------------------------|----|

| 2. Typical Application Circuits         | .8 |

| 3. Functional Description               | .9 |

| 3.1. Overview                           |    |

| 3.2. Input Configuration                | .9 |

| 3.3. Breakthrough MultiSynth Technology | 10 |

| 3.4. Frequency Configuration            | 11 |

| 3.5. Configuring the Si5356             |    |

| 3.6. Output Phase Adjustment            |    |

| 3.7. CMOS Output Drivers                |    |

| 3.8. Jitter Performance                 | 13 |

| 3.9. Status Indicators                  | 13 |

| 3.10. I2C Interface                     | 14 |

| 3.11. Spread Spectrum                   |    |

| 3.12. Power Supply Considerations       |    |

| 4. Si5356 Registers                     |    |

| 5. Pin Descriptions: Si5356             |    |

| 6. Ordering Guide                       |    |

| 7. Package Outline: 24-Lead QFN         |    |

| 8. Recommended PCB Layout               |    |

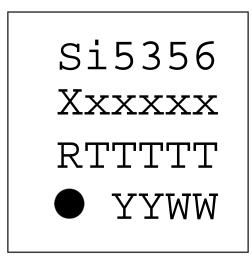

| 9. Top Marking                          |    |

| Document Change List                    |    |

| Contact Information                     |    |

|                                         | -  |

### **1. Electrical Specifications**

#### **Table 1. Recommended Operating Conditions**

$(V_{DD} = 1.8 \text{ V} - 5\% \text{ to } +10\%, 2.5 \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                       | Symbol           | Test Condition | Min  | Тур | Max  | Units |

|---------------------------------------------------------------------------------|------------------|----------------|------|-----|------|-------|

| Ambient Temperature                                                             | T <sub>A</sub>   |                | -40  | —   | 85   | °C    |

| Core Supply Voltage                                                             | V <sub>DD</sub>  |                | 2.97 | 3.3 | 3.63 | V     |

|                                                                                 |                  |                | 2.25 | 2.5 | 2.75 |       |

|                                                                                 |                  |                | 1.71 | 1.8 | 1.98 |       |

| Output Buffer Supply Voltage                                                    | V <sub>DDO</sub> |                | 1.71 |     | 3.63 | V     |

| Note: All minimum and maximun<br>conditions. Typical values<br>otherwise noted. |                  |                |      |     |      |       |

Table 2. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                            | Symbol            | Rating                        | Units |

|------------------------------------------------------|-------------------|-------------------------------|-------|

| Supply Voltage Range                                 | V <sub>DD</sub>   | -0.5 to +3.8                  | V     |

| Input Voltage Range (all pins except pins 1,2,5,6)   | VI                | –0.5 to 3.8                   | V     |

| Input Voltage Range (pins 1,2,5,6)                   | V <sub>I2</sub>   | –0.5 to 1.2                   | V     |

| Output Voltage Range                                 | V <sub>O</sub>    | –0.5 to V <sub>DD</sub> + 0.3 | V     |

| Storage Temperature Range                            | Τ <sub>S</sub>    | -55 to +150                   | °C    |

| ESD Tolerance                                        | HBM               | 2.5                           | kV    |

| -                                                    | CDM               | 550                           | V     |

| -                                                    | MM                | 175                           | V     |

| Latch-up Tolerance                                   | LU                | JESD78 Complia                | ant   |

| Soldering Temperature (Pb-free profile) <sup>2</sup> | T <sub>PEAK</sub> | 260                           | °C    |

Notes:

1. Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to maximum rating conditions for extended periods may affect device reliability. 2. The device is compliant with JEDEC J-STD-020C.

#### Table 3. DC Characteristics

$(V_{DD} = 1.8 \text{ V} -5\% \text{ to } +10\%, 2.5 \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                  | Symbol              | Test Condition                           | Min                    | Тур | Max                 | Units |

|--------------------------------------------|---------------------|------------------------------------------|------------------------|-----|---------------------|-------|

| Current Consumption                        | I <sub>DD</sub>     | 100 MHz on all outputs,<br>25 MHz refclk |                        | 45  | 60                  | mA    |

| High Level Input Voltage                   | V <sub>IH</sub>     | CLKIN, I2C_LSB                           | 0.8 x V <sub>DD</sub>  |     | 3.63                | V     |

|                                            |                     | SSC_DIS, OEB                             | 0.85                   |     | 1.3                 | V     |

| Low Level Input Voltage                    | V <sub>IL</sub>     | CLKIN, I2C_LSB                           | -0.2                   |     | $0.2 \times V_{DD}$ | V     |

|                                            |                     | SSC_DIS, OEB                             |                        |     | 0.3                 | V     |

| Clock Output High Level Output<br>Voltage  | V <sub>OH</sub>     | Pins: CLK0–7<br>I <sub>OH</sub> = –4 mA  | V <sub>DDO</sub> – 0.3 |     | _                   | V     |

| Clock Output Low Level Out-<br>put Voltage | V <sub>OL</sub>     | Pins: CLK0–7<br>I <sub>OH</sub> = +4 mA  |                        |     | 0.3                 | V     |

| INTR Low Level Output Voltage              | V <sub>OLINTR</sub> | Pin: LOS<br>I <sub>OH</sub> = +3 mA      | 0                      |     | 0.4                 | V     |

| SSC_DIS, OEB Input<br>Resistance           | R <sub>IN</sub>     |                                          | 20                     |     | —                   | kΩ    |

#### Table 4. AC Characteristics

(V<sub>DD</sub> = 1.8 V –5% to +10%, 2.5 or 3.3 V ±10%, T<sub>A</sub> = –40 to 85 °C)

| Parameter                                      | Symbol                         | Test Condition                                         | Min  | Тур  | Max  | Units    |

|------------------------------------------------|--------------------------------|--------------------------------------------------------|------|------|------|----------|

| Input Clock                                    |                                |                                                        | I    | 1    |      | 1        |

| Clock Input Frequency                          | F <sub>IN</sub>                |                                                        | 5    | _    | 200  | MHz      |

| Clock Input Rise/Fall Time                     | T <sub>R</sub> /T <sub>F</sub> | 20 to 80% V <sub>DD</sub>                              | _    | —    | 2    | ns       |

| Clock Input Duty Cycle                         | DC                             | < 2 ns tr/tf                                           | 40   | —    | 60   | %        |

| Clock Input Capacitance                        | C <sub>IN</sub>                |                                                        |      | 2    | _    | pF       |

| Output Clocks                                  |                                |                                                        | I    | 1    |      | 1        |

| Clock Output Frequency                         | F <sub>O</sub>                 |                                                        | 1    | _    | 200  | MHz      |

| Clock Output Frequency Synthesis<br>Resolution | F <sub>RES</sub>               | See "3.4. Frequency Con-<br>figuration" on page 11     |      | _    | 0    | ppm      |

| Output Load Capacitance                        | CL                             |                                                        | _    | 15   | _    | pF       |

| Clock Output Rise/Fall Time                    | T <sub>R</sub> /T <sub>F</sub> | 20 to 80% V <sub>DD</sub> ,<br>C <sub>L</sub> = 15 pF  |      | _    | 1.7  | ns       |

| Clock Output Rise/Fall Time                    | T <sub>R</sub> /T <sub>F</sub> | 20 to 80% V <sub>DD</sub> ,<br>C <sub>L</sub> = 2 pF   | _    | 0.45 | 0.85 | ns       |

| Clock Output Duty Cycle                        | DC                             | Measured at V <sub>DD</sub> /2                         | 45   | 50   | 55   | %        |

| Powerup Time                                   | T <sub>PU</sub>                | POR to output clock valid                              |      | _    | 2    | ms       |

| Output Enable Time                             | T <sub>OE</sub>                |                                                        |      | —    | 10   | μs       |

| Output-Output Skew                             | T <sub>SKEW</sub>              | Outputs at same<br>frequency, f <sub>OUT</sub> > 5 MHz | -150 | _    | +150 | ps       |

| Period Jitter                                  | J <sub>PPKPK</sub>             | 10000 cycles                                           | —    | 50   | 75   | ps pk-pk |

| Cycle-Cycle Jitter                             | J <sub>CCPK</sub>              | 10000 cycles                                           |      | 40   | 70   | ps pk    |

| Phase Jitter                                   | J <sub>PH</sub>                | 12 kHz to 20 MHz                                       |      | 2    |      | ps rms   |

| PLL Loop Bandwidth                             | F <sub>BW</sub>                |                                                        |      | 1.6  | _    | MHz      |

#### **Table 5. Crystal Specifications**

| Parameter                                  | Symbol            | Test Condition | Min | Тур | Max | Units |

|--------------------------------------------|-------------------|----------------|-----|-----|-----|-------|

| Crystal Frequency                          | F <sub>XTAL</sub> | Option 1       | _   | 25  | _   | MHz   |

|                                            |                   | Option 2       | —   | 27  | —   | MHz   |

| Load Capacitance<br>(on-chip differential) | CL                |                | 11  | 12  | 13  | pF    |

| Crystal Output Capacitance                 | C <sub>O</sub>    |                | —   | —   | 4   | pF    |

| Equivalent Series Resistance               | ESR               | 25 MHz         | _   | —   | 100 | Ω     |

|                                            |                   | 27 MHz         | _   | —   | 75  | Ω     |

| Max Drive Level                            | dL                |                | 100 | —   | —   | μW    |

#### Table 6. Thermal Characteristics

| Parameter                                 | Symbol        | Test Condition | Value | Unit |

|-------------------------------------------|---------------|----------------|-------|------|

| Thermal Resistance<br>Junction to Ambient | $\theta_{JA}$ | Still Air      | 37    | °C/W |

| Thermal Resistance<br>Junction to Case    | $\theta^{JC}$ | Still Air      | 25    | °C/W |

### Table 7. I<sup>2</sup>C Specifications (SCL,SDA)<sup>2</sup>

| Parameter                                                            | Symbol Test Condition Standard Mode |                                         | d Mode                 | Fast N                 | Unit                         |                                     |    |

|----------------------------------------------------------------------|-------------------------------------|-----------------------------------------|------------------------|------------------------|------------------------------|-------------------------------------|----|

|                                                                      |                                     |                                         | Min                    | Max                    | Min                          | Max                                 |    |

| LOW level input voltage:                                             | V <sub>ILI2C</sub>                  |                                         | -0.5                   | 0.3*V <sub>DDI2C</sub> | -0.5                         | 0.3*V <sub>DDI2C</sub> <sup>1</sup> | V  |

| HIGH level input voltage:                                            | V <sub>IHI2C</sub>                  |                                         | 0.7*V <sub>DDI2C</sub> | 3.63                   | 0.7*<br>V <sub>DDI2C</sub> 1 | 3.63                                | V  |

| Hysteresis of<br>Schmitt trigger<br>inputs                           | V <sub>HYS</sub>                    |                                         | N/A                    | N/A                    | 0.1                          | _                                   | V  |

| LOW level output                                                     | V <sub>OLI2C</sub> <sup>1</sup>     | $V_{DDI2C}^{1} = 2.5 / 3.3 V$           | 0                      | 0.4                    | 0                            | 0.4                                 | V  |

| voltage (open drain<br>or open collector)<br>at 3 mA sink<br>current |                                     | V <sub>DDI2C</sub> <sup>1</sup> = 1.8 V | N/A                    | N/A                    | 0                            | 0.2 x V <sub>DDI2C</sub>            | V  |

| Input current                                                        | I <sub>II2C</sub>                   |                                         | -10                    | 10                     | -10                          | 10                                  | μA |

| Capacitance for each I/O pin                                         | C <sub>II2C</sub>                   | $V_{IN}$ = -0.1 to $V_{DDI2C}$          |                        | 4                      | —                            | 4                                   | pF |

| I <sup>2</sup> C Bus timeout                                         |                                     |                                         | 25                     | 35                     | 25                           | 35                                  | ms |

Notes:

Only I<sup>2</sup>C pull up voltages (VDDI2C) of 1.71 to 3.63 V are supported. Must write register 27[7] = 1 if the I<sup>2</sup>C bus voltage is less than 2.25 V.

**2.** Refer to NXP's UM10204 I<sup>2</sup>C-bus specification and user manual, revision 03, for further details: www.nxp.com/acrobat\_download/usermanuals/UM10204\_3.pdf.

**3.** Compliant with Fast Mode+ pending characterization.

Preliminary Rev. 0.3

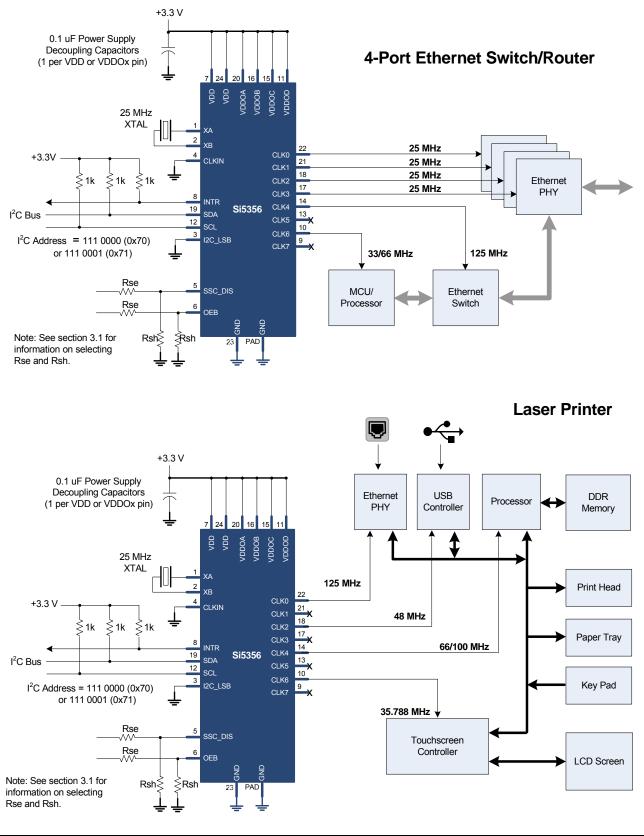

### 2. Typical Application Circuits

### 3. Functional Description

#### 3.1. Overview

The Si5356 is a highly flexible, I<sup>2</sup>C programmable clock generator capable of synthesizing four independent frequencies up to 200 MHz. The device has four banks of outputs with each bank supporting two CMOS outputs at the same frequency. The Si5356 supports free-running mode of operation using an external crystal, or it can lock to an external clock for generating synchronous clocks. The output drivers support 1.8, 2.5, and 3.3 V CMOS formats, and each output bank is independently configurable. Adjustable output-to-output phase offsets are also available to compensate for PCB trace delays or for fine tuning of setup and hold margins.

Configuration and control of the Si5356 is handled through the  $I^2C/SMBus$  interface. The device also provides the option of storing a user-definable clock configuration in its non-volatile memory (NVM), which becomes the default clock configuration an power-up. See section "3.5.1. Ordering a Custom NVM Configuration" on page 11 for details.

#### 3.1.1. ClockBuilder™ Desktop Software

To simplify device configuration, Silicon Labs has released the ClockBuilder Desktop. The software serves two purposes: to configure the Si5356 with optimal configuration based on the desired frequencies, and to control the EVB, when connected to a host PC.

The optimal configuration can be saved from the software in text files that can be used in any system, which configures the device over  $I^2C$ . ClockBuilder Desktop can be downloaded from www.silabs.com/ ClockBuilder and runs on Windows XP, Windows Vista, and Windows 7. Additionally, an NVM file can be generated using the NVM—Save for Factory Programming... menu option. An NVM file can be used by factory to prepare custom pre-programmed devices.

#### 3.2. Input Configuration

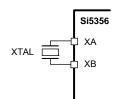

The Si5356 input can be driven from either an external crystal or a reference clock. If the crystal input option is used, the Si5356 operates as a free-running clock generator. In this mode of operation the device requires a low cost 25 or 27 MHz fundamental mode crystal connected across XA and XB as shown in Figure 1. Given the Si5356's frequency flexibility, the same crystal can be reused to generate any combination of output frequencies. Custom frequency crystals are not required. The Si5356 integrates the crystal load capacitors on-chip to reduce external component count. The crystal should be placed very close to the device to minimize stray capacitance. To ensure a stable and accurate output frequency, the recommended crystal specifications provided in Table 5 on page 7 must be followed. See AN360 for additional details regarding crystal recommendations.

#### Figure 1. Connecting an XTAL to the Si5356

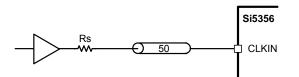

For synchronous timing applications, the Si5356 can lock to a 5 to 200 MHz CMOS reference clock. A typical interface circuit is shown in Figure 2. A series termination resistor matching the driver's output impedance to the impedance of the transmission line is recommended to reduce reflections.

# Figure 2. Interfacing CMOS Reference Clocks to the Si5356

Control input signals to SSC\_DIS and OEB cannot exceed 1.3 V yet also need to meet the VOH and VOL specifications outlined in Table 3 on page 5. When these inputs are driven from CMOS sources, a resistive attenuator as shown in the Typical Application Circuits must be used. Suggested standard 1% resistor values for RSE and RSH, when using a CMOS source, are given below.

| CMOS Level | RSE ohms | RSH ohms |

|------------|----------|----------|

| 1.8 V      | 1000     | 1580     |

| 2.5 V      | 1960     | 1580     |

| 3.3 V      | 3090     | 1580     |

#### 3.3. Breakthrough MultiSynth Technology

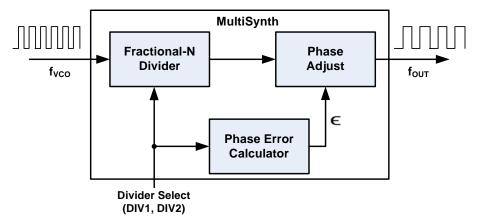

Modern timing architectures require a wide range of frequencies which are often non-integer related. Traditional clock architectures address this by using a combination of single PLL ICs, 4-PLL ICs and discrete XOs, often at the expense of BOM complexity and power. The Si5356 use patented MultiSynth technology to dramatically simplify timing architectures by integrating the frequency synthesis capability of 4 phase-locked loops (PLLs) in a single device, greatly minimizing size and power requirements versus traditional solutions. Based on a fractional-N PLL, the heart of the architecture is a low phase noise, highfrequency VCO. The VCO supplies a high frequency output clock to the MultiSynth block on each of the four independent output paths. Each MultiSynth operates as a high-speed fractional divider with Silicon Laboratories' proprietary phase error correction to divide down the VCO clock to the required output frequency with very low jitter.

The first stage of the MultiSynth architecture is a fractional-N divider which switches seamlessly between the two closest integer divider values to produce the exact output clock frequency with 0 ppm error. To eliminate phase error generated by this process, MultiSynth calculates the relative phase difference between the clock produced by the fractional-N divider and the desired output clock and dynamically adjusts the phase to match the ideal clock waveform. This novel approach makes it possible to generate any output clock frequency without sacrificing jitter performance. Based on this architecture, each clock output can produce any frequency from 1 to 200 MHz.

#### Figure 3. Silicon Labs' MultiSynth Technology

#### 3.4. Frequency Configuration

The Si5356 utilizes a single PLL-based architecture, four independent MultiSynth fractional output dividers, and a MultiSynth fractional feedback divider such that a single device provides the clock generation capability of four independent PLLs. Unlike competitive multi-PLL solutions, the Si5356 can generate four unique non-integer related output frequencies with 0 ppm frequency error, with respect to the reference, for any combination of output frequencies. In addition, any combination of output frequencies can be generated from a single reference frequency without having to change the crystal or reference clock frequency between configurations.

Frequency configurations are fully programmable by writing to device registers using the  $I^2C$  interface. Any combination of output frequencies ranging from 1 to 200 MHz can be configured on each of the device outputs.

The following equation governs how the output frequency is calculated.

$$f_{OUT} = \frac{f_{IN} \times N}{P \times M_i}$$

where  $f_{IN}$  is the reference frequency, N is the MultiSynth feedback divider value, P is the reference divider value,  $M_i$  is the MultiSynth output divider value and  $f_{OUT}$  is the resulting output frequency. The MultiSynth output and feedback dividers are fractional dividers expressed in terms of an integer and a fraction. The integer portion has 10-bit resolution and the fractional portion has 30bit resolution in both the numerator and denominator, meaning that any output frequency can be defined exactly from the input frequency with exact (0 ppm) frequency synthesis error.

#### 3.5. Configuring the Si5356

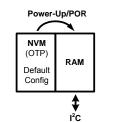

The Si5356 is a highly-flexible clock generator that is entirely configurable through its  $I^2C$  interface. The device's default configuration is stored in non-volatile memory (NVM) as shown in Figure 4. The NVM is a one-time programmable memory (OTP), which can store a custom user configuration at power-up. This is a useful feature for applications that need a clock present at power-up (e.g., for providing a clock to a processor).

During a power cycle or a power-on reset (POR), the contents of the NVM are copied into random access memory (RAM), which sets the device configuration that will be used during operation. Any changes to the device configuration after power-up are made by reading and writing to registers in the RAM space through the I<sup>2</sup>C interface. ClockBuilder Desktop (see "3.1.1. ClockBuilder™ Desktop Software" on page 9) can be used to easily configure register map files that can be written into RAM (see "3.5.2. Creating a New Configuration for RAM" for details). Alternatively, the register map file can be created manually with the help of the equations in AN565.

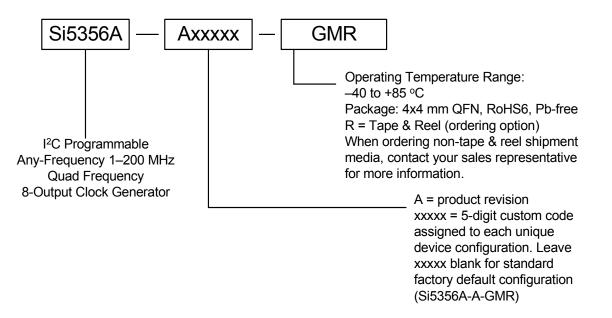

Two versions of the Si5356 are available. First, noncustomized Si5356 devices are available in which the RAM can be configured in-circuit via I<sup>2</sup>C. These blank Si5356 devices can also be field programmed using the Si5338/56-PROG-EVB (see "3.5.5. Writing a Custom Configuration to NVM"). Second, custom factoryprogrammed Si5356 devices are available that include a user-specified startup frequency configuration (example part number Si5356A-Axxxxx-GM).

#### 3.5.1. Ordering a Custom NVM Configuration

The Si5356 is orderable with a factory-programmed custom NVM configuration. This is the simplest way of using the Si5356 since it generates the desired output frequencies at power-up or after a power-on reset (POR). This default configuration can be reconfigured in RAM through the  $I^2C$  interface after power-up (see "3.5.2. Creating a New Configuration for RAM").

The first step in ordering a custom device is generating an NVM file which defines the input and output clock frequencies and signal formats. This is easily done using the NVM $\rightarrow$ Save for Factory Programming... menu option in ClockBuilder Desktop. (See "3.1.1. ClockBuilder<sup>TM</sup> Desktop Software" on page 9.) This Windows based software allows the user to generate an NVM file, which is used by the factory to manufacture custom parts. Each custom part is marked with a unique part number identifying the specific configuration (e.g., Si5356A-A00100-GM).

Consult your local sales representative for more details on ordering a custom Si5356.

#### 3.5.2. Creating a New Configuration for RAM

Any Si5356 device can be configured by writing to registers in RAM through the  $I^2C$  interface. A non-factory programmed device must be configured in this manner.

Figure 4. Si5356 Memory Configuration

When creating a custom RAM configuration, use the following procedure:

- Create a device configuration (register map) using ClockBuilder Desktop (v2.7 or later; see "3.1.1. ClockBuilder™ Desktop Software" on page 9) or manually using the equations in "AN565: Configuring the Si5356A".

- a. Configure the frequency plan.

- b. Configure the output driver format and supply voltage.

- c. Configure initial phase offset (if desired).

- d. Configure spread spectrum (if desired).

- 2. Save the configuration using the Options > Save Register Map File or Options > Save C code Header File, or create the register contents by the conversions listed in AN565.

At this point, the new configuration can be written to the device RAM according to the instructions in "3.5.3. Writing a Custom Configuration to RAM".

#### 3.5.3. Writing a Custom Configuration to RAM

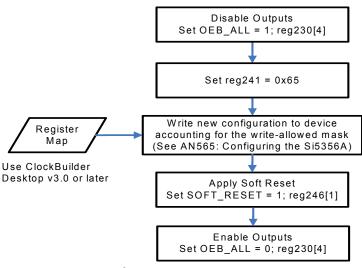

Writing a new configuration (register map) to the RAM consists of pausing the LOL state-machine, writing new values to the IC accounting for the write-allowed mask given in AN565, validating the input clock or crystal, locking the PLL to the input with the new configuration, restarting the LOL state-machine, and calibrating the VCO for robust operation across temperature. The flow chart in Figure 5 on page 12 enumerates the details:

**Note:** The write-allowed mask specifies which bits must be read and modified before writing the entire register byte (a.k.a. read-modify-write). "AN428: Jump Start: In-System, Flash-Based Programming for Silicon Labs' Timing Products" illustrates the procedure defined in Section 3.5.2 with ANSI C code.

#### 3.5.4. Modifying a MultiSynth Output Divider Ratio/ Frequency Configuration

Any of the four output frequencies of a previously configured Si5356 may be modified without disturbing the other outputs. In this case, do not write the feedback Multisynth registers. Instead, only write the set of registers associated with the output MultiSynth divider of interest (see "AN565: Configuring the Si5356A").

To avoid intermediate frequencies, it is recommended that the output to be modified is disabled before changing the divider ratios (see AN565 for a description of Register 230).

Any output Multisynth that is reconfigured will lose its output skew alignment with the other outputs. SOFT\_RESET can be used to realign the outputs; however, a soft reset will temporarily disable all outputs in the process of realignment.

#### 3.5.5. Writing a Custom Configuration to NVM

An alternative to ordering an Si5356 with a custom NVM configuration is to use the field programming kit (Si5338/56-PROG-EVB) to write directly to the NVM of a "blank" Si5356. Since NVM is an OTP memory, it can only be written once. The default configuration can be reconfigured by writing to RAM through the I<sup>2</sup>C interface (see "3.5.2. Creating a New Configuration for RAM").

#### 3.6. Output Phase Adjustment

The Si5356 has a digitally-controlled phase adjustment feature that allows the user to adjust the phase of each output clock in relation to the other output clocks. The phase of each output clock can be adjusted with an error of <20 ps over a range of  $\pm$ 45 ns. This feature is available on any clock output that does not have Spread Spectrum enabled.

Figure 5. I<sup>2</sup>C Programming Procedure

#### 3.7. CMOS Output Drivers

The Si5356 has 4 banks of outputs with each bank comprised of 2 clocks for a total of 8 CMOS outputs per device. By default, each bank of CMOS output clocks are in-phase. Alternatively, each output clock can be inverted. This feature enables each output pair to operate as a differential CMOS clock. Each of the output banks can operate from a different VDDO supply (1.8 V, 2.5 V, 3.3 V), simplifying usage in mixed supply applications. All clock outputs between 5 and 200 MHz are in-phase to within ±150 ps.

The CMOS output driver has a controlled impedance in the range of 42 to 50  $\Omega$ , which includes an internal 22  $\Omega$  series resistor. An external series resistor is not needed when driving 50  $\Omega$  traces. If higher impedance traces are used then a series resistor may be added. A typical configuration is shown in Figure 6.

#### 3.8. Jitter Performance

The Si5356 provides consistently low jitter for any combination of output frequencies. The device leverages a low phase noise single PLL architecture and Silicon Laboratories' patented MultiSynth fractional output divider technology to deliver period jitter less than 100 ps pk-pk (max) for any frequency configuration. This level of jitter performance is

guaranteed across process, temperature and voltage. The Si5356 provides superior performance to traditional multi-PLL solutions which may suffer from degraded jitter performance depending on frequency plan and the number of active PLLs.

#### 3.9. Status Indicators

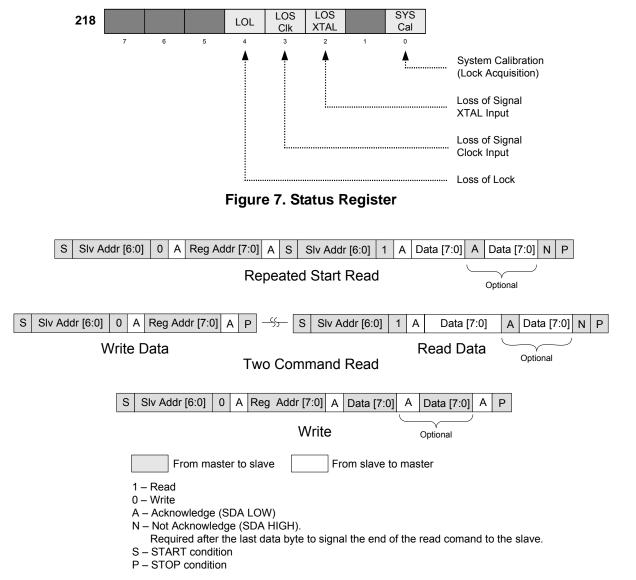

An interrupt pin (INTR) is available to indicate a loss of signal (LOS) condition, a PLL loss of lock (LOL) condition, or that the PLL is in the process of acquiring lock (SYS CAL). As shown in Figure 7, a status register at address 218 is available to help identify the exact event that caused the interrupt pin to become active. A LOS condition occurs when there is no clock input to the Si5356. The loss of lock algorithm works by continuously monitoring the frequency difference between the two inputs of the phase frequency detector. When this frequency difference is greater than 1000 ppm, a loss of lock condition is declared. Note that the VCO will track the input clock frequency for up to ~25000 ppm, which will keep the inputs to the phase frequency detector at the same frequency until the PLL comes out of lock. When a clock input is removed, the interrupt pin will assert, and the clock outputs may drift up to 5%. When the input clock is reapplied with an appropriate frequency, the PLL will again lock.

Figure 6. CMOS Output Driver Configuration

Preliminary Rev. 0.3

### 3.10. I<sup>2</sup>C Interface

The Si5356 control interface is a 2-wire bus for bidirectional communication. The bus consists of a bidirectional serial data line (SDA) and a serial clock input (SCL). The device operates as a slave device on the 2-wire bus and is compatible with  $I^2C$  specifications. Both lines must be connected to the positive supply via an external pull-up. Standard-Mode (100 kbps) and Fast-Mode (400 kbps) operation and 7-bit addressing are supported as specified in the  $I^2C$ -Bus Specification standard. To accommodate multiple Si5356 devices on the same  $I^2C$  bus, the Si5356 has pin 3 as  $I2C\_LSB$ . The complete 7-bit I2C bus address for the device is 70h or 71h depending upon the state of the I2C\\_LSB]. See

Figure 8 for the command format for both read and write access.

Data is always sent MSB first. Table 7 includes the AC and DC electrical parameters for the SCL and SDA I/ Os, respectively. The timing specifications and timing diagram for the  $I^2C$  bus can be found in the  $I^2C$ -Bus Specification standard. SDA timeout support is supported for compatibility with SMBus interfaces.

The I<sup>2</sup>C interface is 3.3 V tolerant.

The I<sup>2</sup>C bus can be operated at a bus voltage of 1.71 to 3.63 V and should have a pullup resistor as recommended by the I<sup>2</sup>C-Bus Specification.

#### Figure 8. I<sup>2</sup>C/SMBus-Compatible Command Format

14

#### 3.11. Spread Spectrum

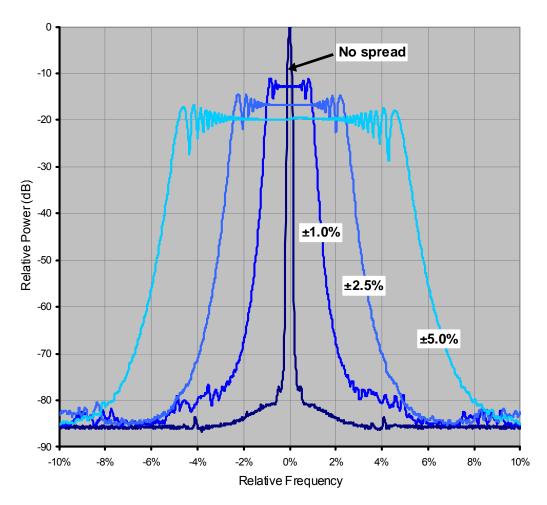

To reduce electro magnetic interference (EMI), the Si5356 supports spread spectrum modulation. The output clock frequencies can be modulated to spread energy across a broader range of frequencies, lowering system EMI. The modulation rate is the time required to transition from the maximum spread spectrum frequency to the minimum spread spectrum frequency and then back to the maximum frequency.

The Si5356 implements spread spectrum using patented MultiSynth technology to achieve previously unattainable precision in both modulation rate and spreading magnitude as shown in Figure 9. This enables the Si5356 to provide "triple A" spread spectrum. Spread spectrum can be applied to *any*

output clock, *any* clock frequency, and *any* spread amount. Spread spectrum can be enabled or disabled on a per-bank basis. The device supports center spread ( $\pm 0.1\%$  to  $\pm 5\%$ ) and down spread (-0.1% to -5%). In addition, the device has extensive on-chip voltage regulation such that power supply variation does not influence the device's spread spectrum clock waveforms.

The programming of Spread Spectrum is made easy by using the Si5356 Programmer. Spread spectrum on all the outputs can be enabled or disabled using the SSC\_DIS pin, or independently for each output bank through the  $I^2C$  interface.

Figure 9. Configurable Spread Spectrum

#### 3.12. Power Supply Considerations

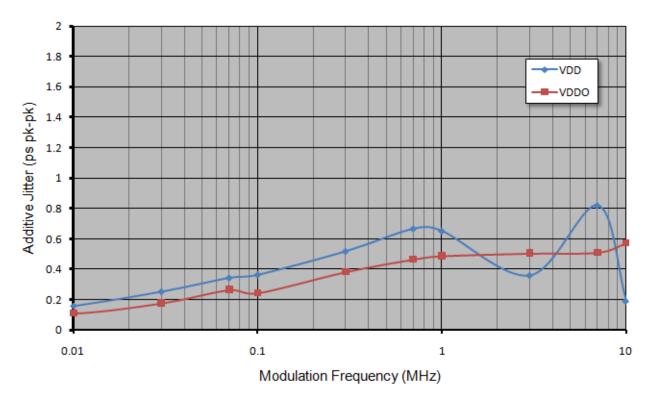

The Si5356 has two core supply voltage pins ( $V_{DD}$ ) and four clock output bank supply voltage pins ( $V_{DDOA}$ –  $V_{DDOD}$ ), enabling the device to be used in mixed supply applications. The Si5356 does not require ferrite beads for power supply filtering. The device has extensive on-chip power supply regulation to minimize the impact of power supply noise on output jitter. Figure 10 shows that the additive jitter created when a significant amount of noise is applied to the device power supply is very small.

Figure 10. Peak-to-Peak Additive Jitter from 100 mV Sine Wave on Supply

### 4. Si5356 Registers

For many applications, the Si5356's register values are easily configured using ClockBuilder Desktop (see "3.1.1. ClockBuilder™ Desktop Software" on page 9). However, for customers interested in using the Si5356 in operating modes beyond the capabilities available with ClockBuilder, refer to "AN565: Configuring the Si5356A" for a detailed description of the Si5356 registers and their usage. Also refer to "AN428: Jump Start: In-System, Flash-Based Programming for Silicon Labs' Timing Products" for a working application example of register programming using the Silicon Labs' C8051F301 MCU.

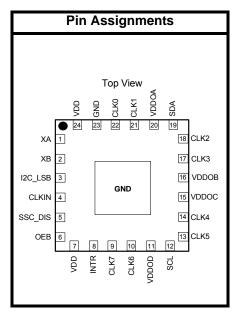

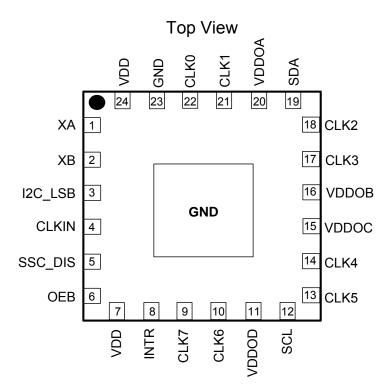

### 5. Pin Descriptions: Si5356

Note: Center pad must be tied to GND for normal operation.

#### Table 8. Si5356 Pin Descriptions

| Pin # | Pin Name | I/O | Description                                                                                                                                                                                                                                                                                      |

|-------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | XA       |     | External Crystal.                                                                                                                                                                                                                                                                                |

|       |          |     | If a 25 or 27 MHz crystal is used as the device frequency reference, connect it across XA and XB. If no input clock is used, this pin should be tied to GND.                                                                                                                                     |

| 2     | XB       | I   | External Crystal.                                                                                                                                                                                                                                                                                |

|       |          |     | If a 25 or 27 MHz crystal is used as the device frequency reference, connect it across XA and XB. If no input clock is used, this pin should be tied to GND.                                                                                                                                     |

| 3     | I2C_LSB  | I   | I <sup>2</sup> C LSB Address Bit                                                                                                                                                                                                                                                                 |

|       |          |     | This pin is the least significant bit of the Si5356 $I^2C$ address allowing up to two Si5356 devices to occupy the same $I^2C$ bus.                                                                                                                                                              |

| 4     | CLKIN    | I   | Single-Ended Input Clock.                                                                                                                                                                                                                                                                        |

|       |          |     | If a single-ended clock is used as the device frequency reference, connect it to this pin.<br>This pin functions as a high-impedance input for CMOS clock signals. The input should<br>be dc coupled. If a crystal is used as the device frequency reference, this pin should be<br>tied to GND. |

| 5                          | SSC_DIS                        | Ι               | <b>Spread Spectrum Disable.</b><br>This pin allows disabling of the spread spectrum feature on the output clocks. Connect to 1.2 V to disable spread spectrum on all outputs. Connect to GND to enable spread spectrum. Note that the maximum voltage level on this pin must not exceed 1.2 V. A resistor voltage divider is recommended when controlled by a signal greater than 1.2 V. See the Typical Application Circuit for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------|--------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6                          | OEB                            | I               | Output Enable (Active Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                            |                                |                 | This pin allows disabling the output clocks. Connect to 1.2 V to disable all outputs.<br>Connect to GND to enable all outputs. Note that the maximum voltage level on this pin<br>must not exceed 1.2 V. A resistor voltage divider is recommended when controlled by a<br>signal greater than 1.2 V. See the Typical Application Circuit for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7                          | VDD                            | VDD             | Core Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                            |                                |                 | The device operates from a 1.8, 2.5, or 3.3 V supply. A 0.1 $\mu F$ bypass capacitor should be located very close to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8                          | INTR                           | 0               | Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            |                                |                 | This pin functions as an maskable interrupt output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                            |                                |                 | 0 = No interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            |                                |                 | 1 = Interrupt present                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            |                                | -               | This pin is open drain and requires an external $\geq 1 \text{ k}\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9                          | CLK7                           | 0               | Output Clock 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                            |                                |                 | CMOS output clock. If unused, this pin must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10                         | CLK6                           | 0               | Output Clock 6.<br>CMOS output clock. If unused, this pin must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11                         | VDDOD                          | VDD             | Clock Output Bank D Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                            |                                |                 | Power supply for clock outputs 6 and 7. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 $\mu$ F bypass capacitor should be located very close to this pin. If CLK6/7 are not used, this pin must be tied to pin 7 and/or pin 24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            |                                |                 | I <sup>2</sup> C Serial Clock Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12                         | SCL                            | -               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12<br>13                   | SCL<br>CLK5                    | <br>0           | Output Clock 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                            |                                |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                            |                                |                 | Output Clock 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13                         | CLK5                           | 0               | Output Clock 5.<br>CMOS output clock. If unused, this pin must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13<br>14                   | CLK5<br>CLK4                   | 0               | Output Clock 5.         CMOS output clock. If unused, this pin must be left floating.         Output Clock 4.         CMOS output clock. If unused, this pin must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13                         | CLK5                           | 0               | Output Clock 5.<br>CMOS output clock. If unused, this pin must be left floating.<br>Output Clock 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13<br>14                   | CLK5<br>CLK4                   | 0               | Output Clock 5.         CMOS output clock. If unused, this pin must be left floating.         Output Clock 4.         CMOS output clock. If unused, this pin must be left floating.         Clock Output Bank C Supply Voltage.         Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13<br>14                   | CLK5<br>CLK4                   | 0               | Output Clock 5.         CMOS output clock. If unused, this pin must be left floating.         Output Clock 4.         CMOS output clock. If unused, this pin must be left floating.         Clock Output Bank C Supply Voltage.         Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V sup-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13<br>14                   | CLK5<br>CLK4                   | 0               | Output Clock 5.         CMOS output clock. If unused, this pin must be left floating.         Output Clock 4.         CMOS output clock. If unused, this pin must be left floating.         Clock Output Bank C Supply Voltage.         Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13<br>14<br>15             | CLK5<br>CLK4<br>VDDOC          | O<br>O<br>VDD   | Output Clock 5.CMOS output clock. If unused, this pin must be left floating.Output Clock 4.CMOS output clock. If unused, this pin must be left floating.Clock Output Bank C Supply Voltage.Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.Clock Output Bank B Supply Voltage.Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V sup-                                                                                                                                                                                                                                                                                                                                        |

| 13<br>14<br>15             | CLK5<br>CLK4<br>VDDOC          | O<br>O<br>VDD   | <ul> <li>Output Clock 5.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> <li>Output Clock 4.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> <li>Clock Output Bank C Supply Voltage.</li> <li>Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Clock Output Bank B Supply Voltage.</li> <li>Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> </ul>                                                                                                 |

| 13<br>14<br>15<br>16       | CLK5<br>CLK4<br>VDDOC<br>VDDOB | O<br>VDD<br>VDD | Output Clock 5.CMOS output clock. If unused, this pin must be left floating.Output Clock 4.CMOS output clock. If unused, this pin must be left floating.Clock Output Bank C Supply Voltage.Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.Clock Output Bank B Supply Voltage.Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK2/3 are not used, this pin must be tied to pin 7 and/or pin 24.                                                                                                                                                                                           |

| 13<br>14<br>15             | CLK5<br>CLK4<br>VDDOC          | O<br>O<br>VDD   | <ul> <li>Output Clock 5.<br/>CMOS output clock. If unused, this pin must be left floating.</li> <li>Output Clock 4.<br/>CMOS output clock. If unused, this pin must be left floating.</li> <li>Clock Output Bank C Supply Voltage.<br/>Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Clock Output Bank B Supply Voltage.<br/>Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Output Clock 3.</li> </ul>                                                                                            |

| 13<br>14<br>15<br>16<br>17 | CLK5<br>CLK4<br>VDDOC<br>VDDOB | O<br>VDD<br>VDD | <ul> <li>Output Clock 5.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> <li>Output Clock 4.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> <li>Clock Output Bank C Supply Voltage.</li> <li>Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Clock Output Bank B Supply Voltage.</li> <li>Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Output Clock 3.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> </ul> |

| 13<br>14<br>15<br>16       | CLK5<br>CLK4<br>VDDOC<br>VDDOB | O<br>VDD<br>VDD | Output Clock 5.CMOS output clock. If unused, this pin must be left floating.Output Clock 4.CMOS output clock. If unused, this pin must be left floating.Clock Output Bank C Supply Voltage.Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.Clock Output Bank B Supply Voltage.Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK2/3 are not used, this pin must be tied to pin 7 and/or pin 24.Output Clock 3.CMOS output clock. If unused, this pin must be left floating.Output Clock 2.                                                                                                |

| 13<br>14<br>15<br>16<br>17 | CLK5<br>CLK4<br>VDDOC<br>VDDOB | O<br>VDD<br>VDD | <ul> <li>Output Clock 5.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> <li>Output Clock 4.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> <li>Clock Output Bank C Supply Voltage.</li> <li>Power supply for clock outputs 4 and 5. May be operated from a 1.8, 2.5 or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Clock Output Bank B Supply Voltage.</li> <li>Power supply for clock outputs 2 and 3. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 μF bypass capacitor should be located very close to this pin. If CLK4/5 are not used, this pin must be tied to pin 7 and/or pin 24.</li> <li>Output Clock 3.</li> <li>CMOS output clock. If unused, this pin must be left floating.</li> </ul> |

| 20         | VDDOA | VDD | <b>Clock Output Bank A Supply Voltage.</b><br>Power supply for clock outputs 0 and 1. May be operated from a 1.8, 2.5, or 3.3 V supply. A 0.1 $\mu$ F bypass capacitor should be located very close to this pin. If CLK0/1 are not used, this pin must be tied to pin 7 and/or pin 24.                  |

|------------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21         | CLK1  | 0   | Output Clock 1.<br>CMOS output clock. If unused, this pin must be left floating.                                                                                                                                                                                                                        |

| 22         | CLK0  | 0   | Output Clock 0.<br>CMOS output clock. If unused, this pin must be left floating.                                                                                                                                                                                                                        |

| 23         | GND   | GND | <b>Ground.</b><br>Must be connected to system ground. Minimize the ground path impedance for optimal performance of the device.                                                                                                                                                                         |

| 24         | VDD   | VDD | Core Supply Voltage.<br>The device operates from a 1.8, 2.5, or 3.3 V supply. A 0.1 $\mu$ F bypass capacitor should be located very close to this pin.                                                                                                                                                  |

| GND<br>PAD | GND   | GND | <b>Ground Pad.</b><br>This is the large pad in the center of the package. Device specifications cannot be guar-<br>anteed unless the ground pad is properly connected to a ground plane on the PCB. See<br>"8. Recommended PCB Layout" on page 23 for the PCB pad sizes and ground via<br>requirements. |

#### Table 8. Si5356 Pin Descriptions (Continued)

### 6. Ordering Guide

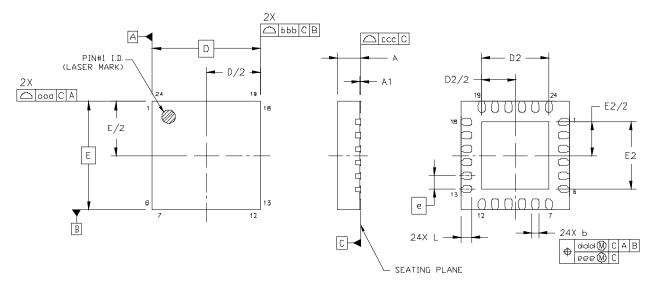

### 7. Package Outline: 24-Lead QFN

Figure 11. 24-Lead Quad Flat No-Lead (QFN)

| Dimension | Min       | Nom  | Max  |

|-----------|-----------|------|------|

| А         | 0.80      | 0.85 | 0.90 |

| A1        | 0.00      | 0.02 | 0.05 |

| b         | 0.18      | 0.25 | 0.30 |

| D         | 4.00 BSC. |      |      |

| D2        | 2.35      | 2.50 | 2.65 |

| е         | 0.50 BSC. |      |      |

| E         | 4.00 BSC. |      |      |

| E2        | 2.35      | 2.50 | 2.65 |

| L         | 0.30      | 0.40 | 0.50 |

| aaa       | 0.10      |      |      |

| bbb       | 0.10      |      |      |

| CCC       | 0.08      |      |      |

| ddd       | 0.10      |      |      |

| eee       | 0.05      |      |      |

#### **Table 9. Package Dimensions**

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Outline MO-220, variation VGGD-8.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

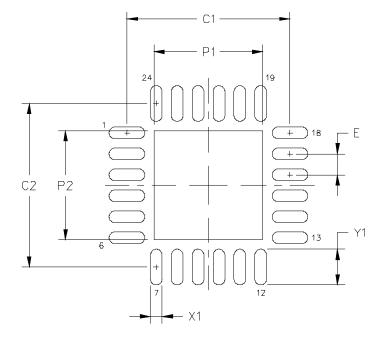

### 8. Recommended PCB Layout

Table 10. PCB Land Pattern

| Dimension | Min  | Nom  | Max  |

|-----------|------|------|------|

| P1        | 2.50 | 2.55 | 2.60 |

| P2        | 2.50 | 2.55 | 2.60 |

| X1        | 0.20 | 0.25 | 0.30 |

| Y1        | 0.75 | 0.80 | 0.85 |

| C1        | 3.90 |      |      |

| C2        | 3.90 |      |      |

| E         | 0.50 |      |      |

| Notes:    |      |      |      |

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. Connect the center ground pad to a ground plane with no less than five vias. These 5 vias should have a length of no more than 20 mils to the ground plane. Via drill size should be no smaller than 10 mils. A longer distance to the ground plane is allowed if more vias are used to keep the inductance from increasing.

#### Solder Mask Design

**5.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### **Stencil Design**

- 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- 9. A 2x2 array of 1.0 mm square openings on 1.25 mm pitch should be used for the center ground pad.

#### Card Assembly

- 10. A No-Clean, Type-3 solder paste is recommended.