## PIN-PROGRAMMABLE PRECISION CLOCK MULTIPLIER

#### **Features**

- Not recommended for new designs. For alternatives, see the Si533x family of products.

- Selectable output frequencies ranging from 19.44 to 1050 MHz

- Low jitter clock outputs with jitter LOS alarm output generation as low as 0.6 ps<sub>RMS</sub> ■ Pin-programmable settings (50 kHz-80 MHz)

- Integrated loop filter with selectable loop bandwidth (150 kHz to 1.3 MHz)

- Dual clock inputs with manual or automatically controlled switching

- Dual clock outputs with selectable signal format: LVPECL, LVDS, CML, CMOS

- Support for ITU G.709 FEC ratios (255/238, 255/237, 255/236)

- On-chip voltage regulator for 1.8 V ±5%, 2.5 or 3.3 V ±10% operation

- Small size: 6 x 6 mm 36-lead QFN

- Pb-free, RoHS compliant

See page 18.

### **Applications**

- SONET/SDH OC-48/STM-16 and OC-192/STM-64 line cards

- GbE/10GbE, 1/2/4/8/10GFC line Test and measurement cards

- ITU G.709 line cards

- Optical modules

### **Description**

The Si5322 is a low jitter, precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, Ethernet, and Fibre Channel. The Si5322 accepts dual clock inputs ranging from 19.44 to 707 MHz and generates two equal frequency-multiplied clock outputs ranging from 19.44 to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, and Fibre Channel rates. The Si5322 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides anyfrequency synthesis in a highly-integrated PLL solution that eliminates the need for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5322 is ideal for providing clock multiplication in high performance timing applications.

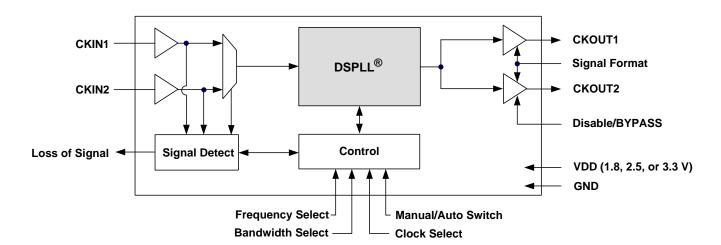

### **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                                                | <u>Page</u> |

|---------------------------------------------------------------|-------------|

| 1. Electrical Specifications                                  |             |

| 1.1. Three-Level (3L) Input Pins (No External Resistors)      |             |

| 1.2. Three-Level Input Pins (Example with External Resistors) | )           |

| 2. Functional Description                                     |             |

| 2.1. Further Documentation                                    |             |

| 3. Pin Descriptions: Si5322                                   |             |

| 4. Ordering Guide                                             |             |

| 5. Package Outline: 36-Pin QFN                                |             |

| 6. Land Pattern: 36-Pin QFN                                   |             |

| 7. Top Marking                                                |             |

| 7.1. Si5322 Top Marking (QFN)                                 |             |

| 7.2. Top Marking Explanation                                  |             |

| Document Change List                                          |             |

| Contact Information                                           |             |

## 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ }^{\circ}\text{C})$

| Parameter         | Symbol          | Test Condition | Min  | Тур | Max  | Unit |

|-------------------|-----------------|----------------|------|-----|------|------|

| Temperature Range | T <sub>A</sub>  |                | -40  | 25  | 85   | °С   |

| Supply Voltage    | V <sub>DD</sub> | 3.3 V nominal  | 2.97 | 3.3 | 3.63 | V    |

|                   |                 | 2.5 V nominal  | 2.25 | 2.5 | 2.75 | V    |

|                   |                 | 1.8 V nominal  | 1.71 | 1.8 | 1.89 | V    |

**Note:** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

### **Table 2. DC Characteristics**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ }^{\circ}\text{C})$

| Parameter                            | Symbol             | Test Condition                                 | Min  | Тур | Max      | Unit            |

|--------------------------------------|--------------------|------------------------------------------------|------|-----|----------|-----------------|

| Supply Current                       | I <sub>DD</sub>    | LVPECL Format                                  | _    | 251 | 279      | mA              |

| (Supply current is indepen-          |                    | 622.08 MHz Out                                 |      |     |          |                 |

| dent of V <sub>DD</sub> )            |                    | All CKOUTs Enabled <sup>1</sup>                |      |     |          |                 |

|                                      |                    | LVPECL Format                                  | _    | 217 | 243      | mA              |

|                                      |                    | 622.08 MHz Out                                 |      |     |          |                 |

|                                      |                    | Only 1 CKOUT Enabled <sup>1</sup>              |      |     |          |                 |

|                                      |                    | CMOS Format                                    | _    | 204 | 234      | mA              |

|                                      |                    | 19.44 MHz Out                                  |      |     |          |                 |

|                                      |                    | All CKOUTs Enabled                             |      |     |          |                 |

|                                      |                    | CMOS Format                                    | _    | 194 | 220      | mA              |

|                                      |                    | 19.44 MHz Out                                  |      |     |          |                 |

|                                      |                    | Only CKOUT1 Enabled                            |      |     |          |                 |

| CKIN Input Pins                      |                    |                                                |      |     |          |                 |

| Input Common Mode                    | V <sub>ICM</sub>   | 1.8 V ±5%                                      | 0.9  | _   | 1.4      | V               |

| Voltage<br>(Input Threshold Voltage) |                    | 2.5 V ±10%                                     | 1.0  | _   | 1.7      | V               |

| (input rineshold voltage)            |                    | 3.3 V ±10%                                     | 1.1  | _   | 1.95     | V               |

| Input Resistance                     | CKN <sub>RIN</sub> | Single-ended                                   | 20   | 40  | 60       | kΩ              |

| Input Voltage Level Limits           | CKN <sub>VIN</sub> | See Note <sup>2</sup>                          | 0    | _   | $V_{DD}$ | V               |

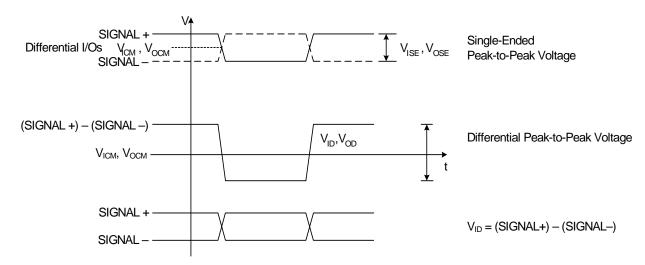

| Single-Ended Input Voltage<br>Swing  | V <sub>ISE</sub>   | f <sub>CKIN</sub> ≤ 212.5 MHz<br>See Figure 2. | 0.2  | _   | _        | V <sub>PP</sub> |

|                                      |                    | f <sub>CKIN</sub> > 212.5 MHz<br>See Figure 2. | 0.25 | _   | _        | V <sub>PP</sub> |

#### Notes:

- 1. LVPECL outputs require nominal  $V_{DD} \ge 2.5 \text{ V}$ .

- 2. No overshoot or undershoot.

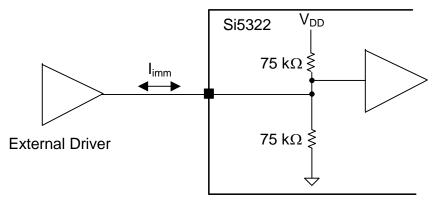

- **3.** This is the amount of leakage that the 3L inputs can tolerate from an external driver. See Figure 3 on page 9. In most designs, an external resistor voltage divider is recommended.

## **Table 2. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                           | Symbol               | Test Condition                                                                                                                  | Min                       | Тур                    | Max                       | Unit             |

|-------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|---------------------------|------------------|

| Differential Input<br>Voltage Swing | V <sub>ID</sub>      | f <sub>CKIN</sub> ≤ 212.5 MHz<br>See Figure 2.                                                                                  | 0.2                       | _                      | _                         | V <sub>PP</sub>  |

|                                     |                      | f <sub>CKIN</sub> > 212.5 MHz<br>See Figure 2.                                                                                  | 0.25                      | _                      | _                         | V <sub>PP</sub>  |

| Output Clocks (CKOUTn) <sup>1</sup> |                      |                                                                                                                                 |                           |                        |                           |                  |

| Common Mode                         | CKO <sub>VCM</sub>   | LVPECL 100 Ω load line-to-line                                                                                                  | V <sub>DD</sub> –<br>1.42 | _                      | V <sub>DD</sub> –<br>1.25 | V                |

| Differential Output Swing           | CKO <sub>VD</sub>    | LVPECL 100 Ω load line-to-line                                                                                                  | 1.1                       | _                      | 1.9                       | V <sub>PP</sub>  |

| Single-ended Output Swing           | CKO <sub>VSE</sub>   | LVPECL 100 Ω load line-to-line                                                                                                  | 0.5                       | _                      | 0.93                      | V <sub>PP</sub>  |

| Differential Output Voltage         | CKO <sub>VD</sub>    | CML 100 Ω load<br>line-to-line                                                                                                  | 350                       | 425                    | 500                       | mV <sub>PP</sub> |

| Common Mode<br>Output Voltage       | CKO <sub>VCM</sub>   | CML 100 Ω load<br>line-to-line                                                                                                  | _                         | V <sub>DD</sub> – 0.36 | _                         | V                |

| Differential<br>Output Voltage      | CKO <sub>VD</sub>    | LVDS 100 Ω load<br>line-to-line                                                                                                 | 500                       | 700                    | 900                       | mV <sub>PP</sub> |

|                                     |                      | Low swing LVDS 100 Ω load line-to-line                                                                                          | 350                       | 425                    | 500                       | mV <sub>PP</sub> |

| Common Mode<br>Output Voltage       | CKO <sub>VCM</sub>   | LVDS 100 Ω load<br>line-to-line                                                                                                 | 1.125                     | 1.2                    | 1.275                     | V                |

| Differential Output<br>Resistance   | CKO <sub>RD</sub>    | CML, LVDS, LVPECL                                                                                                               | _                         | 200                    | _                         | Ω                |

| Output Voltage Low                  | CKO <sub>VOLLH</sub> | CMOS                                                                                                                            | _                         | _                      | 0.4                       | V                |

| Output Voltage High                 | CKO <sub>VOHLH</sub> | V <sub>DD</sub> = 1.71 V<br>CMOS                                                                                                | 0.8 x V <sub>DD</sub>     | _                      | _                         | V                |

| Output Drive Current                | CKO <sub>IO</sub>    | CMOS Driving into CKO <sub>VOL</sub> for output low or CKO <sub>VOH</sub> for output high. CKOUT+ and CKOUT-shorted externally. |                           |                        |                           |                  |

|                                     |                      | V <sub>DD</sub> = 1.8 V                                                                                                         | _                         | 7.5                    | _                         | mA               |

|                                     |                      | V <sub>DD</sub> = 3.3 V                                                                                                         | _                         | 32                     |                           | mA               |

### Notes:

- 1. LVPECL outputs require nominal  $V_{DD} \ge 2.5 \text{ V}$ .

- 2. No overshoot or undershoot.

- **3.** This is the amount of leakage that the 3L inputs can tolerate from an external driver. See Figure 3 on page 9. In most designs, an external resistor voltage divider is recommended.

## **Table 2. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ }^{\circ}\text{C})$

| Parameter                                 | Symbol                        | Test Condition           | Min                    | Тур | Max                    | Unit |  |

|-------------------------------------------|-------------------------------|--------------------------|------------------------|-----|------------------------|------|--|

| 2-Level LVCMOS Input Pins                 |                               |                          |                        |     |                        |      |  |

| Input Voltage Low                         | $V_{IL}$                      | V <sub>DD</sub> = 1.71 V | _                      | _   | 0.5                    | V    |  |

|                                           | -<br>-                        | V <sub>DD</sub> = 2.25 V | _                      |     | 0.7                    | V    |  |

|                                           |                               | V <sub>DD</sub> = 2.97 V | _                      |     | 0.8                    | V    |  |

| Input Voltage High                        | V <sub>IH</sub>               | V <sub>DD</sub> = 1.89 V | 1.4                    | _   | _                      | V    |  |

|                                           |                               | V <sub>DD</sub> = 2.25 V | 1.8                    |     | _                      | V    |  |

|                                           |                               | V <sub>DD</sub> = 3.63 V | 2.5                    |     | _                      | V    |  |

| Input Low Current                         | I <sub>IL</sub>               |                          | _                      |     | 50                     | μA   |  |

| Input High Current                        | I <sub>IH</sub>               |                          | _                      |     | 50                     | μA   |  |

| Weak Internal Input Pull-up<br>Resistor   | R <sub>PUP</sub>              |                          | _                      | 75  | _                      | kΩ   |  |

| Weak Internal Input<br>Pull-down Resistor | R <sub>PDN</sub>              |                          | _                      | 75  | _                      | kΩ   |  |

| 3-Level Input Pins                        |                               |                          |                        |     |                        |      |  |

| Input Voltage Low                         | $V_{ILL}$                     |                          | _                      | _   | 0.15 x V <sub>DD</sub> | V    |  |

| Input Voltage Mid                         | $V_{IMM}$                     |                          | 0.45 x V <sub>DD</sub> |     | 0.55 x V <sub>DD</sub> | V    |  |

| Input Voltage High                        | $V_{IHH}$                     |                          | 0.85 x V <sub>DD</sub> | _   | _                      | V    |  |

| Input Low Current                         | I <sub>ILL</sub> 3            |                          | -20                    | _   | _                      | μΑ   |  |

| Input Mid Current                         | I <sub>IMM</sub> <sup>3</sup> |                          | -2                     | _   | 2                      | μA   |  |

| Input High Current                        | I <sub>IHH</sub> 3            |                          | _                      | _   | 20                     | μA   |  |

| Notes:                                    | J.                            |                          | •                      | 1   |                        |      |  |

#### Notes

- 1. LVPECL outputs require nominal  $V_{DD} \ge 2.5 \text{ V}$ .

- 2. No overshoot or undershoot.

- **3.** This is the amount of leakage that the 3L inputs can tolerate from an external driver. See Figure 3 on page 9. In most designs, an external resistor voltage divider is recommended.

### **Table 2. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ }^{\circ}\text{C})$

| Parameter                | Symbol          | Test Condition                                       | Min                   | Тур | Max | Unit |

|--------------------------|-----------------|------------------------------------------------------|-----------------------|-----|-----|------|

| LVCMOS Output Pins       |                 |                                                      | <u> </u>              |     |     | I.   |

| Output Voltage Low       | V <sub>OL</sub> | I <sub>O</sub> = 2 mA<br>V <sub>DD</sub> = 1.71 V    | _                     | _   | 0.4 | V    |

|                          |                 | $I_{O} = 2 \text{ mA}$<br>$V_{DD} = 2.97 \text{ V}$  | _                     |     | 0.4 | V    |

| Output Voltage High      | V <sub>OH</sub> | $I_{O} = -2 \text{ mA}$<br>$V_{DD} = 1.71 \text{ V}$ | V <sub>DD</sub> – 0.4 | _   | _   | V    |

|                          |                 | $I_{O} = -2 \text{ mA}$<br>$V_{DD} = 2.97 \text{ V}$ | V <sub>DD</sub> – 0.4 |     | _   | V    |

| Disabled Leakage Current | l <sub>OZ</sub> | RST = 0                                              | -100                  | _   | 100 | μA   |

#### Notes:

- **1.** LVPECL outputs require nominal  $V_{DD} \ge 2.5 \text{ V}$ .

- 2. No overshoot or undershoot.

- **3.** This is the amount of leakage that the 3L inputs can tolerate from an external driver. See Figure 3 on page 9. In most designs, an external resistor voltage divider is recommended.

**Figure 1. Voltage Characteristics**

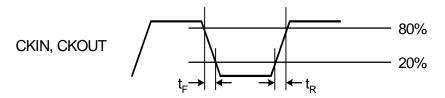

Figure 2. Rise/Fall Time Characteristics

**Table 3. AC Characteristics**

(V<sub>DD</sub> = 1.8 ±5%, 2.5 ±10%, or 3.3 V ±10%,  $T_A$  = -40 to 85 °C)

| Parameter                                                    | Symbol              | Test Condition                                                        | Min         | Тур  | Max    | Units        |

|--------------------------------------------------------------|---------------------|-----------------------------------------------------------------------|-------------|------|--------|--------------|

| CKIN Input Pins                                              | 1 -                 | <u> </u>                                                              |             |      |        |              |

| Input Frequency                                              | CKN <sub>F</sub>    |                                                                       | 19.44       | _    | 707.35 | MHz          |

| Input Duty Cycle                                             |                     | Whichever is smaller                                                  | 40          | _    | 60     | %            |

| (Minimum Pulse Width)                                        | CKN <sub>DC</sub>   | (i.e., the 40%/60% limitation applies only to high clock frequencies) | 2           | _    | _      | ns           |

| Input Capacitance                                            | CKN <sub>CIN</sub>  |                                                                       | _           | _    | 3      | pF           |

| Input Rise/Fall Time                                         | CKN <sub>TRF</sub>  | 20–80%<br>See Figure 2                                                | _           | _    | 11     | ns           |

| CKOUTn Output Pins                                           |                     |                                                                       |             |      |        |              |

| Output Frequency (Output not configured for CMOS or disable) | CK <sub>OF</sub>    |                                                                       | 19.44       |      | 1050   | MHz          |

| Maximum Output Frequency in CMOS Format                      | CKO <sub>FMC</sub>  |                                                                       | _           | _    | 212.5  | MHz          |

| Single-ended Output Rise/Fall<br>(20–80%)                    | CKO <sub>TRF</sub>  | CMOS Output<br>V <sub>DD</sub> = 1.71<br>Cload = 5 pF                 | _           | _    | 8      | ns           |

|                                                              |                     | CMOS Output<br>$V_{DD} = 2.97$<br>Cload = 5 pF                        | _           | _    | 2      | ns           |

| Differential Output Rise/Fall Time                           | CKO <sub>TRF</sub>  | 20 to 80 %, f <sub>OUT</sub> = 622.08                                 | _           | 230  | 350    | ps           |

| Output Duty Cycle Differential<br>Uncertainty                | CKO <sub>DC</sub>   | 100 Ω Load Line to Line Measured at 50% Point (not for CMOS)          | _           | _    | ±40    | ps           |

| LVCMOS Input Pins                                            | 1                   |                                                                       | •           |      | •      |              |

| Minimum Reset Pulse Width                                    | t <sub>RSTMIN</sub> |                                                                       | 1           |      | _      | μs           |

| Input Capacitance                                            | C <sub>IN</sub>     |                                                                       | _           | _    | 3      | pF           |

| LVCMOS Output Pins                                           |                     |                                                                       |             |      |        |              |

| Rise/Fall Times                                              | t <sub>RF</sub>     | C <sub>LOAD</sub> = 20 pf<br>See Figure 2                             | _           | 25   | _      | ns           |

| LOSn Trigger Window                                          | LOS <sub>TRIG</sub> | From last CKIN↑ to LOS↑                                               |             | _    | 750    | μs           |

| PLL Performance                                              |                     |                                                                       |             |      |        |              |

| Output Clock Phase Change                                    | t <sub>P_STEP</sub> | After clock switch f3 ≥ 128 kHz                                       | _           | 200  | _      | ps           |

| Closed Loop Jitter Peaking                                   | J <sub>PK</sub>     | _                                                                     | _           | 0.05 | 0.1    | dB           |

| Jitter Tolerance                                             | J <sub>TOL</sub>    | BW determined by<br>BWSEL[1:0]                                        | 5000/<br>BW | _    | _      | ns pk-<br>pk |

| Spurious Noise                                               | SP <sub>SPUR</sub>  | Max spur @ n x f3<br>(n ≥ 1, n x f3 < 100 MHz)                        | _           | -93  | -70    | dBc          |

| Phase Change due to Temperature<br>Variation                 | t <sub>TEMP</sub>   | Max phase changes from –<br>40 to +85 °C                              | _           | 300  | 500    | ps           |

### 1.1. Three-Level (3L) Input Pins (No External Resistors)

Figure 3. Three-Level Input Pins

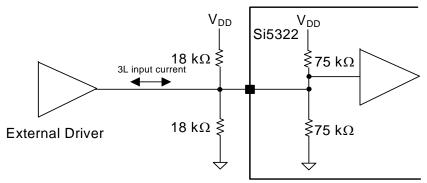

### 1.2. Three-Level Input Pins (Example with External Resistors)

One of eight resistors from a Panasonic EXB-D10C183J (or similar) resistor pack

Figure 4. Three-Level Input Pins

Table 4. Three-Level Input Pins 1,2,3,4

| Parameter          | Min    | Max    |

|--------------------|--------|--------|

| Input Low Current  | –30 μA | _      |

| Input Mid Current  | –11 μA | –11 μA |

| Input High Current | _      | –30 μA |

#### Notes:

- The current parameters are the amount of leakage that the 3L inputs can tolerate from an external driver using the

external resistor values indicated in this example. In most designs, an external resistor voltage divider is

recommended.

- 2. Resistor packs are only needed if the leakage current of the external driver exceeds the current specified in Table 2, limm. Any resistor pack may be used (e.g., Panasonic EXB-D10C183J). PCB layout is not critical.

- 3. If a pin is tied to ground or  $V_{DD}$ , no resistors are needed.

- 4. If a pin is left open (no connect), no resistors are needed.

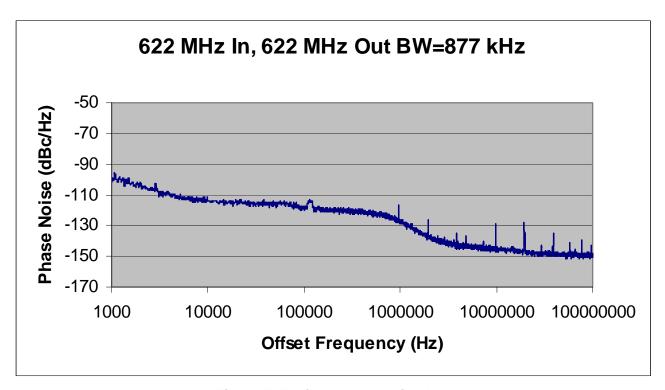

## Table 5. Performance Specifications 1, 2, 3, 4

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \,^{\circ}\text{C})$

| Parameter                                                                | Symbol            | Test Condition | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------------------|-------------------|----------------|-----|------|-----|--------|

| Jitter Generation                                                        | $J_{GEN}$         | 50 kHz-80 MHz  | _   | .47  | _   | ps rms |

| f <sub>IN</sub> = f <sub>OUT</sub> = 622.08 MHz,<br>LVPECL Output Format |                   | 12 kHz–20 MHz  | _   | .48  | _   | ps rms |

| BW = 877 Hz                                                              |                   | 4 MHz-80 MHz   | _   | .23  | _   | ps rms |

| Phase Noise                                                              | CKO <sub>PN</sub> | 1 kHz offset   | _   | -90  | _   | dBc/Hz |

| f <sub>IN</sub> = f <sub>OUT</sub> = 622.08 MHz<br>LVPECL Output Format  |                   | 10 kHz offset  | _   | -113 | _   | dBc/Hz |

|                                                                          |                   | 100 kHz offset | _   | -118 | _   | dBc/Hz |

|                                                                          |                   | 1 MHz offset   | _   | -132 | _   | dBc/Hz |

### Notes:

- 1. BWSEL [1:0] loop bandwidth settings provided in by DSPLLsim.

- **2.**  $V_{DD} = 3.3 \text{ V}$

- **3.**  $T_A = 85 \, ^{\circ}C$

- **4.** Test condition:  $f_{IN}$  = 622.08 MHz,  $f_{OUT}$  = 622.08 MHz, LVPECL clock input: 1.19 Vppd with 0.5 ns rise/fall time (20-80%), LVPECL clock output.

### **Table 6. Thermal Characteristics**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \,^{\circ}\text{C})$

| Parameter                                 | Symbol            | Test Condition | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------|----------------|-----|-----|-----|------|

| Thermal Resistance<br>Junction to Ambient | $\theta_{\sf JA}$ | Still Air      | _   | 32  | _   | °C/W |

| Thermal Resistance<br>Junction to Case    | θЈС               | Still Air      | _   | 14  |     | °C/W |

### **Table 7. Absolute Maximum Ratings**

| Symbol             | Value                                                                | Unit                                                                                                                                                                                             |  |

|--------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>DD</sub>    | -0.5 to 3.8                                                          | V                                                                                                                                                                                                |  |

| V <sub>DIG</sub>   | $-0.3$ to $(V_{DD} + 0.3)$                                           | V                                                                                                                                                                                                |  |

| CKN <sub>VIN</sub> | 0 to V <sub>DD</sub>                                                 | V                                                                                                                                                                                                |  |

| T <sub>JCT</sub>   | -55 to 150                                                           | С                                                                                                                                                                                                |  |

| T <sub>STG</sub>   | -55 to 150                                                           | С                                                                                                                                                                                                |  |

|                    | 2                                                                    | kV                                                                                                                                                                                               |  |

|                    | 150                                                                  | V                                                                                                                                                                                                |  |

|                    | 750                                                                  | V                                                                                                                                                                                                |  |

|                    | 100                                                                  | V                                                                                                                                                                                                |  |

|                    | JESD78 Compliant                                                     |                                                                                                                                                                                                  |  |

|                    | V <sub>DD</sub> V <sub>DIG</sub> CKN <sub>VIN</sub> T <sub>JCT</sub> | VDD       −0.5 to 3.8         VDIG       −0.3 to (VDD + 0.3)         CKNVIN       0 to VDD         TJCT       −55 to 150         TSTG       −55 to 150         2       150         750       100 |  |

**Note:** Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

**Figure 5. Typical Phase Noise Plot**

**Table 8. Typical Jitter Data**

| Jitter Bandwidth            | RMS Jitter (fs) |

|-----------------------------|-----------------|

| OC-48, 12 kHz to 20 MHz     | 374             |

| OC-192, 20 kHz to 80 MHz    | 388             |

| OC-192, 4 MHz to 80 MHz     | 181             |

| OC-192, 50 kHz to 80 MHz    | 377             |

| Broadband, 800 Hz to 80 MHz | 420             |

Notes: 1. Assumes differential LVEPECL termination (3.3 V) on clock inputs.

- 2. Denotes tri-level input pins with states designated as L (ground), M ( $V_{DD}/2$ ), and H ( $V_{DD}$ ).

- 3. Assumes manual input clock selection.

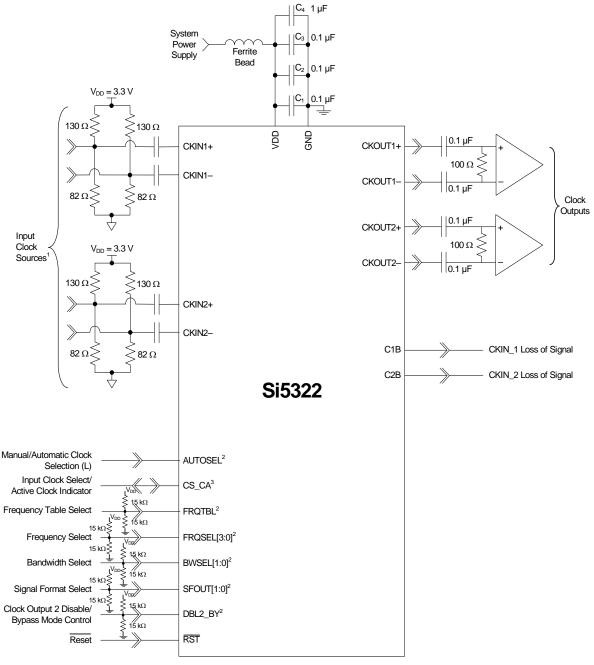

Figure 6. Si5322 Typical Application Circuit

## 2. Functional Description

The Si5322 is a low jitter, precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, SDH STM-16/64 Ethernet, and Fibre Channel. The Si5322 accepts dual clock inputs ranging from 19.44 to 707 MHz and generates two frequencymultiplied clock outputs ranging from 19.44 to 1050 MHz. The two input clocks are at the same frequency and the two output clocks are at the same frequency. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, and Fibre Channel rates. In addition to providing clock multiplication in SONET and datacom applications, the frequency Si5322 supports SONET-to-datacom translations. Silicon Laboratories offers a PC-based software utility, DSPLLsim, that can be used to look up valid Si5322 frequency translations. This utility can be downloaded from http://www.silabs.com/timing (click on Documentation).

The Si5322 is recommended for applications in which the input clock is relatively low jitter and only clock multiplication is required. The Si5322 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-frequency synthesis in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The Si5322 PLL loop bandwidth is selectable via the BWSEL[1:0] pins and supports a range from 150 kHz to 1.5 MHz. The DSPLLsim software utility can be used to calculate valid loop bandwidth settings for a given input clock frequency/clock multiplication ratio. The Si5322 monitors all input clocks for loss of signal and provides a LOS alarm when it detects a missing clock.

In the case when the input clocks enter alarm conditions, the PLL will freeze the DCO output frequency near its last value to maintain operation with an internal state close to the last valid operating state.

The Si5322 has two differential clock outputs. The electrical format of the clock outputs is programmable to support LVPECL, LVDS, CML, or CMOS loads. If not required, the second clock output can be powered down to minimize power consumption. For system-level debugging, a bypass mode is available which drives the output clock directly from the input clock, bypassing the internal DSPLL. The device is powered by a single 1.8, 2.5, or 3.3 V supply.

### 2.1. Further Documentation

Consult the Silicon Laboratories Any-Frequency Precision Clock Family Reference Manual (FRM) for detailed information about the Si5322. Additional design support is available from Silicon Laboratories through your distributor.

Silicon Laboratories has developed a PC-based software utility called DSPLLsim to simplify device configuration, including frequency planning and loop bandwidth selection. The FRM and this utility can be downloaded from <a href="http://www.silabs.com/timing">http://www.silabs.com/timing</a>; click on Documentation.

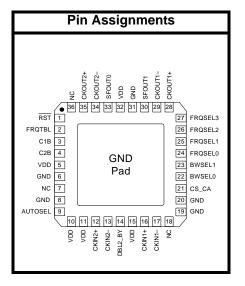

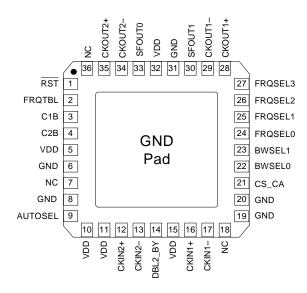

## 3. Pin Descriptions: Si5322

Table 9. Si5322 Pin Descriptions

| Pin # | Pin Name | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                  |

|-------|----------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | RST      | I   | LVCMOS       | External Reset.  Active low input that performs external hardware reset of device. Resets all internal logic to a known state. Clock outputs are tristated during reset. After rising edge of RST signal, the Si5322 will perform an internal self-calibration. This pin has a weak pull-up.                                                 |

| 2     | FRQTBL   | ı   | 3-Level      | Frequency Table Select.  Selects SONET/SDH, datacom, or SONET/SDH to datacom frequency table.  L = SONET/SDH.  M = Datacom.  H = SONET/SDH to Datacom.  The pin has a weak pull-up and weak pull-down and defaults to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state. |

| 3     | C1B      | 0   | LVCMOS       | CKIN1 Loss of Signal.  Active high loss-of-signal indicator for CKIN1. Once triggered, the alarm will remain active until CKIN1 is validated.  0 = CKIN1 present.  1 = LOS on CKIN1.                                                                                                                                                         |

| 4     | C2B      | 0   | LVCMOS       | CKIN2 Loss of Signal.  Active high loss-of-signal indicator for CKIN2. Once triggered, the alarm will remain active until CKIN2 is validated.  0 = CKIN2 present.  1 = LOS on CKIN2.                                                                                                                                                         |

Table 9. Si5322 Pin Descriptions (Continued)

| Pin #                | Pin Name         | I/O             | Signal Level                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 10, 11,<br>15, 32 | V <sub>DD</sub>  | V <sub>DD</sub> | Supply                                                                                                                                                                                                | Supply. The device operates from a 1.8, 2.5, or 3.3 V supply. Bypass capacitors should be associated with the following $V_{DD}$ pins: 5 0.1 $\mu F$ 10 0.1 $\mu F$ 32 0.1 $\mu F$ A 1.0 $\mu F$ should be placed as close to device as is practical.                                                                                                                                                                             |

| 6, 8,19,<br>20, 31   | GND              | GND             | Supply                                                                                                                                                                                                | Ground.  Must be connected to system ground. Minimize the ground path impedance for optimal performance of this device.                                                                                                                                                                                                                                                                                                           |

| 9                    | AUTOSEL          | -               | 3-Level                                                                                                                                                                                               | Manual/Automatic Clock Selection.  Three level input that selects the method of input clock selection to be used.  L = Manual.  M = Automatic non-revertive.  H = Automatic revertive.  The pin has a weak pull-up and weak pull-down and defaults to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                      |

| 12<br>13             | CKIN2+<br>CKIN2- | I               | Clock Input 2.  Differential input clock. This input can also be driven wit single-ended signal. Input frequency selected from a tak of values. The same frequency must be applied to CKIN and CKIN2. |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14                   | DBL2_BY          | -               | 3-Level                                                                                                                                                                                               | Output 2 Disable/Bypass Mode Control.  Controls enable of CKOUT2 divider/output buffer path and PLL bypass mode.  L = CKOUT2 enabled.  M = CKOUT2 disabled.  H = Bypass mode with CKOUT2 enabled.  CMOS outputs do not support Bypass Mode.  The pin has a weak pull-up and weak pull-down and defaults to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state. |

| 16<br>17             | CKIN1+<br>CKIN1- | ı               | Multi                                                                                                                                                                                                 | Clock Input 1.  Differential input clock. This input can also be driven with a single-ended signal. Input frequency selected from a table of values. The same frequency must be applied to CKIN1 and CKIN2.                                                                                                                                                                                                                       |

Table 9. Si5322 Pin Descriptions (Continued)

| Pin #                | Pin Name                                 | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|------------------------------------------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21                   | CS_CA                                    | I/O | LVCMOS       | Input Clock Select/Active Clock Indicator.  Input: If manual clock selection mode is chosen         (AUTOSEL = L), this pin functions as the manual input clock selector. This input is internally deglitched to prevent inadvertent clock switching during changes in the CS input state.  0 = Select CKIN1.  1 = Select CKIN2.  If configured as input, must be set high or low.  Output: If automatic clock selection mode is chosen         (AUTOSEL = M or H), this pin indicates which of the two input clocks is currently the active clock. If alarms exist on both CKIN1 and CKIN2, indicating that the digital hold state has been entered, CA will indicate the last active clock that was used before entering the hold state.  0 = CKIN1 active input clock.  1 = CKIN2 active input clock. |

| 23<br>22             | BWSEL1<br>BWSEL0                         | I   | 3-Level      | Bandwidth Select.  Three level inputs that select the DSPLL closed loop bandwidth. Detailed operations and timing characteristics for these pins may be found in the Any-Frequency Precision Clock Family Reference Manual.  These pins have both weak pull-ups and weak pull-downs and default to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                                                                                                                                                                                                                                                                                                                                                |

| 27<br>26<br>25<br>24 | FRQSEL3<br>FRQSEL2<br>FRQSEL1<br>FRQSEL0 | ı   | 3-Level      | Multiplier Select.  Three level inputs that select the input clock and clock multiplication ratio, depending on the FRQTBL setting. Consult the Any-Frequency Precision Clock Family Reference Manual or DSPLLsim configuration software for settings, both available for download at <a href="https://www.silabs.com/timing">www.silabs.com/timing</a> (click on Documentation).  These pins have both weak pull-ups and weak pull-downs and default to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                                                                                                                                                                                          |

Table 9. Si5322 Pin Descriptions (Continued)

| Pin#      | Pin Name           | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                   |  |

|-----------|--------------------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           |                    |     |              | Signal Format Select.  Three level inputs that select the output signal format (cormon mode voltage and differential swing) for both CKOUT and CKOUT2. Valid settings include LVPECL, LVDS, and CML. Also includes selections for CMOS mode, tristate mode, and tristate/sleep mode.          |  |

|           |                    |     |              | SFOUT[1:0] Signal Format                                                                                                                                                                                                                                                                      |  |

|           |                    |     |              | HH Reserved                                                                                                                                                                                                                                                                                   |  |

|           |                    |     |              | HM LVDS                                                                                                                                                                                                                                                                                       |  |

|           |                    |     |              | HL CML                                                                                                                                                                                                                                                                                        |  |

| 33        | SFOUT0             | ı   | 3-Level      | MH LVPECL                                                                                                                                                                                                                                                                                     |  |

| 30        | SFOUT1             |     |              | MM Reserved                                                                                                                                                                                                                                                                                   |  |

|           |                    |     |              | ML LVDS—Low Swing                                                                                                                                                                                                                                                                             |  |

|           |                    |     |              | LH CMOS                                                                                                                                                                                                                                                                                       |  |

|           |                    |     |              | LM Disabled                                                                                                                                                                                                                                                                                   |  |

|           |                    |     |              | LL Reserved                                                                                                                                                                                                                                                                                   |  |

|           |                    |     |              | CMOS outputs do not support Bypass Mode. These pins have both weak pull-ups and weak pull-downs and default to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                          |  |

| 34<br>35  | CKOUT2-<br>CKOUT2+ | 0   | Multi        | Clock Output 2.  Differential output clock with a frequency selected from a table of values. Output signal format is selected by SFOUT pins. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs. |  |

| 29<br>28  | CKOUT1-<br>CKOUT1+ | 0   | Multi        | Clock Output 1.  Differential output clock with a frequency selected from a table of values. Output signal format is selected by SFOUT pins. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs. |  |

| 7, 18, 36 | NC                 | _   | _            | No Connect. These pins must be left unconnected for normal operation                                                                                                                                                                                                                          |  |

| GND PAD   | GND                | GND | Supply       | Ground Pad.  The ground pad must provide a low thermal and electrical impedance to a ground plane.                                                                                                                                                                                            |  |

# 4. Ordering Guide

| Ordering Part Number                                                             | Package              | ROHS6, Pb-Free | Temperature Range |  |  |

|----------------------------------------------------------------------------------|----------------------|----------------|-------------------|--|--|

| Si5322-C-GM*                                                                     | 36-Lead 6 x 6 mm QFN | Yes            | –40 to 85 °C      |  |  |

| *Note: Not recommended for new designs. For alternatives, see the Si533x family. |                      |                |                   |  |  |

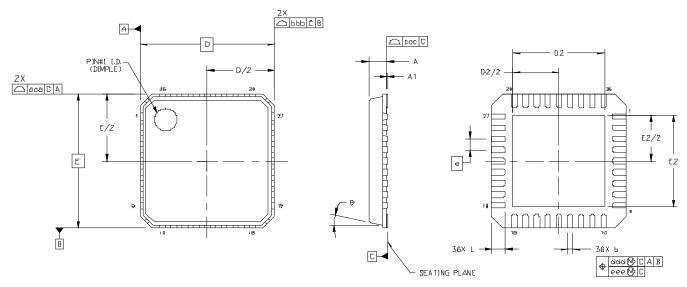

## 5. Package Outline: 36-Pin QFN

Figure 7 illustrates the package details for the Si5322. Table 10 lists the values for the dimensions shown in the illustration.

Figure 7. 36-Pin Quad Flat No-lead (QFN)

**Table 10. Package Dimensions**

| Symbol | Millimeters |      |      |

|--------|-------------|------|------|

|        | Min         | Nom  | Max  |

| Α      | 0.80        | 0.85 | 0.90 |

| A1     | 0.00        | 0.02 | 0.05 |

| b      | 0.18        | 0.25 | 0.30 |

| D      | 6.00 BSC    |      |      |

| D2     | 3.95        | 4.10 | 4.25 |

| е      | 0.50 BSC    |      |      |

| Е      | 6.00 BSC    |      |      |

| E2     | 3.95        | 4.10 | 4.25 |

| Symbol | Millimeter |      | 3    |

|--------|------------|------|------|

|        | Min        | Nom  | Max  |

| L      | 0.50       | 0.60 | 0.70 |

| θ      | _          |      | 12º  |

| aaa    | _          |      | 0.10 |

| bbb    | _          |      | 0.10 |

| CCC    | _          |      | 0.08 |

| ddd    | _          | _    | 0.10 |

| eee    | _          | _    | 0.05 |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-220, variation VJJD.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

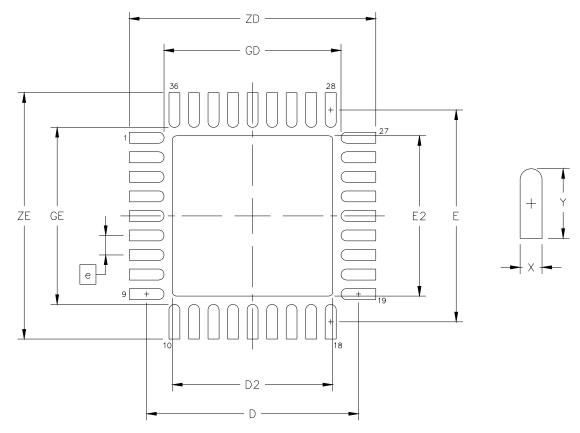

## 6. Land Pattern: 36-Pin QFN

Figure 8. 36-Pin QFN Land Pattern

**Table 11. PCB Land Pattern Dimensions**

| Dimension | MIN       | MAX       |  |  |

|-----------|-----------|-----------|--|--|

| е         | 0.50 BSC. |           |  |  |

| Е         | 5.42      | 5.42 REF. |  |  |

| D         | 5.42      | REF.      |  |  |

| E2        | 4.00      | 4.20      |  |  |

| D2        | 4.00      | 4.20      |  |  |

| GE        | 4.53      | _         |  |  |

| GD        | 4.53      | _         |  |  |

| X         | _         | 0.28      |  |  |

| Y         | 0.89      | REF.      |  |  |

| ZE        | _         | 6.31      |  |  |

| ZD        | _         | 6.31      |  |  |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

### Solder Mask Design

**5.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

### Stencil Design

- A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- **8.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **9.** A 4 x 4 array of 0.80 mm square openings on 1.05 mm pitch should be used for the center ground pad.

### **Card Assembly**

- 10. A No-Clean, Type-3 solder paste is recommended.

- **11.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

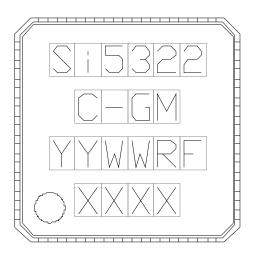

# 7. Top Marking

## 7.1. Si5322 Top Marking (QFN)

## 7.2. Top Marking Explanation

| Mark Method:    | Laser                      |                                                                                                                                                     |

|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Font Size:      | 0.80 mm<br>Right-Justified |                                                                                                                                                     |

| Line 1 Marking: | Si5322                     | Customer Part Number<br>See Ordering Guide for options                                                                                              |

| Line 2 Marking: | C-GM                       | C = Product Revision G = Temperature Range -40 to 85 °C (RoHS6) M = QFN Package                                                                     |

| Line 3 Marking: | YYWWRF                     | YY = Year WW = Work Week R = Die Revision F = Internal code Assigned by the Assembly House. Corresponds to the year and work week of the mold date. |

| Line 4 Marking: | Pin 1 Identifier           | Circle = 0.75 mm Diameter<br>Lower-Left Justified                                                                                                   |

|                 | XXXX                       | Internal Code                                                                                                                                       |

### **DOCUMENT CHANGE LIST**

### Revision 0.44 to Revision 0.45

Condensed format.

### Revision 0.45 to Revision 0.46

- Removed references to latency control, INC, and DEC in figures and text.

- Changed LVTTL to LVCMOS in Table 2, "Absolute Maximum Ratings," on page 5.

- Added Figure 1, "Typical Phase Noise Plot," on page 4

- Updated "3. Pin Descriptions: Si5322".

- Added "6. Land Pattern: 36-Pin QFN".

### Revision 0.46 to Revision 0.47

- Removed Figure 1. "Typical Phase Noise Plot."

- Changed pins 11 and 15 from NC to VDD in "3. Pin Descriptions: Si5322".

### Revision 0.47 to Revision 0.5

- Changed 1.8 V operating range to ±5%.

- Updated Table 1 on page 4.

- Updated Table 2 on page 5.

- Updated Figure 6 on page 12 to add pull-up/pulldown resistors for 3-level inputs.

- Added figure and table on page 11.

- Updated "2. Functional Description" on page 13.

- Clarified "3. Pin Descriptions: Si5322" on page 14.

- Updated SFOUT values.

#### Revision 0.5 to Revision 0.51

- Changed "any-rate" to "any-frequency" throughout.

- Expanded spec tables 1 through 7.

- Updated Table 5 on page 10.

- Added "7. Top Marking" on page 22.

- Added clarification that CMOS output format is not available in PLL bypass mode.

- Updated "4. Ordering Guide" on page 18.

- Removed note from "3. Pin Descriptions: Si5322" on page 14.

## Si5322

## **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories, Silicon Labs, and DSPLL are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.