S19233 Data Sheet

### 10 G Ethernet/Fibre Channel/SONET/SDH Dual CDR

#### **FEATURES**

- Complies with ITU-T specifications, 50 mUI<sub>pp</sub> max. jitter generation (50 KHz - 80 MHz)

- Complies with XFP MSA Specifications

- 25 mUI<sub>pp</sub> Jitter Generation

- CML serial input sensitivity at 5 mV<sub>pp</sub> Diff.

- Dual CDR 9.95 to 11.32 Gbps operation

- · Superior Crosstalk Isolation

- Electronic Dispersion Compensation (EDC)

Optimized for 0 to 100 Km SMF with 2 dB dispersion penalty

- Low power EDC ideal for Power Level 2 XFP modules

- Suitable for low Optical Signal to Noise Ratio (OSNR) environments

- · Automatic Threshold Adjust

- External threshold & Phase Adjust

- AGC embedded equalizer

- LOS Function Compliant to GR-253

- Integrated equalizer that support over 24" FR-4 on Transmitter Electrical Side

- Transmitter (Optical Side) CDR

- Lock detect indication

- 740 mW Typical Power

- -40 to 85°C operation

- CMOS 0.13 Micron Technology

- 1.8 and 3.3 Volt Power Supply

- 6 mm x 6 mm PBGA package with RoHS compliant lead free option

- ESD 1500 V, 1000 V High Speed Inputs

#### **APPLICATIONS**

- 10 G Fibre Channel and Ethernet Designs

- 10 GbE with FEC

- 10 G SONET/SDH/FEC Designs

- SONET/SDH Test Equipment

- SONET/SDH/FEC DWDM Equipment

- XFP MSA Modules

#### GENERAL DESCRIPTION

The S19233 is a fully integrated low power dual CDR device with Electronic Dispersion Compensation (EDC). It is suitable for use in 10 GbE/10G FC/ SONET/SDH PMD modules, such as the XFP MSA modules. This device can be used to compensate channel impairments caused by either single mode fiber up to 100 km or FR-4 copper medium over 24". Integrated in this device on the receive optical side, an AGC amplifier with offset cancellation circuitry, EDC/ Equalization with control circuitry, and CDR. On the transmit electrical side the S19233 also has an equalization circuit, and CDR that reshapes the data after up to 24" of transmission over copper on FR-4 PWB material. The low-jitter CML interfaces guarantees compliance with the bit error rate requirements of the Telcordia and ITU-T standards. The S19233 is packaged in a 6 mm by 6 mm PBGA, offering designers a small package outline.

**Value Proposition** - Design multiple XFP modules ranging from 2 km to 120 km link with one footprint. The S19233 is pin and software compatible to the EDC based 10G Dual CDR S19256.

S19256: 2 km-40 km; S19233: 40 km-120 km

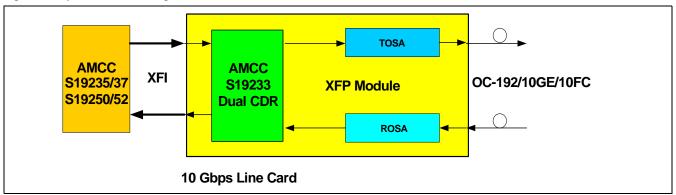

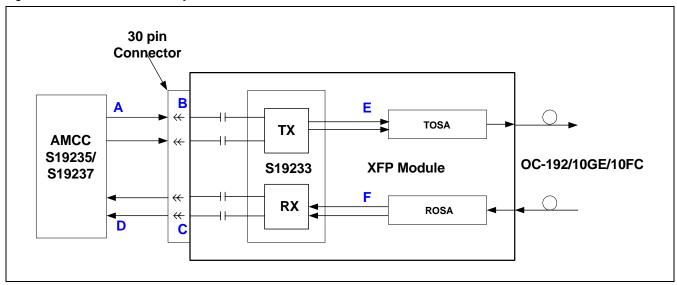

Figure 1. System Block Diagram

### **TABLE OF CONTENTS**

| FEATURES                                                              |    |

|-----------------------------------------------------------------------|----|

| APPLICATIONS                                                          | 1  |

| GENERAL DESCRIPTION                                                   |    |

| TABLE OF CONTENTS                                                     | 2  |

| LIST OF FIGURES                                                       | 4  |

| LIST OF TABLES                                                        | 5  |

| S19233 OVERVIEW                                                       |    |

| POWER UP SEQUENCE                                                     |    |

| RECEIVE OPTICAL SIDE – DESCRIPTION                                    |    |

| Analog Front End                                                      |    |

| Clock Data Recovery                                                   |    |

| Receive Signal Lock Detect                                            |    |

| Receiver Output Polarity Invert                                       |    |

| Receiver Output Squelch                                               |    |

| RECEIVE OPTICAL SIDE - CONTROL DESCRIPTION                            |    |

| Receive Serial Data In (RXDATINP/N) – External Pin                    |    |

| RXDATIP/N Internal Center-Tapped Termination (RXCTAP) – External Pin  |    |

| Receive Loop Filter (RXCAP1, RXCAP2) – External Pin                   |    |

| Receive Lock (RXLOCK) – External Pin                                  | 9  |

| Receive Loss of Signal/Signal Detect (LOS_SD) – External Shared Pin   | 9  |

| Receive Lock-to-Reference (LCKREFRXB) – I2C Register                  | 10 |

| Receive Signal Detect Polarity (SDPOL) – I <sup>2</sup> C Register    |    |

| Receive Squelch Serial Output (RX_SQ_EN) – I <sup>2</sup> C Register  | 10 |

| TRANSMIT ELECTRICAL SIDE – DESCRIPTION                                |    |

| Programmable Equalization                                             | 10 |

| Signal Conditioning Operation                                         |    |

| Clock Data Recovery – Transmit                                        |    |

| Transmit Output Polarity Invert                                       |    |

| Transmit Output Squelch                                               |    |

| TRANSMIT ELECTRICAL SIDE – CONTROL DESCRIPTION                        |    |

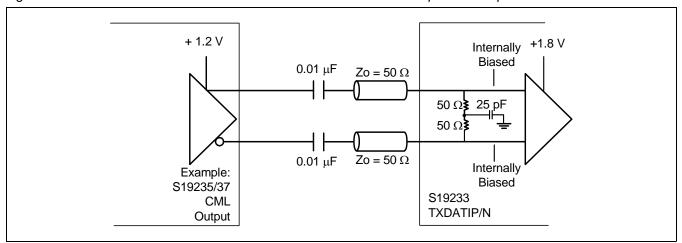

| Transmit Serial Data In (TXDATIP/N) – External Pin                    |    |

| Transmit Loop Filter (TXCAP1, TXCAP2) – External Pin                  |    |

| Transmit Lock (TXLOCk) – External Pin                                 |    |

| Transmit Lock-to-Reference (LCKREFTXB) – I <sup>2</sup> C Register    |    |

| Transmit Squelch Serial Output (TX_SQ_EN) – I <sup>2</sup> C Register |    |

| Reference Clock (REFCLKP/N) – External PinPD – External Pin           |    |

| Electrical Diagnostic Loopback Enable (XLEB) –                        | 12 |

| I <sup>2</sup> C Register                                             | 12 |

| Optical Side Line Loopback Enable (OLEB) – I <sup>2</sup> C Register  |    |

| I2C BUS® and Address Register                                         |    |

| SONET AND ETHERNET JITTER CRITERIA                                    |    |

| SONET Jitter Transfer                                                 |    |

| SONET Jitter Tolerance                                                |    |

|                                                                       |    |

## Data Sheet

| SONET Jitter Generation                           | 15 |

|---------------------------------------------------|----|

| Sinusoidal Jitter                                 | 15 |

| Test Pattern                                      | 15 |

| PIN ASSIGNMENTS AND DESCRIPTIONS                  | 18 |

| I2C SERIAL CONTROL INTERFACE REGISTER MAP SUMMARY | 20 |

| S19233 PINOUT (TOP VIEW)                          | 23 |

| S19233 – 49 PBGA PACKAGE MECHANICAL DRAWING       | 24 |

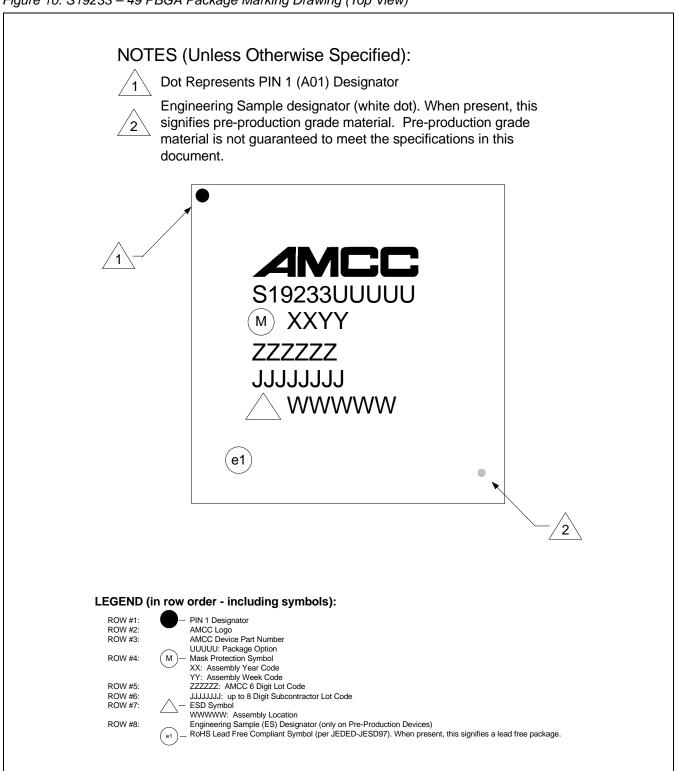

| S19233 – 49 PBGA PACKAGE MARKING DRAWING          | 25 |

| PERFORMANCE SPECIFICATIONS                        | 26 |

| RECOMMENDED TERMINATIONS                          | 35 |

| DOCUMENT REVISION HISTORY                         | 37 |

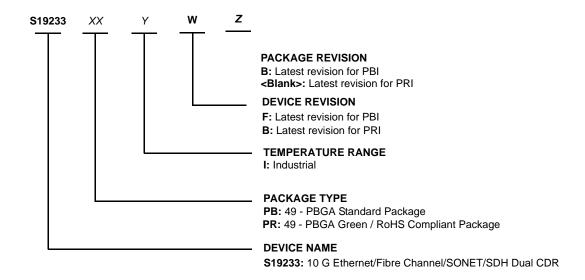

| ORDERING INFORMATION                              | 39 |

## Data Sheet

#### **LIST OF FIGURES**

| Figure 1. System Block Diagram                                                                             | 1  |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 2. S19233 Dual CDR Block Diagram                                                                    |    |

| Figure 3. Two Wire Slave Address                                                                           | 13 |

| Figure 4. SONET STS-192 Jitter Tolerance Mask                                                              | 14 |

| Figure 5. Input Jitter for Receiver Test                                                                   | 16 |

| Figure 6. Applied Sinusoidal Jitter - 10GbE                                                                | 16 |

| Figure 7. Scrambler and Descrambler                                                                        | 17 |

| Figure 8. S19233 Pinout (Top View)                                                                         | 23 |

| Figure 9. S19233 – 49 PBGA Package Mechanical Drawing                                                      | 24 |

| Figure 10. S19233 – 49 PBGA Package Marking Drawing (Top View)                                             | 25 |

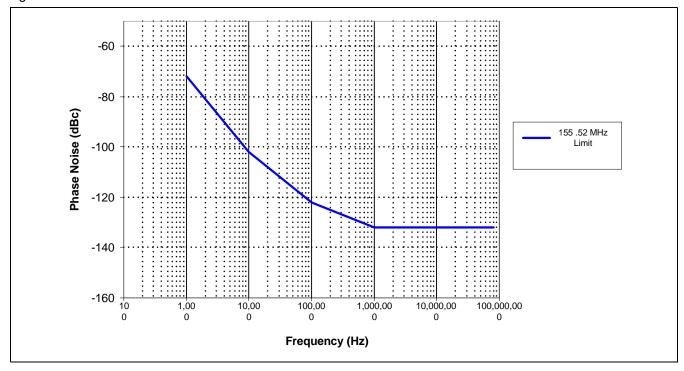

| Figure 11. 155.52 MHz REFCLK Phase Noise                                                                   | 30 |

| Figure 12. S19233 with XFP System Performance Points                                                       | 30 |

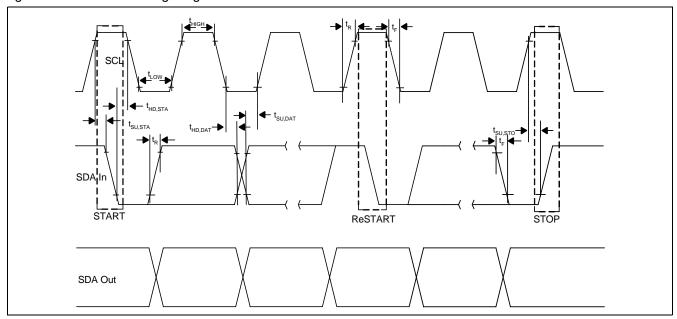

| Figure 13. I <sup>2</sup> C BUS <sup>®</sup> Timing Diagram                                                | 33 |

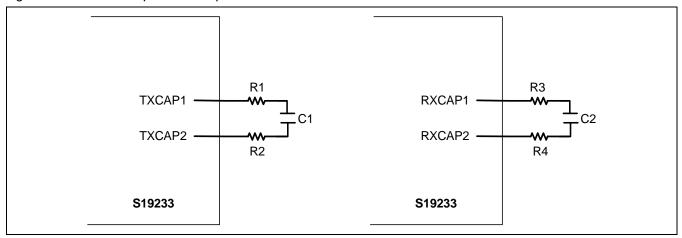

| Figure 14. External Loop Filter Components                                                                 | 34 |

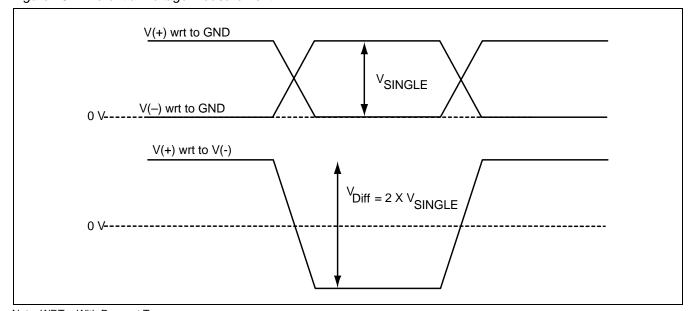

| Figure 15. Differential Voltage Measurement                                                                | 34 |

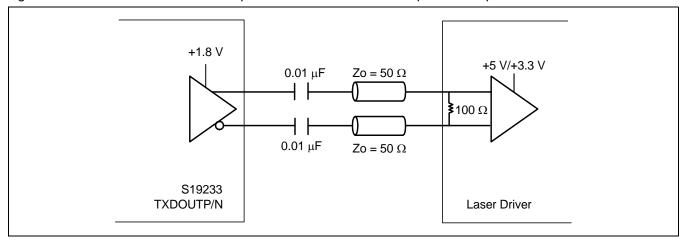

| Figure 16. S19233 Differential CML Output to +5 V/+3.3 V LVPECL Input AC Coupled Termination               | 35 |

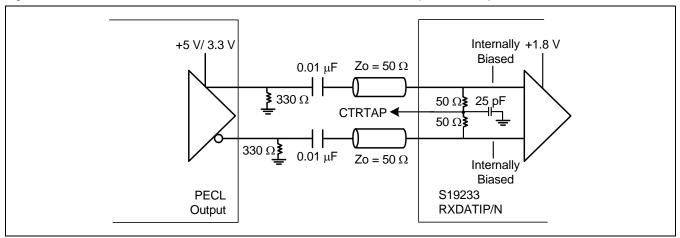

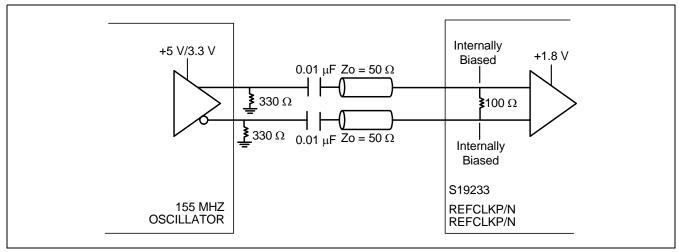

| Figure 17. +5 V Differential PECL Driver to S19233 Differential CML Input AC Coupled Termination           | 35 |

| Figure 18. +5 V/+3.3 V Differential PECL Driver to S19233 CML Reference Clock Input AC Coupled Termination | 35 |

| Figure 10 + 1.2 V Differential CML Driver to \$10222 Differential CML Input AC Coupled Termination         | 26 |

## Data Sheet

### **LIST OF TABLES**

| Table 1. Standard Compliance List                              | 6  |

|----------------------------------------------------------------|----|

| Table 2. AMCC Suggested Interface Devices                      | 6  |

| Table 3. Receive Squelch Control                               | 9  |

| Table 4. Transmit Squelch Control                              | 11 |

| Table 5. Reference Frequency for the Clock Recovery Unit       | 12 |

| Table 7. Pattern Segments                                      | 17 |

| Table 8. Test Patterns                                         | 17 |

| Table 6. Applied Sinusoidal Jitter                             | 17 |

| Table 9. Signals Pin Assignments and Descriptions              |    |

| Table 10. Common Pin Assignments and Descriptions              |    |

| Table 11. Register Map Summary                                 | 20 |

| Table 12. Thermal Management                                   | 24 |

| Table 13. Performance Specifications                           | 26 |

| Table 14. Absolute Maximum Stress Ratings                      | 31 |

| Table 15. Recommended Operating Conditions                     | 31 |

| Table 16. Serial I/O Interface Specifications                  |    |

| Table 17. LVTTL Input/Output Characteristics                   |    |

| Table 18. I2C Input/Output Characteristics                     | 33 |

| Table 19. Transmit and Receive External Loop Filter Components | 34 |

#### **S19233 OVERVIEW**

The S19233 can be used to implement the front end of SONET/SDH/FEC/10GbE/FC/G.709 equipment which consists primarily of the serial transmit interface and the serial receive interface. The system timing circuitry consists of a high-speed phase detector, clock and data recovery unit and equalization circuitry. The device utilizes on-chip clock recovery PLL components that allow the use of a slower external clock reference, 155.52 MHz (or equivalent FEC/10GbE/10 Gbps FC rate), in support of existing system clocking schemes.

The EDC function is embedded in the optical receive side. It provides control to compensate chromatic dispersion in different fiber links. On the transmitter side, an equalizer is integrated in the receive front end to reshape the data after transmission over FR-4. This enables low bit error rate and transmission over longer trace length.

The low-jitter, 1-bit, CML interfaces guarantee compliance with the bit-error rate requirements of the Telcordia and ITU-T standards. The 10 Gbps serial electrical interface specifications are compliant with the XFI as specified in the XFP MSA module specification. The high speed serial input and output can be connected to the AMCC SerDes (S19235 or S19237) across 600 mm (24") of improved FR-4 material or across 400 mm of standard FR-4 with one connector.

Table 2 shows the suggested interface device(s) for the S19233.

Table 1. Standard Compliance List

| Standard                                                                                 | Revision | Date      |

|------------------------------------------------------------------------------------------|----------|-----------|

| XFP - 10 Gigabit Small Form Factor<br>Pluggable Module                                   | 4.0      | 4/13/04   |

| T1.105.03 - 2002 SONET Jitter Tolerance specification                                    | 1        | 08/2002   |

| GR-253-CORE                                                                              | 3.0      | 09/2000   |

| GR-253-ILR- Sonet Jitter Specifications                                                  | Issue 3A | 10/2000   |

| G.825 SDH Jitter Tolerance specification                                                 | -        | 03/2000   |

| G.783 Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks | -        | 02/2004   |

| IEEE 802.3ae                                                                             | -        | 8/30/2002 |

| X3.T11 FC-PH-3 10 G                                                                      | Rev 0    | 5/2003    |

| ESD - JEDEC standard: JESD22-A114-B                                                      | Rev B    | 6/2000    |

Note: Standards compliance only relates to applicable sections pertaining to this product type.

#### **Transmitter Side Operations**

- 1. 1-bit serial data input

- 2. Equalization to compensate for FR-4

- 3. Threshold and Offset cancellation adjust

- 4. Clock and Data recovery

- 5. Data retime

- 6. Serial data output

#### **Receiver Side Operations**

- 1. Serial input with AGC (Equalization)

- 10 mV<sub>pp</sub> Differential Sensitivity with threshold adjust

- 3. Loss of signal detection

- 4. Clock and Data recovery

- 5. Serial data output

#### **Common Operations**

- 1. Optical and Electrical Loopbacks

- 2. Power Down CDR

Table 2. AMCC Suggested Interface Devices

| AMCC | S19235 | SFI4 Phase 1<br>SONET/SDH STS-192/10 Gig Ether-<br>net CMOS Transceiver with ISI Com-<br>pensation |

|------|--------|----------------------------------------------------------------------------------------------------|

| AMCC | S19237 | SFI4 Phase 1<br>SONET/SDH STS-192/10 Gig Ethernet CMOS Transceiver with ISI Compensation           |

#### **POWER UP SEQUENCE**

This Power Up Sequence provides details for the required reset sequence to initialize the S19233 following power on or system reset.

- 3. Apply the reference clock to pin REFCLKP/N

- 4. Set pin **PD** high for at least two clock cycles then set low to initiate initialization and for normal operation.

The initialization will complete in 13 clock cycles following the falling edge of the *PD* signal. The *PD* signal must remain low for normal operation.

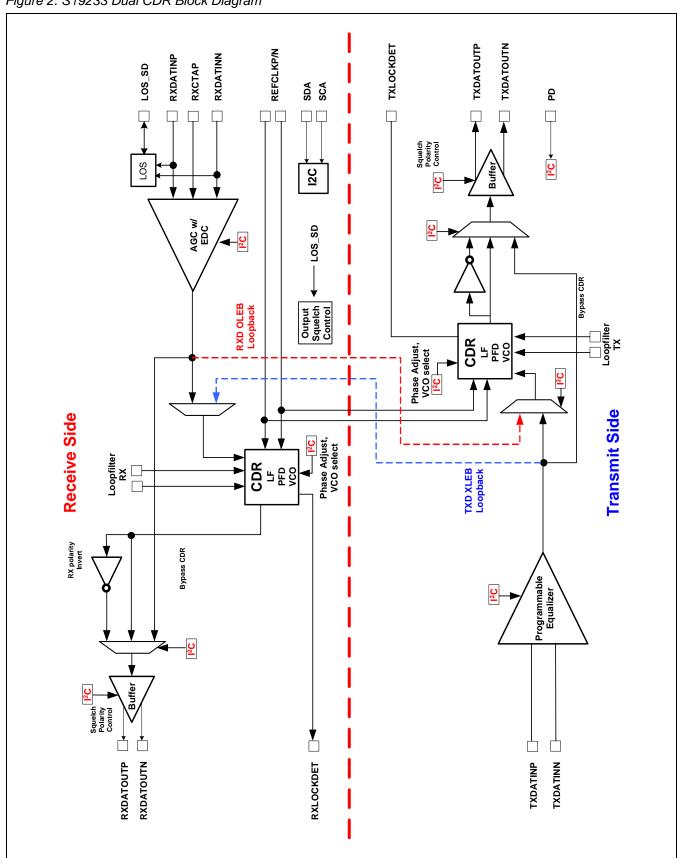

Figure 2. S19233 Dual CDR Block Diagram

#### **RECEIVE OPTICAL SIDE - DESCRIPTION**

The receive side of the S19233 dual CDR device provides an important EDC function to compensate chromatic dispersion for 10 Gigabit Ethernet/10 G Fibre Channel/SONET STS-192 transmitted over single mode fiber. It reshapes the received signal waveform and amplifies the signal to an optimal signal level so that the receive side CDR can achieve optimum performance.

#### **Analog Front End**

An AGC gain stage with offset adjust capability is at the first input stage. The S19233 AGC stage takes the differential serial data from the RXDATINP/N pins. There is a center-tap pin, RXCTAP, that provides a flexible solution for a single-ended input configuration. The input to this stage must be AC coupled.

#### **Clock Data Recovery**

Clock Data recovery (CDR), as shown in the block diagram in Figure 2, S19233 Dual CDR Block Diagram, recovers a clock that is the same frequency as the incoming data bit rate at the serial data input. The clock is phase aligned by a Phase Lock Loop (PLL) so that it samples the data in the center of the data eye pattern.

The Clock Data Recovery Unit (CDR) extracts a synchronous signal from the serial data input using a PLL. The PLL consists of a Voltage Controlled Oscillator (VCO), Phase/Frequency Detectors (PFD), and a loop filter.

The frequency detector ensures predictable lock-up conditions. It is used during acquisition and serves as a means to pull the VCO into the range of the data rate where the phase detector is capable of acquiring lock.

The phase detector used in the CDR is designed to give minimum static phase error of the PLL. When a transition has occurred, the value of the sample in the vicinity of the transition indicates whether the VCO clock leads or lags the incoming data, and the phase detector produces a binary output accordingly.

When a loss of signal condition exists, the PLL locks onto the reference clock (REFCLKP/N) to provide a steady output clock. The output data is invalid and can be squelched.

The phase relationship between the edge transitions of the data and those of the generated clock are compared by a phase/frequency discriminator. Output pulses from the discriminator indicate the required direction of phase corrections. These pulses are smoothed by an integral loop filter (LF). The output of the loop filter controls the frequency of the Voltage Controlled Oscillator (VCO), which generates the recovered clock.

Frequency stability without incoming data is guaranteed by the reference input (REFCLKP/N) onto which the PLL locks when data is lost. If the frequency of the incoming signal varies by a value greater than that stated in Table 13, with respect to REFCLKP/N, the PLL will be declared out of lock, and the PLL will lock to the reference clock.

The loop filter transfer function is optimized in order to enable the PLL to track the jitter yet tolerate the minimum transition density expected in a received 10 Gigabit Ethernet, 10 G Fiber Channel and SONET data signal. There are two pins (RXCAP1 and RXCAP2) to connect the external capacitor and resistors in order to adjust the PLL loop performance.

The total loop dynamics of the clock recovery PLL yield a jitter tolerance which exceeds the minimum tolerance proposed for SONET equipment by the Telcordia standard.

#### **Receive Signal Lock Detect**

The S19233 contains a lock detect circuit that monitors the integrity of the serial data inputs. If the received serial data fails the frequency test as describe previously, the PLL will be forced to lock to the local reference clock. This will maintain the correct frequency of the recovered clock output under loss-ofsignal or loss-of-lock conditions. If the recovered clock frequency deviates from the local reference clock frequency by more than the typical value stated in Table 13, Performance Specifications, the PLL will be declared out of lock. The lock detect circuit will poll the input data stream in an attempt to reacquire lock to data. If the recovered clock frequency is determined to be within the typical value stated in Table 13, Performance Specifications, the PLL will be declared in lock and the lock detect output will go active. An inactive Signal Detect (SD) setting will also cause an out-oflock condition.

### **Receiver Output Polarity Invert**

The output data polarity swap is implemented for the ease of design. This adds routing flexibility for either top or bottom PCB placement of IC or optics compatibility.

When the RX\_POLINV is set high through the I<sup>2</sup>C interface, the polarity of the receiver output is inverted.

#### **Receiver Output Squelch**

The output data squelch functions are controlled through the I2C BUS® interface. RX\_SQ\_POL determines the polarity of the receive squelch data and RX\_SQ\_EN is the control bit used to enable or disable the squelch feature. The RX\_SQ\_CNTL bit is a receiver squelch control bit. See Table 3 for details.

Table 3. Receive Squelch Control

T

| RX_SQ<br>_EN | RX_SQ<br>_CNTL | RX_SQ[1:0] | Function                                                                                                                                                        |

|--------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | 0              | XX         | Squelch RX data                                                                                                                                                 |

| 1            | 1              | 00         | LOS_SD (LOS) output controls the squelch                                                                                                                        |

| 1            | 1              | 01         | RXLOCK signal controls the squelch. The LOS condition will also trigger RXLOCK.                                                                                 |

| 1            | 1              | 10         | LOS_SD (SD) input control the squelch                                                                                                                           |

| 1            | 1              | 11         | (1) RX squelch function is controlled by LOS or RXLOCK (Default: LOS_SDC is active high) (2) RX squelch function is controlled by SD or RXLOCK if LOS_SD is low |

| 0            | Х              | XX         | Disable squelch fea-<br>ture for RX                                                                                                                             |

# RECEIVE OPTICAL SIDE – CONTROL DESCRIPTION

## Receive Serial Data In (RXDATINP/N) – External Pin

The Receive Data In (RXDATIP/N) pins are differential Current Mode Logic (CML) inputs. They receive inputs from an optics module or other upstream logic device. The RXDATIP/N is internally terminated with two 50  $\Omega$  resistors in series. The two 50  $\Omega$  resistors are centertapped with a 25 pF capacitor for use in single-ended applications.

The RXDATIP/N inputs must be AC coupled. These pins are internally biased and terminated 100  $\Omega$  line-to-line.

## RXDATIP/N Internal Center-Tapped Termination (RXCTAP) – External Pin

The RXDATIP/N is internally terminated with two 50  $\Omega$  resistors in series. The two 50  $\Omega$  resistors are centertapped with a 25 pF capacitor. The input to the capacitor can be directly accessed through the RXCTAP pin. This input should be connected to a broadband 850 pF capacitor to ground when used in single-ended applications. This termination scheme enables the S19233 to be driven in the single-ended mode and offers better common-mode noise rejection. This input should be left floating if RXDATIP/N is driven differentially.

## Receive Loop Filter (RXCAP1, RXCAP2) – External Pin

The CDR external loop filter capacitor and resistors are connected to the RXCAP1 and RXCAP2 pins. These devices should be surrounded by a ground shield. Component values should be as stated in Table 19, Transmit and Receive External Loop Filter Components.

#### Receive Lock (RXLOCK) - External Pin

RXLOCK goes active after the receive PLL has locked on the incoming data stream after initially locking onto the clock provided on the REFCLK pins. RXLOCK is an asynchronous output. The Receive Lock status is also available as *RXLOCK* register read only bit.

## Receive Loss of Signal/Signal Detect (LOS\_SD) – External Shared Pin

This is a dual purpose pin. This pin is configured as a Loss of Signal (LOS) pin or can be changed to a Signal Detect (SD) pin through the I<sup>2</sup>C interface using the LOS\_SD bit. The LOS can be programmed active high or active low by setting RX\_LOS\_POL bit to 1 or 0 respectively. The LOS threshold and hysteresis are adjustable via the I<sup>2</sup>C control registers. Upon receiving

an LOS condition the PLL will lock to reference until the LOS condition is de-asserted. LOS pin is not configured as an open drain or open collector output.

The signal detect is an active high or active low LVTTL single-ended input to be driven by the external optical receiver module to indicate the presence of received optical power. Active level (high or low) is programmed by the *SDPOL*. When a loss-of-light condition occurs, an active SD will cause the internal PLL to be locked to the REFCLK input signal.

# Receive Lock-to-Reference (*LCKREFRXB*) – I<sup>2</sup>C Register

Active low. Lock-to-Reference (*LCKREFRXB*) input register will force the PLL to lock to the local Reference Clock (REFCLK) when active. This bit should be set to inactive which is default, for normal operation. This input is only accessible through the I<sup>2</sup>C bus register.

## Receive Signal Detect Polarity (SDPOL) – I<sup>2</sup>C Register

The signal detect polarity is an input bit that will set the LOS\_SD input as either active high or active low when the LOS\_SD bit is set inactive. Setting this pin low will set the LOS\_SD input as active low. Setting this bit high will set the LOS\_SD input as active high. This input is only accessible through the I<sup>2</sup>C bus register.

## Receive Squelch Serial Output (RX\_SQ\_EN) – I<sup>2</sup>C Register

The Squelch Serial Output data enable (RX\_SQ\_EN), when asserted high, will enable the squelch function in the receiver.

# TRANSMIT ELECTRICAL SIDE – DESCRIPTION

#### **Programmable Equalization**

The transmit front end have programmable equalization to compensate for 24 inches FR-4 applications. Equalization is necessary to compensate for bandwidth attenuation/distortions caused by the PWB.

#### **Signal Conditioning Operation**

On the Transmit side, the S19233 performs the signal conditioning stage in the processing of a transmit 10 Gigabit Ethernet/10 G Fibre Channel/SONET STS-192/ data stream. The rate will depend upon the REF-CLK frequency used. A high-frequency bit clock is generated from a 155 MHz (or equivalent FEC/10 Gigabit Ethernet rate) frequency reference by using a clock synthesizer consisting of an on-chip phase-lock loop circuit with a divider, VCO and loop filter.

#### **Clock Data Recovery – Transmit**

The CDR shown in the block diagram in Figure 2, is a monolithic PLL that generates the serial output clock frequency locked to the input Reference Clock (REF-CLKP/N) used by the receive side.

The REFCLKP/N input must be generated from a crystal oscillator which has a frequency accuracy that meets the value stated in Table 13 in order for the Transmit Serial Data (TXDATOUTP/N) frequency to have the accuracy required for operation in a SONET/10 Gigabit Ethernet system. The REFCLK must also meet the phase noise requirements shown in Figure 5 in order to meet the jitter generation specifications as defined in GR-253-Core, Issue 3, September 2000. Lower accuracy crystal oscillators may be used in applications less demanding than the SONET/SDH.

The on-chip PLL consists of; a phase detector, which compares the phase relationship between the VCO output and the REFCLK input, a loop filter, which converts the phase detector output into a smooth DC voltage, and a VCO, whose frequency is varied by this voltage.

The loop filter generates a VCO control voltage based on the average DC level of the phase discriminator output pulses. A single external clean-up capacitor is utilized as part of the loop filter. The loop filter's corner frequency is optimized to minimize output phase jitter.

#### **Transmit Output Polarity Invert**

The output data polarity swap is implemented for the ease of design. This adds routing flexibility for either top or bottom PCB placement of IC or optics compatibility.

When the TX\_POLINV is set high through the I<sup>2</sup>C interface, the polarity of the transmitter output is inverted.

#### **Transmit Output Squelch**

The output data squelch functions are controlled through the I<sup>2</sup>C interface. TX\_SQ\_POL determines the polarity of the receive squelch data and TX\_SQ\_EN is the control bit used to enable or disable the squelch feature. The TX\_SQ\_CNTL bit is a transmit squelch control bit. See Table 4 for details.

Table 4. Transmit Squelch Control

| TX_SQ_<br>EN | TX_SQ_CNTL | Function                                          |

|--------------|------------|---------------------------------------------------|

| 0            | X          | Disable Squelch                                   |

| 1            | 0          | Squelch TX data                                   |

| 1            | 1          | Default mode. TXLOCK signal controls the squelch. |

# TRANSMIT ELECTRICAL SIDE – CONTROL DESCRIPTION

#### Transmit Serial Data In (TXDATIP/N) - External Pin

The Transmit Data In (TXDATIP/N) pins are differential Current Mode Logic (CML) inputs. They receive inputs via a PWB trace which can be up to 10 inches in length. The TXDATIP/N is internally terminated with two 50  $\Omega$  resistors in series. The two 50  $\Omega$  resistors are center-tapped with a 850 pF capacitor for use in single-ended applications.

The TXDATIP/N inputs must be AC coupled. These pins are internally biased and terminated 100  $\Omega$  line-to-line.

## Transmit Loop Filter (TXCAP1, TXCAP2) – External Pin

The CDR external loop filter capacitor and resistors are connected to the TXCAP1 and TXCAP2 pins. These devices should be surrounded by a ground shield. Component values should be as stated in Table 19, Transmit and Receive External Loop Filter Components.

#### Transmit Lock (TXLOCk) - External Pin

TXLOCK goes active after the transmit PLL has locked on the incoming data stream after initially locking onto the clock provided on the REFCLK pins. TXLOCK is an asynchronous output. The Transmit Lock status is also available as *TXLOCK* read only register bit.

# Transmit Lock-to-Reference (*LCKREFTXB*) – I<sup>2</sup>C Register

Active low. Lock-to-Reference (*LCKREFTXB*) will force the PLL to lock to the local Reference Clock (REFCLK) when active. This bit should be set to inactive which is default, for normal operation. This input is only accessible through the I<sup>2</sup>C bus register.

# Transmit Squelch Serial Output (TX\_SQ\_EN) – I<sup>2</sup>C Register

Squelch Serial Output data enable (TX\_SQ\_EN), when asserted high, will enable the squelch function in the transmitter.

#### Reference Clock (REFCLKP/N) - External Pin

The Reference Clock (REFCLKP/N) pins are Differential CML 155.52 MHz to 177 MHz input used to establish the initial operating frequency of the clock recovery Phase Lock Loop (PLL) and is also used in the absence of data to maintain PLL lock. Table 5 summarizes the REFCLK rates used in typical applica-

tions. This input is internally biased and terminated 100  $\Omega$  line-to-line and must be AC coupled. Additionally, Table 5. shows the corresponding RX and TX register configured VCO selections for the frequency of operation. See *S19233 Programming Manual* for additional information on RX and TX VCO selection.

Table 5. Reference Frequency for the Clock Recovery Unit

| Error Correcting<br>Capability                   | Percentage Bandwidth<br>Expansion Due to Code<br>Words and Frame<br>Synchronization Byte (FSB) | Increased Receive<br>Data Input<br>(SERDATI)<br>Frequency | Required<br>(REFCLK)<br>Frequency | RX_VCO_SEL[1:0]/<br>TX_VCO_SEL[1:0] |

|--------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------|-------------------------------------|

| STS-192, 0 bytes                                 | 0% increase                                                                                    | 9.953 Gbps                                                | 155.52 MHz                        | 01                                  |

| STS-192, Reed Soloman<br>- 255/238               | 7.14% increase                                                                                 | 10.66 Gbps                                                | 166.63 MHz                        | 10                                  |

| STS-192, Reed Soloman<br>- 255/237               | 7.59% increase                                                                                 | 10.709 Gbps                                               | 167.33 MHz                        | 10                                  |

| 10 Gigabit Ethernet                              | 0% increase                                                                                    | 10.000 Gbps                                               | 156.25 MHz                        | 01                                  |

| 10 Gigabit Ethernet 64/<br>66B Encoded           | 3.125% increase                                                                                | 10.3125 Gbps                                              | 161.13 MHz                        | 01                                  |

| 10 Gigabit Ethernet 64/<br>66B Encoded - 255/238 | 7.14% increase                                                                                 | 11.0491 Gbps                                              | 172.642 MHz                       | 11                                  |

| 10 Gigabit Ethernet 64/<br>66B Encoded - 255/237 | 7.59% increase                                                                                 | 11.0957 Gbps                                              | 173.37 MHz                        | 11                                  |

| 10 G Fibre Channel                               | 0% increase                                                                                    | 10.51875 Gbps                                             | 164.35 MHz                        | 10                                  |

| 10 G Fibre Channel,<br>Reed Soloman - 255/238    | 7.14% increase                                                                                 | 11.27 Gbps                                                | 176.095 MHz                       | 11                                  |

| 10 G Fibre Channel,<br>Reed Soloman - 255/237    | 7.59% increase                                                                                 | 11.32 Gbps                                                | 176.84 MHz                        | 11                                  |

#### PD - External Pin

Powerdown/Reset pin. This is a dual purpose pin. Active high. Default low, when high, power downs the Transmitter and Receiver. The I2C interface and reset generation logic is functional during power-down with REFCLK supplied. The falling edge initiates a complete reset of TX/RX including 2-wire serial interface. The reset function asynchronously resets the device.

# Electrical Diagnostic Loopback Enable (XLEB) – I<sup>2</sup>C Register

The XLEB is an active low input that selects the diagnostic loopback mode. In this mode, the Transmitter Data (TXD) is routed internally to the receive side. The

serial data is recovered by the receive CDR then send back out the electrical side through pin RXDATOUTP/N. This mode is accessible through the I<sup>2</sup>C bus register.

## Optical Side Line Loopback Enable (OLEB) – I<sup>2</sup>C Register

This active low input selects line loopback mode. In this mode, the Receiver Data (RXD) from the receive side is routed internally to the transmit side. The serial data is recovered by the transmit CDR then send back out the optical side through pin TXDATOUTP/N. This mode is accessible through the I2C BUS® register.

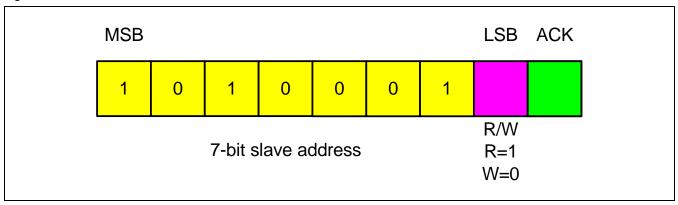

#### I2C BUS® and Address Register

S19233 uses a simple bi-directional two-wire bus for efficient inter-IC control. All register controlled features and functions are programmed via the I<sup>2</sup>C. Table 11summarizes the register map and description necessary for proper operation. A more detailed description can found in the S19233 Programmer's Reference Manual, PRM2001.

The following are some important features of I<sup>2</sup>C bus:

- The S19233 has a unique address on the bus and a slave configuration at all times.

- Only two bus lines are required; a serial Data Input/Output line (SDA) and a Clock line (SCL).

The serial port interface is based on the I<sup>2</sup>C. Communication occurs across two wires and is formatted in frames. The two wires are clock (SCL) and data (SDA). At the rising edge of RSTB, the S19233 loads the device address into a register from the DEVICE ADDR[6:0] and uses it to decode accesses

to its registers. The DEVICE\_ADDR[6:0] default is fixed at 51h. The address bits are used to uniquely identify the S19233 device if multiple I<sup>2</sup>C devices are controlled by a single microprocessor. A more detailed I<sup>2</sup>C interface description can found in the S19233 I<sup>2</sup>C Interface Application Note, AN2076.

A frame is formatted as shown in Figure 3.

**I<sup>2</sup>C Start/Repeat Conditions:** A falling edge on SDA during SCL high time.

**I<sup>2</sup>C Acknowledge:** A low assertion on the SDA line from the receiver after a data transfer.

**I<sup>2</sup>C Not Acknowledge:** A high left on the SDA line by the receiver after a data transfer.

**Stop Code:** A rising edge on SDA during SCL high time. After this condition, the bus becomes tristated, and both SDA and SCL are pulled high.

REFCLKP/N must be supplied continuously in order to access read/write registers through the I<sup>2</sup>C interface.

Figure 3. Two Wire Slave Address

# SONET AND ETHERNET JITTER CRITERIA

#### **SONET Jitter Transfer**

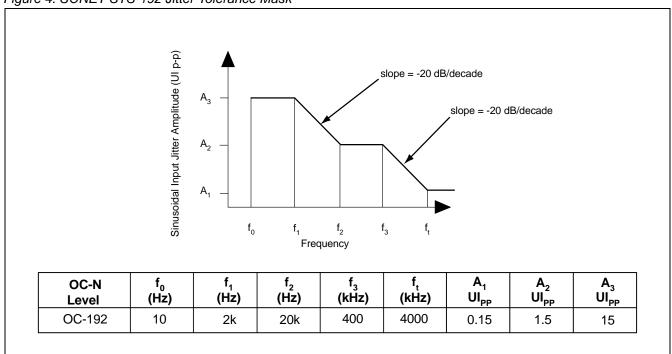

The following jitter transfer requirement applies to STS-192 interfaces as defined in GR-253-Core. For STS-192 interfaces, the jitter transfer function shall meet specifications in Table 13 when input sinusoidal jitter up to the jitter tolerance mask level in Figure 4 is applied.

#### **SONET Jitter Tolerance**

The following jitter tolerance requirement applies to STS-192 interfaces as defined in GR-253-Core. STS-192 interfaces shall tolerate, as a minimum, input jitter applied according to the mask in Figure 4.

Figure 4. SONET STS-192 Jitter Tolerance Mask

#### **SONET Jitter Generation**

The following jitter generation requirement applies to STS-192 interfaces as defined in GR-253-CORE.

According to GR-253-CORE, jitter generation shall not exceed 0.10  $\text{UI}_{PP}$  for STS-192 interfaces when measured using a bandpass measurement filter with a high-pass cutoff frequency of 50 kHz and a low-pass cutoff frequency of at least B3 = 80 MHz.

Note that for SONET rates up to STS-48, the current jitter generation requirement in GR-253-CORE states that the generated jitter must be less than 0.01  $\text{UI}_{\text{rms}}$  and 0.10  $\text{UI}_{\text{PP}}$ . At the STS-192 rate, the measurement of RMS phase variations with less than 0.01 UI granularity (1 picosecond) may not be feasible. Therefore, this requirement specifies the jitter generation only in terms of 0.10  $\text{UI}_{\text{PP}}$ .

The S19233 exceeds the Telcordia Jitter Generation Specification by having less than 50% of the budget in normal modes of operation.

#### 10 Gigabit Ethernet Jitter Tolerance

The following 10 Gigabit Ethernet jitter tolerance requirement applies to 10GBASE-ER as defined in IEEE Std 802.3ae. This total jitter is composed of three components: deterministic jitter; random jitter; and an additional sinusoidal jitter.

The three fundamental components of Jitter Tolerance testing are:

- Input Jitter (Dj and Rj)

- · Sinusoidal Jitter

- Test Pattern (Test patterns are different for 10GBASE-R and 10GBASE-W)

Input Jitter (amount of Dj and Rj)

Dj: 0.35 UI<sub>pp</sub> Rj: 0.015 UI<sub>rms</sub>

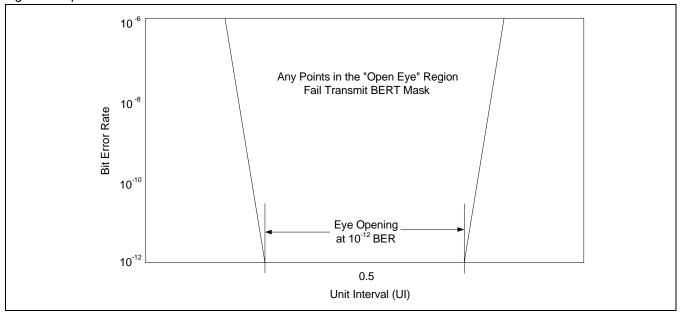

The random jitter (Rj) component of the input signal has uniform spectral content over the measurement frequency range of at least 1 MHz to 1 GHz. Input Signal must pass the bathtub curves between BERs of  $10^{-6}$  and  $10^{-12}$  as shown in Figure 5.

#### Sinusoidal Jitter

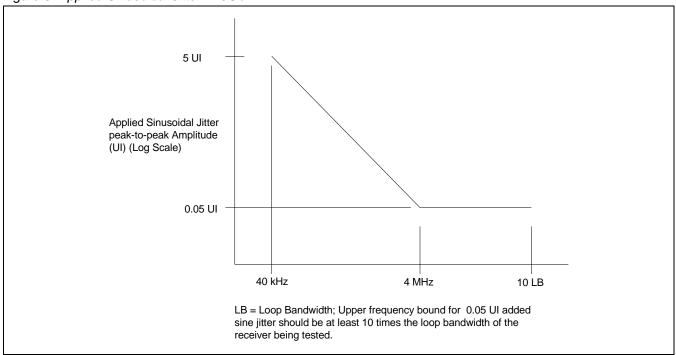

The Sj applied for tolerance testing is defined by the jitter mask shown in Figure 6 and Table 6 (per section IEEE Std 802.3ae). The Loop Bandwidth (LB) for S19233 is approximately 8 MHz.

#### **Test Pattern**

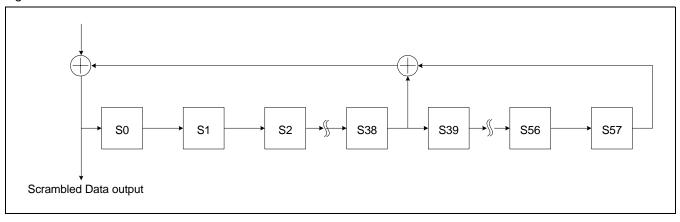

Test pattern is chosen per IEEE Std 802.3ae Section 52.9.1. The test pattern is a static pattern and can be loaded into a BERT. IEEE Std 802.3ae specifies two pseudo-random test patterns for 10GBASE-ER testing. One pattern represents typical scrambled data while the other represents a less typical pattern which could happen by chance and is thought to be more demanding of the transmission process including the clock recovery sub-system. Both patterns are balanced over their length of 33792 bits.

Test pattern is constructed from 4 Segments

- 1 segment is constructed with 128 Blocks

- 1 block is 2 Sync Bits and 64 Payload Bits

- Pay load bits are generated with the scrambler shown in Figure 7.

- Scrambler seeded per Table 7 and Table 8.

- Data input is set to 1 or 0.

Figure 5. Input Jitter for Receiver Test

Figure 6. Applied Sinusoidal Jitter - 10GbE

Table 6. Applied Sinusoidal Jitter

| Frequency Range    | Sinusoidal Amplitude Jitter (UI Peak to Peak) |

|--------------------|-----------------------------------------------|

| f < 40 kHz         | NA                                            |

| 40 kHz < f < 4 MHz | (2 X 10 <sup>5</sup> )/f                      |

| 4 MHz < f < 10 LB  | 0.05                                          |

Figure 7. Scrambler and Descrambler

Table 7. Pattern Segments

| Segments       | Seed [57:0]                      |

|----------------|----------------------------------|

| A <sub>n</sub> | 0x3C8B44DCAB6804F                |

| B <sub>n</sub> | 0x34906BB85A38884                |

| A <sub>i</sub> | Inverted Seed for A <sub>n</sub> |

| B <sub>i</sub> | Inverted Seed for B <sub>n</sub> |

Table 8. Test Patterns

| Pattern | Sequence of Segments |

|---------|----------------------|

| 1       | $B_n B_i B_n B_i$    |

| 2       | $A_n A_i A_n A_i$    |

#### PIN ASSIGNMENTS AND DESCRIPTIONS

Table 9. Signals Pin Assignments and Descriptions

| Pin Name               | Level                     | I/O | Pin#     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|---------------------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 1                         |     |          | TRANSMITTER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TXDATINP<br>TXDATINN   | High<br>Speed<br>Diff CML | I   | G7<br>G6 | <b>Transmit Serial Data Input.</b> Differential high speed serial data input for transmitter. Internally terminated 100 $\Omega$ line-to-line (50 $\Omega$ + 50 $\Omega$ with center tap capacitor). This input must be AC coupled. Clock is recovered from transitions on these inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TXCAP1<br>TXCAP2       | Analog                    | I   | D7<br>C7 | <b>Transmit Loop Filter Capacitors.</b> Connections for external loop filter capacitors and resistors. See Figure 14, External Loop Filters, and Table 19, Transmit and Receive External Loop Filter Components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TXLOCK                 | 3.3 V<br>LVTTL            | 0   | E6       | <b>Transmit Lock</b> . Active High. Goes active after the transmit PLL has locked on the incoming data stream after initially locking onto the clock provided on the REFCLK pins. TXLOCK is an asynchronous output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TXDATOUTP<br>TXDATOUTN | High<br>Speed<br>Diff CML | 0   | A5<br>A6 | <b>Transmit Serial Data Output</b> . Serial data stream signals, normally connected to an optical transmitter module. Output return loss, S <sub>22</sub> of -12dB at 15 GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | •                         | •   |          | RECEIVER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RXDATINP<br>RXDATINN   | High<br>Speed<br>Diff CML | I   | A1<br>A2 | Receive Serial Data Input. Differential high speed serial data input for receiver. Internally biased and terminated 100 $\Omega$ line-to-line (50 $\Omega$ + 50 $\Omega$ with center tap capacitor). This input must be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXCTAP                 | Analog                    | I   | C2       | Center Tap Input. This input should be connected to a broadband 850 pF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RXCAP1<br>RXCAP2       | Analog                    | I   | D1<br>E1 | Receive Loop Filter Capacitors. Connections for external loop filter capacitors and resistors. See Figure 14, External Loop Filters, and Table 19, Transmit and Receive External Loop Filter Components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LOS_SD                 | 3.3 V<br>LVTTL<br>Pull-up | I/O | F4       | Dual purpose pin - Loss of Signal Output for Receiver or Signal Detect Input for Receiver. Active High. Goes active after the receiver fail to sense the incoming data stream. This Loss of Signal is an asynchronous output. When LOS_SD register is set to 0 via I <sup>2</sup> C, this pin becomes the Signal Detect Input for Receiver. Signal Detect Input for Receive. active HIGH default. May be adjusted to be active low with I <sup>2</sup> C control. Signal to be driven by the external optical receiver module to indicate sufficient received optical power. When inactive the RX PLL will be forced to lock to the REFCLKP/N inputs and the data will be forced to a logical '0' or 1' state depending on the polarity of SQ_POL signal and squelch enable feature. |

| RXDATOUTP<br>RXDATOUTN | High<br>Speed<br>Diff CML | 0   | G3<br>G2 | Serial data output for Receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RXLOCK                 | 3.3 V<br>LVTTL            | 0   | C4       | Receive Lock. Active High. Goes active after the receive PLL has locked on the incoming data stream after initially locking onto the clock provided on the REFCLK pins. RXLOCK is an asynchronous output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 9. Signals Pin Assignments and Descriptions (Continued)

| Pin Name           | Level                  | I/O      | Pin#     | Description                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|--------------------|------------------------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | COMMON Signals         |          |          |                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PD/RSTB            | LVCMOS<br>pull-down    | I        | D3       | <b>Powerdown/Reset</b> , active HIGH input. Default Low, when high, power downs the Transmitter and Receiver. 2-wire Serial (I2C) interface and reset generation logic is functional during power-down. The falling edge initiates a complete reset of TX/RX including 2-wire serial interface.                                                                                               |  |  |  |  |  |  |

| REFCLKP<br>REFCLKN | LVPECL                 | I        | E5<br>E4 | Reference Clock. 155.52 MHz (or equivalent FEC/10 GE/10 G FC frequency) input used as the reference for the internal bit clock frequency synthesizer for both receive and transmit reference clock. This input is internally biased and terminated. This input must be AC coupled. REFCLKP/N must be supplied continuously in order to access read/write registers through the I2C interface. |  |  |  |  |  |  |

| SDA<br>SCL         | I2C<br>BUS®            | I/O<br>I | C5<br>C3 | I <sup>2</sup> C BUS <sup>®</sup> . Bi-directional 2-wire bus for efficient inter-IC control. This bus reads from and writes into most of the S19233 control logic.                                                                                                                                                                                                                           |  |  |  |  |  |  |

| SCANMODE           | LVTTL<br>Pull-<br>down | I        | E3       | Scan Logic Input. Active High. Bring device into scan mode. Default low for normal operation.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

Table 10. Common Pin Assignments and Descriptions

| Pin Name  | Level  | I/O | Pin #                                                 | Description                  |

|-----------|--------|-----|-------------------------------------------------------|------------------------------|

| AVDD_TX   | +1.8 V |     | B7, E7                                                | Transmit analog power supply |

| AVDD_RX   | +1.8 V |     | C1, F1                                                | Receive analog power supply  |

| VDD_TX    | +1.8 V |     | B5, B6                                                | Transmit CML power supply    |

| VDD_RX    | +1.8 V |     | F2, F3                                                | Receive CML power supply     |

| VDD_PA_TX | +1.8 V |     | F5, F6                                                | Transmit PA power supply     |

| VDD_PA_RX | +1.8 V |     | B2, B3                                                | Receive PA power supply      |

| VDD_CMOS  | +1.8 V |     | D4                                                    | CMOS power supply            |

| VDD_33IO  | +3.3 V |     | B4                                                    | I/O power supply             |

| VSS       | GND    |     | A3, A4, A7, B1, C6, D2, D5, D6,<br>E2, F7, G1, G4, G5 | Ground                       |

#### **12C SERIAL CONTROL INTERFACE REGISTER MAP SUMMARY**

Table 11 below contains the register map summary for the S19233. For detailed register descriptions, please consult the S19233 - Programmer's Reference Manual: PRM2001. When programming the S19233 device, care should be take to preserve the default state of all RESERVED register bits - see note below.

Register Access Type Definitions

- RW = Read/Write Access

- RO = Read Only Access

- N/A = Access Type Not Applicable

Table 11. Register Map Summary

| Address<br>(hex) | Default<br>Value <sup>a</sup> | Bit<br>Field | Register Name  | Mode | Description                                     |

|------------------|-------------------------------|--------------|----------------|------|-------------------------------------------------|

| 0x00             | -                             | 7:0          | RESERVED       | N/A  | RESERVED                                        |

| 0x01             | 0001 0111                     | 4            | SDPOL          | RW   | Signal Detect Polarity for LOS_SD (Active High) |

|                  |                               | 2            | LOS_SD         | RW   | LOS_SD Pin Configured as LOS or SD (LOS)        |

|                  |                               | 1            | XLEB           | RW   | XFI (Electrical Side) Line Loopback (Disabled)  |

|                  |                               | 0            | OLEB           | RW   | Optical (Optical Side) Line Loopback (Disabled) |

| 0x02             | 0001 100x                     | 7            | RX_CDRBYC      | RW   | RX CDR Bypass (Disabled)                        |

|                  |                               | 5            | RX_POLINV      | RW   | RX Output Polarity Invert (Non-Inverted)        |

|                  |                               | 4            | RX_I2CRSTB     | RW   | RX Reset (Disabled)                             |

|                  |                               | 3            | LCKREFXB       | RW   | Force RX to Lock to Reference (disabled)        |

|                  |                               | 0            | RXLOCK         | RO   | RX Lock Status                                  |

| 0x03             | 0001 100x                     | 7            | TX_CDRBYC      | RW   | TX CDR Bypass (Disabled)                        |

|                  |                               | 5            | TX_POLINV      | RW   | TX Output Polarity Invert (Non-Inverted)        |

|                  |                               | 4            | TX_I2CRSTB     | RW   | TX Reset (Disabled)                             |

|                  |                               | 3            | LCKREFTXB      | RW   | Force TX to Lock to Reference (Disabled)        |

|                  |                               | 0            | TXLOCK         | RO   | TX Lock Status                                  |

| 0x04             | 0111 1011                     | 7            | RX_SQ_POL      | RW   | RX Squelch Polarity (Low)                       |

|                  |                               | 6            | RX_SQ_EN       | RW   | RX Squelch Enable (Enabled, see Table 3)        |

|                  |                               | 5            | RX_SQ_CNTL     | RW   | RX Squelch Control (Enabled, see Table 3)       |

|                  |                               | 4:3          | RX_SQ          | RW   | RX Squelch Control (see Table 3)                |

|                  |                               | 2            | TX_SQ_POL      | RW   | TX Squelch Polarity (active low)                |

|                  |                               | 1            | TX_SQ_EN       | RW   | TX Squelch Enable (Enabled, see Table 4)        |

|                  |                               | 0            | TX_SQ_CNTL     | RW   | TX Squelch Control (see Table 4)                |

| 0x05             | 0000 1101                     | 4:2          | RX_CLKOFFSET   | RW   | RX Clock Phase Offset                           |

| 0x06             | -                             | 7:0          | RESERVED       | N/A  | RESERVED                                        |

| 0x07             | 0010 0100                     | 5:3          | RX_OUTPUT_SLEW | RW   | RX Output Slew Rate Control                     |

|                  |                               | 2:0          | TX_OUTPUT_SLEW | RW   | TX Output Slew Rate Control                     |

Table 11. Register Map Summary

| Address<br>(hex) | Default<br>Value <sup>a</sup> | Bit<br>Field | Register Name         | Mode               | Description                               |

|------------------|-------------------------------|--------------|-----------------------|--------------------|-------------------------------------------|

| 80x0             | -                             | 7:0          | RESERVED              | ERVED N/A RESERVED |                                           |

| 0x09             | 0101 0001                     | 6:0          | DEVICE_ADDR           | RO                 | I <sup>2</sup> C Device Address           |

| 0x0A             | -                             | 7:0          | RESERVED              | N/A                | RESERVED.                                 |

| 0x0B             | 00                            | 7            | RXCOREPD              | RW                 | RX Core Power Down (Disabled)             |

|                  |                               | 6            | TXCOREPD              | RW                 | TX Core Power Down (Disabled)             |

| 0x0C             | 100                           | 7            | RX_PA_DCOFFADJ_ON     | RW                 | RX Automatic Offset Threshold Adjust (On) |

| 0x0D             | -                             | 7:0          | RESERVED              | N/A                | RESERVED                                  |

| 0x0E             | 001-                          | 3:1          | RX_OUT_SWING          | RW                 | RX Output Swing (Low Swing Mode)          |

| 0x0F             | -                             | 7:0          | RESERVED              | N/A                | RESERVED                                  |

| 0x10             | 1000 0000                     | 7:0          | RX_PA_DCOFFSET        | RW                 | RX Manual Offset Threshold Adjust         |

| 0x11             | 1                             | 7            | TX_PA_DCOFFADJ_ON     | RW                 | TX Automatic Offset Threshold Adjust (On) |

|                  |                               | 6:5          | RESERVED1[6:5]b       | RW                 | RESERVED1[6:5]                            |

| 0x12             | -                             | 6:3          | RESERVED2[6:3]b       | RW                 | RESERVED2[6:3]                            |

| 0x13             | 001-                          | 3:1          | TX_OUT_SWING          | RW                 | TX Output Swing (Low Swing Mode)          |

| 0x14             | -                             | 7:0          | RESERVED              | N/A                | RESERVED                                  |

| 0x15             | 1000 0000                     | 7:0          | TX_PA_DCOFFSET        | RW                 | TX Manual Offset Threshold Adjust         |

| 0x16             | 0000 0000                     | 7:0          | RX_LOS_VTH_ASTC       | RW                 | RX LOS Assert Threshold                   |

| 0x17             | 0000 0001                     | 7:0          | RX_LOS_VTH_DSTC       | RW                 | RX LOS De-assert Threshold                |

| 0x18             | -                             | 7:0          | RESERVED              | N/A                | RESERVED                                  |

| 0x19             | 1111 0101                     | 6            | RX_LOS_POL            | RW                 | RX LOS Polarity (Active High)             |

|                  |                               | 5            | RX_LOS_CNTL           | RW                 | RX LOS Function (Enabled)                 |

| 0x1A             | 1100 0000                     | 6:5          | RX_PA_STEP_CNTL       | RW                 | RX Offset Threshold Adjust Step Size      |

|                  |                               | 4:0          | RX_EQ_CNTL_LINK_ OPT2 | RW                 | RX Equalizer Setting                      |

| 0x1B             | 1010 0110                     | 4:0          | RX_EQ_CNTL_LINK_ OPT1 | RW                 | RX EDC Setting                            |

| 0x1C -<br>- 0x1E | -                             | 7:0<br>      | RESERVED              | N/A                | RESERVED                                  |

| 0x1F             | xxxx xxxx                     | 2            | RX_LOS_MEM            | RO                 | RX LOS Status                             |

|                  |                               | 1            | RX_RSSI_HIRANGE       | RO                 | RX RSSI High Range Indicator              |

| 0x20             | xxxx xxxx                     | 7:0          | RX_PA_DCOFFADJ_ FBC   | RO                 | RX Auto Threshold Adjust Read Back Value  |

| 0x21             | xxxx xxxx                     | 7:0          | RX_RSSI               | RO                 | RX RSSI Value                             |

| 0x22 -<br>- 0x70 | -                             | 7:0<br>      | RESERVED              | N/A                | RESERVED                                  |

Data Sheet

Table 11. Register Map Summary

| Address<br>(hex) | Default<br>Value <sup>a</sup> | Bit<br>Field | Register Name         | Mode | Description                                  |

|------------------|-------------------------------|--------------|-----------------------|------|----------------------------------------------|

| 0x71             | 1100 0000                     | 6:5          | TX_PA_STEP_CNTL       | RW   | TX Offset Threshold Adjust Step Size         |

|                  |                               | 4:0          | TX_EQ_CNTL_LINK_ OPT2 | RW   | TX Equalizer Setting                         |

| 0x72             | 1010 0011                     | 4:0          | TX_EQ_CNLT_LINK_ OPT1 | RW   | TX EDC Setting                               |

| 0x73 -<br>- 0x76 | -                             | 7:0<br>      | RESERVED              | N/A  | RESERVED                                     |

| 0x77             | xxxx xxxx                     | 7:0          | TX_PA_DCOFFADJ_ FBC   | RO   | TX AutomaticThreshold Adjust Read Back Value |

| 0x78 -<br>- 0xC3 | -                             | 7:0<br>      | RESERVED              | N/A  | RESERVED                                     |

| 0xC4             | 0111 0000                     | 7:6          | VCO_SEL_CNTL          | RW   | RX & TX VCO Select                           |

| 0xC5 -<br>- 0xFF | -                             | 7:0<br>      | RESERVED              | N/A  | RESERVED                                     |

a. Default values are based on a post reset view of the register map and may differ from part to part depending on the associated register. Consult the Programmer's Reference Manual, PRM2001, for additional notes. "x" represents an unknown value as the associated register bit is configured as read only and may be dependent on a status signal or input value. "-" represents a factory fused default value based on process variation.

b. Consult the Programmer's Reference Manual, PRM2001, for register 0x11 and 0x12 RESERVED1/2 settings when using device revision S19233PBIEB.

## **S19233 PINOUT (TOP VIEW)**

Figure 8. S19233 Pinout (Top View)

|   | 1        | 2         | 3         | 4        | 5         | 6         | 7        |

|---|----------|-----------|-----------|----------|-----------|-----------|----------|

| A | RXDATINP | RXDATINN  | VSS       | VSS      | TXDATOUTP | TXDATOUTN | VSS      |

| В | VSS      | VDD_PA_RX | VDD_PA_RX | VDD33IO  | VDD_TX    | VDD_TX    | AVDD_TX  |

| С | AVDD_RX  | RXCTAP    | SCL       | RXLOCK   | SDA       | VSS       | TXCAP2   |

| D | RXCAP1   | VSS       | PD        | VDD_CMOS | VSS       | VSS       | TXCAP1   |

| E | RXCAP2   | VSS       | SCANMODE  | REFCLKN  | REFCLKP   | TXLOCK    | AVDD_TX  |

| F | AVDD_RX  | VDD_RX    | VDD_RX    | LOS_SD   | VDD_PA_TX | VDD_PA_TX | VSS      |

| G | VSS      | RXDATOUTN | RXDATOUTP | VSS      | VSS       | TXDATINN  | TXDATINP |

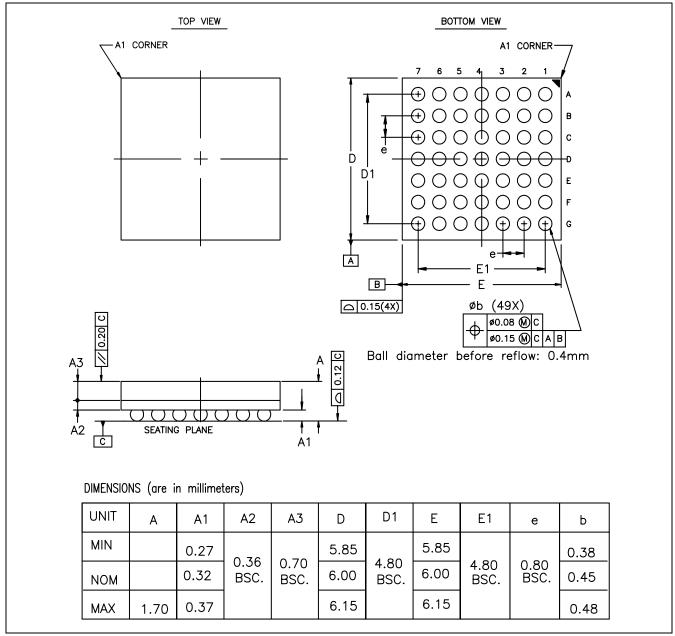

#### S19233 - 49 PBGA PACKAGE MECHANICAL DRAWING

Figure 9. S19233 - 49 PBGA Package Mechanical Drawing

#### **PACKAGE MATERIAL NOTE:**

Standard Package: Ball Composition - 63/37 Sn/Pb.

Green / RoHS Compliant Package: Ball Composition - 96.5/3.0/0.5 Sn/Ag/Cu.

Table 12. Thermal Management

| Device | ⊚ja         | Θјс         |  |

|--------|-------------|-------------|--|

| S19233 | 42.1°C/Watt | 13.8°C/Watt |  |

#### S19233 – 49 PBGA PACKAGE MARKING DRAWING

Figure 10. S19233 – 49 PBGA Package Marking Drawing (Top View)

#### PERFORMANCE SPECIFICATIONS

High-speed/low noise design practices must be implemented to meet the following performance specifications. Consult AMCC's Applications Engineering Department for recommendations regarding your specific application: support@amcc.com.

Table 13. Performance Specifications

| Parameter                                                                                                                                                         | Min                       | Тур | Max                | Units           | Conditions                                                                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|--------------------|-----------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| VCO                                                                                                                                                               |                           |     |                    |                 |                                                                                    |  |  |  |  |  |

| Nominal VCO Center Frequency (both transmit and receive side)                                                                                                     | 9.953                     |     | 11.1               | GHz             |                                                                                    |  |  |  |  |  |

| Upper End VCO Center Frequency (both transmit and receive side)                                                                                                   |                           |     | 11.32 <sup>a</sup> | GHZ             | Consult factory for conditional restrictions                                       |  |  |  |  |  |

| Frequency difference at which the receive PLL goes out of lock (REFCLK compared to the divided down VCO clock). LOCKDET is de-asserted when PLL goes out of lock. | ±350                      |     | ± 550              | ppm             |                                                                                    |  |  |  |  |  |

| Frequency difference at which receive PLL goes into lock (REFCLK compared to the divided down VCO clock). LOCKDET is asserted 0.5 ms after PLL goes into lock.    | ± 220                     |     | ± 320              | ppm             | Guaranteed by design                                                               |  |  |  |  |  |

|                                                                                                                                                                   | Reference Clock           |     |                    |                 |                                                                                    |  |  |  |  |  |

| Reference Clock Frequency Tolerance<br>(Transmit and Receive)                                                                                                     | -100                      |     | +100               | ppm             |                                                                                    |  |  |  |  |  |

| Reference Clock Range                                                                                                                                             | 155                       |     | 177                | MHz             |                                                                                    |  |  |  |  |  |

| Reference Clock Rise & Fall Times for<br>155.52 MHz (or equivalent FEC/10 Gigabit<br>Ethernet rate) REFCLK                                                        | 0.2                       |     | 1.25               | ns              | 20% to 80% of amplitude.                                                           |  |  |  |  |  |

| Duty Cycle of Reference Clock                                                                                                                                     | 40                        |     | 60                 | %               |                                                                                    |  |  |  |  |  |

| Reference Clock Differential Input                                                                                                                                | 640                       |     | 1600               | mV              | AC coupled                                                                         |  |  |  |  |  |

|                                                                                                                                                                   |                           | CDR |                    |                 |                                                                                    |  |  |  |  |  |

| L <sub>CID</sub> Consecutive identical digits at Serial Data Input                                                                                                |                           |     | 80                 | bits            | Number of bits with no transitions (ITU-T spec is 72)                              |  |  |  |  |  |