### **FEATURES**

- 7-bit flash A/D converter

- 20MHz sampling rate

- Low power (250mW)

- Single +5V supply

- 1.2 micron CMOS technology

- 7-bit latched 3-state output with overflow bit

- Surface-mount versions

- High-reliability version

- No missing codes

### PRODUCT OVERVIEW

The ADC-207 is the industry's first 7-bit flash converter using an advanced high-speed VLSI 1.2 micron CMOS process. This process offers some very distinctive advantages over other processes, making the ADC-207 unique. The smaller geometrics of the process achieve high speed, better linearity and superior temperature performance.

Since the ADC-207 is a CMOS device, it also has very low power consumption (250mW). The device draws power from a single +5V supply and is conservatively rated for 20MHz operation. The ADC-207 allows using sampling apertures as small as 12ns, making it more closely approach an ideal

sampler. The small sampling apertures also let the device operate at greater than 20MHz.

The ADC-207 has 128 comparators which are auto-balanced on every conversion to cancel out any offsets due to temperature and/or dynamic effects. The resistor ladder has a midpoint tap for use with an external voltage source to improve integral linearity beyond 7 bits. The ADC-207 also provides the user with 3-state outputs for easy interfacing to other components.

There are eight models of the ADC-207 covering three operating temperature ranges: 0 to  $+70^{\circ}$ C, -40 to  $+100^{\circ}$ C, and -55 to  $+125^{\circ}$ C. Two high-reliability "QL" models are also available.

|          | INPUT/OUTPUT CONNECTIONS |          |

|----------|--------------------------|----------|

| DIP Pins | FUNCTION                 | LCC Pins |

| 1        | CLOCK INPUT              | 1        |

| 2        | DIGITAL GROUND           | 4        |

| 3        | -REFERENCE               | 5        |

| 4        | ANALOG INPUT             | 6        |

| 5        | MIDPOINT                 | 7        |

| 6        | +REFERENCE               | 8        |

| 7        | ANALOG GROUND            | 9        |

| 8        | CS1                      | 11       |

| 9        | CS2                      | 12       |

| 10       | OVERFLOW                 | 13       |

| 11       | 1 BIT 1 (MSB)            |          |

| 12       | BIT 2                    | 16       |

| 13       | BIT 3                    | 17       |

| 14       | BIT 4                    | 19       |

| 15       | BIT 5                    | 20       |

| 16       | BIT 6                    | 21       |

| 17       | BIT 7 (LSB)              | 23       |

| 18       | +5V SUPPLY               | 24       |

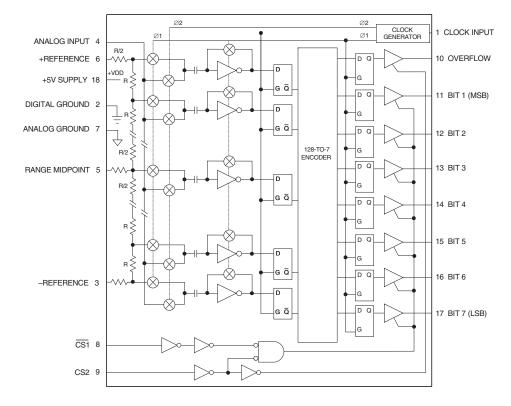

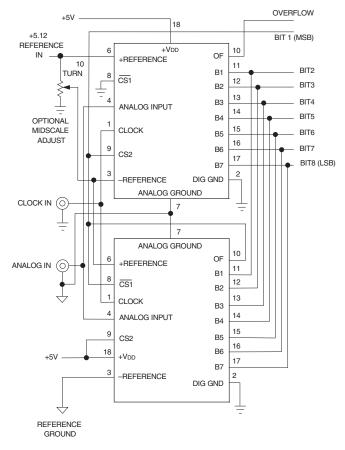

Figure 1. ADC-207 Functional Block Diagram (DIP Pinout)

DATEL is a registered trademark of Murata Power Solutions • 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

| ABSOLUTE MAXIMUM RATINGS        |                                                                                   |  |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| PARAMETERS LIMITS UNITS         |                                                                                   |  |  |  |  |  |  |

| LIMITS                          | UNITS                                                                             |  |  |  |  |  |  |

| -0.5 to +7                      | Volts                                                                             |  |  |  |  |  |  |

| -0.5 to +5.5                    | Volts                                                                             |  |  |  |  |  |  |

| -0.5 to (+V <sub>DD</sub> +0.5) | Volts                                                                             |  |  |  |  |  |  |

| -0.5 to +VDD                    | Volts                                                                             |  |  |  |  |  |  |

| -0.5 to +5.5                    | Volts                                                                             |  |  |  |  |  |  |

|                                 |                                                                                   |  |  |  |  |  |  |

| +300                            | °C                                                                                |  |  |  |  |  |  |

|                                 | -0.5 to +7<br>-0.5 to +5.5<br>-0.5 to (+VDD +0.5)<br>-0.5 to +VDD<br>-0.5 to +5.5 |  |  |  |  |  |  |

# **Functional Specifications**

(Typical at +5V power, +25°C, 20MHz clock, +REFERENCE = +5V, -REFERENCE - ground unless noted)

| -REFERENCE = ground, unless note                                                                                                                                                               |                                       |                                          | ,                                   |                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------|-------------------------------------|------------------------------------------|

| ANALOG INPUT                                                                                                                                                                                   | MIN.                                  | TYP.                                     | MAX.                                | UNITS                                    |

| Input Type<br>Input Range (dc-20MHz)<br>Input Impedance<br>Input Capacitance (Full Range)                                                                                                      | 0<br><u>-</u><br>-                    | Single-e<br>—<br>1000<br>10              | ended, non-<br>+5<br>—<br>—         | isolated<br>Volts<br>Ohms<br>pF          |

| DIG                                                                                                                                                                                            | Ital input                            | S                                        |                                     |                                          |

| Logic Levels Logic "1" Logic "0" Logic Loading "1" Logic Loading "0" Sample Pulse Width (During Sampling Portion of Clock) Reference Ladder Resistance                                         | +3.2<br>—<br>—<br>—<br>—<br>12<br>225 |                                          | +0.8<br>±5<br>±5                    | Volts<br>Volts<br>microamps<br>microamps |

|                                                                                                                                                                                                |                                       |                                          |                                     | Offilis                                  |

|                                                                                                                                                                                                | RFORMANC                              |                                          |                                     | NAL I                                    |

| Conversion Rate ① Harmonic Distortion ② (8MHz 2nd Order Harmonic) Differential Gain ③ Differential Phase ③ Aperture Delay Aperture Jitter No Missing Codes LC/MC grade LE/ME grade LM/MM grade | 20<br><br><br><br>0<br>-40<br>-55     | 25<br>-40<br>3<br>1.5<br>8<br>50<br><br> | <br><br><br><br>+70<br>+100<br>+125 | MHz  dB % degrees ns ps  °C °C °C        |

| Integral Linearity   Over Temperature Range Differential Nonlinearity Over Temperature Range Power Supply Rejection                                                                            | _<br>_<br>_<br>_<br>_                 | ±0.8<br>±1<br>±0.3<br>±0.4<br>±0.02      | ±1<br>—<br>±0.5<br>±0.6<br>—        | LSB<br>LSB<br>LSB<br>LSB<br>%FSR/%Vs     |

|                                                                                                                                                                                                | TAL OUTPU                             |                                          |                                     |                                          |

| Data Coding Data Output Resolution Logic Levels                                                                                                                                                | 7                                     | Straight —                               | binary<br>—                         | Bits                                     |

| Logic "1" Logic "0" (at 1.6mA)                                                                                                                                                                 | +2.4<br>—<br>–4                       | +4.5<br>—<br>—                           | +0.4                                | Volts<br>Volts<br>mA                     |

| Data Coding                            |            | Straight | binary |       |

|----------------------------------------|------------|----------|--------|-------|

| Data Output Resolution                 | 7          | _ `      | _      | Bits  |

| Logic Levels                           |            |          |        |       |

| Logic "1"                              | +2.4       | +4.5     | _      | Volts |

| Logic "0" (at 1.6mA)                   | _          | _        | +0.4   | Volts |

| Logic Loading "1"                      | -4         | _        | _      | mA    |

| Logic Loading "0"                      | +4         | _        | _      | mA    |

| Output Data Valid Delay                |            |          |        |       |

| (From Rising Edge)                     | _          | 15       | 17     | ns    |

| POWE                                   | R REQUIREN | IENTS    |        |       |

| Power Supply Range (+V <sub>DD</sub> ) | +3.0       | +5.0     | +5.5   | Volts |

| Power Supply Current                   | _          | +50      | +70    | mA    |

| Power Dissipation                      | _          | 250      | 385    | mW    |

| Footnotes:                             |            |          |        |       |

- ① At full power input and chip selects enabled.

- ② At 4MHz input and 20MHz clock.

- ③ For 10-step, 40 IRE NTSC ramp test.

- ④ Adjustable using reference ladder midpoint tap. See ADC-207 Operation.

| PHYSICAL/ENVIRONMENTAL       |                    |        |             |       |  |  |  |

|------------------------------|--------------------|--------|-------------|-------|--|--|--|

| PARAMETERS                   | MIN.               | TYP.   | MAX.        | UNITS |  |  |  |

| Operating Temp. Range, Case: |                    |        |             |       |  |  |  |

| LC/MC Versions               | 0                  | _      | +70         | °C    |  |  |  |

| LE/ME Versions               | -40                | _      | +100        | °C    |  |  |  |

| MM/LM/QL Versions            | -55                | _      | +125        | °C    |  |  |  |

| Storage Temp. Range          | -65                | _      | +150        | °C    |  |  |  |

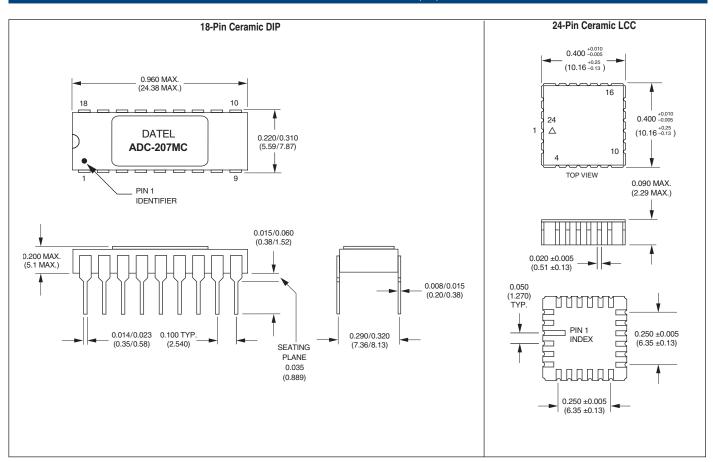

| Package Type                 |                    |        |             |       |  |  |  |

| DIP                          | 18-pin ceramic DIP |        |             |       |  |  |  |

| LCC                          |                    | 24-pin | ceramic LCC | 0     |  |  |  |

#### **TECHNICAL NOTES**

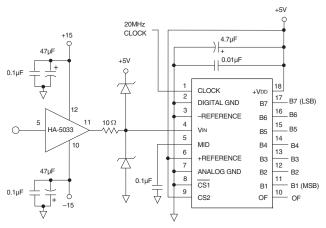

- 1. Input Buffer Amplifier Since the ADC-207 has a switched capacitor type input, the input impedance of the 207 is dependent on the clock frequency. At relatively slow conversion rates, a general purpose type input buffer can be used; at high conversion rates DATEL recommends either the HA-5033 or Elantec 2003. See Figure 2 for typical connections.

- 2. Reference Ladder Adjusting the voltage at +REFERENCE adjusts the gain of the ADC-207. Adjusting the voltage at -REFERENCE adjusts the offset or zero of the ADC-207. The midpoint pin is usually bypassed to ground through a 0.1µF capacitor, although it can be tied to a precision voltage halfway between +REFERENCE and –REFERENCE. This would improve integral linearity beyond 7 bits.

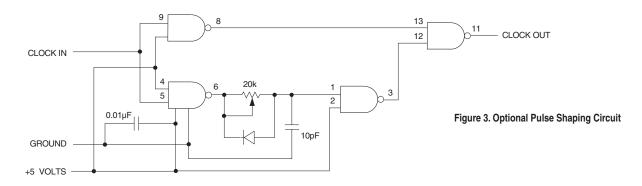

- 3. Clock Pulse Width To improve performance at Nyquist bandwidths, the clock duty cycle can be adjusted so that the low portion of the clock pulse is 12ns wide. The smaller aperture allows the ADC-207 to closely resemble an ideal sampler. See Figure 4.

- 4. At sampling rates less than 100kHz, there may be some degradation in offset and differential nonlinearity. Performance may be improved by increasing the clock duty cycle (decreasing the time spent in the sample mode).

#### CAUTION

Since the ADC-207 is a CMOS device, normal precautions against static electricity should be taken. Use ground straps, grounded mats, etc. The Absolute Maximum Ratings of the device MUST NOT BE EXCEEDED as irrevocable damage to the ADC-207 will occur.

Figure 2. Typical Connections for Using the ADC-207

DATEL is a registered trademark of Murata Power Solutions • 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

# 7-Bit, 20MHz, CMOS Flash A/D Converters

#### **OUTPUT CODING**

(+REFERENCE = +5.12V, -REFERENCE = ground, MIDPOINT = no connection) NOTE: The reference should be held to  $\pm 0.1\%$  accuracy or better. Do not use the  $\pm 5V$ power supply as a reference input without precision regulation and high frequency decoupling.

Values shown here are for a +5.12V reference. Scale other references proportionally. Calibration equipment should test for code changes at the midpoints between these center values shown in Table 1. For example, at the half-scale major carry, set the input to 2.54V and adjust the reference until the code flickers equally between 63 and 64. Note also that the weighting for the comparator resistor network leaves the first and last thresholds within 1/2LSB of the end points to adjust the code transition to the proper midpoint values.

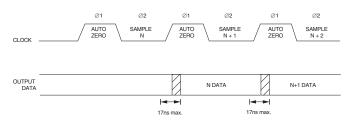

**TIMING DIAGRAM**

Table 1. ADC-207 Output Coding

| Analog Input Code | Overflow      | 1       | 2  | 3   | 4 | 5 | 6 | 7   | Decimal | Hexadecimal |            |

|-------------------|---------------|---------|----|-----|---|---|---|-----|---------|-------------|------------|

| (Center Value)    | Code          | Overnow | MS | MSB |   |   |   | LSB |         | Decimai     | (Incl. 0V) |

| 0.00V             | Zero          | 0       | 0  | 0   | 0 | 0 | 0 | 0   | 0       | 0           | 00         |

| +0.04V            | +1LSB         | 0       | 0  | 0   | 0 | 0 | 0 | 0   | 1       | 1           | 01         |

| +1.28V            | +1/4FS        | 0       | 0  | 1   | 0 | 0 | 0 | 0   | 0       | 32          | 20         |

| +2.52V            | +1/2FS - 1LSB | 0       | 0  | 1   | 1 | 1 | 1 | 1   | 1       | 63          | 3F         |

| +2.56V            | +1/2FS        | 0       | 1  | 0   | 0 | 0 | 0 | 0   | 0       | 64          | 40         |

| +2.60V            | +1/2FS + 1LSB | 0       | 1  | 0   | 0 | 0 | 0 | 0   | 1       | 65          | 41         |

| +3.84V            | +3/4FS        | 0       | 1  | 1   | 0 | 0 | 0 | 0   | 0       | 96          | 60         |

| +5.08V            | +FS           | 0       | 1  | 1   | 1 | 1 | 1 | 1   | 1       | 127         | 7F         |

| +5.12V            | Overflow      | 1       | 1  | 1   | 1 | 1 | 1 | 1   | 1       | 255*        | FF         |

### **ADC-207 OPERATION**

The ADC-207 uses a switched capacitor scheme in which there is an autozero phase and a sampling phase. See Figure 1 and Timing Diagram. The ADC-207 uses a single clock input. When the clock is at a high state (logic 1), the ADC-207 is in the auto-zero phase (Ø1). When the clock is at a low state (logic 0), the ADC-207 is in the sampling phase (Ø2). During phase 1, the 128 comparator outputs are shorted to their inputs through CMOS switches. This serves the purpose of bringing the inputs and outputs to the transition levels of the respective comparators. The inputs to the comparators are also connected to 128 sampling capacitors. The other end of the 128 capacitors are also shorted to 128 taps of a resistor ladder, via CMOS switches. Therefore, during phase 1 the sampling capacitors are charged to the differential voltage between a resistor tap and its respective comparator transition voltage.

This eliminates offset differences between comparators and yields better temperature performance. During phase 2 (Ø2) the input voltage is applied to the 128 capacitors, via CMOS switches. This forces the comparators to trip either high or low. Since the comparators during phase 1 were sitting at their transition point, they can trip very quickly to the correct state. Also during phase 2, the outputs of the comparators are loaded into internal latches which in turn feed a128-to-7 encoder. When going back into phase 1, the output of the encoder is loaded into an output latch. This latch then feeds the 3-state output buffer.

This means that the ADC-207 is of pipeline design. To do a single conversion, the ADC-207 requires a positive pulse followed by a negative pulse followed by a positive pulse. Continuous conversion requires one cycle/ sample (one positive pulse and one negative pulse). The 3-state buffer has

two enable lines, CS1 and CS2. Table 2 shows the truth table for chip select signals. CS1 has the function of enabling/disabling bits 1 through 7. CS2 has the function of enabling/disabling bits 1 through 7 and the overflow bit. Also, a full-scale input produces all ones, including the overflow bit at the output. The ADC-207 has an adjustable resistor ladder string. The top end, idle point, and bottom end are brought out for use with applications circuits.

These pins are called +REFERENCE, MIDPOINT and -REFERENCE, respectively. In typical operation +REFERENCE is tied to +5V, -REFERENCE is tied to ground, and MIDPOINT is bypassed to ground. Such a configuration results in a 0 to +5V input voltage range. The MIDPOINT pin can also be tied to a +2.5V source to further improve integral linearity. This is usually not necessary unless better than 7-bit linearity is needed.

Table 2. Chip Select Truth Table

| <u>CS1</u> | CS2 | Bits 1-7      | Overflow Bit  |

|------------|-----|---------------|---------------|

| 0          | 0   | 3-State Mode  | 3-State Mode  |

| 1          | 0   | 3-State Mode  | 3-State Mode  |

| 0          | 1   | Data Outputed | Data Outputed |

| 1          | 1   | 3-State Mode  | Data Outputed |

|            |     |               |               |

NOTE: Reduce the sample time (sample pulse) to 12ns to improve performance above 20MHz. Such a configuration will closely resemble an ideal sampler.

DATEL is a registered trademark of Murata Power Solutions • 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 www.datel.com e-mail: help@datel.com

### **USING TWO ADC-207s FOR 8-BIT RESOLUTION**

Two ADC-207s (A and B) are cascadable for applications requiring 8-bit resolution. The device A provides a typical 7-bit output. The OVERFLOW signal of device A turns off device A and turns on the device B. The OVER-FLOW signal of device A is also used as MSB for 8-bit operation. The device B provides the other seven bits from the input signal. Figure 4 shows the circuit connections for the application.

Figure 4. Using Two ADC-207s for 8-Bit Operation

NOTE: The output data bit numbering is offset by a bit to the device B's output.

### **BEAT FREQUENCY AND ENVELOPE TESTS**

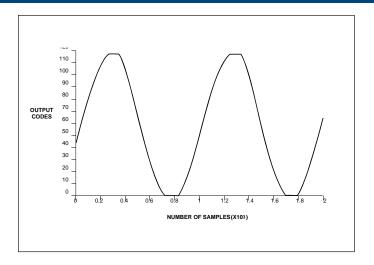

Figure 5 shows an actual ADC-207 plot of the Beat Frequency Test. This test uses a 20MHz clock input to the ADC-207 with a 20.002MHz full-scale sine wave input. Although the converter would not normally be used in this mode because the input frequency violates Nyquist criteria for full recovery of signal information, the test is an excellent demonstration of the ADC-207's high-frequency performance.

The effect of the 2kHz frequency difference between the input and the clock is that the output will be a 2kHz sinusoidal digital data array which "walks" along the actual input at the 2kHz beat note frequency. Any inability to follow the 20.002MHz input will be immediately obvious by plotting the digital data array. Further arithmetic analysis may be done on the data array to determine spectral purity, harmonic distortion, etc. This test is an excellent indication of:

- Full power input bandwidth of all 128 comparators.

(Any gain loss would show as signal distortion.)

- Phase response linearity vs. instantaneous signal magnitude. (Phase problems would show as improper codes.)

- 3. Comparator slew rate limiting.

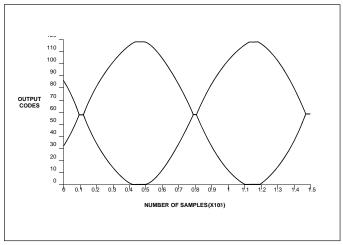

Figure 6 shows an actual ADC-207 plot of the Envelope Test. This test is a variation of the previous test but uses a 10.002MHz sinewave input to give two overlapping cycles when the data is reconstructed by a D/A converter output to an oscilloscope. The scope is triggered by the 20MHz clock used by the A/D. Any asymmetry between positive and negative portions of the signal will be very obvious. This test is an excellent indication of slew rate capability. At the peaks of the envelope, consecutive samples swing completely through the input voltage range.

Figure 5. Beat Frequency Test at 20MHz

Figure 6. 10MHz Envelope Test

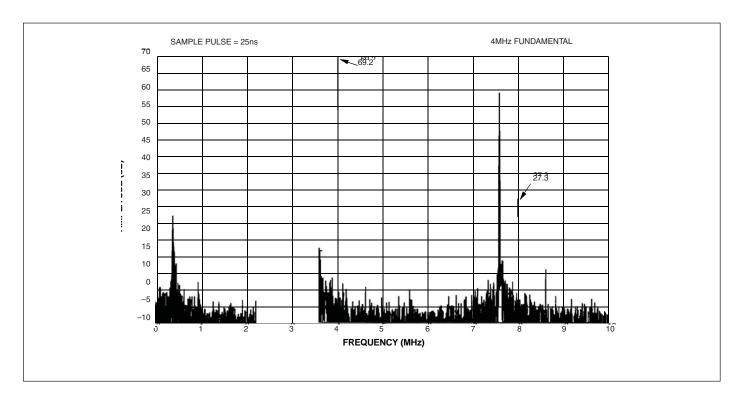

## **FFT TEST**

This test actually produces an amplitude versus frequency graph (Figure 7) which indicates harmonic distortion and signal-to-noise ratio. The theoretical rms signal-to-noise ration for a 7-bit converter is +43.8dB.

Figure 7. FFT Test Using the ADC-207

DATEL is a registered trademark of Murata Power Solutions • 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

### MECHANICAL DIMENSIONS INCHES (mm)

|              | ORDERING INFORMATION                               | N           |  |

|--------------|----------------------------------------------------|-------------|--|

|              |                                                    |             |  |

| MODEL        | TEMP. RANGE                                        | PACKAGE     |  |

| ADC-207MC    | 0 to +70°C                                         | 18-pin DIP  |  |

| ADC-207ME    | -40 to +100°C                                      | 18-pin DIP  |  |

| ADC-207MM    | -55 to +125°C                                      | 18-pin DIP  |  |

| ADC-207MM-QL | -55 to +125°C                                      | 18-pin DIP  |  |

| ADC-207LC    | 0 to +70°C                                         | 24-pin CLCC |  |

| ADC-207LE    | -40 to +100°C                                      | 24-pin CLCC |  |

| ADC-207LM    | -55 to +125°C                                      | 24-pin CLCC |  |

| ADC-207LM-QL | −55 to +125°C                                      | 24-pin CLCC |  |

| ACCESSORIES  |                                                    |             |  |

| ADC-B207/208 | Evaluation Board for DIP Version (without ADC-207) |             |  |

DATEL is a registered trademark of Murata Power Solutions, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA ITAR and ISO 9001/14001 REGISTERED

Murata Power Solutions, Inc. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

© 2012 Murata Power Solutions, Inc.

www.datel.com • e-mail: help@datel.com