## MC3420 MC3520

## Specifications and Applications Information

## SWITCHMODE REGULATOR CONTROL CIRCUIT

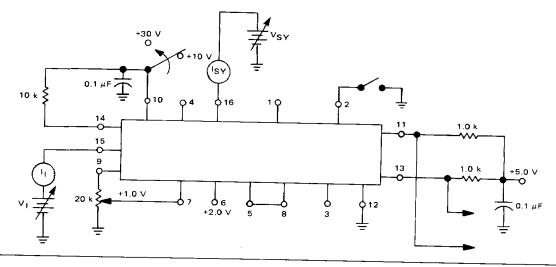

The MC3520/3420 is an inverter control unit which provides all the control circuitry for PWM push-pull, bridge and series type switchmode power supplies.

These devices are designed to supply the pulse width modulated drive to the bases of two external power transistors. Other applications where these devices can be used are in transformer-less voltage doublers, transformer coupled dc-to-dc converters and other power control functions.

The MC3520 is specified over the military operating range of  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . The MC3420 is specified from 0°C to  $+70^{\circ}\text{C}$ .

- Includes Symmetrical Oscillator

- On Chip Pulse Width Modulator, Voltage Reference, Dead Time Comparator, and Phase Splitter

- Output Frequency Adjustable (2.0 kHz to 100 kHz)

- Inhibit and Symmetry Correction Inputs Available

- Controlled Start-Up

- Frequency and Dead Time are Independently Adjustable (0% to 100%)

- Can be Slaved to Other MC3420s

- Open Collector Outputs

- Output Capability 50 mA (Max.)

- On Chip Protection Against Double Pulsing of Same Output During Load Transient Condition

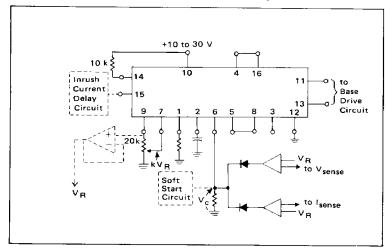

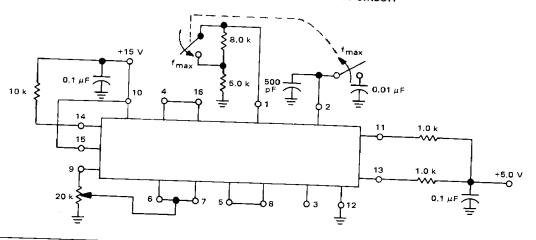

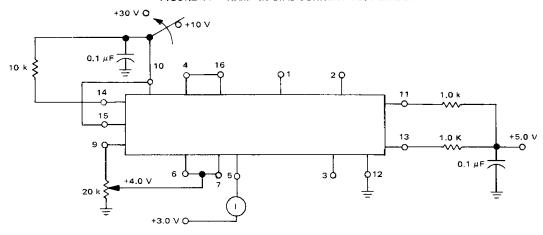

#### FIGURE 1-TYPICAL APPLICATION

# SWITCHMODE REGULATOR CONTROL CIRCUIT

SILICON MONOLITHIC INTEGRATED CIRCUITS

|         | ERING INFORMAT       |             |

|---------|----------------------|-------------|

| DEVICE  | TEMPERATURE<br>RANGE | PACKAGE     |

| MC3420P | 0 to +70°C           | Plastic DIP |

| MC3420L | 0 to +70°C           | Ceramic DIF |

| MC3520L | -55 to +125°C        | Ceramic DIP |

## MAXIMUM RATINGS

| Rating                              | Symbol           | MC3520                  | MC3420      | Unit |

|-------------------------------------|------------------|-------------------------|-------------|------|

| Power Supply Voltage                | Vcc              | 3                       | 0           | ٧    |

| Output Voltage (pins 11 and 13)     | Vout             | 40                      |             | ٧    |

| Oscillator Output Voltage (pin 14)  | V14              | 30                      |             | ٧    |

| Voltage at pin 4                    | V4               | 2.0                     |             | V    |

| Voltage at pins 3 and 8             | V3, V8           | 5.0                     |             | V    |

| Voltage at pin 5                    | V <sub>5</sub>   | 7.0                     |             | ٧    |

| Power Dissipation                   | PD               | See Thermal Information |             |      |

| Operating Junction Temperature      | Tj               |                         |             | oC   |

| Plastic Package                     |                  | _                       | 125         |      |

| Ceramic Package                     |                  | 150                     | 150         |      |

| Operating Ambient Temperature Range | TA               | -55 to +125             | 0 to +70    | οC   |

| Storage Temperature Range           | T <sub>stg</sub> | -65 to +150             | -65 to +150 | °C   |

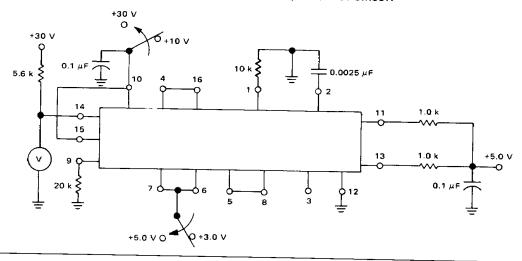

ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 10 to 30 V, T<sub>A</sub> = 25°C unless otherwise noted.)

|                                                                                                         | 1            | Ĺ                     | MC3520   |              |          | MC3420 |              |                  | 4                      |

|---------------------------------------------------------------------------------------------------------|--------------|-----------------------|----------|--------------|----------|--------|--------------|------------------|------------------------|

| Characteristic                                                                                          | Figure       | Symbol                | Min      | Тур          | Max      | Min    | Тур          | Max              | Unit                   |

| REFERENCE SECTION                                                                                       |              |                       |          |              |          |        |              |                  | ·                      |

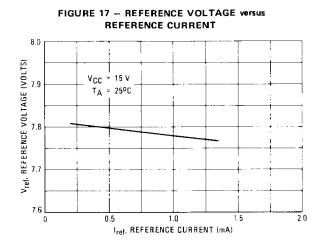

| Reference Voltage<br>(I <sub>ref</sub> = 400 µA)                                                        | 5            | V <sub>ref</sub>      | 7.6      | 7.8          | 8.0      | 7.4    | 7.8          | 8.2              | V                      |

| Temperature Coefficient of Reference Voltage  {VCC = 15 V, I <sub>ref</sub> = 400 µA}                   | 5            | TCV <sub>ref</sub>    |          | 800.0        | 0.03     | 1      | 0.008        | 0.03             | %/ <sup>0</sup> C      |

| Input Regulation of Reference Voltage (I <sub>ref</sub> = 400 µA) (I <sub>ref</sub> = 1.0 mA)           | 5            | Regline               |          | 3.0<br>5.0   | 7.5      | _<br>  | 4.0<br>5.0   | 7.5<br>_         | mV/\                   |

| DC SUPPLY SECTION                                                                                       | <del> </del> |                       |          |              |          | 40     | т:-          | T 20             | V                      |

| Supply Voltage                                                                                          | 5            | Vin                   | 10       |              | 30       | 10     |              | 30               | <u> </u>               |

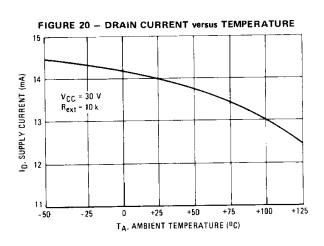

| Supply Current $(R_{ext} = 10 \text{ k}\Omega, excluding load and current and reference current})$      | 5            | l D                   | _        | _            | 16       | -      |              | 22               | mA                     |

| OSCILLATOR SECTION                                                                                      |              |                       |          |              | , -      | 1      |              |                  | т                      |

| Line Frequency Stability (f = 20 kHz) (f = 20 kHz, V <sub>CC</sub> = 15 V, T <sub>low</sub> to Thigh)   | 5            | Δf<br>Δf              | _<br>  _ | 0.03         | 3.0      | -      | 0.04         | 5.0              | %<br>%/ <sup>0</sup> ( |

| Maximum Output Frequency (V <sub>CC</sub> = 15 V)                                                       | 6            | fmax                  | 100      | 200          |          | 100    | 200          | _                | kHź                    |

| Minimum Output Frequency (V <sub>CC</sub> = 15 V)                                                       | 6            | <sup>f</sup> min      | _        | 2.0          | 5.0      |        | 2.0          | 5.0              | kHz                    |

| Oscillator Output Saturation Voltage (I14 sink = 5.0 mA)                                                | 11           | V <sub>osc(sat)</sub> | _        | 0.2          | 0.5      | _      | 0.2          | 0.5              |                        |

| OUTPUT SECTION                                                                                          |              |                       |          |              |          | Υ      |              | _                | т                      |

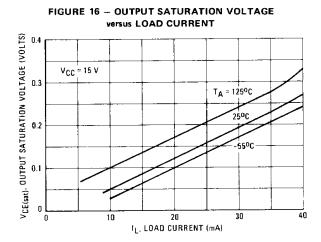

| Output Saturation Voltage (IL = 40 mA, $T_{high}$ to $T_{low}$ ) {IL = 25 mA, $T_{high}$ to $T_{low}$ } | 7            | VCE(sat)              | _        | 0.33<br>0.22 | 0.5      |        | 0.33<br>0.22 | 0.5              | V                      |

| Output Leakage Current<br>(V <sub>CE</sub> = 40 V, Pins 11 and 13)                                      | 8            | ICE                   |          | _            | 50       | _      |              | 50               | μА                     |

| COMPARATOR SECTION                                                                                      |              |                       |          |              | 1        | 1 .    |              | T 400            | - 01                   |

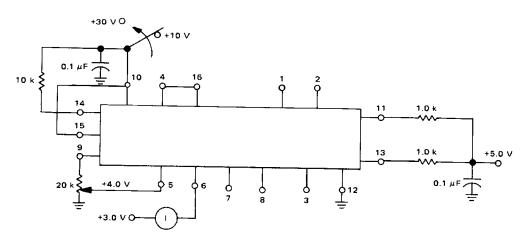

| Pulse Width Adjustment Range                                                                            | 9            | ΔPW                   | 0        | <b>_</b>     | 100      | 0      |              | 100              | %                      |

| Dead Time Adjustment Range                                                                              | 9            | ΔDT                   | 0        |              | 100      | 0      |              | 100              | %                      |

| Temperature Coefficient of Dead Time                                                                    |              | TCDT                  |          | 0.1          | <u> </u> |        | 0.1          |                  | %/ <sup>C</sup>        |

| Comparator Bias Currents                                                                                | 12,13<br>14  | I <sub>IB</sub>       | _        | 5.0<br>10    | 15<br>30 | _<br>_ | 5.0          | 1 <b>5</b><br>30 | <b>μ</b> Α<br>μΔ       |

## **ELECTRICAL CHARACTERISTICS (continued)**

| Characteristic                                            |           |                        | MC3520 |       |                                                  | MC3420         |       |              | T           |

|-----------------------------------------------------------|-----------|------------------------|--------|-------|--------------------------------------------------|----------------|-------|--------------|-------------|

| AUXILIARY INPUTS/OUTPUTS                                  | Figure    | Symbol                 | Min    | Тур   | Max                                              | Min            | Тур   | Max          | Unit        |

| Ramp Voltage                                              |           |                        |        |       |                                                  |                |       |              |             |

| Peak High                                                 | 5         |                        |        |       | Τ                                                | T-             | Т-    | Т            | Τv          |

| Peak Low                                                  |           | V <sub>ramp(Hi)</sub>  | 5.5    | 6.0   | 6.5                                              | 5.5            | 6.0   | 6.5          | °           |

| Ramp Voltage Change                                       |           | V <sub>ramp(Low)</sub> | 2.0    | 2.4   | 2.8                                              | 2.0            | 2.4   | 2.8          | 1           |

| (Vramp Hi - Vramp Low)                                    | 5         | △ V <sub>ramp</sub>    | 3.0    | 3.5   | 4.0                                              | 3.0            | 3.5   | 4.0          | l v         |

| Ramp Out Sink Current                                     |           |                        |        | l     | -                                                |                |       | 7.0          | *           |

|                                                           | 5         | sink                   |        | 400   | <del>                                     </del> | <del>  -</del> | 400   | <del> </del> | μA          |

| Ramp Out Source Current                                   | 5         | Isource                |        | 3.0   |                                                  | <del> </del> - | 3.0   | ⊢ —          | <del></del> |

| Inhibit Input Current — High                              | 10        | IIH                    |        |       | 40                                               | <del></del>    | 3.0   | -            | mA          |

| (V <sub>IH</sub> = 2.0 V)                                 | i         | l ''' I                |        | _     | 40                                               | _              | -     | 40           | μA          |

| Inhibit Input Current — Low                               | 10        | IIL.                   |        | -25   | -180                                             | <del> </del>   |       |              |             |

| (V <sub>IL</sub> = 0.8 V)                                 |           |                        |        | -25   | -180                                             | _              | -25   | -180         | μA          |

| Symmetry Correction Input/Output 2 Inhibit Current — High | 10        | <sup>I</sup> SY/H      |        |       |                                                  |                |       |              | <b> </b>    |

| $(V_{SY} = 2.0 \text{ V, Pin 16})$                        |           | 31/11                  | _      | -     | 40                                               | _              | - 1   | 40           | μA          |

| Symmetry Correction Input/Output 2 Inhibit Current - Low  | 10        | ISY/L                  |        | -10   | 400                                              |                |       |              |             |

| $V_{SY} = 0.8 \text{ V, Pin 16}$                          | ,,,       | 'SY/L                  | _      | -10   | -180                                             | _              | -10   | -180         | μA          |

| F/F <sub>out</sub> Source Current                         |           |                        |        |       |                                                  |                |       |              |             |

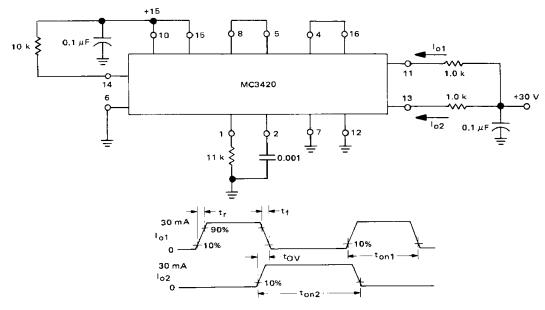

| OUTPUT AC CHARACTERISTICS (TA = Thigh, VCC)               | ≈ +15 V f | source                 |        | 2.0   |                                                  |                | 2.0   |              | mA          |

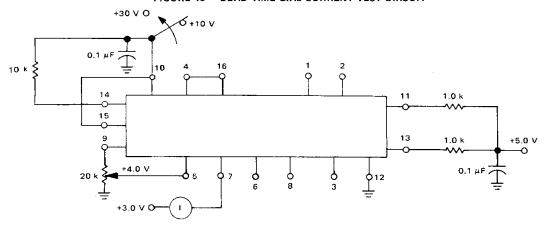

| Rise Time                                                 |           | - 20 KH2)              |        |       |                                                  |                |       |              |             |

| Fall Time                                                 | 15        | tr                     |        | 40    | - 7                                              | _              | 40    |              | ns          |

| Overlap Time                                              | 15        | tf                     | - 1    | 150   |                                                  |                | 150   |              | ns          |

| <del></del>                                               | 15        | tov                    |        | 275   |                                                  |                | 275   |              |             |

| Assymmetry                                                | 15        | ton1 -ton2             |        | ± 1.0 |                                                  |                | ± 1.0 |              | ns          |

| (Duty Cycle = 50%)                                        | İ         |                        |        |       |                                                  | _              | ± 1.0 | _            | %           |

|                                                           |           | ton1                   | 1      | 1     | - 1                                              | - 1            | i     |              |             |

## NOTE:

Thigh = +125°C for MC3520

+70°C for MC3420

$T_{low} = -55^{\circ}C$  for MC3520

0°C for MC3420

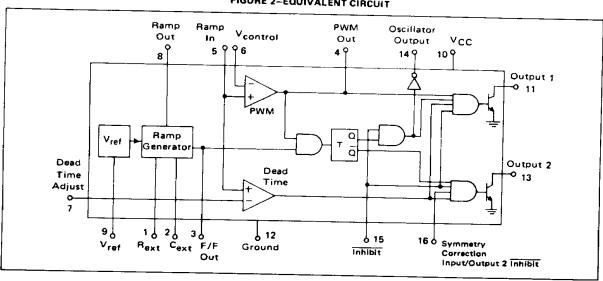

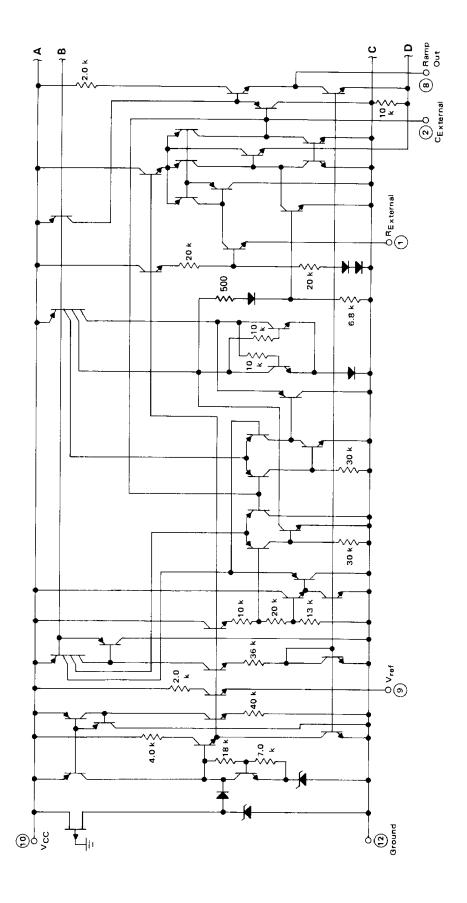

## FIGURE 2-EQUIVALENT CIRCUIT

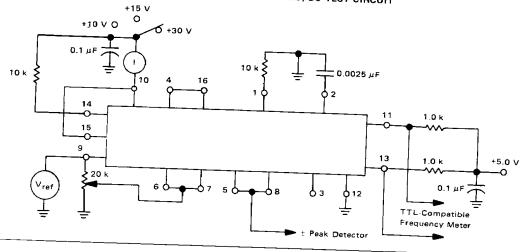

FIGURE 3 -- CIRCUIT SCHEMATIC (continued next page)

(continued) FIGURE 3 - CIRCUIT SCHEMATIC

MOTOROLA LINEAR/INTERFACE DEVICES

## **GENERAL INFORMATION**

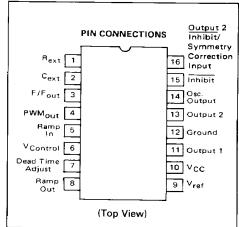

The internal block diagram of the MC3420 is shown in Figure 2, and consists of the following sections:

#### Voltage Reference

A stable reference voltage is generated by the MC3420 primarily for internal use. However, it is also available externally at Pin 9 ( $V_{ref}$ ) for use in setting the dead time (Pin 7) and for use as a reference for the external control loop error amplifiers.

#### Ramp Generator

The ramp generator section produces a symmetrical triangular waveform ramping between 2.4 V and 6.0 V, with frequency determined by an external resistor ( $R_{\text{ext}}$ ) and capacitor ( $C_{\text{ext}}$ ) tied from Pins 1 and 2, respectively, to ground.

#### **PWM Comparator**

The output of the ramp generator at pin 8 is normally connected to Pin 5, RAMP IN. The PWM (pulse width modulation) comparator compares the voltage at Pin 6 (Vcontrol) to the ramp generator output. The level of Vcontrol determines the outputs' pulse width or duty cycle. The duty cycle of each output can vary, exclusive of dead time, from 50% (when Vcontrol is at approximately 2.4 V) to 0% (Vcontrol approximately 6.0 V).

#### **Dead Time Comparator**

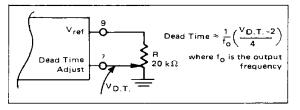

An additional comparator has been included in MC3420 to allow independent adjustment of system dead time or maximum duty cycle. By dividing down  $V_{ref}$  at Pin 9 with a resistive divider or potentiometer, and applying this voltage to Pin 7, a stable dead time is obtained for prevention of inverter switching transistor cross conduction at high duty cycles due to storage time delays.

#### Phase Splitter

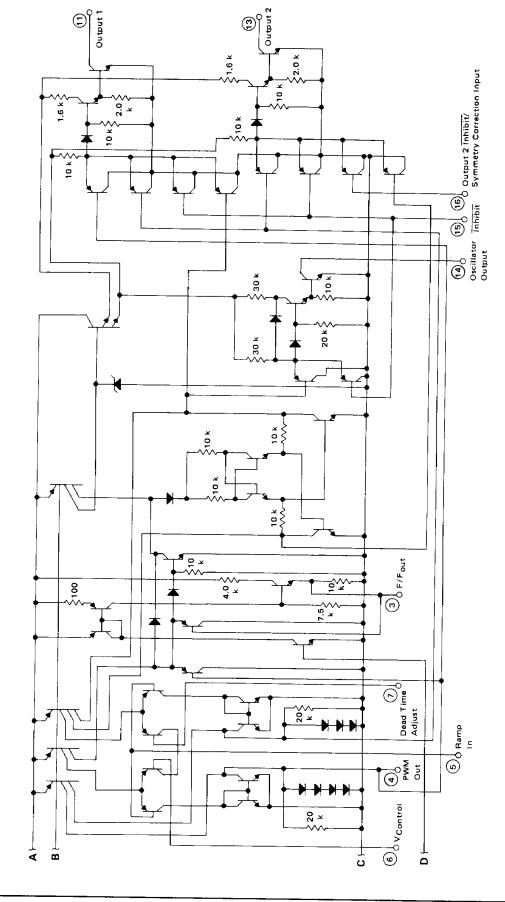

A phase splitter is included to obtain two 180° out of phase outputs for use in multiple transistor inverter systems. It consists of a toggle flip-flop whose clock signal is derived by "ANDing" the output of the PWM comparator and a signal from the ramp generator section. This "AND" gate ensures that the outputs truly alternate under control loop transient conditions. Better understanding of this feature and MC3420 operation may be gained by studying the circuit waveforms, shown in Figure 4.

FIGURE 4 - INTERNAL WAVEFORMS

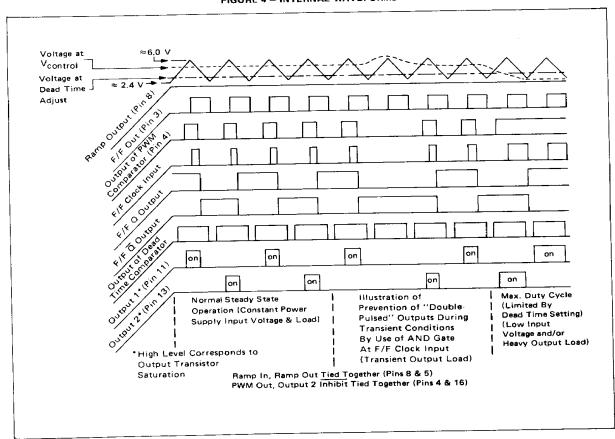

FIGURE 5 - STANDARD AC, DC TEST CIRCUIT

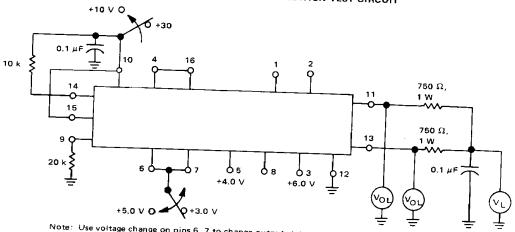

FIGURE 6 - FREQUENCY LIMIT TEST CIRCUIT

FIGURE 7 - OUTPUT SATURATION TEST CIRCUIT

Note: Use voltage change on pins 6, 7 to change output states.

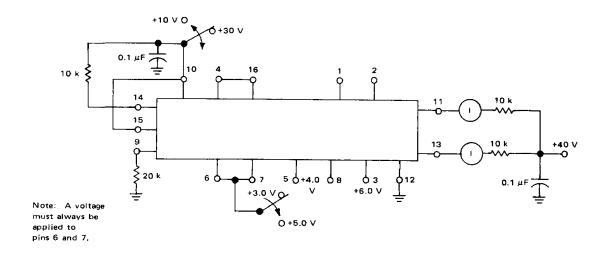

A voltage must always be present on pins 6 and 7.

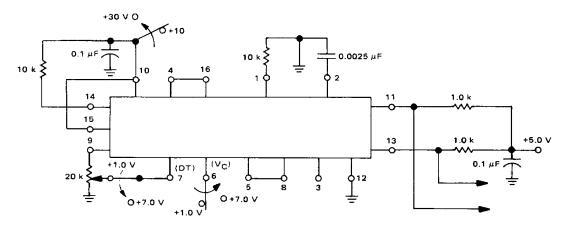

## FIGURE 8 - OUTPUT LEAKAGE TEST CIRCUIT

FIGURE 9 - OUTPUT DUTY CYCLE TEST CIRCUIT

| TYPICAL DUT                    | Y CYCLE   | TYPICAL DUTY CYCLE            |           |  |  |  |

|--------------------------------|-----------|-------------------------------|-----------|--|--|--|

| versus DEAD TIM                | E VOLTAGE | versus PWM VOLTAGE (Vcontrol) |           |  |  |  |

| PIN 7.                         | % DUTY    | PIN 6.                        | % DUTY    |  |  |  |

| DEAD TIME                      | CYCLE     | V <sub>control</sub> (V)      | CYCLE     |  |  |  |

| VOLTAGE (V)                    | (FOR EACH | (DEAD TIME                    | (FOR EACH |  |  |  |

| (V <sub>control</sub> = 2.0 V) | OUTPUT)   | VOLTAGE = 1.0 V)              | OUTPUT)   |  |  |  |

| 2.0                            | 50        | 2.0                           | 50        |  |  |  |

| 2.5                            | 46        | 2.5                           | 46        |  |  |  |

| 3.0                            | 40        | 3.0                           | 40        |  |  |  |

| 3.5                            | 33        | 3.5                           | 33        |  |  |  |

| 4.0                            | 26        | 4.0                           | 26        |  |  |  |

| 4.5                            | 18        | 4.5                           | 18        |  |  |  |

| 5.0                            | 11        | 5.0                           | 11        |  |  |  |

| 5.5                            | 4.0       | 5.5                           | 4.0       |  |  |  |

| 6.0                            | 0         | 6.0                           | 0         |  |  |  |

|                                |           |                               |           |  |  |  |

|             | ٧ <sub>6</sub> | ٧7  |                               |

|-------------|----------------|-----|-------------------------------|

|             | Vo             | lts |                               |

| 100% Adjust |                |     |                               |

| Dead Time   | 1.0            | 1.0 |                               |

| Pulse Width | 1.0            | 1.0 | (Pin 11 + Pin 13 = Logic "1") |

| 0% Adjust   |                |     |                               |

| Dead Time   | 7.0            | 1.0 |                               |

| Pulse Width | 1.0            | 7.0 | (Pin 11)(Pin 13) = Logic "1"  |

NOTE: Logic "1" is TTL-Compatible VOH.

FIGURE 10 - INHIBIT/SYMMETRY TEST CIRCUIT

FIGURE 11 - OSCILLATOR OUTPUT (pin 14) TEST CIRCUIT

FIGURE 12 - VControl BIAS CURRENT TEST CIRCUIT

FIGURE 13 - DEAD TIME BIAS CURRENT TEST CIRCUIT

FIGURE 14 - RAMP IN BIAS CURRENT TEST CIRCUIT

FIGURE 15 - AC TEST CIRCUIT AND WAVEFORMS

## TYPICAL CHARACTERISTICS

#### **OPERATION AND APPLICATIONS INFORMATION**

#### The Voltage Reference

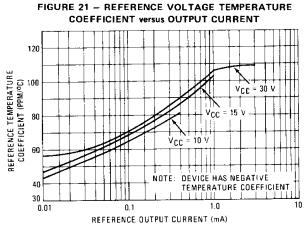

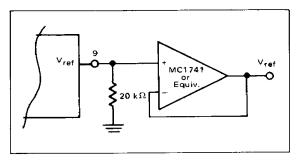

The temperature coefficient of  $V_{ref}$  has been optimized for a 400  $\mu$ A ( $\cong$ 20 k $\Omega$ ) load. If increased current capability is required, an op amp buffer may be used, as shown in Figure 22.

FIGURE 22

#### **Output Frequency**

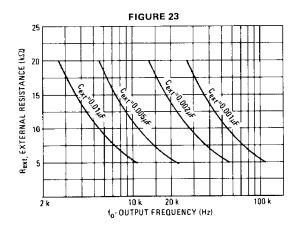

The values of  $R_{ext}$  and  $C_{ext}$  for a given output frequency,  $f_0$ , can be found from:

$$f_0 \cong \frac{0.55}{R_{ext} C_{ext}}$$

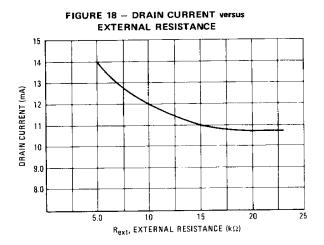

;  $5.0 \text{ k}\Omega \leqslant R_{ext} \leqslant 20 \text{ k}\Omega \text{ (Eq. 1)}$

or from the graph shown in Figure 23.

Note that  $f_{\rm O}$  refers to the frequency of Output 1 (Pin 11) or Output 2 (Pin 13). The frequency of the ramp generator output waveform at Pin 8 will be twice  $f_{\rm O}$ .

#### **Dead Time**

Figure 24 illustrates how to set or adjust the MC3420 outputs' dead time or maximum duty cycle. For minimum dead time drift with temperature or supply voltage,  $V_{D,T}$  should be derived from  $V_{ref}$  as shown.

Pin 7 should always be tied to some voltage between Gnd and  $\ensuremath{V_{ref}}.$

FIGURE 24

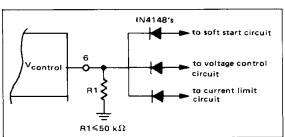

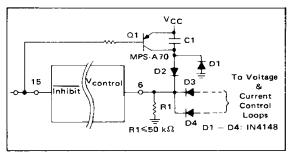

## Connections to the V<sub>control</sub> Pin

In many systems, it is necessary to make multiple connections to the  $V_{control}$  Pin in order to implement features in addition to voltage regulation such as current limiting, soft start, etc. These can be made by the use of a simple "diode-OR" connection, as shown in Figure 25. This allows whichever control element is seeking the lowest PWM duty cycle to dominate. Note that a resistor, R1, whose value is  $\leqslant 50~\mathrm{k}\Omega$  is placed from the  $V_{control}$  Pin to ground. This is necessary to provide a dc path for the PWM comparator input bias current under all conditions.

The system duty cycle is given by:

D.C. (%)

$$\approx \frac{V_{Control} - 2}{4} \times 100$$

(Eq. 2)

FIGURE 25

#### Soft Start

In most PWM switching supplies, a soft start feature is desired to prevent output voltage overshoots and magnetizing current imbalances in the power transformer primary. This feature forces the duty cycle of the switching elements to gradually increase from zero to their normal operating point during initial system power-up or after an inhibit. This feature can be easily implemented with the MC3420. One method is shown in Figure 26.

FIGURE 26

After an inhibit command or during power-up, the voltage on R1 and Pin 6 exponentially decays from  $V_{CC}$  toward ground with a time constant of R1C1, allowing a gradual increase in duty cycle. Diodes D2-D4 provide a diode-or function at the  $V_{COntrol}$  Pin, while Q1 serves to reset the timing capacitor, C1, when an inhibit command is received thereby reinitializing the soft-start feature. D1 allows C1 to reset when power ( $V_{CC}$ ) is turned off,

#### Inrush Current Limiting

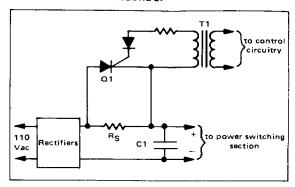

Since many PWM switching supplies are operated directly off the rectified 110 Vac line with capacitive input filters, some means of preventing rectifier failure due to inrush surge currents is usually necessary. One method which can be used is shown in Figure 27.

In this circuit, a series resistor, Rg, is used to provide inrush surge current limiting. After the filter capacitor, C1, is charged, Q1 receives a trigger signal from the control circuitry through T1 and shorts Rg out of the circuit, eliminating its otherwise larger power dissipation. The trigger signal for Q1 may be derived from either the oscillator output (Pin 14) or one of the MC3420's outputs. If the oscillator output is used, it will be necessary

FIGURE 27

to provide a time delay on the inhibit pin to keep it low until the input filter capacitor, C1, has had time to charge, whereas the initial portion of the soft start timing cycle can be used for this delay if this signal is derived from one of the output pins. However, using the Oscillator Output Pin does offer the advantage that its waveform has a constant 50% duty cycle, independent of the outputs' duty cycle which can simplify the design of a drive circuit for T1.

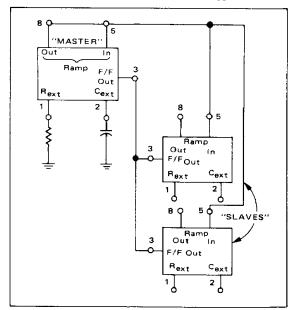

#### Slaving

In some applications, as when one PWM inverter/converter is used to feed another, it may be desired that their frequencies be synchronized. This can be done with multiple MC3420s as shown in Figure 28. By omitting their  $R_{\text{ext}}$  and  $C_{\text{ext}}$ , up to two MC3420s may be slaved to a master MC3420.

FIGURE 28 - SLAVING THE MC3420

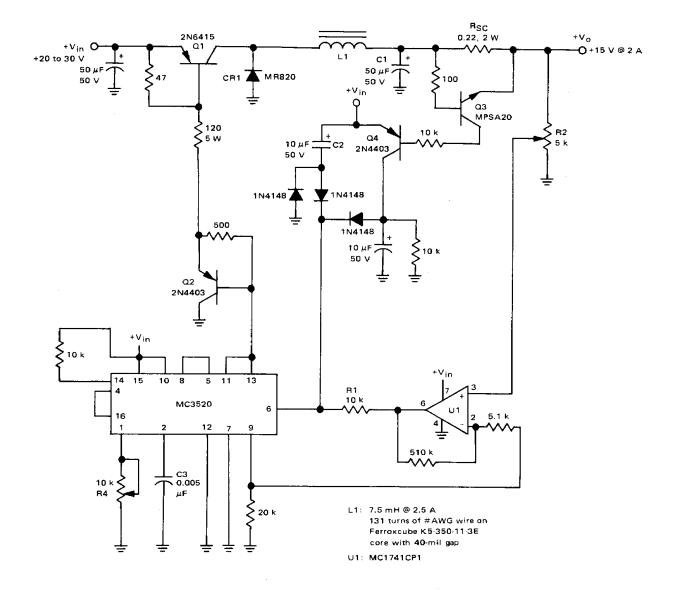

## 15 V, 2 A DC-to-DC Converter

Figure 29 illustrates the use of the MC3520 in a PWM switching power supply utilizing a single series switching element (see Appendix for description of PWM switching supply configurations). The series switching transistor, Q1, chops the dc input voltage,  $V_{in}$ , at a frequency of  $\cong$  25 kHz, and the resulting waveform is filtered by L1 and C1 to provide the dc output voltage. The frequency is set by R4 and C3, and since the outputs of the MC3520 are wire-ORed together, fo is twice that given by Equation 1 and Figure 23.  $V_{o}$  is regulated by comparing its value to the MC3520's reference voltage and amplifying the error voltage with U1. The output of U1 is fed into the MC3520 to provide PWM to Q1, thereby controlling its duty cycle and thus the value of  $V_{o}$ .

C2 provides a soft-start feature during power up to prevent output voltage overshoots and excessive start up currents through Q1.

Short circuit protection is provided by  $R_{SC}$ , Q3 and Q4. When an overcurrent condition occurs, Q3 is turned on by the voltage across  $R_{SC}$ ; Q3 drives Q4 on, which raises the voltage at pin 6 ( $V_{control}$ ) of the MC3520, reducing Q1's duty cycle and maintaining a constant output current of  $\cong$  2.5 A.

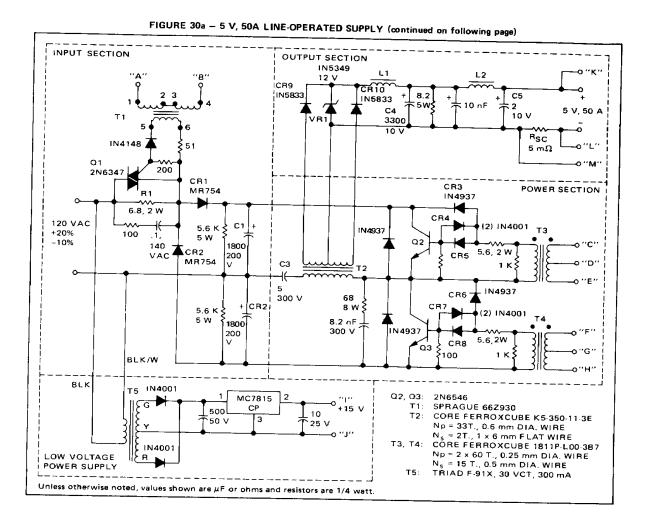

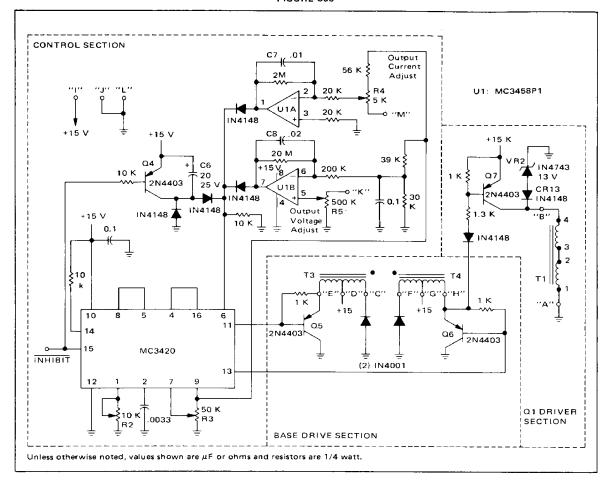

## 5 V, 50 A Line-Operated Supply

A 5 V, 50 A line-operated 20 kHz switching power supply using the MC3520 is shown in Figures 30a and b. An explanation of the operation of each section of the supply follows.

### Input Section

The 120 Vac line is full wave voltage doubled by CR1, CR2, C1 and C2 to provide 310 Vdc to the power section of the supply. Inrush surge current limiting is provided by R1, which is shorted out of the circuit by Q1 after C1 and C2 are initially charged.

#### **Power Section**

The supply utilizes two switching transistors, Q2 and Q3, in a half-bridge configuration (see Appendix) to drive the high frequency power transformer, T2.

The bases of  $\Omega 2$  and  $\Omega 3$  are driven by T3 and T4, respectively, to provide isolation from the control and base drive sections of the supply. CR3, CR5, CR6, and CR8 constitute anti-saturation (Baker) clamps which provide increased and more uniform switching speeds for

${\bf Q2}$  and  ${\bf Q3}$ . CR4 and CR7 allow reverse base currents during turn off.

#### **Output Section**

The output of T2 is rectified by Schottky diodes, CR9 and CR10. VR1 is a transient suppressor to protect CR9 and CR10 from transients that might cause reverse breakdown. L1 and C4 constitute the output filter. C4 should have very low ESR (equivalent series resistance) at 20 kHz to provide the most effective filtering. L2 and C5 make up a high-frequency filter to reduce commutation spikes which pass L1 due to its interwinding capacitance. RSC provides output overcurrent sensing to the control section.

#### **Control Section**

The MC3520 provides the PWM control for the supply. R2 is adjusted to obtain a 20 kHz operating frequency. R3 adjusts the dead time ( $\cong 5~\mu s$  each half-cycle). U1A and U1B are the output current and output voltage error amplifiers, respectively. R5 sets the output voltage while R4 determines the output current limit. C7 and C8 are the current and voltage loop compensation capacitors.

C6 provides the soft-start feature while Q4 ensures a soft-start after each system inhibit (pin 15 low).

#### **Base Drive Section**

Turn on drive to the power section switching transistors occurs when each of the outputs of the MC3520 saturate. Q5 or Q6 are therefore turned on, and 15 V applied to the primaries of T3 or T4, supplying forward base drive to Q2 or Q3.

Turn off drive occurs when Q5 or Q6 turn off, and the magnetizing energy stored in T3 or T4's core is transformed into a negative "flyback" voltage at their secondaries, providing reverse base drive to Q2 or Q3. CR11 and CR12 act as clamps, to prevent this flyback voltage from exceeding -5 V at T3 or T4's secondary (30 V on Q5 or Q6's collector).

#### Q1 Driver Section

$\Omega$ 7 and T1 provide the gate drive to  $\Omega$ 1.  $\Omega$ 7 starts operating after an initial delay of 100 ms created by the soft-start circuit, thereby allowing C1 and C2 to charge up before firing  $\Omega$ 1.

FIGURE 29 - 15 V, 2A DC-TO-DC CONVERTER

| Performance                    |           |  |  |  |

|--------------------------------|-----------|--|--|--|

| Line Regulation:               | 0.4%      |  |  |  |

| Load Regulation:               | 0.25%     |  |  |  |

| Output Ripple and Noise:       | 60 mV p-p |  |  |  |

|                                | 25 mV rms |  |  |  |

| Line current surge at turn-on: | 35 A max  |  |  |  |

| Efficiency:                    | 80%       |  |  |  |

#### FIGURE 30b

### APPENDIX: BASIC PWM SWITCHING SUPPLY POWER CIRCUIT CONFIGURATIONS

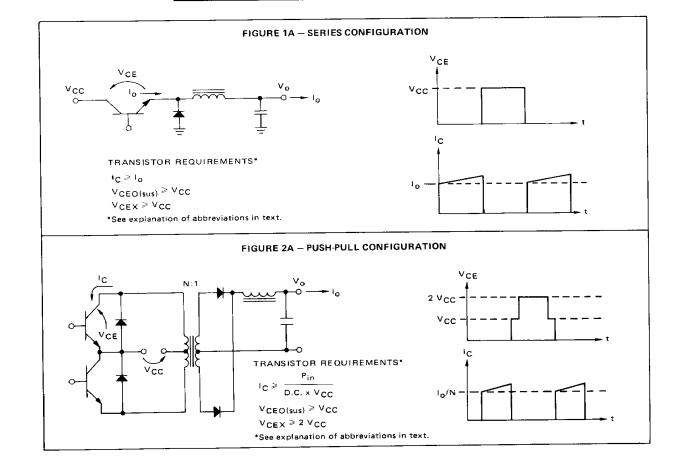

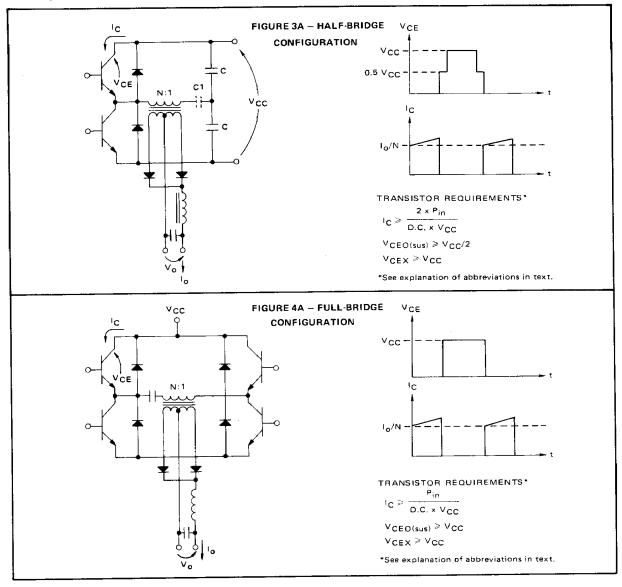

The material given in this section is intended to acquaint the designer with the basic switching transistor configurations used in PWM power supplies. Circuit configurations, collector voltage and current waveforms of the switching transistors, and required transistor specifications for the most commonly utilized configurations are shown in Figures 1A through 4A. It should be noted that the waveforms and specifications are idealized, in that the effects of leakage inductance voltage spikes, stray circuit capacitance, snubber networks, clamp diode overshoots, diode reverse recovery and saturation voltages have been neglected. For more information on these effects, the configurations, or switching supplies in general, consult the references listed in the References section.

### **Series Configuration**

The single transistor series configuration is shown in Figure 1A. This configuration is usually limited to applications in which 0.2  $\rm V_{CC} < \rm V_{o} < 0.8~\rm V_{CC}$  and where input-output isolation is not required.

#### **Push-Pull Configuration**

Figure 2A shows the two-transistor push-pull configuration. Unlike the series configuration, it can be used to either step-up or step-down the input voltage, V<sub>CC</sub>, and also provides input-output isolation. It does, however, have the disadvantage that additional circuitry must be used to provide symmetry correction for the prevention of transformer saturation.

#### Half-Bridge Configuration

The half-bridge configuration, shown in Figure 3A, does not suffer from the symmetry problems of the push-pull configuration since the transformer primary is capacitively coupled. This prevents transformer core saturation since no net dc current is allowed to flow in its primary.

Note that for the same input power, bus voltage, and duty cycle, the half-bridge requires switching transistors

which have twice the current and half the voltage requirements as those of the push-pull configuration.

### **Full-Bridge Configuration**

By replacing the bridge capacitors, C, of the halfbridge configuration of Figure 4A results. With this configuration, double the power of the half-bridge configuration can be obtained at the expense of two additional switching transistors and their associated circuitry.

## ABBREVIATIONS USED IN FIGURES 1A THROUGH 4A

I<sub>C</sub>: Switching transistor collector current

V<sub>CE</sub>: Switching transistor collector-to-emitter-voltage

P<sub>in</sub>: Average input power

D.C.: Inverter duty cycle

VCC: DC bus voltage

V<sub>CC</sub>: DC bus voltage V<sub>CEO(sus)</sub>: V<sub>CE</sub> that transistor must withstand during

turn-on

V<sub>CEX</sub>: V<sub>CE</sub> that transistor must block during non-

conduction period.

#### REFERENCES

More detailed information on switching power supplies may be obtained by consulting the following articles:

- L. Jansson: "A Survey of Converter Circuits for SMPS," Mullard Technical Communications #119, July 1973.

- R. Haver: "A New Approach to Switching Regulators," Motorola AN-719, May 1974.

- R. Haver: "Switched Mode Power Supplies, a 5 V, 40 A Design," Motorola AN-737, December 1974.

- W. Hersom: "Optimizing the High Current Transistor Converter," Solid State Power Conversion, March/ April 1975.

- W. Hirshberg: "Simplify Converter Designs with Flyback," Solid State Power Conversion, March/April 1975.

- P. Wood: "Design of a 5 V, 100 Watt Power Supply, TRW AN #122, February 1975.

- 7. J. Turnbull: "Radio Frequency Interference Suppression in SMPS," Ferroxcube AN-F601.

- 8. W. Hetterscheid: "Base Circuit Design for High-Voltage Switching Transistors in Power Converters," Mullard Technical Communications (North American Phillips) #473, November 1974.

- B. George: "6 V 100 A Switched-Mode Power Supply Operating Directly from the Mains," Mullard Technical Communications (North American Phillips) #123, July 1974.

- B. Bailey: "Circuit Design and Semiconductor Selection for Square-Wave and Sine-Wave Inverters," Proc. of Powercon 2, October 1975.

- 11. B. Bailey: "Safe Reverse Bias Operation—A New Approach," *Proc. of Powercon 3*, June 1976.

- Gutmann and Suva: "A Line-Operated, Regulated 5 V/50 A Switching Power Supply," Motorola AN-767, September 1976.