125 MHz Single Supply, Clamping Op Amps

#### **Features**

- Specified for +3V, +5V, or ± 5V Applications

- Power Down to 0 μA

- Output Voltage Clamp

- Output Swings to Ground Without Saturating

- -3 dB Bandwidth = 125 MHz

- $\pm$  0.1 dB Bandwidth = 30 MHz

- Low Supply Current = 5 mA

- Slew Rate =  $275 \text{ V/}\mu\text{s}$

- Low Offset Voltage = 4 mV max

- Output Current =  $\pm 100 \text{ mA}$

- High Open Loop Gain = 80 dB

- Differential Gain = 0.05%

- Differential Phase =  $0.05^{\circ}$

### **Applications**

- Video Amplifier

- PCMCIA Applications

- A/D Driver

- Line Driver

- Portable Computers

- High Speed Communications

- RGB Printer, FAX, Scanner Applications

- Broadcast Equipment

- Active Filtering

- Multiplexing

## **Ordering Information**

| Part No. | Temp. Range    | Package     | Outline # |

|----------|----------------|-------------|-----------|

| EL2257CN | -40°C to +85°C | 14 Pin PDIP | MDP0031   |

| EL2257CS | -40°C to +85°C | 14 Pin SOIC | MDP0027   |

| EL2357CN | -40°C to +85°C | 16 Pin PDIP | MDP0031   |

| EL2357CS | -40°C to +85°C | 16 Pin SOIC | MDP0027   |

## **General Description**

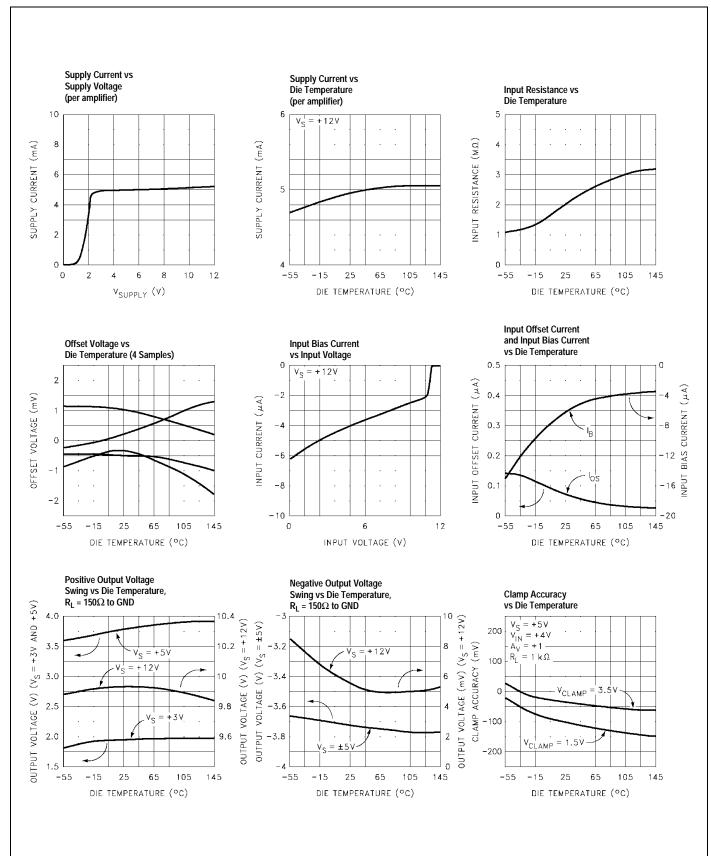

The EL2257C/EL2357C are supply op amps. Prior single supply op amps have generally been limited to bandwidths and slew rates 1/4 that of the EL2257C/EL2357C. The 125 MHz bandwidth, 275 V/µs slew rate, and  $0.05\%/0.05^{\circ}$  differential gain/differential phase makes this part ideal for single or dual supply video speed applications. With its voltage feedback architecture, this amplifier can accept reactive feedback networks, allowing them to be used in analog filtering applications. The inputs can sense signals below the bottom supply rail and as high as 1.2V below the top rail. Connecting the load resistor to ground and operating from a single supply, the outputs swing completely to ground without saturating. The outputs can also drive to within 1.2V of the top rail. The EL2257C/EL2357C will output  $\pm 100$  mA and will operate with single supply voltages as low as 2.7V, making them ideal for portable, low power applications.

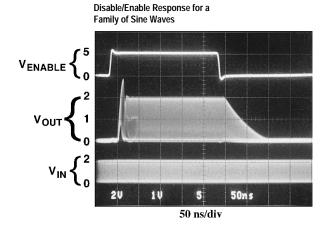

The EL2257C/EL2357C have a high speed disable feature. Applying a low logic level to all ENABLE pins reduces the supply current to 0  $\mu$ A within 50 ns. Each amplifier has its own ENABLE pin. This is useful for both multiplexing and reducing power consumption.

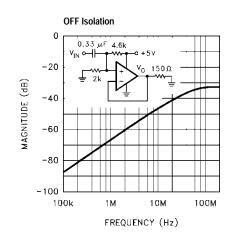

The EL2257C/EL2357C also have an output voltage clamp feature. This clamp is a fast recovery (<7 ns) output clamp that prevents the output voltage from going above the preset clamp voltage. This feature is desirable for A/D applications, as A/D converters can require long times to recover if overdriven.

The EL2257C/EL2357C are available in plastic DIP and SOIC packages. Both parts operate over the industrial temperature range of -40°C to +85°C. For single amplifier applications, see the EL2150C/EL2157C. For space saving, industry standard pin out dual and quad applications, see the EL2250C/EL2450C.

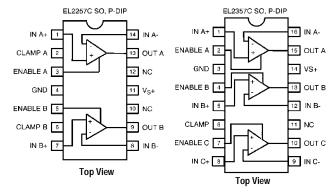

### **Connection Diagrams**

© 1995 Elantec, Inc.

### 125 MHz Single Supply, Clamping Op Amps

### Absolute Maximum Ratings (T<sub>A</sub> = 25 °C)

Supply Voltage between  $\boldsymbol{V}_{\boldsymbol{S}}$  and GND 12.6V Power Dissipation See Curves Input Voltage (IN+, IN-, ENABLE, CLAMP) -65°C to +150°C GND-0.3V,  $V_S+0.3V$ Storage Temperature Range Differential Input Voltage Ambient Operating Temperature Range -40°C to +85°C  $\pm 6V$ Maximum Output Current 90 mA Operating Junction Temperature 150°C

Output Short Circuit Duration (see note [1] DC Electrical Characteristics)

#### **Important Note:**

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefor  $T_1 = T_C = T_A$ .

Series system. Unless otherwise noted, all tests are pulsed tests, therefor  $T_J = T_C = T_A$ .

Test Level Test Procedure

I 100% production tested and QA sample tested per QA test plan QCX0002.

II 100% production tested at  $T_A = 25$ °C and QA sample tested at  $T_A = 25$ °C,  $T_{MAX}$  and  $T_{MIN}$  per QA test plan QCX0002.

III QA sample tested per QA test plan QCX0002.IV Parameter is guaranteed (but not tested) by Design and Characterization Data.

V Parameter is typical value at  $T_A = 25^{\circ}C$  for information purposes only.

#### **DC Electrical Characteristics**

$V_S \!\!=\!\! +5V, GND \!\!=\!\! 0V, T_A \!\!=\!\! 25^{\circ}C, V_{CM} \!\!=\!\! 1.5V, V_{OUT} \!\!=\!\! 1.5V, V_{CLAMP} \!\!=\!\! +5V, V_{ENABLE} \!\!=\!\! +5V, unless otherwise specified.$

| D                  | Description                                | Total Com Nations                                                                      | M2    | Т    | M                   | Test  | TI!4- |

|--------------------|--------------------------------------------|----------------------------------------------------------------------------------------|-------|------|---------------------|-------|-------|

| Parameter          | Description                                | Test Conditions                                                                        | Min   | Тур  | Max                 | Level | Units |

| $V_{OS}$           | Offset Voltage                             | EL2257C                                                                                | -4    |      | 4                   | I     | mV    |

|                    |                                            | EL2357C                                                                                | -6    |      | 6                   | I     | mV    |

| TCV <sub>OS</sub>  | Offset Voltage Temperature Coefficient     | Measured from Tmin to Tmax                                                             |       | 10   |                     | V     | μV/°C |

| IB                 | Input Bias Current                         | V <sub>IN</sub> =0V                                                                    |       | -5.5 | -10                 | I     | μΑ    |

| I <sub>OS</sub>    | Input Offset Current                       | V <sub>IN</sub> =0V                                                                    | -1100 | 150  | +1100               | I     | nA    |

| TCI <sub>OS</sub>  | Input Bias Current Temperature Coefficient | Measured from Tmin to Tmax                                                             |       | 50   |                     | V     | nA/°C |

| PSRR               | Power Supply Rejection Ratio               | V <sub>S</sub> =V <sub>ENABLE</sub> =+2.7V to +12V,<br>V <sub>CLAMP</sub> =OPEN        | 45    | 70   |                     | I     | dB    |

| CMRR               | Common Mode Rejection Ratio                | VCM=0V to +3.8V                                                                        | 50    | 65   |                     | I     | dB    |

|                    |                                            | VCM=0V to +3.0V                                                                        | 55    | 70   |                     | I     | dB    |

| CMIR               | Common Mode Input Range                    |                                                                                        | 0     |      | V <sub>S</sub> -1.2 | I     | V     |

| R <sub>IN</sub>    | Input Resistance                           | Common Mode                                                                            | 1     | 2    |                     | I     | ΜΩ    |

| C <sub>IN</sub>    | Input Capacitance                          | SOIC Package                                                                           |       | 1    |                     | V     | pF    |

|                    |                                            | PDIP Package                                                                           |       | 1.5  |                     | V     | pF    |

| R <sub>OUT</sub>   | Output Resistance                          | Av=+1                                                                                  |       | 40   |                     | V     | mΩ    |

| I <sub>S,ON</sub>  | Supply Current - Enabled (per amplifier)   | $V_S=V_{CLAMP}=+12V, V_{ENABLE}=+12V$                                                  |       | 5    | 6.5                 | I     | mA    |

| I <sub>S,OFF</sub> | Supply Current - Shut Down (per amplifier) | $V_S = V_{CLAMP} = +10V, V_{ENABLE} = +0.5V$                                           |       | 0    | 50                  | I     | μΑ    |

|                    |                                            | $V_S = V_{CLAMP} = +12V, V_{ENABLE} = +0.5V$                                           |       | 5    |                     | V     | μΑ    |

| PSOR               | Power Supply Operating Range               |                                                                                        | 2.7   |      | 12.0                | I     | V     |

| AVOL               | Open Loop Gain                             | $V_S = V_{CLAMP} = +12V$ , $V_{OUT} = +2V$ to $+9V$ , $R_L = 1 \text{ k}\Omega$ to GND | 65    | 80   |                     | I     | dB    |

|                    |                                            | $V_{OUT}$ =+1.5V to +3.5V, $R_L$ =1 k $\Omega$ to GND                                  |       | 70   |                     | V     | dB    |

|                    |                                            | $V_{OUT}$ =+1.5V to +3.5V, $R_L$ =150 $\Omega$ to GND                                  |       | 60   |                     | V     | dB    |

125 MHz Single Supply, Clamping Op Amps

## **DC Electrical Characteristics (Continued)**

$V_S \!\!=\!\! +5V, GND \!\!=\!\! 0V, T_A \!\!=\!\! 25^\circ C, V_{CM} \!\!=\!\! 1.5V, V_{OUT} \!\!=\!\! 1.5V, V_{CLAMP} \!\!=\!\! +5V, V_{ENABLE} \!\!=\!\! +5V, unless otherwise specified.$

|                      |                                                  |                                                   |      |      |                 | Test  |       |

|----------------------|--------------------------------------------------|---------------------------------------------------|------|------|-----------------|-------|-------|

| Parameter            | Description                                      | Test Conditions                                   | Min  | Typ  | Max             | Level | Units |

| $V_{\mathrm{OP}}$    | Positive Output Voltage Swing                    | $V_S$ =+12V, $A_V$ =+1, $R_L$ =1 k $\Omega$ to 0V |      | 10.8 |                 | V     | V     |

|                      |                                                  | $V_S$ =+12V, $A_V$ =+1, $R_L$ =150 $\Omega$ to 0V | 9.6  | 10.0 |                 | I     | V     |

|                      |                                                  | $V_S$ =±5V, $A_V$ =+1, $R_L$ =1 $k\Omega$ to $0V$ |      | 4.0  |                 | V     | V     |

|                      |                                                  | $V_S$ =±5V, $A_V$ =+1, $R_L$ =150 $\Omega$ to 0V  | 3.4  | 3.8  |                 | I     | V     |

|                      |                                                  | $V_S$ =+3V, $A_V$ =+1, $R_L$ =150 $\Omega$ to 0V  | 1.8  | 1.95 |                 | I     | V     |

| V <sub>ON</sub>      | Negative Output Voltage Swing                    | $V_S$ =+12V, $A_V$ =+1, $R_L$ =150 $\Omega$ to 0V |      | 5.5  | 8               | I     | mV    |

|                      |                                                  | $V_S$ =±5V, $A_V$ =+1, $R_L$ =1 k $\Omega$ to 0V  |      | -4.0 |                 | V     | V     |

|                      |                                                  | $V_S$ =±5V, $A_V$ =+1, $R_L$ =150 $\Omega$ to 0V  |      | -3.7 | -3.4            | I     | V     |

| I <sub>OUT</sub>     | Output Current [1]                               | $V_S=\pm 5V$ , $A_V=+1$ , $R_L=10\Omega$ to $0V$  | ±75  | ±100 |                 | I     | mA    |

|                      |                                                  | $V_S=\pm 5V$ , $A_V=+1$ , $R_L=50\Omega$ to $0V$  |      | ±60  |                 | V     | mA    |

| I <sub>OUT,OFF</sub> | Output Current, Disabled                         | V <sub>ENABLE</sub> =+0.5V                        |      | 0    | 20              | I     | μΑ    |

| V <sub>IH-EN</sub>   | ENABLE pin Voltage for Power Up                  | Relative to GND Pin                               | 2.0  |      |                 | I     | V     |

| V <sub>IL-EN</sub>   | ENABLE pin Voltage for Shut Down                 | Relative to GND Pin                               |      |      | 0.5             | I     | V     |

| I <sub>IH-EN</sub>   | ENABLE pin Input Current-High [2]                | $V_S = V_{CLAMP} = +12V, V_{ENABLE} = +12V$       |      | 340  | 410             | I     | μΑ    |

| I <sub>IL-EN</sub>   | ENABLE pin Input Current-Low [2]                 | $V_S = V_{CLAMP} = +12V, V_{ENABLE} = +0.5V$      |      | 0    | 1               | I     | μΑ    |

| V <sub>OR-CL</sub>   | Voltage Clamp Operating Range [3]                | Relative to GND Pin                               | 1.2  |      | V <sub>OP</sub> | I     | V     |

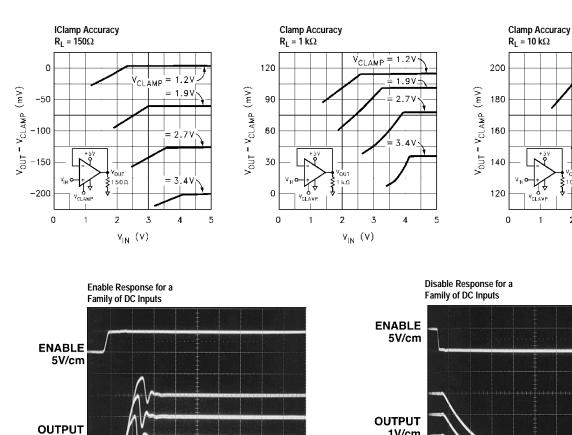

| V <sub>ACC-CL</sub>  | CLAMP Accuracy [4]                               | $V_{IN}$ =+4V, $R_L$ =1 k $\Omega$ to GND         | -250 | 100  | 250             | I     | mV    |

|                      |                                                  | V <sub>CLAMP</sub> =+1.5V and +3.5V               |      |      |                 |       |       |

| I <sub>IH-CL</sub>   | CLAMP pin Input Current - High                   | $V_S = V_{CLAMP} = +12V$                          |      | 12   | 25              | I     | μΑ    |

| I <sub>IL-CL</sub>   | CLAMP pin Input Current - Low / Per<br>Amplifier | V <sub>S</sub> =+12V, V <sub>CLAMP</sub> =+1.2V   | -30  | -15  |                 | I     | μΑ    |

- 1. Internal short circuit protection circuitry has been built into the EL2257C/EL2357C. See the Applications section.

- 2. If the disable feature is not desired, tie the ENABLE pins to the  $V_S$  pin, or apply a logic high level to the ENABLE pins.

- 3. The maximum output voltage that can be clamped is limited to the maximum positive output Voltage, or  $V_{OP}$ . Applying a Voltage higher than  $V_{OP}$  inactivates the clamp. If the clamp feature is not desired, either tie the CLAMP pin to the  $V_S$  pin, or simply let the CLAMP pin float.

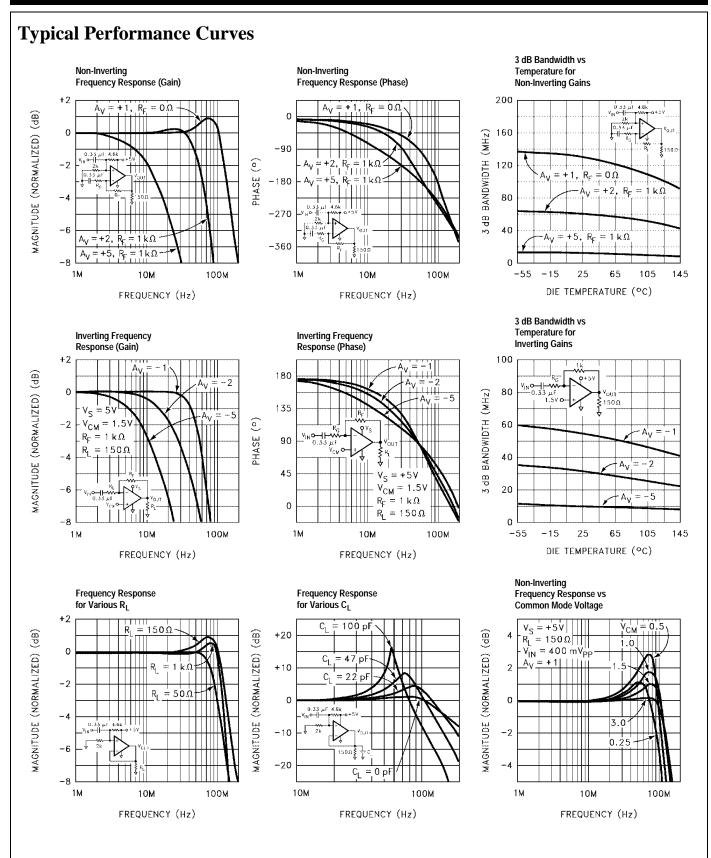

- $4. \quad \text{The clamp accuracy is affected by $V_{IN}$ and $R_L$. See the Typical Curves Section and the Clamp Accuracy vs. $V_{IN}$ and $R_L$ curve.} \\$

125 MHz Single Supply, Clamping Op Amps

## **Closed Loop AC Electrical Characteristics**

$V_S = +5V, GND = 0V, T_A = 25^{\circ}C, V_{CM} = +1.5V, V_{OUT} = +1.5V, V_{CLAMP} = +5V, V_{ENABLE} = +5V, A_V = +1, RF = 0\Omega, RL = 150\Omega \text{ to GND pin, unless otherwise specified}^{[1]}$

| Parameter        | Description                        | Test Conditions                                             | Min | Тур  | Max | Test<br>Level | Units      |

|------------------|------------------------------------|-------------------------------------------------------------|-----|------|-----|---------------|------------|

| BW               | -3 dB Bandwidth (Vout=400 mVp-p)   | $V_S = +5V, A_V = +1, R_F = 0\Omega$                        |     | 125  |     | V             | MHz        |

|                  |                                    | $V_S=+5V, A_V=-1, R_F=500\Omega$                            |     | 60   |     | V             | MHz        |

|                  |                                    | $V_S = +5V$ , $A_V = +2$ , $R_F = 500\Omega$                |     | 60   |     | V             | MHz        |

|                  |                                    | $V_S=+5V$ , $A_V=+10$ , $R_F=500\Omega$                     |     | 6    |     | V             | MHz        |

|                  |                                    | $V_S = +12V, A_V = +1, R_F = 0\Omega$                       |     | 150  |     | V             | MHz        |

|                  |                                    | $V_S = +3V, A_V = +1, R_F = 0\Omega$                        |     | 100  |     | V             | MHz        |

| BW               | ±0.1 dB Bandwidth (Vout=400 mVp-p) | $V_S = +12V, A_V = +1, R_F = 0\Omega$                       |     | 25   |     | V             | MHz        |

|                  |                                    | $V_S = +5V, A_V = +1, R_F = 0\Omega$                        |     | 30   |     | V             | MHz        |

|                  |                                    | $V_S = +3V, A_V = +1, R_F = 0\Omega$                        |     | 20   |     | V             | MHz        |

| GBWP             | Gain Bandwidth Product             | V <sub>S</sub> =+12V, @ A <sub>V</sub> =+10                 |     | 60   |     | V             | MHz        |

| PM               | Phase Margin                       | $R_L$ =1 kΩ, CL=6 pF                                        |     | 55   |     | V             | 0          |

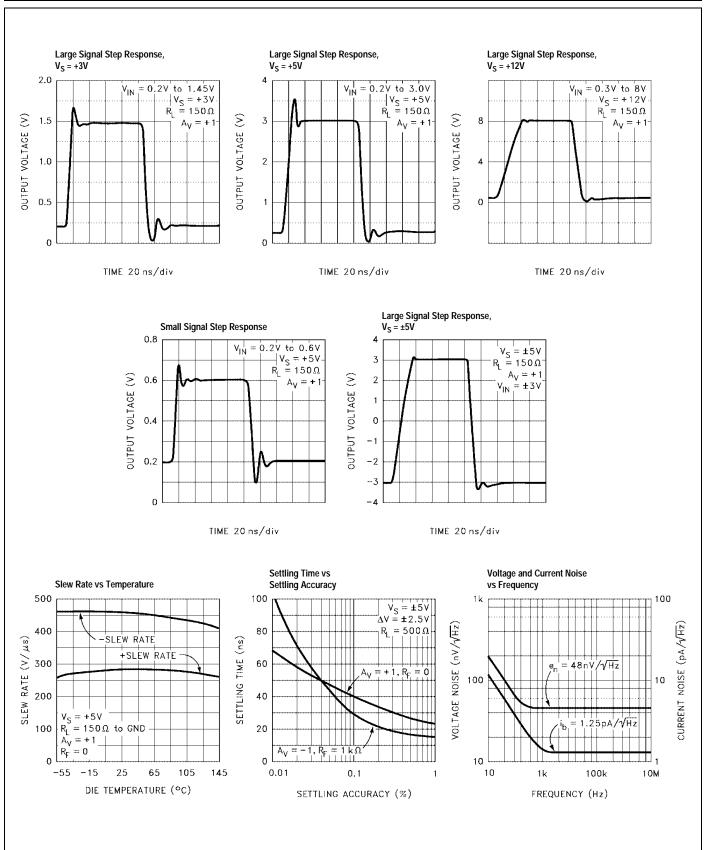

| SR               | Slew Rate                          | $V_S$ =+10V, $R_L$ =150 $\Omega$ , Vout=0V to +6V           | 200 | 275  |     | I             | V/µs       |

|                  |                                    | $V_S$ =+5V, $R_L$ =150 $\Omega$ , Vout=0V to +3V            |     | 300  |     | V             | V/µs       |

| $t_R, t_F$       | Rise Time, Fall Time               | ±0.1V Step                                                  |     | 2.8  |     | V             | ns         |

| OS               | Overshoot                          | ±0.1V Step                                                  |     | 10   |     | V             | %          |

| t <sub>PD</sub>  | Propagation Delay                  | ±0.1V step                                                  |     | 3.2  |     | V             | ns         |

| t <sub>S</sub>   | 0.1% Settling Time                 | $V_S = \pm 5V, R_L = 500\Omega, A_V = +1, V_{OUT} = \pm 3V$ |     | 40   |     | V             | ns         |

|                  | 0.01% Settling Time                | $V_S = \pm 5V, R_L = 500\Omega, A_V = +1, V_{OUT} = \pm 3V$ |     | 75   |     | V             | ns         |

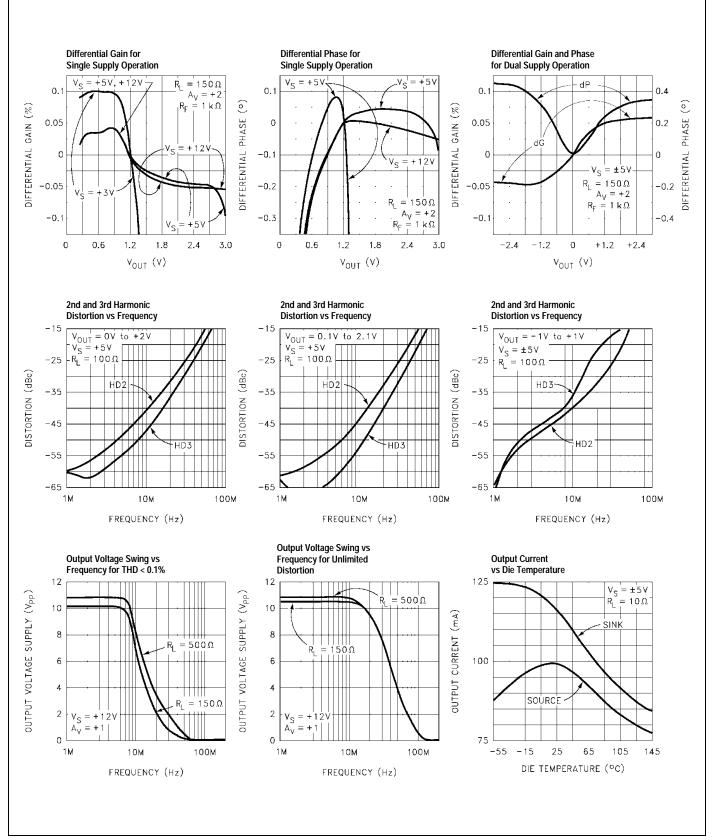

| dG               | Differential Gain [2]              | $A_V=+2$ , $R_F=1$ k $\Omega$                               |     | 0.05 |     | V             | %          |

| dP               | Differential Phase [2]             | $A_V=+2$ , $R_F=1$ k $\Omega$                               |     | 0.05 |     | V             | 0          |

| e <sub>N</sub>   | Input Noise Voltage                | f=10 kHz                                                    |     | 48   |     | V             | nV/ĐH<br>z |

| i <sub>N</sub>   | Input Noise Current                | f=10 kHz                                                    |     | 1.25 |     | V             | pA/ĐH<br>z |

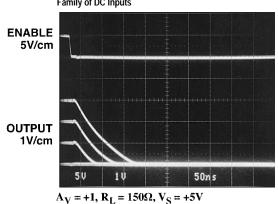

| t <sub>DIS</sub> | Disable Time [3]                   |                                                             |     | 50   |     | V             | ns         |

| t <sub>EN</sub>  | Enable Time [3]                    |                                                             |     | 25   |     | V             | ns         |

| $t_{\rm CL}$     | Clamp Overload Recovery            |                                                             |     | 7    |     | V             | ns         |

- 1. All AC tests are performed on a "warmed up" part, except slew rate, which is pulse tested.

- 2. Standard NTSC signal = 286 mVp-p, f=3.58 MHz, as  $V_{IN}$  is swept from 0.6V to 1.314V.  $R_L$  is DC coupled.

- 3. Disable/Enable time is defined as the time from when the logic signal is applied to the ENABLE pin to when the supply current has reached half its final value.

## 125 MHz Single Supply, Clamping Op Amps

= 1.2

= 1.9

= 2.7 V

$V_{|N|}(v)$

5

10

$A_V = +1, R_L = 150\Omega, V_S = +5V$

20ns

1V/cm

125 MHz Single Supply, Clamping Op Amps

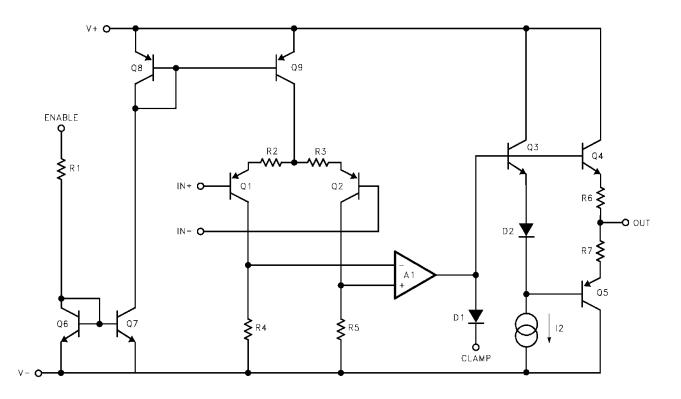

# **Simplified Schematic (One Channel)**

125 MHz Single Supply, Clamping Op Amps

## **Applications Information**

#### **Product Description**

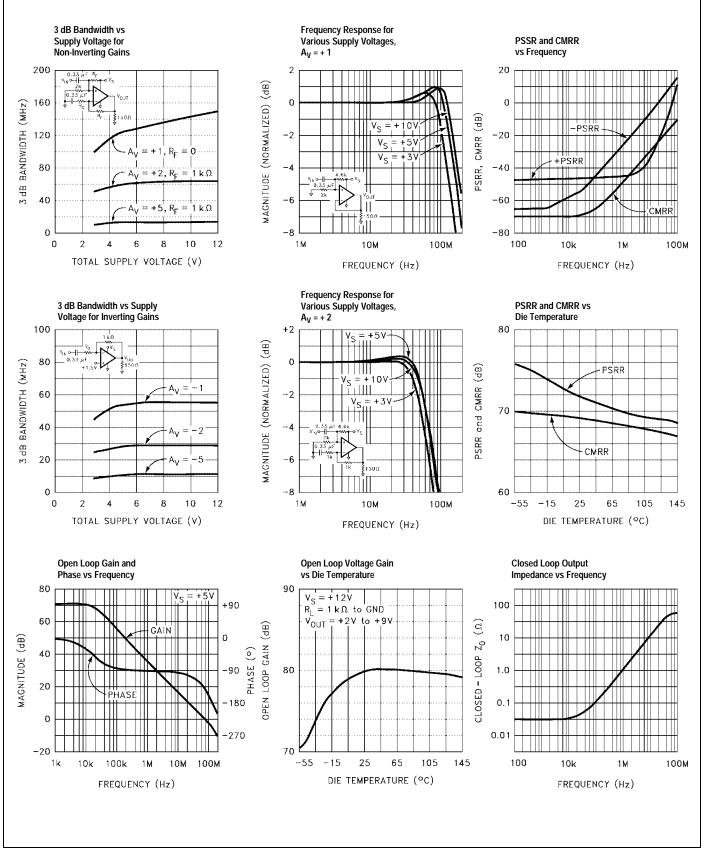

The EL2257C/EL2357C's, connected in voltage follower mode, -3 dB bandwidth is 125 MHz while maintaining a 275 V/µs slew rate. With an input and output common mode range that includes ground, these amplifiers were optimized for single supply operation, but will also accept dual supplies. They operate on a total supply voltage range as low as +2.7V or up to +12V. This makes them ideal for +3V applications, especially portable computers.

While many amplifiers claim to operate on a single supply, and some can sense ground at their inputs, most fail to truly drive their outputs to ground. If they do succeed in driving to ground, the amplifier often saturates, causing distortion and recovery delays. However, special circuitry built into the EL2257C/EL2357C allows the output to follow the input signal to ground without recovery delays.

#### Power Supply Bypassing And Printed Circuit Board Layout

As with any high-frequency device, good printed circuit board layout is necessary for optimum performance. Ground plane construction is highly recommended. Lead lengths should be as short as possible. The power supply pins must be well bypassed to reduce the risk of oscillation. The combination of a 4.7  $\mu$ F tantalum capacitor in parallel with a 0.1  $\mu$ F ceramic capacitor has been shown to work well when placed at each supply pin. For single supply operation, where the GND pin is connected to the ground plane, a single 4.7  $\mu$ F tantalum capacitor in parallel with a 0.1  $\mu$ F ceramic capacitor from the  $V_{S+}$  pin to the GND pin will suffice.

For good AC performance, parasitic capacitance should be kept to a minimum. Ground plane construction should be used. Carbon or Metal-Film resistors are acceptable with the Metal-Film resistors giving slightly less peaking and bandwidth because of their additional series inductance. Use of sockets, particularly for the SO package should be avoided if possible. Sockets add parasitic inductance and capacitance which will result in some additional peaking and overshoot.

# **Supply Voltage Range and Single-Supply Operation**

The EL2257C/EL2357C have been designed to operate with supply voltages having a span of greater than 2.7V, and less than 12V. In practical terms, this means that the EL2257C/EL2357C will operate on dual supplies ranging from  $\pm 1.35$ V to  $\pm 6$ V. With a single-supply, the EL2257C/EL2357C will operate from  $\pm 2.7$ V to  $\pm 12$ V. Performance has been optimized for a single  $\pm 5$ V supply.

Pins 11 and 4 (14 and 3) are the power supply pins on the EL2257C (EL2357C). The positive power supply is connected to pin 11 (14). When used in single supply mode, pin 4 (3) is connected to ground. When used in dual supply mode, the negative power supply is connected to pin 4 (3).

As supply voltages continue to decrease, it becomes necessary to provide input and output voltage ranges that can get as close as possible to the supply voltages. The EL2257C/EL2357C have an input voltage range that includes the negative supply and extends to within 1.2V of the positive supply. So, for example, on a single +5V supply, the EL2257C/EL2357C have an input range which spans from 0V to 3.8V.

The output range of the EL2257C/EL2357C is also quite large. It includes the negative rail, and extends to within 1V of the top supply rail with a 1 k $\Omega$  load. On a +5V supply, the output is therefore capable of swinging from 0V to +4V. On split supplies, the output will swing  $\pm 4V$ . If the load resistor is tied to the negative rail and split supplies are used, the output range is extended to the negative rail.

#### Choice Of Feedback Resistor, R<sub>F</sub>

The feedback resistor forms a pole with the input capacitance. As this pole becomes larger, phase margin is reduced. This increases ringing in the time domain and peaking in the frequency domain. Therefore,  $R_F$  has some maximum value which should not be exceeded for optimum performance. If a large value of  $R_F$  must be used, a small capacitor in the few picofarad range in parallel with  $R_F$  can help to reduce this ringing and peaking at the expense of reducing the bandwidth.

125 MHz Single Supply, Clamping Op Amps

As far as the output stage of the amplifier is concerned,  $R_F + R_G$  appear in parallel with  $R_L$  for gains other than +1. As this combination gets smaller, the bandwidth falls off. Consequently,  $R_F$  has a minimum value that should not be exceeded for optimum performance.

For  $A_V=+1$ ,  $R_F=0\Omega$  is optimum. For  $A_V=-1$  or +2 (noise gain of 2), optimum response is obtained with  $R_F$  between  $500\Omega$  and 1 k $\Omega$ . For  $A_V=-4$  or +5 (noise gain of 5), keep  $R_F$  between 2 k $\Omega$  and 10 k $\Omega$ .

#### Video Performance

For good video performance, an amplifier is required to maintain the same output impedance and the same frequency response as DC levels are changed at the output. This can be difficult when driving a standard video load of  $150\Omega$ , because of the change in output current with DC level. Differential Gain and Differential Phase for the EL2257C/EL2357C are specified with the black level of the output video signal set to +1.2V. This allows ample room for the sync pulse even in a gain of +2 configuration. This results in dG and dP specifications of 0.05% and  $0.05^{\circ}$  while driving  $150\Omega$  at a gain of +2. Setting the black level to other values, although acceptable, will compromise peak performance. For example, looking at the single supply dG and dP curves for  $R_L=150\Omega$ , if the output black level clamp is reduced from 1.2V to 0.6V dG/dP will increase from  $0.05\%/0.05^{\circ}$  to  $0.08\%/0.25^{\circ}$ . Note that in a gain of +2 configuration, this is the lowest black level allowed such that the sync tip doesn't go below 0V.

If your application requires that the output goes to ground, then the output stage of the EL2257C/EL2357C, like all other single supply op amps, requires an external pull down resistor tied to ground. As mentioned above, the current flowing through this resistor becomes the DC bias current for the output stage NPN transistor. As this current approaches zero, the NPN turns off, and dG and dP will increase. This becomes more critical as the load resistor is increased in value. While driving a light load, such as 1 k $\Omega$ , if the input black level is kept above 1.25V, dG and dP are a respectable 0.03% and 0.03°.

For other biasing conditions see the Differential Gain and Differential Phase vs. Input Voltage curves.

#### **Output Drive Capability**

In spite of their moderately low 5 mA of supply current, the EL2257C/EL2357C are capable of providing  $\pm 100$  mA of output current into a  $10\Omega$  load, or  $\pm 60$  mA into  $50\Omega.$  With this large output current capability, a  $50\Omega$  load can be driven to  $\pm 3V$  with  $V_S=\pm 5V$ , making it an excellent choice for driving isolation transformers in telecommunications applications.

#### **Driving Cables and Capacitive Loads**

When used as a cable driver, double termination is always recommended for reflection-free performance. For those applications, the back-termination series resistor will de-couple the EL2257C/EL2357C from the cable and allow extensive capacitive drive. However, other applications may have high capacitive loads without a back-termination resistor. In these applications, a small series resistor (usually between  $5\Omega$  and  $50\Omega$ ) can be placed in series with the output to eliminate most peaking. The gain resistor ( $R_G$ ) can then be chosen to make up for any gain loss which may be created by this additional resistor at the output.

#### **Disable/Power-Down**

Each amplifier in the EL2257C/EL2357C can be individually disabled, placing each output in a highimpedance state. The disable or enable action takes only about 40 ns. When all amplifiers are disabled, the total supply current is reduced to 0 mA, thereby eliminating all power consumption by the EL2257C/EL2357C. The EL2257C/EL2357C amplifier's power down can be controlled by standard CMOS signal levels at each ENABLE pin. The applied CMOS signal is relative to the GND pin. For example, if a single +5V supply is used, the logic voltage levels will be +0.5V and +2.0V. If using dual  $\pm 5V$  supplies, the logic levels will be -4.5V and -3.0V. Letting all ENABLE pins float will disable the EL2257C/EL2357C. If the power-down feature is not desired, connect all ENABLE pins to the  $V_{S+}$  pin. The guaranteed logic levels of +0.5V and +2.0V are not standard TTL levels of +0.8V and +2.0V, so care must be taken if standard TTL will be used to drive the ENABLE pins.

125 MHz Single Supply, Clamping Op Amps

#### **Output Voltage Clamp**

The EL2257C/EL2357C amplifiers have an output voltage clamp. This clamping action is fast, being activated almost instantaneously, and being deactivated in < 7 ns, and prevents the output voltage from going above the preset clamp voltage. This can be very helpful when the EL2257C/EL2357C are used to drive an A/D converter, as some converters can require long times to recover if overdriven. The output voltage remains at the clamp voltage level as long as the product of the input voltage and the gain setting exceeds the clamp voltage. For example, if the EL2257C/EL2357C is connected in a gain of 2, and +3V DC is applied to the CLAMP pin, any voltage higher than +1.5V at the inputs will be clamped and +3V will be seen at the output. Each amplifier of the EL2257C have their own CLAMP pin, so individual clamp levels may be set, whereas a single CLAMP pin controls the clamp level of the EL2357C.

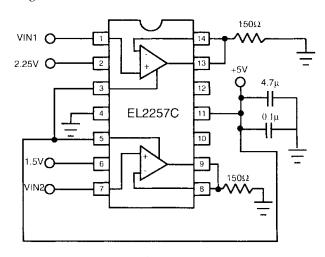

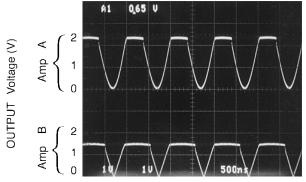

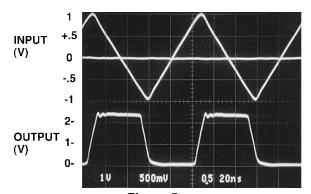

Figure 1 below is the EL2257C with each amplifier unity gain connected. Amplifier A is being driven by a 3 Vp-p sinewave and has 2.25V applied to CLAMPA, while amplifier B is driven by a 3 Vp-p triangle wave and 1.5V is applied to CLAMPB. The resulting output waveforms, with their outputs being clamped is shown in Figure 2.

Figure 1.

Figure 2.

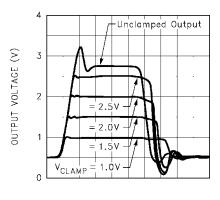

Figure 3 shows the output of amplifier A of the same circuit being driven by a 0.5V to 2.75V square wave as the clamp voltage is varied from 1.0V to 2.5V, as well as the unclamped output signal. The rising edge of the signal is clamped to the voltage applied to the CLAMP pin almost instantaneously. The output recovers from the clamped mode within 5–7 ns, depending on the clamp voltage. Even when the CLAMP pin is taken 0.2V below the minimum 1.2V specified, the output is still clamped and recovers in about 11 ns.

TIME 10 ns/div

Figure 3.

The clamp accuracy is affected by 1) the CLAMP pin voltage, 2) the input voltage, and 3) the load resistor. Depending upon the application, the accuracy may be as little as a few tens of millivolts up to a few hundred millivolts. Be sure to allow for these inaccuracies when choosing the clamp voltage. Curves of Clamp Accuracy vs.  $V_{CLAMP}$  and  $V_{IN}$  for 3 values of  $R_L$  are included in the Typical Performance Curves Section.

### 125 MHz Single Supply, Clamping Op Amps

Unlike amplifiers that clamp at the input and are therefore limited to non-inverting applications only, the EL2257C/EL2357C output clamp architecture works for both inverting and non-inverting gain applications. There is also no maximum voltage difference limitation between  $V_{\rm IN}$  and  $V_{\rm CLAMP}$  which is common on input clamped architectures.

The voltage clamp operates for any voltage between +1.2V above the GND pin, and the minimum output voltage swing,  $V_{OP}$ . Forcing the CLAMP pin much below +1.2V can saturate transistors and should therefore be avoided. Forcing the CLAMP pin above  $V_{OP}$  simply de-activates the CLAMP feature. In other words, one cannot expect to clamp any voltage higher than what the EL2257C/EL2357C can drive to in the first place. If the clamp feature is not desired, either let the CLAMP pin float or connect it to the  $V_{S+}$  pin.

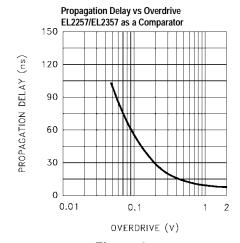

#### EL2257C/EL2357C Comparator Application

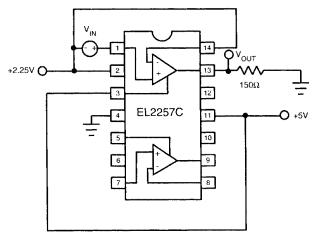

The EL2257C/EL2357C can be used as a very fast, single supply comparator by utilizing the clamp feature. Most op amps used as comparators allow only slow speed operation because of output saturation issues. However, by applying a DC voltage to the CLAMP pin of the EL2257C/EL2357C, the maximum output voltage can be clamped, thus preventing saturation. *Figure 4* is amplifier A of an EL2257C implemented as a comparator. 2.25V DC is applied to the CLAMP pin, as well as the IN- pin. A differential signal is then applied between the inputs. *Figure 5* shows the output square wave that results when a ±1V, 10 MHz triangular wave is applied,

while *Figure 6* is a graph of propagation delay vs. over-drive as a square wave is presented at the input.

Figure 4.

Figure 5.

Figure 6.

125 MHz Single Supply, Clamping Op Amps

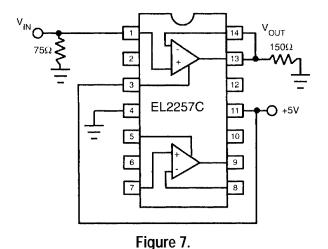

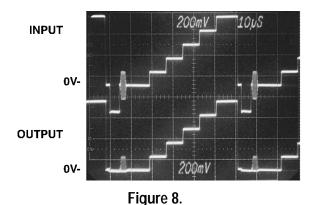

#### **Video Sync Pulse Remover Application**

All CMOS Analog to Digital Converters (A/Ds) have a parasitic latch-up problem when subjected to negative input voltage levels. Since the sync tip contains no useful video information and it is a negative going pulse, we can chop it off. *Figure 7* shows a unity gain connected amplifier A of an EL2257C. *Figure 8* shows the complete input video signal applied at the input, as well as the output signal with the negative going sync pulse removed.

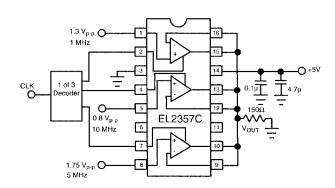

### Multiplexing with the EL2257C/EL2357C

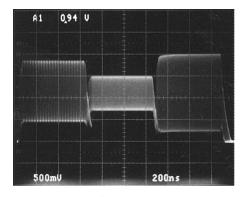

The ENABLE pins on the EL2257C/EL2357C allow for multiplexing applications. Figure 9 shows an EL2357C with all 3 outputs tied together, driving a back terminated  $75\Omega$  video load. Three sinewaves of varying amplitudes and frequencies are applied to the three

inputs. Logic signals are applied to each of the ENABLE pins to cycle through turning each of the amplifiers on, one at a time. Figure~10 shows the resulting output waveform at  $V_{\rm OUT}$ . Switching is complete in about 50 ns. Notice the outputs are tied directly together. Decoupling resistors at each output are not necessary. In fact, adding them approximately doubles the switching time to  $100~\rm ns$ .

Figure 9.

Figure 10.

#### **Short Circuit Current Limit**

The EL2257C/EL2357C have internal short circuit protection circuitry that protect it in the event of its output being shorted to either supply rail. This limit is set to around 100 mA nominally and reduces with increasing junction temperature. It is intended to handle temporary shorts. If an output is shorted indefinitely, the power dissipation could easily increase such that the part will be destroyed. Maximum reliability is maintained if the output current never exceeds  $\pm 90$  mA. A heat sink may be

### 125 MHz Single Supply, Clamping Op Amps

required to keep the junction temperature below absolute maximum when an output is shorted indefinitely.

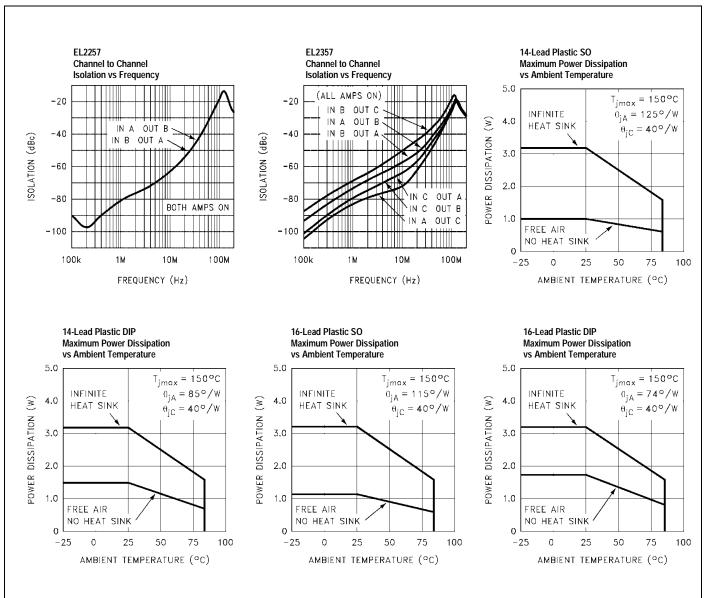

#### **Power Dissipation**

With the high output drive capability of the EL2257C/EL2357C, it is possible to exceed the 150°C Absolute Maximum junction temperature under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for the application to determine if power-supply voltages, load conditions, or package type need to be modified for the EL2257C/EL2357C to remain in the safe operating area.

The maximum power dissipation allowed in a package is determined by:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMAX}}{\theta_{JA}}$$

where:

- $T_{JMAX} = Maximum Junction Temperature$

- T<sub>AMAX</sub> = Maximum Ambient Temperature

- $\theta_{JA}$  = Thermal Resistance of the Package

- PD<sub>MAX</sub> = Maximum Power Dissipation in the Package.

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or:

$$PD_{MAX} = N \times V_S \times I_{SMAX} + (V_S - V_{OUT}) \times \frac{V_{OUT}}{R_L}$$

where:

- N = Number of amplifiers

- $V_S = \text{Total Supply Voltage}$

- $I_{SMAX} = Maximum Supply Current per amplifier$

- V<sub>OUT</sub> = Maximum Output Voltage of the Application

- R<sub>L</sub> = Load Resistance tied to Ground

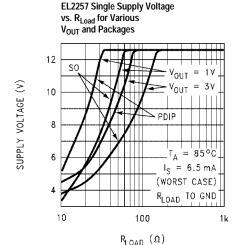

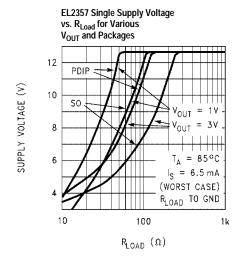

If we set the two PD<sub>MAX</sub> equations, [1] and [2], equal to each other, and solve for  $V_S$ , we can get a family of

curves for various loads and output voltages according to:

$$V_{S} = \frac{\frac{R_{L} \times (T_{JMAX} - T_{AMAX})}{N \times \theta_{JA}} + (V_{OUT})^{2}}{\frac{(I_{S} \times R_{L}) + V_{OUT}}{}}$$

Figures 11 and 12 below show total single supply voltage  $V_S$  vs.  $R_L$  for various output voltage swings for the PDIP and SOIC packages. The curves assume WORST CASE conditions of  $T_A = +85\,^{\circ}\text{C}$  and  $I_S = 6.5\,\text{mA}$  per amplifier.

Figure 11.

Figure 12.

125 MHz Single Supply, Clamping Op Amps

### EL2257C/EL2357C Macromodel (one channel)

```

* Revision A, October 1995

* Pin numbers reflect a standard single opamp.

* When not being used, the clamp pin, pin 1,

* should be connected to Vsupply, pin 7

Connections:

+input

-input

+Vsupply

-Vsupply

output

clamp

.subckt EL2257/el 3

Input Stage

il 7 10 250μA

i2 7 11 250µA

r1 10 11 4K

q1 12 2 10 qp

q2 13 3 11 qpa

r2 12 4 100

r3 13 4 100

* Second Stage & Compensation

gm 15 4 13 12 4.6m

r4 15 4 15Meg

c1 15 4 0.36pF

* Poles

el 17 4 15 4 1.0

r6 17 25 400

c3 25 4 1pF

r7 25 18 500

c4 18 4 1pF

* Connections:IN+IN+IN+IN+IN+IN+INININININ

* Output Stage & Clamp

i3 20 4 1.0mA

q3 7 23 20 qn

q4 7 18 19 qn

q5 7 18 21 qn

q6 4 20 22 qp

q7 7 23 18 qn

d1 19 20 da

d2 18 1 da

r8 21 6 2

r9 22 6 2

r10 18 21 10k

r11 7 23 100k

d3 23 24 da

d4 24 4 da

d5 23 18 da

* Power Supply Current

ips 7 4 3.2mA

* Models

```

```

.model qn npn(is800e-18 bf150 tf0.02nS)

.model qpa pnp(is810e-18 bf50 tf0.02nS)

.model qp pnp(is800e-18 bf54 tf0.02nS)

.model da d(tt0nS)

.ends

```

125 MHz Single Supply, Clamping Op Amps

#### **General Disclaimer**

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

#### Elantec, Inc.

1996 Tarob Court Milpitas, CA 95035

Telephone: (408) 945-1323

(800) 333-6314

Fax: (408) 945-9305 European Office: 44-71-482-4596

#### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. Products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.