# 1

# **Keyboard Encoder**

### **FEATURES**

- One integrated circuit required for complete keyboard assembly

- N key rollover or lock out operation

- Quad mode operation

- Lock out/rollover selection under external control (option)

- Self-contained or slave oscillator circuit

- 10 output data bits available

- Outputs directly compatible with TTL/DTL or MOS logic arrays

- Output data buffer register included

- Output enable provided (option)

- External data complement control provided (option)

- Pulse or level data ready output signal provided (option)

- "Any Key Down" output provided (option)

- Externally controlled delay network provided to eliminate the effect of contact bounce

- Programmable coding with a single mask change

- Static charge protection on all input and output terminals

- Entire circuit protected by a layer of glass passivation

## **DESCRIPTION**

The General Instrument AY-5-3600 is a Keyboard Encoder containing a 3600 bit Read Only Memory and all the logic necessary to encode single pole single throw keyboard closures into a usable 10 bit code. Data, Any Key Down and Data Ready outputs are directly compatible with TTL/DTL or MOS logic arrays without the need for any special interface components.

The AY-5-3600 is fabricated with MTNS technology and contains 5000 P channel enhancement mode transistors on a single monolithic chip.

#### **CUSTOM CODING INFORMATION**

The custom coding information for General Instrument's AY-5-3600 Keyboard Encoder ROM should be transmitted to General Instrument in the form of 80 column punched cards. Each ROM pattern requires 92 cards (1 title card, 1 circuit option card and 90 ROM pattern cards). (See Note 1)

If it is not possible to supply punched cards, then the Truth Table should be completed (See Note 1). However, there would be a

substantial savings in both the coding charge and turn-around time if punched cards were used. Upon receipt of the punched cards or the Truth Table, General Instrument will prepare a computer-generated Truth Table which will be returned to the user for verification.

NOTE 1: Card and Truth Table format available upon request.

#### **PIN OPTIONS**

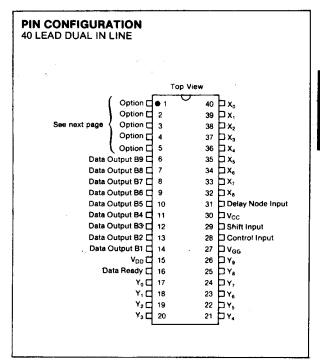

Pins 6-40 of the AY-5-3600 are permanently assigned. The functions assigned to pins 1-5 depend on which functional options are selected from the following:

#### **External Clock**

-requires one package pin to input an external clock source. Internal Oscillator

-requires three package pins interconnected with an external RC network to develop the clock required.

### Lockout/Rollover (LO/RO)

—requires one package pin to externally select N-Key Lockout or N-Key Rollover. LO = +5V, RO = GND.

## Complement Control (CC)

-requires one package pin to externally control the logic state of the data bits (B1-B10) and, if required, the Data Ready output.

# Chip Enable (CE)

-requires one package pin to control the data bits (B1-B10) and, if required, the Data Ready and Any Key Output.

#### Any Key Output (AKO)

-requires one package pin to indicate a key depression.

#### Output Data Bit 10 (B10)

-requires one package pin when ten data bits are required to encode each key.

#### Select the pin options desired:

External Clock + 4 of the following functions

Internal Oscillator + 2 of the following functions LO/RO, CC, CE, AKO, BIO

The following chart lists the pin assignments according to the functions selected above:

| PIN 1          | PIN 2               | PIN 3 | PIN 4 | PIN 5 |

|----------------|---------------------|-------|-------|-------|

| External Clock | LO/RO               | CC    | CE    | AKO   |

| External Clock | LO/RO               | CC    | CE    | BIO   |

| External Clock | LO/RO               | CC    | AKO   | BIO   |

| External Clock | LO/RO               | CE    | AKO   | BIO   |

| External Clock | cc                  | CE    | AKO   | BIO   |

|                | <u> </u>            | LO/RO | CC    |       |

|                |                     | LO/RO | CE    |       |

|                |                     | LO/RO | AKO   |       |

|                |                     | LO/RO | BIO   |       |

|                | Internal Oscillator |       |       | CE    |

|                |                     | cc    | AKO   |       |

|                |                     |       | cc    | BIO   |

|                |                     |       | CE    | AKO   |

|                |                     |       | CE    | BIO   |

|                |                     |       | AKO   | BIO   |

#### **ELECTRICAL CHARACTERISTICS**

# Maximum Ratings\*

$V_{DD}$  and  $V_{GG}$  (with respect to  $V_{CC})$  . . . . . . . . . . . -20V to +0.3V Logic input voltages (with respect to  $V_{\rm cc})$  . . . . . . -20V to  $\pm 0.3V$ Storage Temperature . . . . . . . . . . . . . . . -65°C to +150°C Operating Temperature Range. . . . . . . . . . . 0°C to +70°C \*Exceeding these ratings could cause permanent damage. Functional operation of this device at these conditions is not implied-operating ranges are specified below.

#### Standard Conditions (unless otherwise noted)

$V_{\rm CC} = +5$  Volts  $\pm 0.5$  Volts  $V_{GG} = -12 \text{ Volts } \pm 1.0 \text{ Volts, } V_{DD} = \text{GND}$  $(V_{cc} = Substrate Voltage)$ Operating Temperature (T<sub>A</sub>)= 0°C to +70°C

| Characteristics                                             | Sym              | Min                                  | Typ**              | Max                         | Units                    | Conditions                                          |

|-------------------------------------------------------------|------------------|--------------------------------------|--------------------|-----------------------------|--------------------------|-----------------------------------------------------|

| Clock Frequency                                             | f                | 10                                   | 50                 | 100                         | kHz                      | See Block diagram footnote* for typical R-C values  |

| External Clock Width                                        |                  | 7                                    |                    | _                           | μS                       | ior typical 11-5 values                             |

| Clock Input                                                 | Vio              | \ \v                                 |                    | 1                           | v                        |                                                     |

|                                                             | VI,              | V <sub>GG</sub> V <sub>CC</sub> -1.4 |                    | .15<br>V <sub>cc</sub> +0.3 | l v                      |                                                     |

| Data Input                                                  | ''               | 1.7                                  | _                  | Vac 10.3                    | 1                        |                                                     |

| (Shift, Control,                                            |                  | 1                                    | 1                  | 1                           | 1                        | †                                                   |

| Complement Control,<br>Lockout/Rollover,<br>Chip Enable     |                  |                                      |                    |                             |                          |                                                     |

| & External Clock) Logic "0" Level                           | 1                |                                      |                    |                             | l                        |                                                     |

| Logic "1" Level                                             | Vio<br>VII       | Vag                                  | -                  | +0.75                       | V                        |                                                     |

| Shift & Control Input                                       | VI1              | V <sub>cc</sub> -1.1                 | -                  | Vcc+0.3                     | V                        | }                                                   |

| Current                                                     | I <sub>NSC</sub> | 75                                   | 95                 | 120                         | ۸ ا                      | 1 N = 151                                           |

| X Output (X <sub>0</sub> -X <sub>8</sub> )                  | Nac              | /3                                   | 95                 | 120                         | μA                       | V <sub>1</sub> = +5V                                |

| Logic "1" Output Current                                    | Ixt              | 40                                   | 170                | 400                         | 1.                       | 1 , , , , , , , , ,                                 |

| Logic 1 Capat Carrent                                       | ואי              | 600                                  | 170                | 400                         | μA                       | V <sub>OUT</sub> = V <sub>CC</sub> (See Note 2)     |

|                                                             |                  | 900                                  | 1300<br>1600       | 2500<br>3500                | μA                       | $V_{OUT} = V_{CC} - 1.3V$                           |

|                                                             | -                | 1500                                 | 3800               | 6000                        | μΑ                       | $V_{\text{OUT}} = V_{\text{CC}} - 2.0V$             |

|                                                             | 1                | 3000                                 | 6000               | 10000                       | μA<br>                   | $V_{OUT} = V_{CC} - 5V$ $V_{OUT} = V_{CC} - 10V$    |

| Logic "0" Output Current                                    | 1 <sub>xo</sub>  | 8                                    | 15                 | 50                          | μ <b>Α</b><br>μ <b>Α</b> | $V_{OUT} = V_{CC} - 10V$ $V_{OUT} = V_{CC}$         |

| • • • • • • • • • • • • • • • • • • •                       | 1                | 6                                    | 11                 | 35                          | μΑ                       | $V_{OUT} = V_{CC} - 1.3V$                           |

|                                                             | 1                | 5                                    | 10                 | 30                          | μA                       | $V_{OUT} = V_{CC} = 1.3V$ $V_{OUT} = V_{CC} = 2.0V$ |

|                                                             |                  | 2                                    | 5                  | 15                          | μA                       | $V_{OUT} = V_{CC} - 5V$                             |

|                                                             |                  | _                                    | 0.5                | 5                           | μА                       | $V_{\text{OUT}} = V_{\text{CC}} - 10V$              |

| / Input (Y <sub>0</sub> -Y <sub>9</sub> )                   |                  |                                      | 1                  |                             |                          | 1 1007 100                                          |

| Trip Level                                                  | Vy               | V <sub>cc</sub> -5                   | V <sub>cc</sub> –3 | V <sub>cc</sub> -2          | l v                      | Y Input Going Positive (See Note 2)                 |

| Hysteresis                                                  | $\Delta V_{Y}$   | 0.5                                  | 0.9                | 1.4                         | v                        | (See Note 1)                                        |

| Selected Y Input Current                                    | lys              | 18                                   | 36                 | 100                         | μA                       | $V_{IN} = V_{CC}$                                   |

| •                                                           | 1                | 14                                   | 28                 | 90                          | μA                       | $V_{IN} = V_{CC} - 1.3V$                            |

|                                                             |                  | 13                                   | 25                 | 80                          | μΑ                       | $V_{IN} = V_{CC} - 2.0V$                            |

|                                                             | 1                | 6                                    | 12                 | 60                          | μA                       | $V_{IN} = V_{CC} - 5V$                              |

|                                                             | 1                | _                                    | 1                  | 30                          | μA                       | $V_{1N} = V_{CC} - 10V$                             |

| Unselected Y Input Current                                  | ÎΙγυ             | 9                                    | 18                 | 50                          | μA                       | $V_{1N} = V_{CC}$                                   |

|                                                             | İ                | 7                                    | 14                 | 45                          | μΑ                       | $V_{IN} = V_{CC} - 1.3V$                            |

|                                                             |                  | 6                                    | 13                 | 40                          | μА                       | $V_{IN} = V_{CC} + 2.0V$                            |

|                                                             |                  | 3                                    | 6                  | 30                          | μA                       | $V_{IN} = V_{CC} - 5V$                              |

|                                                             |                  | _                                    | 0.5                | 15                          | μΑ                       | $V_{IN} = V_{CC} - 10V$                             |

| nput Capacitance                                            | CIN              | <b>–</b>                             | 3                  | 10                          | pF                       | at 0V (All Inputs)                                  |

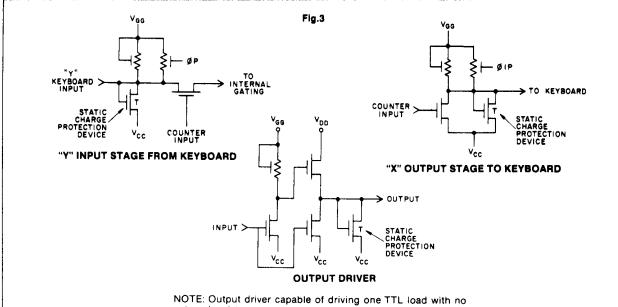

| -Y Precharge                                                |                  |                                      | _                  |                             | F*                       | , and the mission                                   |

| Characteristics                                             | φP               | 1500                                 | 3500               | 5000                        | μΑ                       | <b>V</b> = <b>V</b> <sub>cc</sub>                   |

|                                                             |                  | 200                                  | 600                | 1500                        | μA                       | V = V <sub>CC</sub> −5 (See Note 2)                 |

| witch Characteristics                                       |                  |                                      |                    |                             | · · · ·                  | (300 Hoto E)                                        |

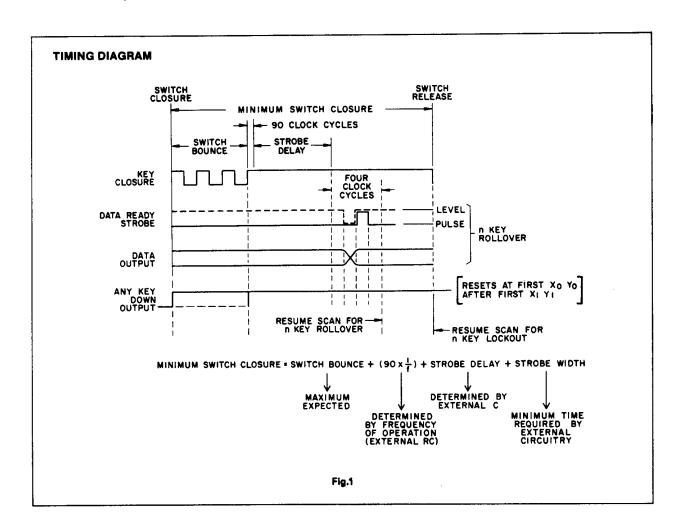

| Minimum Switch Closure                                      | <b>—</b>         | _                                    |                    | _                           |                          | See Timing Diagram                                  |

| Contact Closure                                             |                  |                                      |                    |                             |                          | Coo Timing Biagram                                  |

| Resistance                                                  | Zcc              | _                                    | _                  | 300                         | Ω                        |                                                     |

|                                                             | Zco              | 1 × 10 <sup>7</sup>                  | -                  | _                           | Ω                        |                                                     |

| itrobe Delay                                                |                  |                                      |                    |                             |                          |                                                     |

| Trip Level (Pin 31)                                         | V <sub>SD</sub>  | V <sub>cc</sub> -4                   | V <sub>cc</sub> -3 | V <sub>cc</sub> -2          | V                        |                                                     |

| Hysteresis                                                  | V <sub>SD</sub>  | 0.5                                  | 0.9                | 1.4                         | V                        | (See Note 1)                                        |

| Quiescent Voltage (Pin 31)                                  | i I              | -3                                   | -5                 | -9                          | v                        | With Internal Switched Resistor                     |

| Pata Output (B1-B10),<br>uny Key Down Output,<br>Pata Ready |                  |                                      |                    |                             |                          |                                                     |

| Logic "0"                                                   | _                | _                                    | _                  | .55                         | v                        | $I_{OL} = .25 mA$                                   |

|                                                             | -                | _                                    | _                  | 0.8                         | ν̈́Ι                     | $I_{OL} = 1.6 \text{mA}$                            |

| Logic "1"                                                   | _                | V∞ -1.3                              | _                  | _                           | ν̈́Ι                     | I <sub>OH</sub> = .95mA                             |

| ower                                                        |                  | '                                    | l                  |                             | •                        | -017 .0011171                                       |

| Icc                                                         | _                | _                                    | 8                  | 13                          | mA                       | $V_{cc} = +5V$                                      |

|                                                             |                  |                                      |                    |                             |                          |                                                     |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.

NOTE

I. Hysteresis is defined as the amount of return required to unlatch an input. 2. Precharge of X outputs and Y inputs occurs during each scanned clock cycle.

#### **OPERATION**

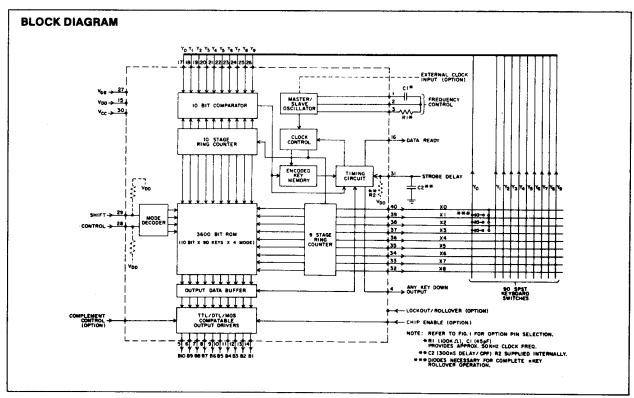

The AY-5-3600 contains (see Block Diagram) a 3600 bit ROM, 9-stage and 10-stage ring counters, a 10 bit comparator, timing circuitry, a 90 bit memory to store the location of encoded keys for n key rollover operation, an externally controllable delay network for eliminating the effect of contact bounce, an output data buffer, and TTL/DTL/MOS compatible output drivers.

The ROM portion of the chip is a 360 by 10 bit memory arranged into four 90-word by 10-bit groups. The appropriate levels on the Shift and Control Inputs selects one of the four 90-word groups; the 90-individual word locations are addressed by the two ring counters. Thus, the ROM address is formed by combining the Shift and Control Inputs with the two ring counters.

The external outputs of the 9-stage ring counter and the external inputs to the 10-bit comparator are wired to the keyboard to form an X-Y matrix with the 90-keyboard switches as the crosspoints. In the standby condition, when no key is depressed, the two ring counters are clocked and sequentially address the ROM, thereby scanning the key switches for key closures.

When a key is depressed, a single path is completed between one output of the 9-stage ring counter (X0 thru X8) and one input of the 10-bit comparator ( $Y_0$ - $Y_9$ ). After a number of clock cycles, a condition will occur where a level on the selected path to the comparator matches a level on the corresponding comparator input from the 10-stage ring counter.

#### N KEY ROLLOVER

— When a match occurs, and the key has not been encoded, the switch bounce delay network is enabled. If the key is still depressed at the end of the selected delay time, the code for the depressed key is transferred to the output data buffer, the data ready signal appears, a one is stored in the encoded key memory and the scan sequence is resumed. If a match occurs at another key location, the sequence is repeated thus encoding the next key. If the match occurs for an already encoded key, the match is not recognized. The code of the last key encoded remains in the output data buffer.

#### N KEY LOCKOUT

— When a match occurs, the delay network is enabled. If the key is still depressed at the end of the selected delay time, the code for the depressed key is transferred to the output data buffer, the data ready signal appears and the remaining keys are locked out by halting the scan sequence. The scan sequence is resumed upon key release. The output data buffer stores the code of the last key encoded.

#### **SPECIAL PATTERNS**

— Since the selected coding of each key and all the options are defined during the manufacture of the chip, the coding and options can be changed to fit any particular application of the keyboard. Up to 360 codes of up to 10 bits can be programmed into the AY-5-3600 ROM covering most popular codes such as ASCII, EBCDIC, Selectric, etc., as well as many specialized codes. The ASCII code in conjunction with internal oscillator, 10 data outputs and any key down output, is available as a standard pattern (See Figure 2).

3-26

| SYMBOL      | MODE         |                                       |              |              |          | MODE         |                     |              |                 |  |  |

|-------------|--------------|---------------------------------------|--------------|--------------|----------|--------------|---------------------|--------------|-----------------|--|--|

|             | N            | s                                     | С            | SC           | SYMBOL   | N            | 8                   | C            | sc              |  |  |

| •           | ļ            | X1 Y0, X0 Y8                          |              |              | SOH      |              |                     | <del></del>  | + <del>sc</del> |  |  |

| A           | l            | X0 Y2                                 | ľ            | X1 Y2        | STX      |              | I                   | X0 Y9        | X5 Y0, X6 Y9    |  |  |

| В           | l            | X5 Y3                                 | 1            | X2 Y2        |          |              | 1                   | X1 Y9        | X4 Y0, X1 Y9    |  |  |

| C           | ſ            | X2 Y3                                 |              | X3 Y2        | ETX      | X4 Y4        | X4 Y4               | X4 Y4        | X4 Y4, X6 Y0    |  |  |

| Ð           |              | X2 Y2                                 | 1            |              | EOT      |              | İ                   | 1            | X4 Y1           |  |  |

| Ē           | 1            | X2 Y1                                 | 1            | X4 Y2        | ENG      |              | 1                   |              | x3 Y1           |  |  |

| F           |              | X3 Y2                                 |              | X5 Y2        | ACK      |              |                     | X2 Y8        |                 |  |  |

| G           |              |                                       |              | X6 Y2        | 8€∟      |              | 1                   | X3 Y8        | X7 Y1, X2 Y8    |  |  |

| H           | X0 Y5        | X4 Y2                                 | l .          | X7 Y2        | li es i  |              |                     | A3 78        | X6 Y1, X3 Y8    |  |  |

|             | AU 15        | X0 Y5, X5 Y2                          | X0 Y5        | X0 Y5        | TH I     | X0 Y4        | UR III              | l            | X3 Y4           |  |  |

| 1           |              | X7 Y1                                 | i            | X0 Y4        | ll ië    | X7 Y6        | X0 Y4               | X0 Y4, X8 Y9 | X8 Y9           |  |  |

| J           |              | X6 Y2                                 | ľ            | X6 Y6        | l vi     |              | X7 Y6               | X7 Y6        |                 |  |  |

| K           | _            | X7 Y2                                 | 1            | ×3 Y6        |          | X3 Y7        | X3 Y7               | X3 Y7        | X3 Y7           |  |  |

| L           | X2 Y6        | X2 Y6, X8 Y2                          | X2 Y6        | X2 Y6        | FF       | X7 Y8        |                     | X7 YB        | X7 Y8           |  |  |

| M           |              | X7 Y3                                 |              | X3 Y5        | CR       | X3 Y5        | X3 Y5               | X3 Y5, X1 Y6 | X1 Y6           |  |  |

| N           |              | X6 Y3                                 | ł.           | X4 Y5        | i so     | X0 Y7        | 1                   | X0 Y7, X1 Y8 | X0 Y7, X1 YB    |  |  |

| 0           | 1            | X8 YI                                 | ĺ.           | A4 75        | Si       | X1 Y7        | XI Y7               | X1 Y7        |                 |  |  |

| ē           |              |                                       | 1            |              | I DLE I  |              |                     | 7,           | X1 Y7           |  |  |

| 0 1         |              | x6 Y6                                 | ł            | X0 Y2, X0 Y3 | DC:      |              | 1                   |              | X0 Y1           |  |  |

| ă į         |              | X0 Y1                                 | 1            | XI Y3        | OC2      |              | 1                   |              | X5 Y1           |  |  |

|             |              | X3 Y1                                 |              | X2 Y3        | DC3      |              | 1                   |              | X6 Y7           |  |  |

| s           |              | XIY2                                  | ı            | X4 Y3        | 004      |              | 1                   | ı            | X2 Y1           |  |  |

| 7           |              | X4 YT                                 | ľ            | X5 Y3        |          |              | 1                   | i .          | X3 Y0           |  |  |

| U           |              | XO Y I                                |              | X6 Y3        | NAK      |              | ı                   |              | X2 Y0           |  |  |

| v           |              | X4 Y3                                 |              | X7 Y3        | SYN ]    |              |                     | 1            | X5 Y4           |  |  |

| w           |              | XI YI                                 |              |              | ETB      |              |                     | i            | X1 Y0           |  |  |

| x i         |              | X1 Y3                                 |              | X6 Y5        | CAN      | X3 Y4        |                     | X3 Y4        | ^/ ''           |  |  |

| ÿ           |              |                                       | 1            | X8 Y2        | EW       |              | 1                   | ~3.14        | X8 Y0           |  |  |

| ; l         |              | X5 Y1                                 |              | X5 Y6        | Sue      |              |                     | 1            | X0 Y0           |  |  |

| - 1         |              | XO Y3                                 |              | X5 Y5        | ESC      |              | ł                   | [            |                 |  |  |

| • 1         | X0 Y2        |                                       | X0 Y2        | l            | FS       |              | 1                   |              | X7 Y0           |  |  |

| ы           | X5 Y3        |                                       | X5 Y3        |              | GS       |              |                     | ļ            | X1 Y4           |  |  |

| ٠           | ×2 Y3        |                                       | X2 Y3        |              |          |              |                     | 1            | X7 Y6           |  |  |

| d           | X2 Y2        |                                       | X2 Y2        | 1            | AS       | X1 Y4        | X1 Y4               | XIY4         | ł               |  |  |

| e           | X2 Y1        | 1                                     | X2 Y1        | i            | US       | X2 Y7        | X2 Y7               | X2 Y7        | X2 Y7           |  |  |

|             | X3 Y2        | i I                                   | X3 Y2        | 1            | SP       | X3 Y3, X4 Y9 | X4 Y9, X3 Y3        | X4 Y9, X3 Y3 | X4 Y9, X3 Y3    |  |  |

| .           | X4 Y2        |                                       |              | i            | 11 ' 1   | X5 Y9        | X5 Y9, X0 Y9        | X5 Y9        | X5 Y9           |  |  |

| ń I         | X5 Y2        | 1                                     | X4 Y2        | ì            | 11 - 1   | X3 Y9        | X3 Y9, X7 Y5, X1 Y9 | X3 Y9        | X3 Y9, X7 Y5    |  |  |

|             | X7 Y1        | 1                                     | X5 Y2        |              |          | X6 Y9        | X6 Y9, X2 Y0        | X6 Y9.       |                 |  |  |

| .           |              | j l                                   | X7 Y1        | !            | <b>S</b> | X2 Y5        | X2 Y5, X3 Y0        | X2 Y5        | X6 Y9           |  |  |

| ! 1         | X6 Y2        |                                       | X6 Y2        | 1            |          | X1 Y5        |                     |              | X2 Y5           |  |  |

| : 1         | X7 Y2, X2 Y9 | 1                                     | X7 Y2        | f            | ا ة ا    | X6 Y8        | X1 Y5, X4 Y0        | X1 Y5        | X1 Y5           |  |  |

| '           | X8 Y2        | 1                                     | X8 Y2        |              | "        |              | X6 Y0, X6 Y0, X2 Y8 | X6 Y8        | X6 Y8           |  |  |

| m .         | X7 Y3, X1 Y6 |                                       | X7 Y3        |              | 11 7 1   | X7 Y5        | X3 Y8               | X7 Y5        | X7 Y4           |  |  |

| n           | X6 Y3, X1 Y8 |                                       | X6 Y3        | İ            | 11 ' 1   | x7 Y9        | X7 Y4, X3 Y4, X8 Y0 | X7 Y9        | X7 Y9           |  |  |

| . !         | X8 Y1        | i i                                   | X8 YI        | •            | (I - )   | X4 Y8        | X4 Y8, X5 Y7, X8 Y9 | X4 Y8        | X4 Y8           |  |  |

| . 1         | X6 Y6, X0 Y8 | ļ l                                   |              |              | 11       | X5 Y8        | X5 Y8, X7 YD, X5 Y4 | X5 Y8        | X5 Y8           |  |  |

|             | XO YI        |                                       | X6 Y6        |              | 11 • 1   | XO YE        | X0 Y6, X5 Y6, X7 Y7 | X0 Y6        | X0 Y6, X7 Y7    |  |  |

| .           |              |                                       | X0 YI        |              | 11       | X8 Y3        | XB Y3               | XB Y3        |                 |  |  |

| . 1         | X3 Y1        |                                       | X3 Y1        |              |          | X2 Y4        | X2 Y4, X8 Y7        | X2 Y4        | X8 Y3           |  |  |

|             | X1 Y2        |                                       | X3 Y2        |              | n. I     | X8 Y4        | XB Y4               | X8 Y4        | X8 Y7           |  |  |

|             | X4 Y1        |                                       | X4 Y1        |              | , ,      |              | 1 ***               |              | X8 Y4           |  |  |

| ,           | X6 Y1        |                                       | X6 Y1        |              | 11 ' 1   | X7 Y4        | 1                   | X7 Y4        |                 |  |  |

| , 1         | X4 Y3        | 1                                     | X4 Y3        |              | ] 0      | X8 Y7, X8 Y8 | XB Y8               | X6 Y7, X8 Y8 | 8Y 8X           |  |  |

| ~ I         | XI YI        | 1                                     | XI YI        |              |          | X0'Y0, X0 Y9 | l I                 | X0 Y0        |                 |  |  |

| .           | X1 Y3        | i .                                   |              |              | 2        | X1 YO, X1 Y9 | 1                   | X1 Y0        |                 |  |  |

| .           | XS YI        |                                       | X1 Y3        |              | 3        | X2 Y6        | 1                   | X2 Y0        |                 |  |  |

|             |              |                                       | X5 Y1        |              | 4        | X3 Y0        |                     | X3 Y0        |                 |  |  |

|             | X0 Y3        | l 1                                   | X0 A3        |              | 5        | X4 Y0        | 1                   | X4 Y0        |                 |  |  |

| : 1         |              | X8 Y6, X2 Y9                          |              | X4 Y6, X8 Y6 | 6 (      | X5 YO, X2 YB | [                   |              |                 |  |  |

|             |              | : !                                   |              | XI YI        | ,        | X6 YO, X3 YB | [ [                 | X5 Y0        |                 |  |  |

| ) /         | X8 Y6        | X1 Y6                                 | X8 Y6        | XB Y1        | 6        |              | 1 1                 | X0 Y0        |                 |  |  |

| ١ ١         | i            | X1 YB                                 |              | X2 Y4        |          | X7 Y0        | 1 1                 | X7 Y0        |                 |  |  |

| - 1         | X4 Y7, X8 Y7 | · · · · · · · · · · · · · · · · · · · | X4 Y7, X8 Y7 | X4 Y7        | 9        | X6 Y0, X8 Y9 | 1                   | X8 Y0        |                 |  |  |

| - 1         | X3 Y6        | X3 Y6                                 |              | A4 T/        | li i     | X5 Y4        | X8 Y5               | X5 Y4        | X8 Y5           |  |  |

| - 1         | X4 Y5        |                                       | X3 Y6        |              | IJ ₁ L   | X8 Y5, X5 Y6 | 1                   | X8 Y5, X5 Y6 |                 |  |  |

| - 1         | A-19         | X4 Y5                                 | X4 Y5        |              | (        | X6 Y5        | X7 Y8, X6 Y5, X0 Y0 | X6 Y5        |                 |  |  |

| ÆL .        |              | 1                                     |              | X6 Y4        | -        | X8 Y4, X7 Y7 | X7 Y7, X6 Y4, X4 Y7 | X6 Y4        |                 |  |  |

|             |              | ı                                     | X2 Y9        | X2 Y9        | l , l    | X5 Y5        | X5 Y5, X5 Y0, X0 Y7 |              |                 |  |  |

| <b>W</b> LL | X5 Y7        | X5 Y7                                 | X5 Y7, X0 Y8 | X5 Y7, X0 Y8 | <b>)</b> | X4 Y6        |                     | X5 Y5        |                 |  |  |

|             |              | ŧ                                     |              |              | 1        | A4 10        | X4 Y6, X7 Y4        | X4 Y6        |                 |  |  |

Note 2. Codes 0000011 and 0011111 are not present in the standard AY-8-3600 pattern.

Fig.2 STANDARD AY-5-3600 CODE ASSIGNMENTS ASCINCODE

# OPTIONS PROVIDED WITH STANDARD ENCODER

- Device Marking: AY-5-3600

- Internal Oscillator on Pin Nos. 1, 2, 3

- Any Key Output on Pin No. 4

- Any Key Output True (Logic 1) During Key Depression

- Output Data Bit B10 on Pin No. 5

- N-Key Rollover Only

- True Outputs Only

- Pulse Data Ready Signal

- Internal Resistor to V<sub>DD</sub> on Shift/Control Pin

- Plastic Package

NOTE: Output driver capable of driving one TTL load with no external resistor. Capable of driving two TTL loads using an external 6.8K $\Omega$  resis-

Capable of driving two TTL loads using an external 6.8K $\Omega$  resistor to  $V_{\rm time}$

## TYPICAL CHARACTERISTIC CURVES

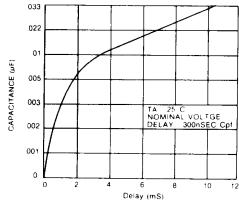

Fig.4 STROBE DELAY vs. C.

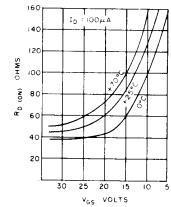

Fig.6 TYPICAL OUTPUT ON RESISTANCE (RDON) vs. GATE BIAS VOLTAGE (VGS)

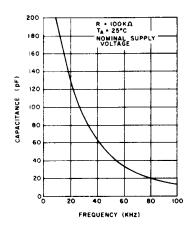

Fig.5 OSCILLATOR FREQUENCY vs. C<sub>2</sub>

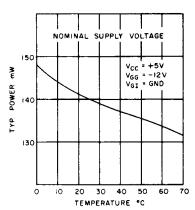

Fig.7 TYPICAL POWER CONSUMPTION (mW)