## Low Skew Output Buffer

### FEATURES

- Frequency range:

- 15 ~ 170MHz @ 3.3V

- 15 ~ 145MHz @ 2.5V

- Internal phase locked loop will allow spread spectrum modulation on reference clock to pass to outputs.

- Zero input output delay

- Less than 700 ps device device skew

- Less than 200 ps skew between outputs

- Less than 100 ps cycle cycle jitter

- 2.5V or 3.3V power supply operation

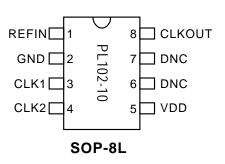

- Available in 8-Pin SOP or 6-pin SOT GREEN/ RoHS compliant package

**PIN CONFIGURATION**

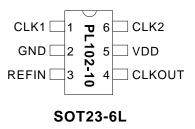

### DESCRIPTION

The PL102-10 is a high performance, low skew, low jitter zero delay buffer designed to distribute high speed clocks and is available in 8-pin SOP or 6-pin SOT23 package. It has two outputs that are synchronized with the input. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than  $\pm$ 350 ps, the device acts as a zero delay buffer.

### **BLOCK DIAGRAM**

## Low Skew Output Buffer

#### **PIN DESCRIPTIONS**

| Pin Name | Pin N  | lumber   | Tupo | Description                                                                                                                      |  |

|----------|--------|----------|------|----------------------------------------------------------------------------------------------------------------------------------|--|

|          | SOP-8L | SOT23-6L | Туре |                                                                                                                                  |  |

| REFIN    | 1      | 3        | I    | Input reference frequency. Spread spectrum modulation on this signal will be passed to the output (up to 100kHz SST modulation). |  |

| GND      | 2      | 2        | Р    | Ground Connection.                                                                                                               |  |

| CLK1     | 3      | 1        | 0    | Buffered clock output.                                                                                                           |  |

| CLK2     | 4      | 6        | 0    | Buffered clock output.                                                                                                           |  |

| VDD      | 5      | 5        | Р    | 2.5V or 3.3V Power Supply connection.                                                                                            |  |

| DNC      | 6, 7   | -        | -    | Do Not Connect                                                                                                                   |  |

| CLKOUT   | 8      | 4        | 0    | Buffered clock output. Internal feed back on this pin.                                                                           |  |

### **ELECTRICAL SPECIFICATIONS**

#### 1. Absolute Maximum Ratings

| PARAMETERS                        | SYMBOL          | MIN. | MAX.                 | UNITS |

|-----------------------------------|-----------------|------|----------------------|-------|

| Supply Voltage                    | V <sub>DD</sub> |      | 4.6                  | V     |

| Input Voltage, dc                 | VI              | -0.5 | $V_{DD}$ +0.5        | V     |

| Output Voltage, dc                | Vo              | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature               | Ts              | -65  | 150                  | °C    |

| Ambient Operating Temperature*    | T <sub>A</sub>  | -40  | 85                   | °C    |

| Junction Temperature              | TJ              |      | 125                  | °C    |

| Lead Temperature (soldering, 10s) |                 |      | 260                  | °C    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied. \*Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

#### 2. Electrical Characteristics

| PARAMETERS          | SYMBOL          | CONDITIONS                                            | MIN. | TYP. | MAX. | UNITS |

|---------------------|-----------------|-------------------------------------------------------|------|------|------|-------|

| Supply Voltage      | V <sub>DD</sub> |                                                       | 2.25 |      | 3.63 | V     |

| Input Low Voltage   | V <sub>IL</sub> |                                                       |      |      | 0.8  | V     |

| Input High Voltage  | V <sub>IH</sub> |                                                       | 2.0  |      |      | V     |

| Output Low Voltage  | Vol             | $I_{OL} = 24 \text{mA}$                               |      |      | 0.4  | V     |

| Output High Voltage | V <sub>OH</sub> | I <sub>он</sub> = 24mA                                | 2.4  |      |      | V     |

| Supply Current      | I <sub>DD</sub> | Unloaded outputs at 100MHz,<br>V <sub>DD</sub> =3.3V. |      | 22   | 30   | mA    |

## Low Skew Output Buffer

#### 3. Switching Characteristics

| PARAMETERS                                      | SYMBOL               | DESCRIPTION                                                         | MIN. | TYP. | MAX.    | UNITS |

|-------------------------------------------------|----------------------|---------------------------------------------------------------------|------|------|---------|-------|

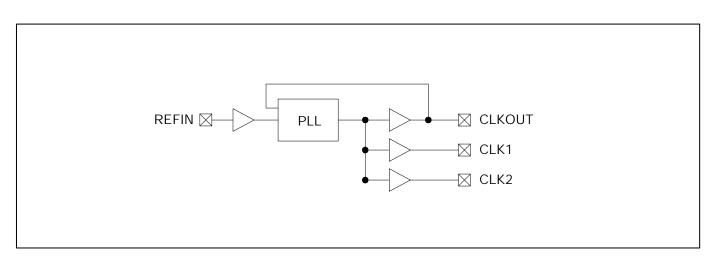

| Output Frequency                                | t1                   | 2.5V/3.3V                                                           | 15   |      | 145/170 | MHz   |

| Duty Cycle                                      | DC                   | Measured at $V_{DD}/2$ , $C_L=15pF$ , $F_{out} = 100MHz$            | 45   | 50   | 55      | %     |

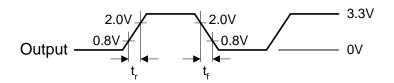

| Rise Time                                       | Tr                   | Measured between 10% and 90% $V_{\text{DD}},  C_{\text{L}} = 15 pF$ |      | 1.2  | 1.5     | ns    |

| Fall Time                                       | T <sub>f</sub>       | Measured between 90% and 10%, $C_{\text{L}}\text{=}15\text{pF}$     |      | 1.2  | 1.5     | ns    |

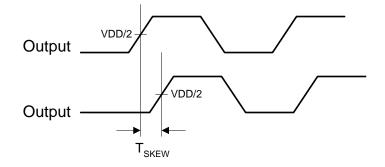

| Output to Output Skew                           | T <sub>skew</sub>    | All outputs equally loaded, $C_L=15pF$                              |      |      | 200     | ps    |

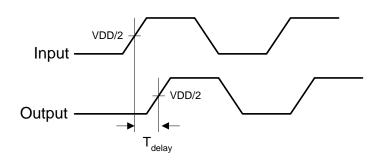

| Delay, REF Rising Edge<br>to CLKOUT Rising Edge | T <sub>delay</sub>   | Measured at $V_{DD}/2$                                              |      | 0    | ±350    | ps    |

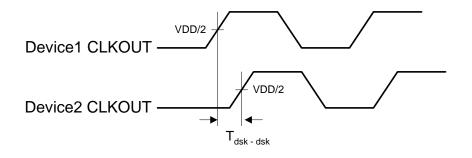

| Device to Device Skew                           | T <sub>dsk-dsk</sub> | Measured at V <sub>DD</sub> /2 on the CLKOUT pins of devices        |      | 0    | 700     | ps    |

| Cycle to Cycle Jitter                           | Т <sub>сус-сус</sub> | Measured at 100MHz                                                  |      |      | 60      | ps    |

| PLL Lock Time                                   | Tlock                | Stable power supply, valid clock presented on REF pin               |      |      | 1.0     | ms    |

| Jitter; Absolute Jitter                         | T <sub>jabs</sub>    | Measured 10,000 cycles,<br>low jitter input signal                  |      | 20   | 50      | ps    |

| Jitter; 1-sigma                                 | T <sub>j1-s</sub>    | Measured 10,000 cycles,<br>low jitter input signal                  |      | 9    | 15      | ps    |

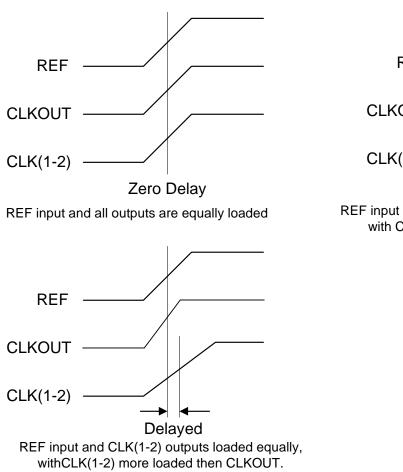

### SWITCHING WAVEFORMS

**Output - Output Skew**

**Duty Cycle Timing**

## Low Skew Output Buffer

#### SWITCHING WAVE FORMS

All Outputs Rise/Fall Time

Input to Output Propagation Delay

Device to Device Skew

### Low Skew Output Buffer

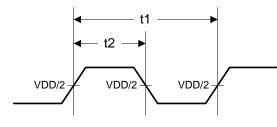

### **Output-Output Skew**

The skew between CLKOUT and the CLK(1-2) outputs is not dynamically adjusted by the PLL. Since CLKOUT is one of the inputs to the PLL, zero phase difference is maintained from REF to CLKOUT. If all outputs are equally loaded, zero phase difference will be maintained from REF to all outputs.

If applications requiring zero output-output skew, all the outputs must be equally loaded.

If the CLK(1-2) outputs are less loaded than CLKOUT, CLK(1-2) outputs will lead it; if the CLK(1-2) is more loaded than CLKOUT, CLK(1-2) will lag the CLKOUT.

Since the CLKOUT and the CLK(1-2) outputs are identical, they all start at the same time, but difference loads cause them to have different rise times and different times crossing the measurement thresholds.

Advanced REF input and CLK(1-2) outputs are equally loaded, with CLK(1-2) less loaded than CLKOUT.

## Low Skew Output Buffer

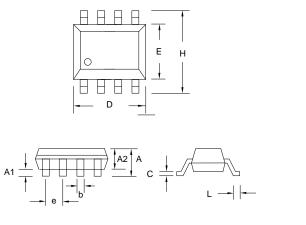

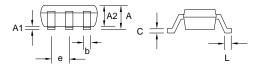

### PACKAGE INFORMATION (GREEN PACKAGE COMPLIANT)

#### SOP-8L

| Symbol | Dimension in MM |      |  |  |

|--------|-----------------|------|--|--|

| Symbol | Min.            | Max. |  |  |

| А      | 1.35            | 1.75 |  |  |

| A1     | 0.10            | 0.25 |  |  |

| A2     | 1.25            | 1.50 |  |  |

| В      | 0.33            | 0.53 |  |  |

| С      | 0.19            | 0.27 |  |  |

| D      | 4.80            | 5.00 |  |  |

| E      | 3.80            | 4.00 |  |  |

| Н      | 5.80            | 6.20 |  |  |

| L      | 0.40            | 0.89 |  |  |

| е      | 1.27 BSC        |      |  |  |

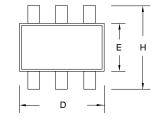

#### SOT23-6L

| Symbol | Dimension in MM |      |  |  |

|--------|-----------------|------|--|--|

| Symbol | Min.            | Max. |  |  |

| А      | 1.05            | 1.35 |  |  |

| A1     | 0.05            | 0.15 |  |  |

| A2     | 1.00            | 1.20 |  |  |

| В      | 0.30            | 0.50 |  |  |

| С      | 0.08            | 0.20 |  |  |

| D      | 2.80            | 3.00 |  |  |

| E      | 1.50            | 1.70 |  |  |

| Н      | 2.60            | 3.0  |  |  |

| L      | 0.35            | 0.55 |  |  |

| е      | 0.95 BSC        |      |  |  |

## Low Skew Output Buffer

### **ORDERING INFORMATION (GREEN PACKAGE COMPLIANT)**

| For part ordering, please contact our Sales Department:<br>47745 Fremont Blvd., Fremont, CA 94538, USA<br>Tel: (510) 492-0990 Fax: (510) 492-0991 |         |                           |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------|--|--|--|

| PART NUMBER<br>The order number for this device is a combination of the following:<br>Part number, Package type and Operating temperature range   |         |                           |  |  |  |

| PL102-10 X X - X<br>PART NUMBER NONE= TUBE<br>R=TAPE AND REEL                                                                                     |         |                           |  |  |  |

| PACKAGE TYPE TEMPERATURE<br>S= SOP-8L C=COMMERCIAL (0°C<br>T= SOT23-6L I=INDUSTRIAL (-40°C                                                        |         |                           |  |  |  |

| Part / Order Number                                                                                                                               | Marking | Package Option            |  |  |  |

| PL102-10SC                                                                                                                                        | P102-10 | 8-Pin SOP (Tube)          |  |  |  |

| PL102-10SC-R                                                                                                                                      | P102-10 | 8-Pin SOP (Tape and Reel) |  |  |  |

| PL102-10TC-R                                                                                                                                      | 10210   | 6-Pin SOT (Tape and Reel) |  |  |  |

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Phaselink is believed to be accurate and reliable. However, PhaseLink makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product. LIFE SUPPORT POLICY: PhaseLink's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.

Solder reflow profile available at www.phaselink.com/QA/solderingGreen.pdf