# 250 mW Power Amplifier with T/R and Diversity Switches 2.4 - 2.5 GHz AM55-0003

#### Features

- Highly Integrated Power Amplifier With T/R and **Diversity Switches**

- Operates Over 2.7 V to 6 V Supply Voltage

- High Linear Output Power (P<sub>1dB</sub>: +24 dBm)

- Individual Gate Control for Each Amplifier Stage

- Low Cost SSOP-28 Plastic Package

### Description

M/A-COM's AM55-0003 is a GaAs power amplifier with integrated transmit/receive and an antenna diversity switch in a low cost SSOP 28 plastic package. The power amplifier delivers +24 dBm of linear power with high efficiency and can be operated with voltages as low as 2.7 volts. The power amplifier switch is fully monolithic. The T/R and diversity switches achieve good insertion loss and isolation without degrading the overall linearity. The switches can be controlled with CMOS logic levels.

The AM55-0003 is ideally suited for QPSK, BPSK or other linearly modulated systems in the 2.4 GHz ISM frequency band. It can also be used in GFSK systems where levels of +25 dBm are required. Typical applications include WLAN and wireless portable data collection. This power amplifier can be combined with a transceiver IC (MD58-0001 or MD58-0002) to form a complete RF front end.

M/A-COM's AM55-0003 is fabricated using a mature 0.5-micron gate length GaAs process. The process features full passivation for increased performance and reliability.

## Typical Electrical Specifications

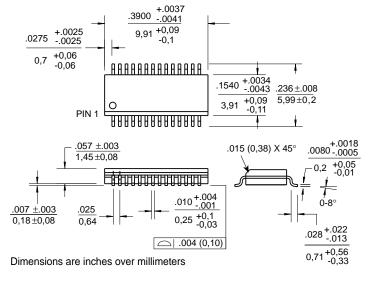

#### SSOP-28

#### **Ordering Information**

| Part Number  | Description                  |

|--------------|------------------------------|

| AM55-0003    | SSOP 28-Lead Plastic Package |

| AM55-0003TR  | Forward Tape & Reel*         |

| AM55-0003RTR | Reverse Tape & Reel*         |

| AM55-0003SMB | Designer's Kit               |

\* If specific reel size is required, consult factory for part number assignment.

| Test Conditions: Frequency: 2.45 GHz, V <sub>DD1,2,3</sub> = 5 V±5%, V <sub>G1</sub> adjusted for 20 mA quiescent bias on V <sub>DD1</sub> , V <sub>G2</sub> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| adjusted for 70 mA quiescent bias on $V_{DD2}$ , $V_{G3}$ adjusted for 90 mA quiescent bias on $V_{DD3}$ , $T_A = +25^{\circ}C$                              |

|   | 24   | 28<br>1.75:1 | 32                  |

|---|------|--------------|---------------------|

|   |      | 1.75:1       | 32                  |

|   | 22.5 | -            |                     |

|   | 22.5 | 24 5         |                     |

|   |      | 24.5         |                     |

|   |      | -20          | 0                   |

|   |      | -30          | -10                 |

|   |      | 270          | 375                 |

| i |      |              |                     |

|   |      | 1.2          |                     |

|   | 10   | 12           |                     |

|   |      | 1.5:1        |                     |

|   |      |              |                     |

|   |      | 10           | 270<br>1.2<br>10 12 |

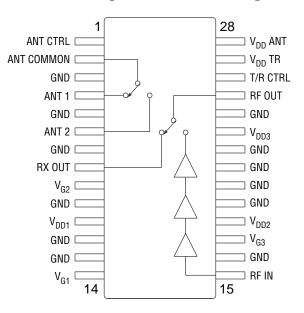

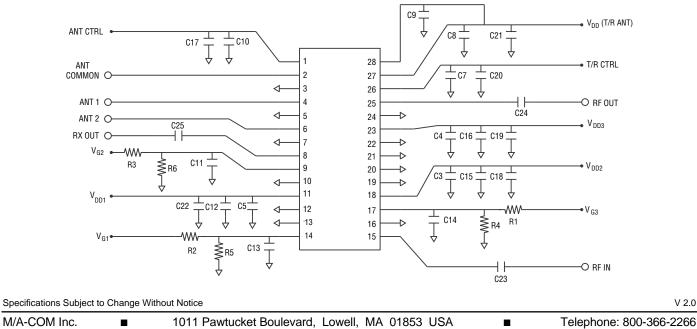

#### Pin Configuration

| Pin No. | Pin Name            | Description                                                                                                                                                                                   |

|---------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ANT CTRL            | Antenna selection: Select ANT 1                                                                                                                                                               |

|         |                     | (0V) or ANT 2 (+5 V)                                                                                                                                                                          |

| 2       | ANT COMMON          | Common Port of Diversity Switch                                                                                                                                                               |

| 3       | GND                 | DC and RF Ground                                                                                                                                                                              |

| 4       | ANT 1               | Output #1 of Diversity Switch                                                                                                                                                                 |

| 5       | GND                 | DC and RF Ground                                                                                                                                                                              |

| 6       | ANT 2               | Output #2 of Diversity Switch                                                                                                                                                                 |

| 7       | GND                 | DC and RF Ground                                                                                                                                                                              |

| 8       | RX OUT              | Output of T/R Switch for receive mode                                                                                                                                                         |

| 9       | V <sub>G2</sub>     | Negative bias control for the second PA stage, adjusted to set $V_{DD2}$ quiescent bias current, which is typically 70 mA. Typical voltage at pin = -0.55 V Input impedance: > 1 M $\Omega$   |

| 10      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 11      | V <sub>DD1</sub>    | Positive bias for the first stage of the PA, 2.7 to 6 volts                                                                                                                                   |

| 12      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 13      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 14      | V <sub>G1</sub>     | Negative bias control for the first PA stage, adjusted to set $V_{DD1}$ quiescent bias current, which is typically 20 mA.<br>Typical voltage at pin = -0.75 V Input impedance: > 1 M $\Omega$ |

| 15      | RF IN               | RF Input of the Power Amplifier                                                                                                                                                               |

| 16      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 17      | V <sub>G3</sub>     | Negative bias control for the third PA stage, adjusted to set $V_{DD3}$ quiescent bias current, which is typically 90 mA. Typical voltage at pin = -0.95 V Input impedance: > 1 M $\Omega$    |

| 18      | V <sub>DD2</sub>    | Positive bias for the second stage of the PA, 2.7 to 6 volts                                                                                                                                  |

| 19      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 20      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 21      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 22      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 23      | V <sub>DD3</sub>    | Positive bias for the third stage of the PA, 2.7 to 6 volts                                                                                                                                   |

| 24      | GND                 | DC and RF Ground                                                                                                                                                                              |

| 25      | RF OUT              | RF output of T/R switch and power amplifier for transmit mode                                                                                                                                 |

| 26      | T/R CTRL            | 0 V for transmit mode, +5 V for receive mode                                                                                                                                                  |

| 27      | V <sub>DD</sub> TR  | V <sub>DD</sub> for T/R switch                                                                                                                                                                |

| 28      | V <sub>DD</sub> ANT | V <sub>DD</sub> for Diversity Switch                                                                                                                                                          |

# Absolute Maximum Ratings<sup>1</sup>

| Parameter                         | Absolute Maximum      |

|-----------------------------------|-----------------------|

| Max. Input Power <sup>2</sup>     | +23 dBm               |

| Operating Voltages <sup>2,3</sup> | V <sub>DD</sub> = 8 V |

|                                   | $V_{GG} = -8 V$       |

| Operating Temperature             | -40°C to +85°C        |

| Storage Temperature               | -65°C to +150°C       |

1. Exceeding these limits may cause permanent damage.

2. Ambient temperature  $(T_A) = +25^{\circ}C$

3.  $|V_{DD}| + |V_{GG}|$  not to exceed 12 volts.

#### **Truth Table**

| Contro | l Line | Operating |

|--------|--------|-----------|

| ANT    | T/R    | Mode      |

| CTRL   | CTRL   | incuc     |

| Х      | 1      | Receive   |

| X      | 0      | Transmit  |

| 0      | X      | ANT 1     |

| 1      | X      | ANT 2     |

X - Don't Care

"0" = 0 V to 0.2 V @ 100 μA

"1" =  $V_{DD}$  to  $V_{DD}$  - 0.2 V @ 200  $\mu A$

#### **Functional Diagram and Pin Configuration**

Specifications Subject to Change Without Notice

M/A-COM Inc.

1011 Pawtucket Boulevard, Lowell, MA 01853 USA

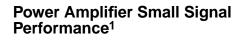

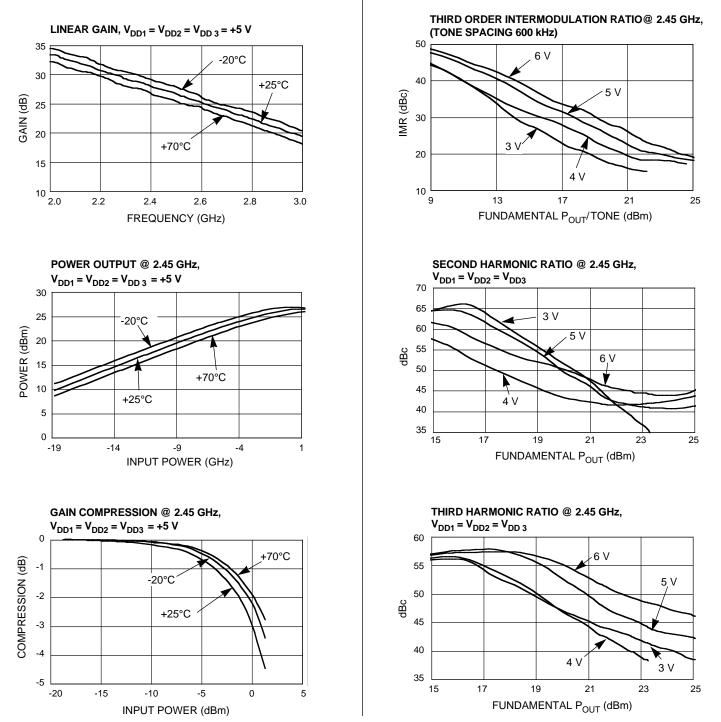

Power Amplifier CW Performance at Various Supply Voltages<sup>1</sup>

# 1. All data measured at T<sub>A</sub> = +25°C and V<sub>G1</sub>, V<sub>G2</sub> and V<sub>G3</sub> adjusted for first stage quiescent current of 20 mA, second stage current of 70 mA and third stage current of 90 mA, respectively.

| Spec | ifications Subject t | o Change Withou | It Notice |  |

|------|----------------------|-----------------|-----------|--|

M/A-COM Inc.

1011 Pawtucket Boulevard, Lowell, MA 01853 USA

Power Amplifier Spurious Response at

Various Supply Voltages<sup>1</sup>

# Power Amplifier Temperature Performance<sup>1</sup>

1. All data measured at T<sub>A</sub> = +25°C and V<sub>G1</sub>, V<sub>G2</sub> and V<sub>G3</sub> adjusted for first stage quiescent current of 20 mA, second stage current of 70 mA and third stage current of 90 mA, respectively.

| Specifications Subject | t to Change W | /ithout Notice                                 | V 2.0                   |

|------------------------|---------------|------------------------------------------------|-------------------------|

| M/A-COM Inc.           |               | 1011 Pawtucket Boulevard, Lowell, MA 01853 USA | Telephone: 800-366-2266 |

4

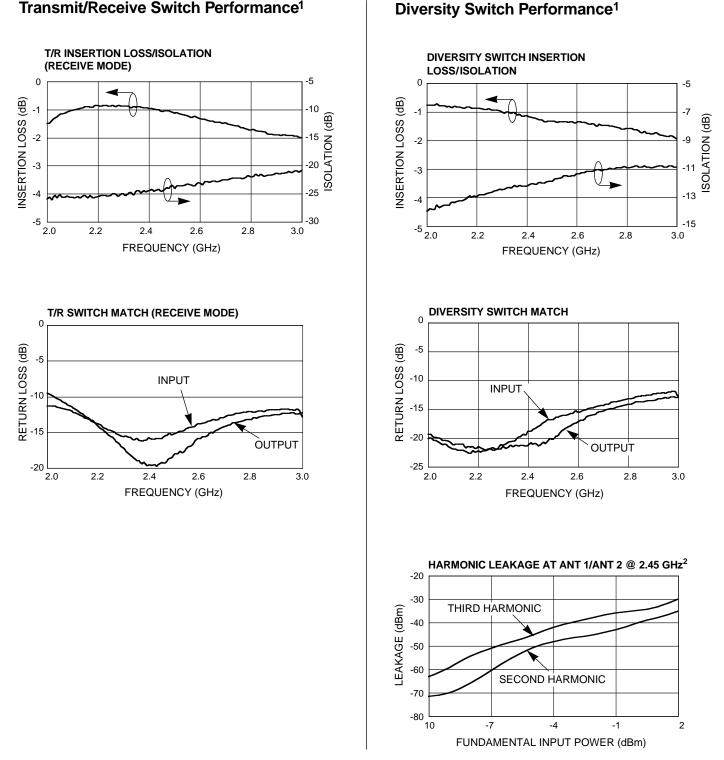

#### Transmit/Receive Switch Performance<sup>1</sup>

1. All data measured with V<sub>DD</sub> TR = V<sub>DD</sub> ANT = +5 V, T<sub>A</sub> = +25°C.

2. Measured at 2.45 GHz at RF IN. Output measured at ANT 1 or ANT 2, with RF OUT and ANT COMMON terminated in 50 Ω.

| M/A-COM Inc. | 1011 Pawtucket Boulevard, Lowell, MA 01853 USA | Telephone: 800-366-2266 |

|--------------|------------------------------------------------|-------------------------|

Layout View

V 2.0

#### **Recommended PCB Configuration**

#### 0.0690 in. R1 R2 R3 0.975 in. R5 R6 R4 C14 C13 C23 -776 Ó $\cap$ C12 C5 $\cap$ C11 中 C25 0.625 in. C24 C7 C10 C9 C8

#### **Cross-Section View**

The PCB dielectric between RF traces and RF ground layers should be chosen to reduce RF discontinuities between 50- $\Omega$ lines and package pins. M/A-COM recommends an FR-4 dielectric thickness of 0.008 in. (0.2 mm), yielding a 50- $\Omega$  line width of 0.015 in. (0.38 mm). The recommended metalization thickness is 1 oz. copper.

Shaded traces are vias to DC routing layer and traces on DC routing layer.

#### **Biasing Procedure**

The AM55-0003 requires that  $V_{GG}$  bias be applied prior to any  $V_{DD}$  bias. Permanent damage may occur if this procedure is not followed. All FETs in the PA will draw excessive current and damage internal circuitry.

### **External Circuitry Parts List**

| Label     | Value   | Purpose         |

|-----------|---------|-----------------|

| C1 - C6   | 22 pF   | Bypass (GHz)    |

| C23 - C24 | 22 pF   | DC Block        |

| C7 - C16  | 1000 pF | Bypass (MHz)    |

| C17 - C22 | 0.01 µF | Bypass (kHz)    |

| R1, R6    | 1.5 kΩ  |                 |

| R3, R5    | 5 kΩ    | FET Gate        |

| R2        | 12 kΩ   | Divider Network |

| R4        | 1 kΩ    |                 |

All off-chip components are low-cost surface mount components obtainable from multiple sources. (0.020 in. x 0.040 in. or 0.030 in. x 0.050 in.)

6

# **External Circuitry**

#### Designer's Kit (AM55-0003SMB)

The AM55-0003SMB Designer's Kit allows for immediate evaluation of M/A-COM's AM55-0003 integrated power amplifier with T/R and diversity switches. The evaluation board consists of an AM55-0003, recommended external surface mount circuitry, RF connectors and a DC multi-pin connector, all mounted to a multi-layer FR-4 PCB. Other items included in the Designer's Kit: a floppy disk (with typical performance data and a .DXF file of the recommended PCB layout) and any additional Application Notes. The AM55-0003SMB evaluation PCB and block diagram are illustrated below with all functional ports labeled.

Functional Block Diagram

#### P/A Switch Sample Board

#### **PIN 19** PIN 1 RF IN **PIN 20** PIN 2 RX OUT N RF IN O RX OUT <del>o<u></u>zo</del> (LNA IN) 01000 $\odot$ ANT 2 - ANT 2 0 D ŝ $\odot$ $\odot$ 88 D:::Q h... 0 - ANT 1 ANT 1 $\odot$ 0...0 **D** $\odot$ RF OUT RF OUT 6..... C ANT COMMON r ANT COMMON (DIV SW)

### **DC Connector Pinout**

| PCB DC<br>Connector | Function                | Device<br>Pin Number | PCB DC<br>Connector | Function                                      | Device<br>Pin Number |

|---------------------|-------------------------|----------------------|---------------------|-----------------------------------------------|----------------------|

| 1                   | GND                     | N/C                  | 11                  | N/C                                           | N/C                  |

| 2                   | ANT CTRL (0 V/ +5 V)    | 1                    | 12                  | V <sub>G3</sub>                               | 17                   |

| 3                   | N/C                     | N/C                  | 13                  | N/C                                           | N/C                  |

| 4                   | N/C                     | N/C                  | 14                  | V <sub>DD2</sub> (+5 V)                       | 18                   |

| 5                   | N/C                     | N/C                  | 15                  | N/C                                           | N/C                  |

| 6                   | V <sub>G2</sub>         | 9                    | 16                  | V <sub>DD3</sub> (+5 V)                       | 23                   |

| 7                   | VSW                     | N/C                  | 17                  | N/C                                           | N/C                  |

| 8                   | V <sub>DD1</sub> (+5 V) | 11                   | 18                  | T/R CTRL (0 V/ +5 V)                          | 8                    |

| 9                   | N/C                     | N/C                  | 19                  | GND                                           | N/C                  |

| 10                  | V <sub>G1</sub>         | 14                   | 20                  | V <sub>DD</sub> TR, V <sub>DD</sub> ANT(+5 V) | 27, 28               |

#### Specifications Subject to Change Without Notice

Downloaded from Elcodis.com electronic components distributor

M/A-COM Inc.

1011 Pawtucket Boulevard, Lowell, MA 01853 USA

V 2.0 Telephone: 800-366-2266

#### AM55-0003SMB Biasing Procedure

In order to prevent transients which may damage the MMIC, please adhere to the following procedure.

- Turn on all power supplies and set all voltages to 0 volts BEFORE connecting the power supplies to the DC connector.

- Apply a -5.0 volt supply to DC connector pin 10 ( $V_{G1}$ ).

- Apply a -5.0 volt supply to DC connector pin 6 ( $V_{G2}$ ).

- Apply a -5.0 volt supply to DC connector pin 12 ( $V_{G3}$ ).

- Apply a +5.0 volt supply to the DC connector pin 20 ( $V_{DD}$  TR,  $V_{DD}$  ANT).

- Apply a +5.0 volt supply to the DC connector pin 8 ( $V_{DD1}$ ).

- Apply a +5.0 volt supply to the DC connector pin 14 ( $V_{DD2}$ ).

- Apply a +5.0 volt supply to the DC connector pin 16 ( $V_{DD3}$ ).

- Apply a GND or +5.0 volt supply to the DC connector pin 18 (T/R CTRL, see truth table for desired mode).

- Apply a GND or +5.0 volt supply to the DC connector pin 2 (ANT CTRL, see truth table for desired mode).

- Adjust V<sub>G1</sub>, V<sub>G2</sub>, V<sub>G3</sub> supplies to -5 volts.

- Adjust all  $V_{DD}$  supplies to +5 volts.

- Adjust  $V_{G1}$  supply for desired  $V_{DD1}$  quiescent current (typically 20 mA,  $V_{G1}$  nominally -2.5 volts).

- Adjust V<sub>G2</sub> supply for desired V<sub>DD2</sub> quiescent current (typically 70 mA, V<sub>G2</sub> nominally -2.5 volts).

- Adjust V<sub>G3</sub> supply for desired V<sub>DD3</sub> quiescent current (typically 90 mA, V<sub>G3</sub> nominally -2.5 volts).

- To power off, reverse above procedure.

- 1) Set all  $V_{DD}$  lines to 0 volts.

- 2) Set  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  to 0 volts.

- 3) Disconnect bias lines from DC connector.

- 4) Turn off power supplies.

#### **Evaluation PCB and RF Connector Losses**

| Port Reference      | Loss (dB) |

|---------------------|-----------|

| RF IN               | 0.25      |

| RF OUT              | 0.25      |

| RX OUT (LNA IN)     | 0.25      |

| ANT COMMON (DIV SW) | 0.25      |

| ANT 1               | 0.25      |

| ANT 2               | 0.25      |

The DC connector on the Designer's Kit PCB allows selection of all the device's operating modes. It is accomplished by one or more of the following methods.

- 1. A mating female multi-pin connector (Newark Electronics Stock #46F-4658, not included)

- 2. Wires soldered to the necessary pins (not included)

- 3. Clip leads (not included)

- 4. A combination of clip leads or wires and jumpers (jumpers included as required)

Specifications Subject to Change Without Notice

M/A-COM Inc.

1011 Pawtucket Boulevard, Lowell, MA 01853 USA

V 2.0