# **Microcomputer Components**

8-Bit CMOS Microcontroller

Data Sheet 08.94

# SIEMENS

#### 8-Bit CMOS Microcontroller

C502

#### Preliminary

- Fully compatible to standard 8051 microcontroller

- Versions for 12 / 20 MHz operating frequency

- 16 K × 8 ROM (SAB-C502-2R only)

- 256 × 8 RAM

- 256 × 8 XRAM (additional on-chip RAM)

- Eight datapointers for indirect addressing of program and external data memory (including XRAM)

- Four 8-bit ports

- Three 16 -bit Timers / Counters (Timer 2 with Up/Down Counter feature)

- USART with programmable 10-bit Baudrate-Generator

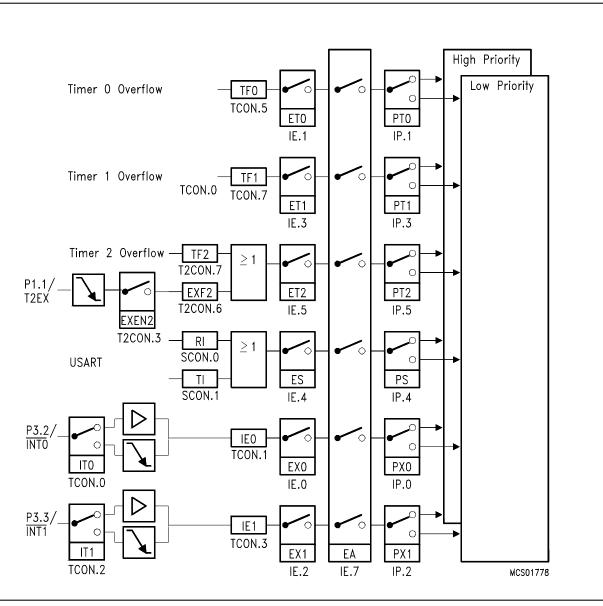

- Six interrupt sources, two priority levels

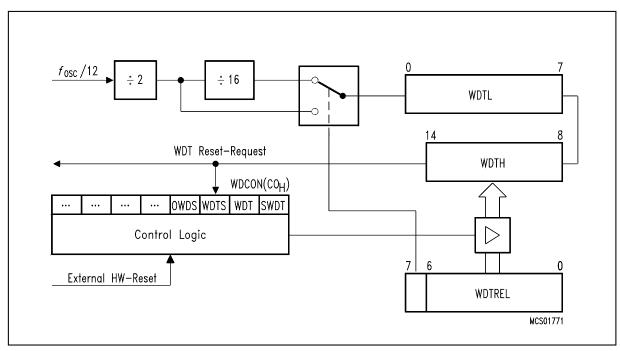

- Programmable 15-bit Watchdog Timer

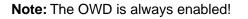

- Oscillator Watchdog

- Fast Power On Reset

- Power Saving Modes

- P-DIP-40 package and P-LCC-44 package

- Temperature ranges: SAB-C502

- $T_{\rm A}$ : 0 °C to 70 °C  $T_{\rm A}$ : - 40 °C to 85 °C SAF-C502

The SAB-C502-L/C502-2R described in this document is compatible with the SAB 80C52 and can be used for all present SAB 80C52 applications.

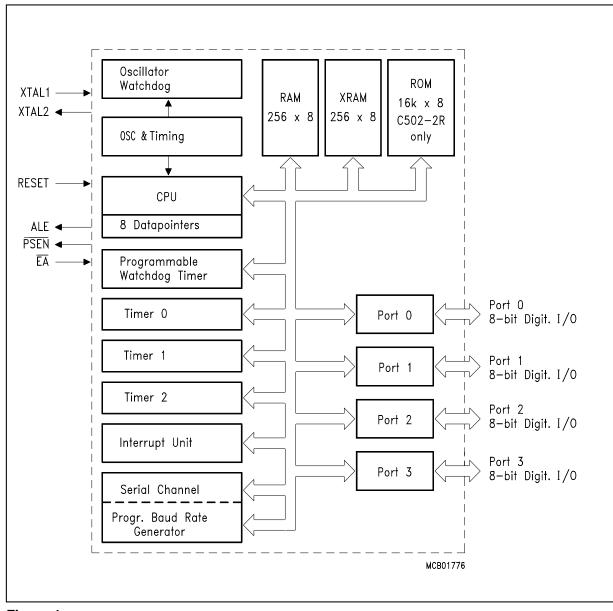

The SAB-C502-2R contains a non-volatile 16 K  $\times$  8 read-only program memory, a volatile 256  $\times$  8 read/write data memory, four ports, three 16-bit timers/counters, a six source, two priority level interrupt structure, a serial port and versatile fail save mechanisms. The SAB-C502-L/C502-2R incorporates 256  $\times$  8 additional on-chip RAM called XRAM. For higher performance eight datapointers are implemented. The SAB-C502-L is identical, except that it lacks the program memory on chip. Therefore the term SAB-C502 refers to both versions within this specification unless otherwise noted.

| Туре           | Ordering<br>Code | Package  | Description<br>(8-Bit CMOS microcontroller)                     |

|----------------|------------------|----------|-----------------------------------------------------------------|

| SAB-C502-LN    | Q67120-C838      | P-LCC-44 | for external memory 12 MHz                                      |

| SAB-C502-LP    | Q67120-C889      | P-DIP-40 |                                                                 |

| SAB-C502-2RN   | Q67120-C839      | P-LCC-44 | with mask-programmable ROM, 12 MHz                              |

| SAB-C502-2RP   | Q67120-C890      | P-DIP-40 |                                                                 |

| SAB-C502-L20N  | Q67120-C885      | P-LCC-44 | for external memory 20 MHz                                      |

| SAB-C502-L20P  | Q67120-C891      | P-DIP-40 |                                                                 |

| SAB-C502-2R20N | Q67120-C884      | P-LCC-44 | with mask-programmable ROM, 20 MHz                              |

| SAB-C502-2R20P | Q67120-C892      | P-DIP-40 |                                                                 |

| SAF-C502-LN    | Q67120-C883      | P-LCC-44 | for external ROM, 12 MHz,                                       |

| SAF-C502-LP    | Q67120-C893      | P-DIP-40 | ext. temp. – 40 °C to 85 °C                                     |

| SAF-C502-2RN   | Q67120-C886      | P-LCC-44 | with mask-programmable ROM, 12 MHz, ext. temp. – 40 °C to 85 °C |

| SAF-C502-2RP   | Q67120-C894      | P-DIP-40 |                                                                 |

| SAF-C502-L20N  | Q67120-C887      | P-LCC-44 | for external memory, 20 MHz,                                    |

| SAF-C502-L20P  | Q67120-C895      | P-DIP-40 | ext. temp. – 40 °C to 85 °C                                     |

| SAF-C502-2R20N | Q67120-C888      | P-LCC-44 | with mask-programmable ROM, 20 MHz, ext. temp. – 40 °C to 85 °C |

| SAF-C502-2R20P | Q67120-C896      | P-DIP-40 |                                                                 |

Note: Extended temperature range – 40 °C to 110 °C (SAH-C502) on request.

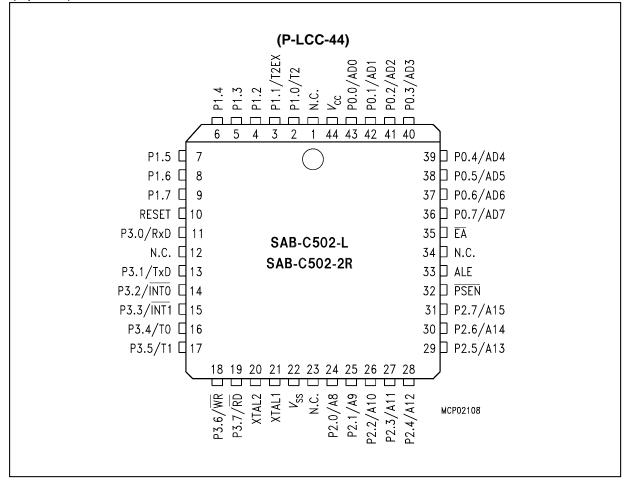

#### **Pin Configuration**

(top view)

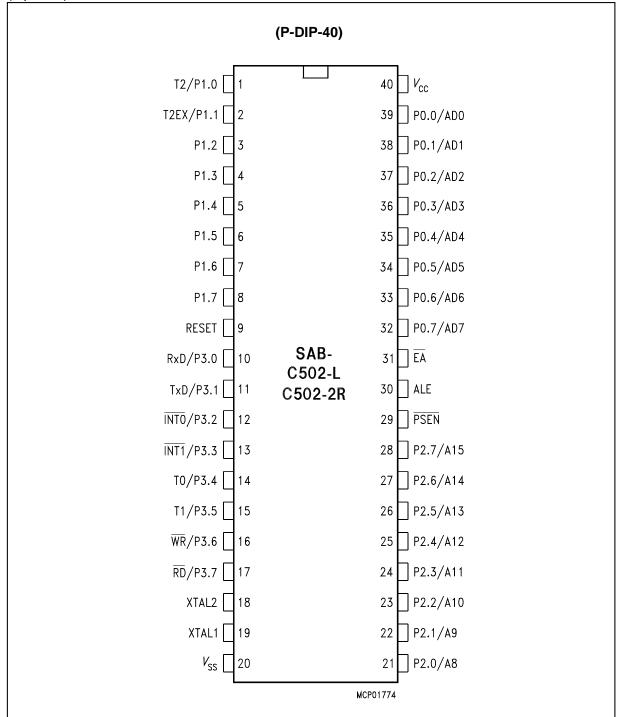

#### **Pin Configuration**

(top view)

### SIEMENS

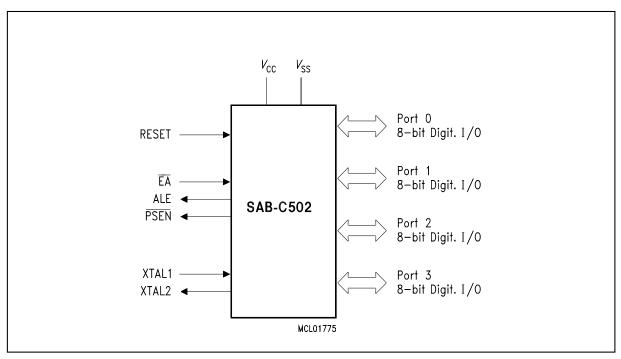

Logic Symbol

Downloaded from  $\underline{Elcodis.com}$  electronic components distributor

#### Pin Definitions and Functions

| Symbol      | Pin N    | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | P-LCC-44 | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1.7 – P1.0 | 9–2      | 8–1      | 1     | <b>Port 1</b><br>is a bidirectional I/O port with internal pull-up<br>resistors. Port 1 pins that have 1s written to<br>them are pulled high by the internal pull-up<br>resistors, and in that state can be used as<br>inputs. As inputs, port 1 pins being externally<br>pulled low will source current ( $I_{IL}$ , in the DC<br>characteristics) because of the internal pull-up<br>resistors. Port 1 also contains the timer 2 pins<br>as secondary function. The output latch corre-<br>sponding to a secondary function must be pro-<br>grammed to a one (1) for that function to<br>operate.<br>The secondary functions are assigned to the<br>pins of port 1, as follows: |

|             | 2<br>3   | 1<br>2   |       | P1.0 T2 Input to counter 2<br>P1.1 T2EX Capture - Reload trigger of<br>timer 2 / Up-Down count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

\*) I = Input O = Output

#### Pin Definitions and Functions (cont'd)

| Symbol      | Pin N     | umber    | I/O*) | Func                                                                                                    | tion                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-----------|----------|-------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | P-LCC-44  | P-DIP-40 |       |                                                                                                         |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P3.0 – P3.7 | 11, 13–19 | 10–17    | I/O   | resist<br>them<br>resist<br>inputs<br>pulled<br>chara<br>resist<br>timer,<br>pins t<br>put la<br>tion n | oidirecti<br>ors. Po<br>are pu<br>ors, an<br>s. As in<br>d low v<br>octeristic<br>ors. Po<br>ors. Po<br>, serial p<br>hat are<br>atch co | onal I/O port with internal pull-up<br>ort 3 pins that have 1s written to<br>ulled high by the internal pull-up<br>of in that state can be used as<br>puts, port 3 pins being externally<br>will source current ( $I_{IL}$ , in the DC<br>cs) because of the internal pull-up<br>ort 3 also contains the interrupt,<br>port 0 and external memory strobe<br>used by various options. The out-<br>rresponding to a secondary func-<br>programmed to a one (1) for that<br>perate. |

|             |           |          |       |                                                                                                         |                                                                                                                                          | ary functions are assigned to the<br>3, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 11        | 10       |       | P3.0                                                                                                    | R×D                                                                                                                                      | receiver data input<br>(asynchronous) or data input/<br>output (synchronous) of serial<br>interface 0                                                                                                                                                                                                                                                                                                                                                                            |

|             | 13        | 11       |       | P3.1                                                                                                    | T×D                                                                                                                                      | transmitter data output<br>(asynchronous) or clock output<br>(synchronous) of the serial<br>interface 0                                                                                                                                                                                                                                                                                                                                                                          |

|             | 14        | 12       |       | P3.2                                                                                                    | INT0                                                                                                                                     | interrupt 0 input/timer 0 gate control                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 15        | 13       |       | P3.3                                                                                                    | INT1                                                                                                                                     | interrupt 1 input/timer 1 gate control                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 16        | 14       |       | P3.4                                                                                                    | то                                                                                                                                       | counter 0 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 17        | 15       |       |                                                                                                         | T1                                                                                                                                       | counter 1 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 18        | 16       |       | P3.6                                                                                                    | WR                                                                                                                                       | the write control signal latches<br>the data byte from port 0 into the<br>external data memory                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 19        | 17       |       | P3.7                                                                                                    | RD                                                                                                                                       | the read control signal enables<br>the external data memory to<br>port 0                                                                                                                                                                                                                                                                                                                                                                                                         |

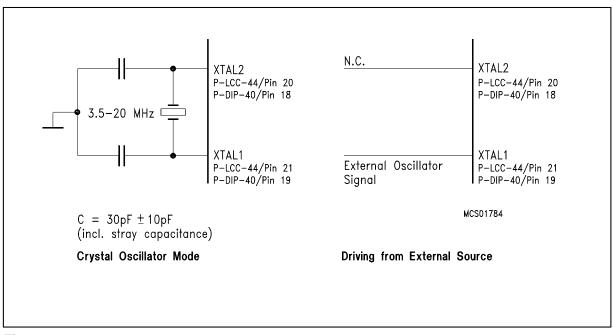

| XTAL2       | 20        | 18       | -     | XTAL<br>Outpu                                                                                           |                                                                                                                                          | e inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

\*)I = Input

O = Output

| Pin | Definitions | and | Functions | (cont'd) |

|-----|-------------|-----|-----------|----------|

|-----|-------------|-----|-----------|----------|

| Symbol      | Pin N    | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | P-LCC-44 | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL1       | 21       | 19       | -     | XTAL1<br>Input to the inverting oscillator amplifier and<br>input to the internal clock generator circuits.<br>To drive the device from an external clock<br>source, XTAL1 should be driven, while XTAL2<br>is left unconnected. There are no requirements<br>on the duty cycle of the external clock signal,<br>since the input to the internal clocking circuitry<br>is divided down by a divide-by-two flip-flop.<br>Minimum and maximum high and low times as<br>well as rise fall times specified in the AC<br>characteristics must be observed.                                                                                                                                                                                                                                                                                           |

| P2.0 – P2.7 | 24–31    | 21–28    | I/O   | <b>Port 2</b><br>ia a bidirectional I/O port with internal pull-up<br>resistors. Port 2 pins that have 1s written to<br>them are pulled high by the internal pull-up<br>resistors, and in that state can be used as<br>inputs. As inputs, port 2 pins being externally<br>pulled low will source current ( <i>I</i> <sub>IL</sub> , in the DC<br>characteristics) because of the internal pull-up<br>resistors. Port 2 emits the high-order address<br>byte during fetches from external program<br>memory and during accesses to external data<br>memory that use 16-bit addresses (MOVX<br>@DPTR). In this application it uses strong<br>internal pull-up resistors when issuing 1s.<br>During accesses to external data memory that<br>use 8-bit addresses (MOVX @Ri), port 2<br>issues the contents of the P2 special function<br>register. |

| PSEN        | 32       | 29       | 0     | The <b>Program Store Enable</b><br>output is a control signal that enables the<br>external program memory to the bus during<br>external fetch operations. It is activated every<br>six oscillator periodes except during external<br>data memory accesses. Remains high during<br>internal program execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

\*) I = Input O = Output

| Pin Definitions and Functions (cont'd |

|---------------------------------------|

|---------------------------------------|

| Symbol          | Pin N            | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------|------------------|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | P-LCC-44         | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RESET           | 10               | 9        | I     | <b>RESET</b><br>A high level on this pin for two machine cycles while the oscillator is running resets the device. An internal diffused resistor to $V_{\rm SS}$ permits power-on reset using only an external capacitor to $V_{\rm CC}$ .                                                                                                                                                                                                                                                                                                                 |  |

| ALE             | 33               | 30       | 0     | The Address Latch Enable<br>output is used for latching the low-byte of th<br>address into external memory during norma<br>operation. It is activated every six oscillator<br>periodes except during an external data<br>memory access.                                                                                                                                                                                                                                                                                                                    |  |

| ĒĀ              | 35               | 31       | I     | <b>External Access Enable</b><br>When held at high level, instructions are<br>fetched from the internal ROM (SAB-C502-2R<br>only) when the PC is less than 4000 <sub>H</sub> . When<br>held at low level, the SAB-C502 fetches all<br>instructions from external program memory.<br>For the SAB-C502-L this pin must be tied low.                                                                                                                                                                                                                          |  |

| P0.0 – P0.7     | 43–36            | 39–32    | I/O   | Port 0<br>is an 8-bit open-drain bidirectional I/O port.<br>Port 0 pins that have 1s written to them float<br>and in that state can be used as high-<br>impedance inputs. Port 0 is also the<br>multiplexed low-order address and data bus<br>during accesses to external program or data<br>memory. In this application it uses strong<br>internal pull-up resistors when issuing 1s.<br>Port 0 also outputs the code bytes during<br>program verification in the SAB-C502-2R.<br>External pull-up resistors are required during<br>program verification. |  |

| V <sub>SS</sub> | 22               | 20       | -     | Circuit ground potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| V <sub>cc</sub> | 44               | 40       | -     | Supply terminal for all operating modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| N.C.            | 1, 12,<br>23, 34 | -        | -     | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

\*) I = Input O = Output

#### **Functional Description**

The SAB-C502 is fully compatible to the standard 8051 microcontroller family.

It is compatible with the SAB 80C52. While maintaining all architectural and operational characteristics of the SAB 80C52 the SAB-C502 incorporates some enhancements in the Timer2 and Fail Save Mechanism Unit.

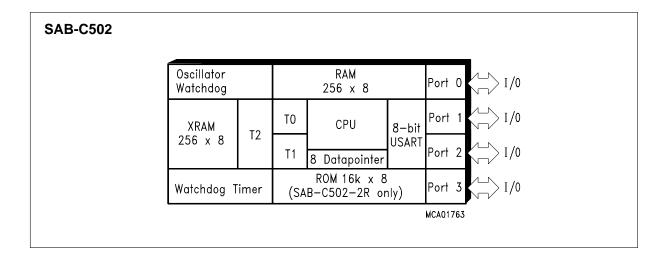

Figure 1 shows a block diagram of the SAB-C502.

#### CPU

The SAB-C502 is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and 15 % three-byte instructions. With a 12 MHz crystal, 58 % of the instructions execute in 1.0  $\mu$ s (18 MHz : 667 ns).

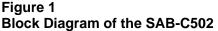

#### **Special Function Register PSW**

| Bit Function |     | Function                                                                                                                                              |  |  |  |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CY           |     | Carry Flag                                                                                                                                            |  |  |  |

| AC           |     | Auxiliary Carry Flag (for BCD operations)                                                                                                             |  |  |  |

| F0           |     | General Purpose Flag                                                                                                                                  |  |  |  |

| RS1          | RS0 | Register Bank select control bits                                                                                                                     |  |  |  |

| 0            | 0   | Bank 0 selected, data address 00 <sub>H</sub> - 07 <sub>H</sub>                                                                                       |  |  |  |

| 0            | 1   | Bank 1 selected, data address 08 <sub>H</sub> - 0F <sub>H</sub>                                                                                       |  |  |  |

| 1            | 0   | Bank 2 selected, data address 10 <sub>H</sub> - 17 <sub>H</sub>                                                                                       |  |  |  |

| 1            | 1   | Bank 3 selected, data address 18 <sub>H</sub> - 1F <sub>H</sub>                                                                                       |  |  |  |

| ov           |     | Overflow Flag                                                                                                                                         |  |  |  |

| F1           |     | General Purpose Flag                                                                                                                                  |  |  |  |

| P            |     | Parity Flag.<br>Set/cleared by hardware each instruction cycle to indicate an odd/<br>even number of "one" bits in the accumulator, i.e. even parity. |  |  |  |

Reset value of PSW is 00H.

#### **Special Function Registers**

All registers, except the program counter and the four general purpose register banks, reside in the special function register area.

The 36 special function register (SFR) include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. There are also 128 directly addressable bits within the SFR area.

All SFRs are listed in **table 1**, **table 2** and **table 3**. In **table 1** they are organized in numeric order of their addresses. In **table 2** they are organized in groups which refer to the functional blocks of the SAB-C502. **Table 3** illustrates the contents of the SFRs.

| Address         | Register                | Contents<br>after Reset            | Address         | Register                | Contents<br>after Reset            |

|-----------------|-------------------------|------------------------------------|-----------------|-------------------------|------------------------------------|

| 80 <sub>H</sub> | <b>P0</b> <sup>1)</sup> | FF <sub>H</sub>                    | 98 <sub>H</sub> | SCON <sup>1)</sup>      | 00 <sub>H</sub>                    |

| 81 <sub>H</sub> | SP                      | 07 <sub>H</sub>                    | 99 <sub>H</sub> | SBUF                    | XX <sub>H</sub> <sup>2)</sup>      |

| 82 <sub>H</sub> | DPL                     | 00 <sub>H</sub>                    | 9A <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 83 <sub>H</sub> | DPH                     | 00 <sub>H</sub>                    | 9B <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 84 <sub>H</sub> | reserved                |                                    | 9CH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 85 <sub>H</sub> | reserved                |                                    | 9D <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 86 <sub>H</sub> | WDTREL                  | 00 <sub>H</sub>                    | 9E <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 87 <sub>H</sub> | PCON                    | 000X0000B <sup>2)</sup>            | 9F <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 88 <sub>H</sub> | TCON 1)                 | 00 <sub>H</sub>                    | A0 <sub>H</sub> | <b>P2</b> <sup>1)</sup> | FFH                                |

| 89 <sub>H</sub> | TMOD                    | 00 <sub>H</sub>                    | A1 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 8AH             | TL0                     | 00 <sub>H</sub>                    | A2 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 8BH             | TL1                     | 00 <sub>H</sub>                    | A3 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 8CH             | TH0                     | 00 <sub>H</sub>                    | A4 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 8DH             | TH1                     | 00 <sub>H</sub>                    | A5 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 8EH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      | A6 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 8F <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | A7 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 90 <sub>H</sub> | <b>P1</b> <sup>1)</sup> | FF <sub>H</sub>                    | A8 <sub>H</sub> | IE <sup>1)</sup>        | 0X00000 <sub>B</sub> <sup>2)</sup> |

| 91 <sub>H</sub> | XPAGE                   | 00H                                | A9 <sub>H</sub> | reserved                | XX <sub>H<sup>2)</sup></sub>       |

| 92 <sub>H</sub> | DPSEL                   | XXXXX000 <sub>B<sup>2)</sup></sub> | AAH             | SRELL                   | D9 <sub>H</sub>                    |

| 93 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | ABH             | reserved                | XXH <sup>2)</sup>                  |

| 94 <sub>H</sub> | XCON                    | F8 <sub>H</sub>                    | ACH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 95 <sub>H</sub> | reserved                | XXH <sup>2)</sup>                  | ADH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 96 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | AEH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

| 97 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | AFH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      |

### Table 1Special Function Register in Numeric Order of their Addresses

<sup>1)</sup>: Bit-addressable Special Function Register

2): X means that the value is indeterminate and the location is reserved

| Decial Function Register in Numeric Order of their Addresses (cont'd)         Address       Register       Contents       Address       Register       Contents |                         |                               |                 |          |                               |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|-----------------|----------|-------------------------------|--|--|

| Address                                                                                                                                                         | Register                | after Reset                   | Address         | Register | after Reset                   |  |  |

| B0 <sub>H</sub>                                                                                                                                                 | <b>P3</b> <sup>1)</sup> | FF <sub>H</sub>               | D8 <sub>H</sub> | BAUD     | 0XXXXXXXB <sup>2</sup>        |  |  |

| в1 <sub>Н</sub>                                                                                                                                                 | SYSCON                  | XXXXXX01B <sup>2)</sup>       | D9 <sub>H</sub> | reserved | XX <sub>H<sup>2)</sup></sub>  |  |  |

| B2 <sub>H</sub>                                                                                                                                                 | reserved                | XX <sub>H</sub> <sup>2)</sup> | DAH             | reserved | XX <sub>H</sub> <sup>2)</sup> |  |  |

| B3 <sub>H</sub>                                                                                                                                                 | reserved                | XX <sub>H</sub> <sup>2)</sup> | DBH             | reserved | XX <sub>H</sub> <sup>2)</sup> |  |  |

| D4                                                                                                                                                              | recerved                | $\mathbf{V}\mathbf{V}$ (2)    |                 | record   | <b>VV</b> 2)                  |  |  |

Table 1

| B1 <sub>H</sub>                                                                                                                                                                                                              | SYSCON                                                                                                             | XXXXXX01B <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                             | D9 <sub>H</sub>                                                                                                                                                                                                                  | reserved                                                                                                                         | XX <sub>H<sup>2)</sup></sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B2 <sub>H</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | DA <sub>H</sub>                                                                                                                                                                                                                  | reserved                                                                                                                         | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B3 <sub>H</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | DBH                                                                                                                                                                                                                              | reserved                                                                                                                         | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B4 <sub>H</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | DCH                                                                                                                                                                                                                              | reserved                                                                                                                         | XX <sub>H<sup>2)</sup></sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B5 <sub>Н</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | DDH                                                                                                                                                                                                                              | reserved                                                                                                                         | XX <sub>H<sup>2)</sup></sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| N6 <sub>H</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | DEH                                                                                                                                                                                                                              | reserved                                                                                                                         | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B7 <sub>H</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | DF <sub>H</sub>                                                                                                                                                                                                                  | reserved                                                                                                                         | XX <sub>H<sup>2)</sup></sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B8 <sub>H</sub>                                                                                                                                                                                                              | <b>IP</b> <sup>1)</sup>                                                                                            | X000000 <sub>B</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                  | E0 <sub>H</sub>                                                                                                                                                                                                                  | <b>ACC</b> <sup>1)</sup>                                                                                                         | 00 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| B9 <sub>H</sub>                                                                                                                                                                                                              | reserved                                                                                                           | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       | E1 <sub>H</sub>                                                                                                                                                                                                                  | reserved                                                                                                                         | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

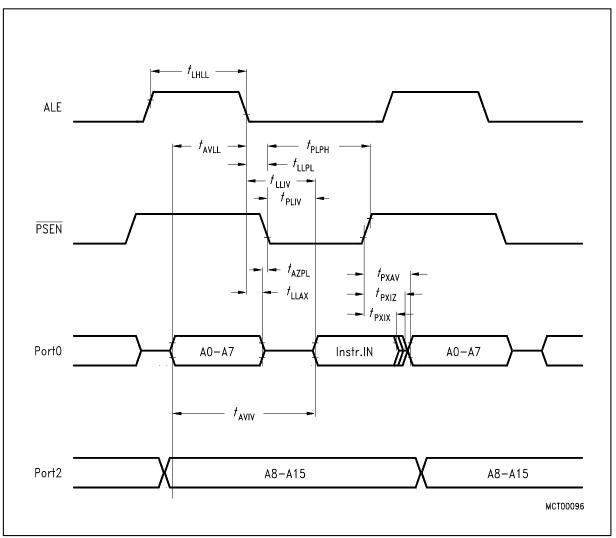

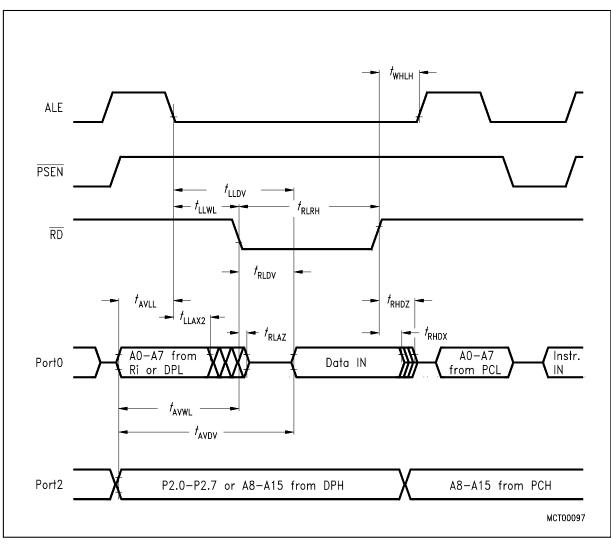

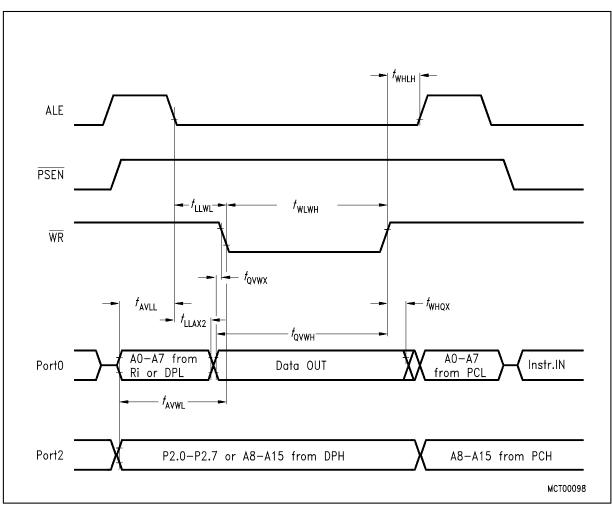

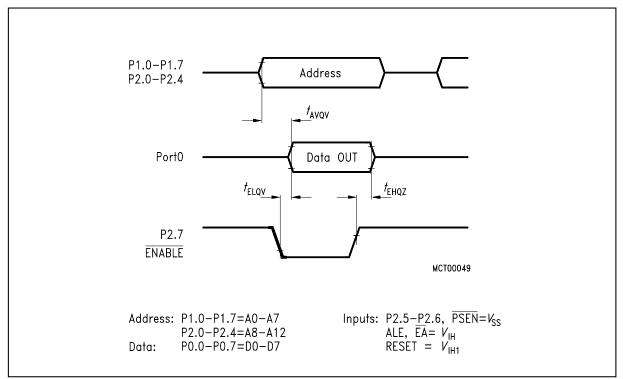

| BA <sub>H</sub>                                                                                                                                                                                                              | SRELH                                                                                                              | XXXXXXX11 <sub>B<sup>2)</sup></sub>                                                                                                                                                                                                                                                                                                                                                                                                                 | E2 <sub>H</sub>                                                                                                                                                                                                                  | reserved                                                                                                                         | XX <sub>H</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |