# YSS944/943/940

## **ADAMB**

Advanced Digital Audio Multi channel decode processor

#### Outline

The YSS944 (ADAMB-f)/YSS943 (ADAMB-b)/YSS940 (ADAMB-nd) is an audio decoding digital signal processor that integrates onto a single chip the various digital signal processing functions required for AV amplifiers, etc. It includes an advanced 32-bit floating-point DSP and is able to decode a variety of audio formats.

#### [Note]

- The contents described in this manual are implemented by downloading boot firmware. For detailed information about the boot firmware, please contact YAMAHA.

- The YSS943 cannot execute DTS-ES and DTS Neo:6 decoding.

- The YSS940 cannot execute any decoding related to DTS (DTS, DTS-ES, DTS 96/24, and DTS Neo:6).

#### ■ Features

- Supports various types of decoding up to 7.1 channels (5.1/6.1/7.1 channels selectable).

- 5.1-channel decoding of Dolby Digital (AC-3), DTS, AAC.

- 6.1-channel decoding of Dolby Digital EX, DTS-ES.

- DTS 96/24 decoding and audio interface clock division/switching functions.

- Dolby Pro Logic IIx and DTS Neo:6 decoding

- Tone control and bass management functions

- Function modification/expansion by downloading firmware to on-chip memory

- Lip-sync function that enables synchronization of voice and video with variable voice delay

- Supports sampling frequencies up to 192 kHz during PCM playback.

- 1/2 down sampling function when two PCM channels are played back

- Dolby Digital/DTS/AAC decode information output function (can be read by microprocessor)

- High-speed/high-accuracy operation by 32-bit floating-point DSP

Operating frequency: 180 MHz (178.176 MHz)

Data bus width: 32 bits (24-bit mantissa and 8-bit exponent)

Multiplier/adder: 32 bits  $\times$  32 bits + 55 bits  $\rightarrow$  55 bits (47-bit mantissa and 8-bit exponent)

- No external memory needed (external memory is used when delay is increased.)

- Eight general I/O ports

- On-chip PLL for generation of high-speed internal operating clock

- Supply voltage: 1.2 V (core block) and 3.3 V (pin block)

- Low power consumption: about 210 mW (standard value during Dolby Digital decoding)

- Si-gate CMOS process

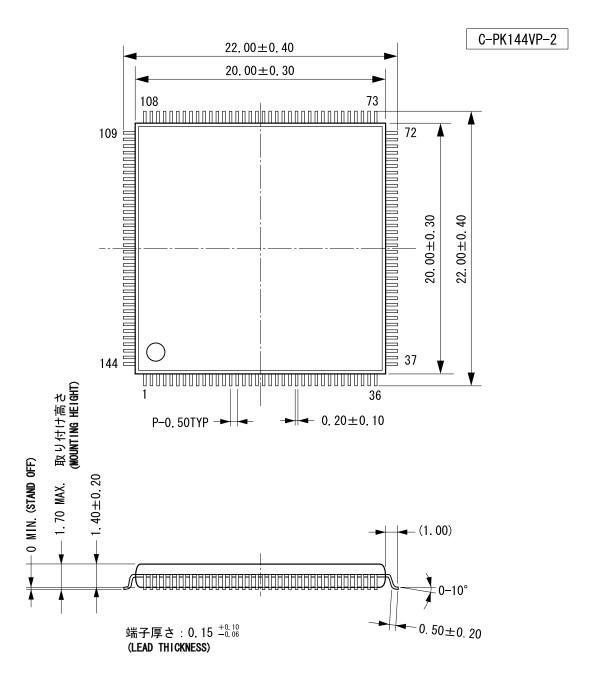

- Lead-free plating LQFP144 package (YSS944-VZ, YSS943-VZ, and YSS940-VZ)

#### [Note]

"Dolby," "Dolby Pro Logic IIx," and "AC-3" are trademarks of Dolby Laboratories. "DTS," "DTS-ES," "DTS 96/24," and "DTS Neo:6" are trademarks of Digital Theater Systems, Inc.

#### D15, D15 D5, D16 76/21, and D16 100.0 are diademarks 01 Digital Theater Systems, the

#### Applications

- AV amplifiers for home theaters

- Car audio systems

YAMAHA CORPORATION

YSS944/943/940 CATALOG CATALOG No.: LSI-4SS944A31

2005.6

## ■ YSS944/943/940 functional comparison

## **Decoder functional comparison**

| devise              | YSS944 | YSS943 | YSS940 |

|---------------------|--------|--------|--------|

| Dolby Digital       | YES    | YES    | YES    |

| Dolby Digital EX    | YES    | YES    | YES    |

| Dolby Pro Logic IIx | YES    | YES    | YES    |

| AAC                 | YES    | YES    | YES    |

| DTS                 | YES    | YES    | NO     |

| DTS 96/24           | YES    | YES    | NO     |

| DTS-ES              | YES    | NO     | NO     |

| DTS Neo:6           | YES    | NO     | NO     |

## YSS944/943/940 common functions

| Input channel selection  |

|--------------------------|

| Volume adjustment        |

| Tone Control             |

| Bass Management          |

| User mute                |

| Auto mute                |

| Input delay              |

| Output delay             |

| Stream detection         |

| Noise generation         |

| Impulse generation       |

| General purpose I/O port |

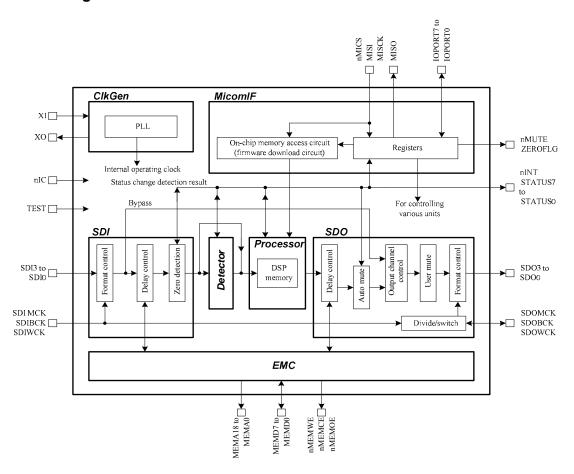

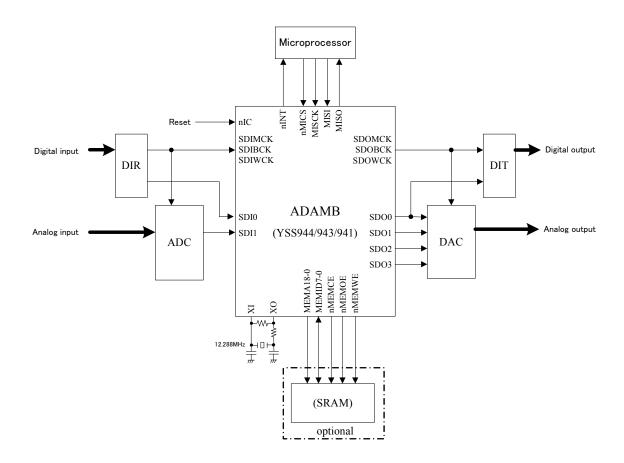

## **■** Block Diagram

| Block Name | Function                                                                   |

|------------|----------------------------------------------------------------------------|

| ClkGen     | This is the internal operating clock generation block.                     |

| CikGen     | This block provides the PLL and supplies the clock to each block.          |

| MicomIF    | This is an interface block to connect to a microprocessor.                 |

| WIICOIIIIF | This block controls access to the registers/memory in this LSI.            |

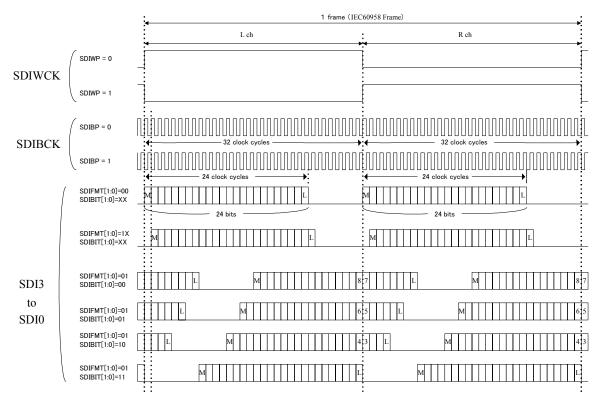

| SDI        | This is the audio interface block for DIR, ADC, etc.                       |

| SDI        | This block controls the input data format/delay, etc.                      |

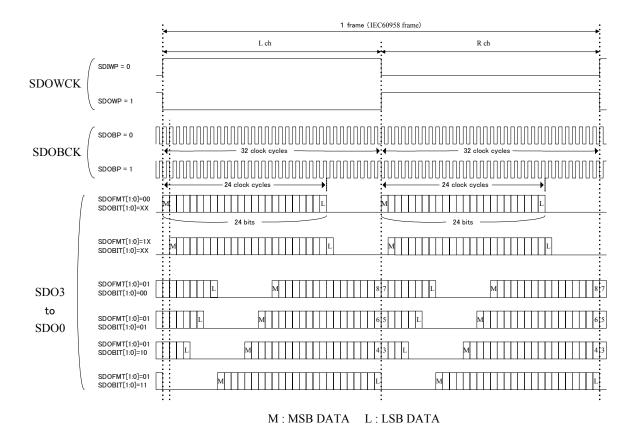

| SDO        | This is the audio interface block for DIT, DAC, etc.                       |

| SDO        | This block controls the output data format/delay, etc.                     |

| Detector   | This is the stream detection block.                                        |

| Detector   | This block detects the input data encoding format.                         |

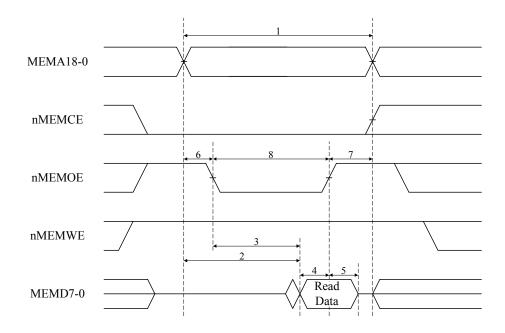

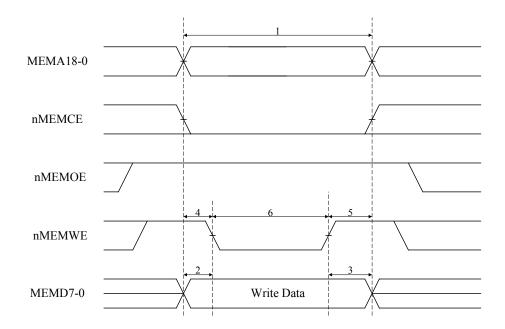

| EMC        | This is an interface block to read from and write to external memory.      |

| ENIC       | This block implements delay functions using external memory.               |

|            | This is an operation processing block.                                     |

| Decorate   | This decoder includes a 32-bit floating-point DSP and memory (ROM or RAM). |

| Processor  | Various functions can be implemented.                                      |

|            | Function modification/expansion by downloading firmware is also supported. |

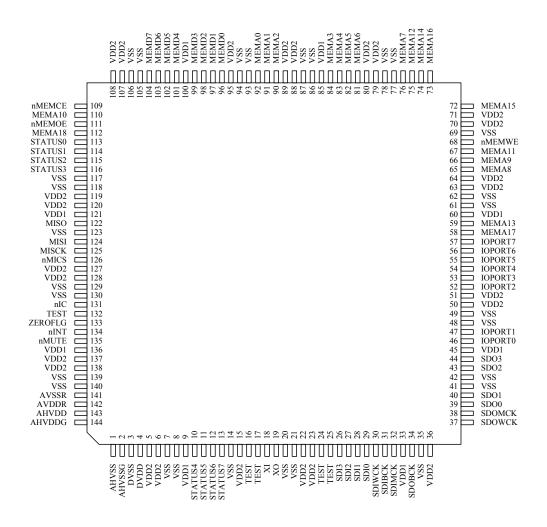

## ■ Pin Configuration

< LQFP 144 TOP VIEW >

## YSS944/943/940

## **■** Pin Functions

| Type         | Pin        | Pin Name      | I/O     | Function                                                                                                                  |

|--------------|------------|---------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| 1 ype        | No.        | 1 III INAIIIE | Note 1) | FullCtion                                                                                                                 |

| Power supply | 9          | VDD1          | -       | Power supply pins for pin block (Typ. 3.3 V).                                                                             |

| 11.5         | 33         |               |         |                                                                                                                           |

|              | 45         |               |         |                                                                                                                           |

|              | 60         |               |         |                                                                                                                           |

|              | 85         |               |         |                                                                                                                           |

|              | 100        |               |         |                                                                                                                           |

|              | 121        |               |         |                                                                                                                           |

|              | 136        | LIDDA         |         | D 1 1 (T 121)                                                                                                             |

|              | 5          | VDD2          | -       | Power supply pins for core block (Typ. 1.2 V).                                                                            |

|              | 6          |               |         |                                                                                                                           |

|              | 15<br>22   |               |         |                                                                                                                           |

|              | 23         |               |         |                                                                                                                           |

|              | 36         |               |         |                                                                                                                           |

|              | 50         |               |         |                                                                                                                           |

|              | 51         |               |         |                                                                                                                           |

|              | 63         |               |         |                                                                                                                           |

|              | 64         |               |         |                                                                                                                           |

|              | 70         |               |         |                                                                                                                           |

|              | 71         |               |         |                                                                                                                           |

|              | 79         |               |         |                                                                                                                           |

|              | 80         |               |         |                                                                                                                           |

|              | 88         |               |         |                                                                                                                           |

|              | 89         |               |         |                                                                                                                           |

|              | 95         |               |         |                                                                                                                           |

|              | 107<br>108 |               |         |                                                                                                                           |

|              | 119        |               |         |                                                                                                                           |

|              | 120        |               |         |                                                                                                                           |

|              | 127        |               |         |                                                                                                                           |

|              | 128        |               |         |                                                                                                                           |

|              | 137        |               |         |                                                                                                                           |

|              | 138        |               |         |                                                                                                                           |

|              | 142        | AVDDR         | -       | Power supply pin 1 for PLL analog block (Typ. 3.3 V).                                                                     |

|              |            |               |         | Be sure to insert a 0.1 $\mu$ F capacitor between the AVDDR and AVSSR pins.                                               |

|              | 143        | AHVDD         | -       | Power supply pin 2 for PLL analog block (Typ. 3.3 V).                                                                     |

|              |            |               |         | Be sure to insert a 0.1 $\mu$ F capacitor between the AHVDD and AHVSS                                                     |

|              | 1          | A THURS C     |         | pins.                                                                                                                     |

|              | 144        | AHVDDG        | -       | Power supply pin 3 for PLL analog block (Typ. 3.3 V).<br>Be sure to insert a 0.1 $\mu$ F capacitor between the AHVDDG and |

|              |            |               |         | AHVSSG pins.                                                                                                              |

|              | 4          | DVDD          | _       | Power supply pin for PLL digital block (Typ. 1.2 V).                                                                      |

|              |            | 2.00          |         | Be sure to insert a 0.1 $\mu$ F capacitor between the DVDD and DVSS                                                       |

|              |            |               |         | pins.                                                                                                                     |

|              | 7          | VSS           | -       | Ground pins                                                                                                               |

|              | 8          |               |         |                                                                                                                           |

|              | 14         |               |         |                                                                                                                           |

|              | 20         |               |         |                                                                                                                           |

|              | 21         |               |         |                                                                                                                           |

|              | 35         |               |         |                                                                                                                           |

|              | 41 42      |               |         |                                                                                                                           |

|              | 48         |               |         |                                                                                                                           |

|              | 49         |               |         |                                                                                                                           |

| L            | 17         | l .           | l       |                                                                                                                           |

| Second pin 2 for PLL analog block   Resure to insert a 0.1 plc capacitor between the AHVDD and AHVSS pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Туре            | Pin<br>No. | Pin Name | I/O<br>Note 1) | Function                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|----------|----------------|-----------------------------------------------------------------------|

| G2   69   77   78   86   87   93   94   105   106   117   118   123   129   130   139   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140      |                 |            |          | Note 1)        |                                                                       |

| Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |            |          |                |                                                                       |

| Proceedings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |            |          |                |                                                                       |

| Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |            |          |                |                                                                       |

| ST   93   94   105   106   117   118   123   129   130   139   140   139   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   1   |                 |            |          |                |                                                                       |

| Part      |                 | 86         |          |                |                                                                       |

| Part      |                 | 87         |          |                |                                                                       |

| 105   106   117   118   123   129   130   140   140   140   150   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140    |                 | 93         |          |                |                                                                       |

| The content of the    |                 | 94         |          |                |                                                                       |

| 117   118   123   130   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140    |                 |            |          |                |                                                                       |

| Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |            |          |                |                                                                       |

| 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |            |          |                |                                                                       |

| 130   130   130   130   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140    |                 |            |          |                |                                                                       |

| 130   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140   140    |                 |            |          |                |                                                                       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |            |          |                |                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |            |          |                |                                                                       |

| AHVSS   Ground pin 2 for PLL analog block. Be sure to insert a 0.1 µF capacitor between the AHVDD and AHVSS pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1               |            |          |                |                                                                       |

| AHVSSG   Ground pin 3 for PLL analog block. Be sure to insert a 0.1 µF capacitor between the AHVDDG and AHVSSG pins.    3 DVSS   Ground pin for PLL digital block. Be sure to insert a 0.1 µF capacitor between the DVDD and DVSS pins.    141 AVSSR   Ground pin 1 for PLL digital block. Be sure to insert a 0.1 µF capacitor between the DVDD and DVSS pins.    141 AVSSR   Ground pin 1 for PLL analog block. Be sure to insert a 0.1 µF capacitor between the AVDDR and AVSSR pins.    141 AVSSR   Ground pin 1 for PLL analog block. Be sure to insert a 0.1 µF capacitor between the AVDDR and AVSSR pins.    141 AVSSR   Hardware reset input pin The LSI is initialized when this pin is at low level.    15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |            | AHVSS    |                | Ground pin 2 for PLL analog block.                                    |

| AHVSSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |            |          |                | Be sure to insert a 0.1 $\mu$ F capacitor between the AHVDD and AHVSS |

| Be sure to insert a 0.1 µF capacitor between the AHVDDG and AHVSSG pins.  3 DVSS Ground pin for PLL digital block. Be sure to insert a 0.1 µF capacitor between the DVDD and DVSS pins.  141 AVSSR Ground pin 1 for PLL analog block. Be sure to insert a 0.1 µF capacitor between the AVDDR and AVSSR pins.  Initial clear 131 nIC Is Hardware reset input pin The LSI is initialized when this pin is at low level.  Clock 18 XI I Clock input pin. Connect this pin as shown in the circuit example Note 2) of the 12.288 MHz crystal oscillator. If not connected to a crystal oscillator, input a 12.288 MHz clock to this pin.  19 XO O This is the output pin for the crystal oscillator. Connect this pin as shown in the circuit example Note 2). If not connected to a crystal oscillator and inputting directly to the XI pin, do not connect anything to this pin. Do not use this pin for any purpose other than clock oscillation.  Microprocessor interface  126 nMICS Is This is the microprocessor interface's chip select input pin. Input to the MISCK and MISI pins becomes valid when this pin is at low level.  125 MISCK Is This is the microprocessor interface's clock input pin. Input to the MISCK and MISI pins becomes valid when this pin is at low level.  Audio interface  32 SDIMCK Is This is the microprocessor interface's data output pin. Connect a pull-up resistor. This is the microprocessor interface's data output pin. Connect a pull-up resistor. This is the microprocessor interface's data output pin. Connect a pull-up resistor. The highest clock frequency that can be input is 25 MHz. (The clock rate is 512 fs when the input sampling frequency is 48 kHz or less, 256 fs when the frequency is 96 kHz, and 128 fs when the frequency is up to 192 kHz.)                                                                              |                 |            |          |                | pins.                                                                 |

| AHVSSG pins.   Ground pin for PLL digital block.   Be sure to insert a 0.1 µF capacitor between the DVDD and DVSS pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | 2          | AHVSSG   |                |                                                                       |

| AVSSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |            |          |                | • -                                                                   |

| Be sure to insert a 0.1 µF capacitor between the DVDD and DVSS pins.    141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |            | DVCC     |                | •                                                                     |

| AVSSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | 3          | DV 55    |                |                                                                       |

| Initial clear   131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |            |          |                | ·                                                                     |

| Initial clear  Initia |                 | 141        | AVSSR    |                | •                                                                     |

| Initial clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |            |          |                |                                                                       |

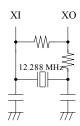

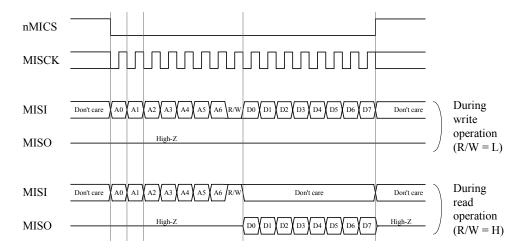

| Clock  18 XI  I Clock input pin. Connect this pin as shown in the circuit example Note 2) of the 12.288 MHz crystal oscillator, input a 12.288 MHz clock to this pin.  19 XO  O This is the output pin for the crystal oscillator. Connect this pin as shown in the circuit example Note 2). If not connected to a crystal oscillator and inputting directly to the XI pin, do not connect anything to this pin. Do not use this pin for any purpose other than clock oscillation.  Microprocessor interface  126 nMICS  Is This is the microprocessor interface's chip select input pin. Input to the MISCK and MISI pins becomes valid when this pin is at low level.  125 MISCK  Is This is the microprocessor interface's clock input pin. Input to the MISCK and MISI pins becomes valid when this pin is at low level.  This is the microprocessor interface's clock input pin. This is the microprocessor interface's address read/write control and data input pin.  Audio interface  32 SDIMCK  Is This is the microprocessor interface's data output pin. Connect a pull-up resistor.  The inject clock input pin for the audio interface's input side. The master clock is input from DIR, ADC, etc. The highest clock frequency that can be input is 25 MHz. (The clock rate is 512 fs when the input sampling frequency is 48 kHz or less, 256 fs when the frequency is 96 kHz, and 128 fs when the frequency is up to 192 kHz.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |            |          |                | pins.                                                                 |

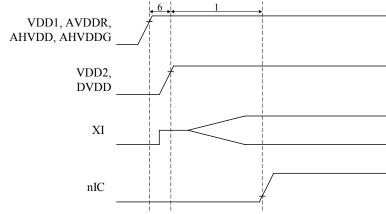

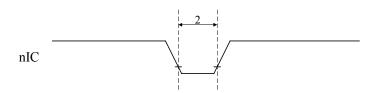

| Clock    18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Initial clear   | 131        | nIC      | Is             |                                                                       |

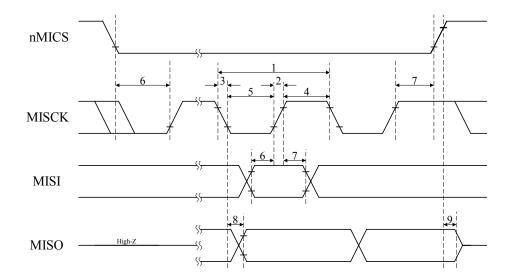

| Connect this pin as shown in the circuit example Note 2) of the 12.288 MHz crystal oscillator. If not connected to a crystal oscillator, input a 12.288 MHz clock to this pin.  19 XO O This is the output pin for the crystal oscillator. Connect this pin as shown in the circuit example Note 2). If not connected to a crystal oscillator and inputting directly to the XI pin, do not connect anything to this pin. Do not use this pin for any purpose other than clock oscillation.  Microprocessor interface  126 nMICS Is This is the microprocessor interface's chip select input pin. Input to the MISCK and MISI pins becomes valid when this pin is at low level.  125 MISCK Is This is the microprocessor interface's clock input pin. 124 MISI I This is the microprocessor interface's address read/write control and data input pin.  128 MISO Ot This is the microprocessor interface's data output pin. Connect a pull-up resistor.  This is the master clock input pin for the audio interface's input side. The master clock is input from DIR, ADC, etc. The highest clock frequency that can be input is 25 MHz. (The clock rate is 512 fs when the input sampling frequency is 48 kHz or less, 256 fs when the frequency is 96 kHz, and 128 fs when the frequency is up to 192 kHz.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |            |          |                |                                                                       |

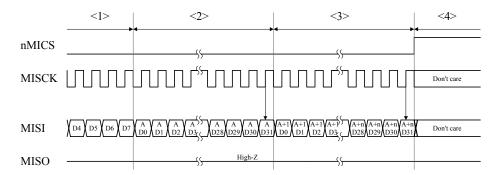

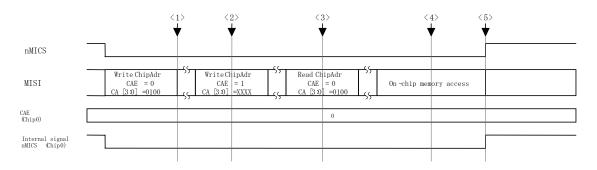

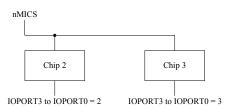

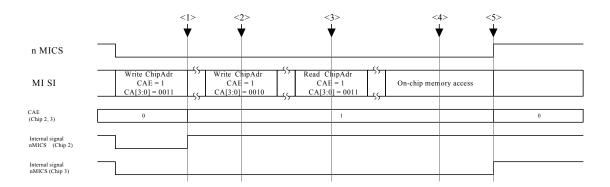

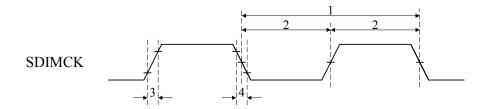

| 12.288 MHz crystal oscillator. If not connected to a crystal oscillator, input a 12.288 MHz clock to this pin.    19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Clock           | 18         | XI       | I              |                                                                       |