**Features**

## Windows Vista-Compliant, Stereo Class AB Speaker **Amplifiers and DirectDrive Headphone Amplifiers**

### **General Description**

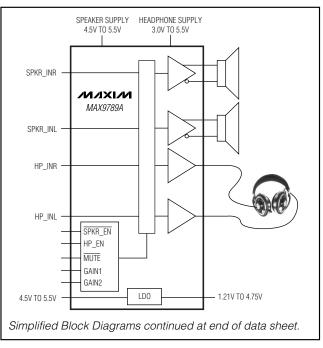

The MAX9789A/MAX9790A combine a stereo, 2W Class AB speaker power amplifier with a stereo 100mW DirectDrive™ headphone amplifier in a single device. The MAX9789A/MAX9790A are designed for use with the Microsoft Windows Vista™ operating system and are fully compliant with Microsoft's Windows Vista specifications. The headphone amplifier features Maxim's patented DirectDrive architecture that produces a ground-referenced output from a single supply to eliminate the need for large DC-blocking capacitors, as well as save cost, board space, and component height. A high +90dB PSRR and low 0.002% THD+N ensures clean, low-distortion amplification of the audio signal.

Separate speaker and headphone amplifier control inputs provide independent shutdown of the speaker and headphone amplifiers, allowing speaker and headphone amplifiers to be active simultaneously, if required. The industry-leading click-and-pop suppression circuitry reduces audible transients during startup and shutdown cycles.

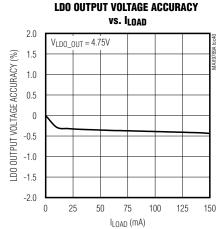

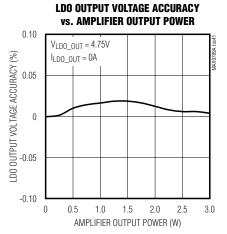

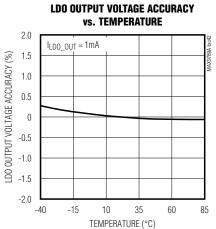

The MAX9789A features an internal LDO that can be used as a clean power supply for a CODEC or other circuits. The LDO output voltage is set internally at 4.75V or can be adjusted between 1.21V and 4.75V using a simple resistive divider. The LDO is protected against thermal overloads and short circuits while providing 120mA of continuous output current and can be enabled independently of the audio amplifiers.

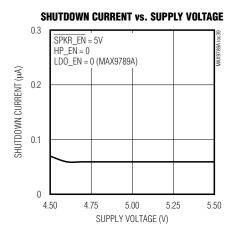

By disabling the speaker and headphone amplifiers, and the LDO (for MAX9789A), the MAX9789A/MAX9790A enter low-power shutdown mode and draw only 0.3µA.

The MAX9789A/MAX9790A operate from a single 4.5V to 5.5V supply and feature thermal-overload and output short-circuit protection. Devices are specified over the -40°C to +85°C extended temperature range.

### **Applications**

Notebook Computers

Tablet PCs

Portable Multimedia Players

Pin Configurations appear at end of data sheet.

†U.S. Patent # 7,061,327

Windows Vista is a trademark of Microsoft Corp.

#### ♦ Microsoft Windows Vista Compliant

- ◆ Class AB 2W Stereo BTL Speaker Amplifier

- 100mW DirectDrive Headphone Amplifier Eliminates Costly, Bulky DC-Blocking Capacitors

- **♦ Excellent RF Immunity**

- ♦ Integrated 120mA LDO (MAX9789A)

- ♦ High +90dB PSRR, Low 0.002% THD+N

- **♦ Low-Power Shutdown Mode**

- **♦ Click-and-Pop Suppression**

- ♦ Short-Circuit and Thermal-Overload Protection

- ♦ ±8kV ESD-Protected Headphone Driver Outputs

- Available in 32-Pin Thin QFN (5mm x 5mm x 0.8mm) Package

### **Ordering Information**

| PART         | PIN-PACKAGE     | INTERNAL<br>LDO | PKG<br>CODE |  |  |

|--------------|-----------------|-----------------|-------------|--|--|

| MAX9789AETJ+ | 32 Thin QFN-EP* | Yes             | T3255N-1    |  |  |

| MAX9790AETJ+ | 32 Thin QFN-EP* | No              | T3255N-1    |  |  |

**Note:** All devices are specified over the -40°C to +85°C extended temperature range.

+Denotes lead-free package.

\*EP = Exposed paddle.

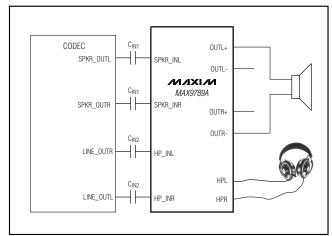

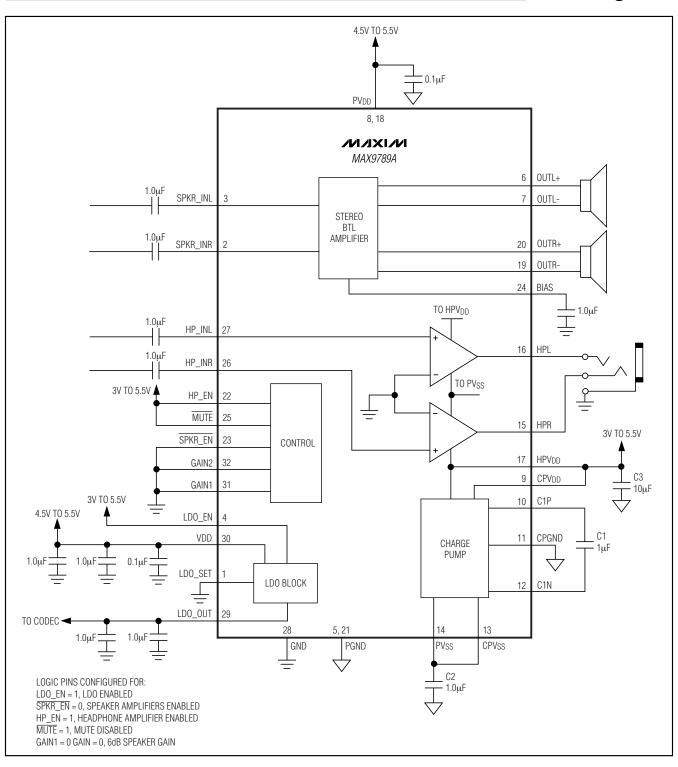

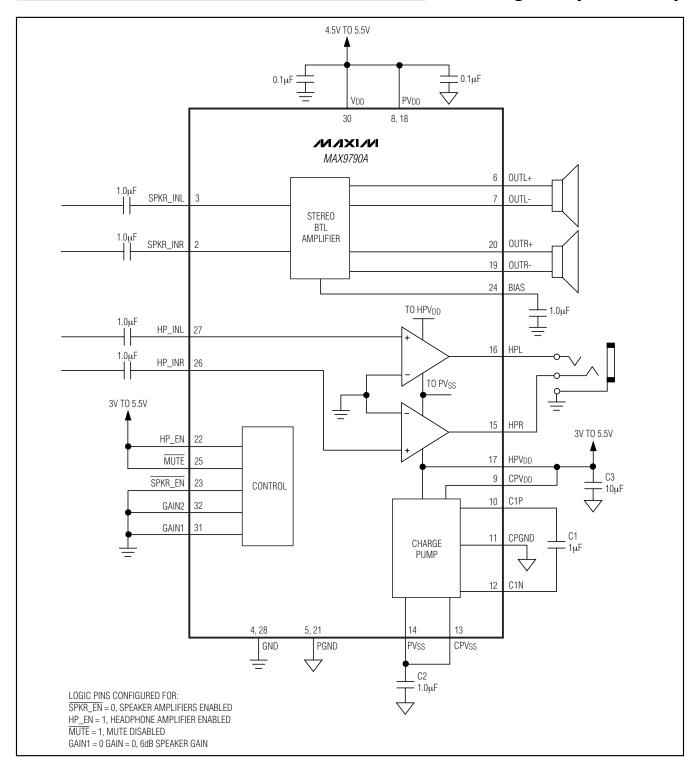

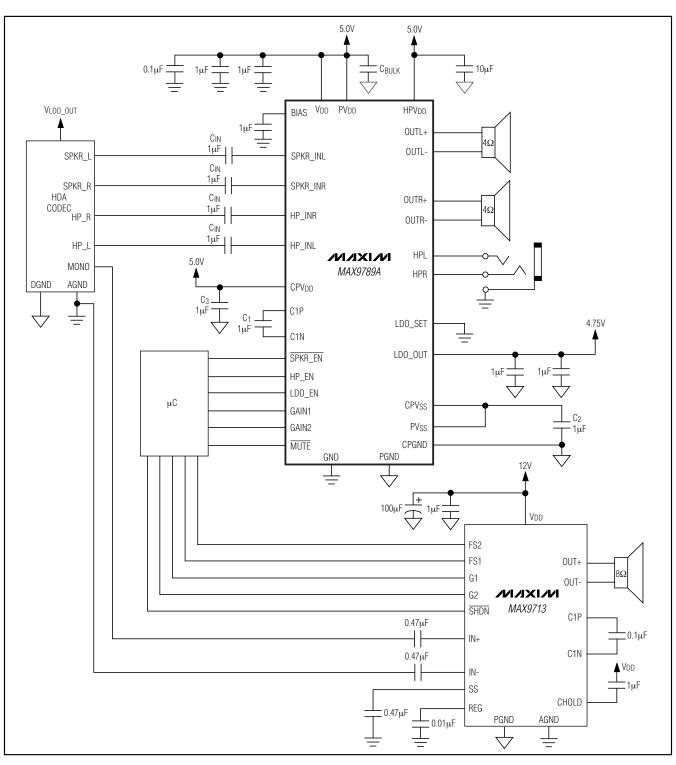

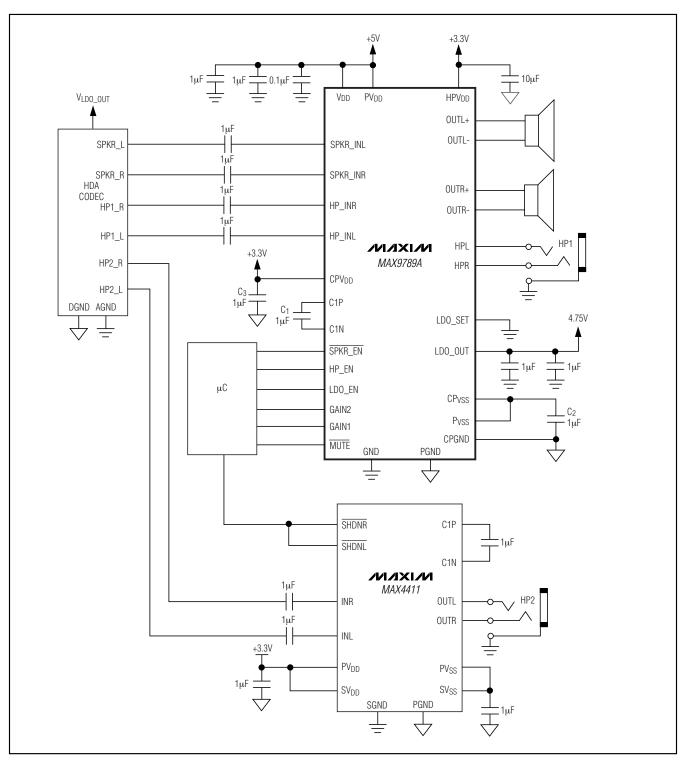

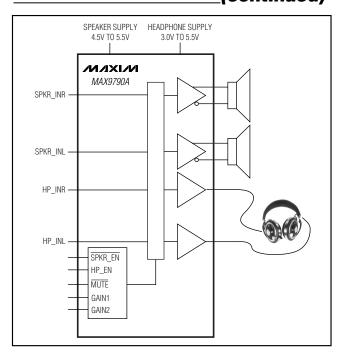

### Simplified Block Diagrams

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>DD</sub> , PV <sub>DD</sub> , HPV <sub>DD</sub> , |                             |

|--------------------------------------------------------------------------|-----------------------------|

| CPV <sub>DD</sub> to GND)                                                | 0.3V to +6.0V               |

| GND to PGND, CPGND                                                       | ±0.3V                       |

| CPVSS, C1N, VSS to GND                                                   | 6.0V to +0.3V               |

| HPR, HPL to GND                                                          |                             |

| Any Other Pin                                                            | $0.3V$ to $(V_{DD} + 0.3V)$ |

| Duration of OUT_+, OUT Short Circuit                                     |                             |

| to GND or PV <sub>DD</sub>                                               | Continuous                  |

| Duration of Short Circuit between OUT_+,                                 | OUT                         |

| and LDO_OUT                                                              | Continuous                  |

| Duration of Short Circuit between HPR, HF                                | PL and GND,                 |

| V <sub>SS</sub> or HPV <sub>DD</sub>                                     | Continuous                  |

| Continuous Current (PVDD, OUT_+, OUT_                                    | -, PGND)1.7A                |

| Continuous Current (CPVDD, C1N, C1P, CPV                 | 'SS, PVSS,     |

|----------------------------------------------------------|----------------|

| V <sub>DD</sub> , HPV <sub>DD</sub> , LDO_OUT, HPR, HPL) | 850mA          |

| Continuous Input Current (all other pins)                | ±20mA          |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )    |                |

| 32-Pin Thin QFN Single-Layer Board                       |                |

| (derate 18.6mW/°C above +70°C)                           | 1489mW         |

| 32-Pin Thin QFN Multilayer Board                         |                |

| (derate 24.9 mW/°C above +70°C)                          | 1990mW         |

| Operating Temperature Range                              | 40°C to +85°C  |

| Junction Temperature                                     | +150°C         |

| Storage Temperature Range                                | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                        | +300°C         |

|                                                          |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO_EN (MAX9789A only) = +5V, GND = PGND = CPGND = LDO_SET (MAX9789A only) = 0V, I_{LDO_OUT} (MAX9789A only) = 0, C1 = C2 = C_{BIAS} = 1\mu F. R_L = <math>\infty$ , unless otherwise specified, GAIN1 = 0, GAIN2 = 5V (A<sub>VSP</sub> = 10dB, A<sub>VHP</sub> = 3.5dB), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                           | SYMBOL                                   | COND                                    | ITIONS                                        |                 | MIN | TYP   | MAX  | UNITS |

|-------------------------------------|------------------------------------------|-----------------------------------------|-----------------------------------------------|-----------------|-----|-------|------|-------|

| GENERAL                             |                                          |                                         |                                               |                 |     |       |      |       |

| Supply Voltage                      | V <sub>DD</sub> , PV <sub>DD</sub>       | Guaranteed by PSRR<br>Regulation Tests  | 4.5                                           |                 | 5.5 | V     |      |       |

| Headphone Supply Voltage            | CPV <sub>DD</sub> ,<br>HPV <sub>DD</sub> | Guaranteed by PSRR                      | Test                                          |                 | 3.0 |       | 5.5  | V     |

|                                     |                                          | SPKR_EN                                 | HI                                            | P_EN            |     |       |      |       |

| Quiescent Current                   |                                          | 1 (MAX9789A)                            | 0 (MA                                         | X9789A)         |     | 0.1   | 0.16 | mA    |

|                                     | IDD                                      | 1 (MAX9790A)                            | 0 (MA                                         | X9790A)         |     | 0.3   | 6    | μΑ    |

|                                     | .00                                      | 1                                       |                                               | 1               |     | 7     | 13   |       |

|                                     |                                          | 0                                       |                                               | 0               |     | 14    | 29   | mA    |

|                                     |                                          | 0                                       |                                               | 1               |     | 18    | 40   |       |

| Shutdown Current                    | ISHDN                                    | SPKR_EN = V <sub>DD</sub> , HP_         | EN = LDO                                      | _EN = GND       |     | 0.3   | 6    | μΑ    |

| Bias Voltage                        | V <sub>BIAS</sub>                        |                                         |                                               |                 | 1.7 | 1.8   | 1.9  | V     |

| Shutdown to Full Operation          | tson                                     |                                         |                                               |                 |     | 100   |      | ms    |

| Gain Switching Time                 | tsw                                      |                                         |                                               |                 |     | 10    |      | μs    |

| Channel-to-Channel Gain<br>Tracking |                                          |                                         |                                               |                 |     | ±0.1  |      | dB    |

| SPEAKER AMPLIFIER                   |                                          |                                         |                                               |                 |     |       |      |       |

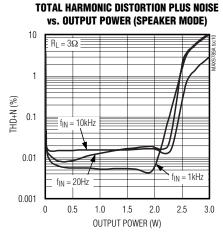

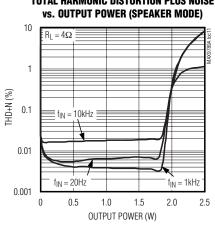

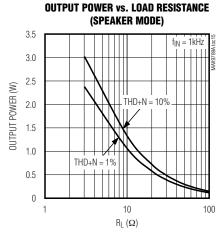

| Output Power                        | Роит                                     | THD+N = 1%, f = 1kH                     | Z,                                            | $R_L = 4\Omega$ |     | 2     |      | W     |

| Output Fower                        | FOUT                                     | T <sub>A</sub> = +25°C                  |                                               | $R_L = 8\Omega$ |     | 1     |      | VV    |

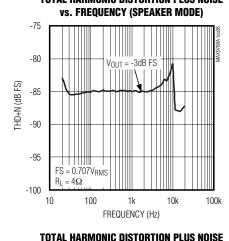

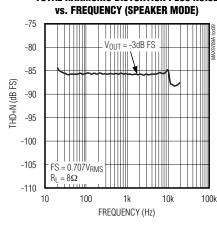

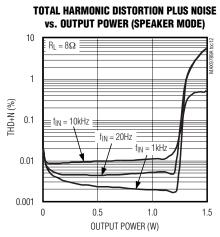

| Total Harmonic Distortion Plus      | THD+N                                    | $R_L = 8\Omega$ , $P_{OUT} = 1W$ ,      | f = 1kHz                                      |                 |     | 0.002 |      | %     |

| Noise                               | HIDHN                                    | $R_L = 4\Omega$ , $P_{OUT} = 1W$ ,      | $R_L = 4\Omega$ , $P_{OUT} = 1W$ , $f = 1kHz$ |                 |     |       |      | /0    |

|                                     |                                          | $V_{DD} = 4.5V \text{ to } 5.5V, T_{A}$ | 4 = +25°C                                     |                 | 72  | 90    |      |       |

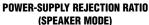

| Power-Supply Rejection Ratio        | PSRR                                     | $f = 1kHz$ , $200mV_{P-P}$ (N           |                                               |                 | 70  |       | dB   |       |

|                                     |                                          | $f = 10kHz, 200mV_{P-P}$                |                                               | 50              | ·   |       |      |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO_EN (MAX9789A only) = +5V, GND = PGND = CPGND = LDO_SET (MAX9789A only) = 0V, I_{LDO_OUT} (MAX9789A only) = 0, C1 = C2 = C_{BIAS} = 1 \mu F. R_L = <math>\infty$ , unless otherwise specified, GAIN1 = 0, GAIN2 = 5V (A<sub>VSP</sub> = 10dB, A<sub>VHP</sub> = 3.5dB), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                      | SYMBOL          | OL CONDITIONS                                                                                         |                   | MIN  | TYP  | MAX   | UNITS             |

|--------------------------------|-----------------|-------------------------------------------------------------------------------------------------------|-------------------|------|------|-------|-------------------|

|                                |                 | GAIN1                                                                                                 | GAIN2             |      |      |       |                   |

|                                |                 | 0                                                                                                     | 0                 |      | 6    |       |                   |

| Voltage Gain                   | Ay              | 0                                                                                                     | 1                 |      | 10   |       | dB                |

|                                |                 | 1                                                                                                     | 0                 |      | 15.6 |       |                   |

|                                |                 | 1                                                                                                     | 1                 |      | 21.6 |       |                   |

|                                |                 | Measured at speaker a                                                                                 | mplifier inputs   |      |      |       |                   |

|                                |                 | GAIN1                                                                                                 | GAIN2             |      |      |       |                   |

| loget books done               | D               | 0                                                                                                     | 0                 |      | 80   |       | 1.0               |

| nput Impedance                 | R <sub>IN</sub> | 0                                                                                                     | 1                 |      | 65   |       | kΩ                |

|                                |                 | 1                                                                                                     | 0                 |      | 45   |       |                   |

|                                |                 | 1                                                                                                     | 1                 |      | 25   |       |                   |

| Output Offset Voltage          | Vos             | Measured between OU TA = +25°C                                                                        | T_+ and OUT,      |      | ±1   | ±15   | mV                |

| 01: 1                          | 14              | $R_L = 8\Omega$ , peak voltage,                                                                       |                   |      | -50  |       | IDV               |

| Click-and-Pop Level            | KCP             | A-weighted, 32 sample per second (Notes 2, 3)                                                         |                   | -50  |      |       | dBV               |

| 0                              | ONID            | A-weighted 102                                                                                        |                   |      | ID   |       |                   |

| Signal-to-Noise Ratio          | SNR             | $R_L = 8\Omega$ , $P_{OUT} = 1W$                                                                      | f = 22Hz to 22kHz |      | 99   |       | dB                |

| Noise                          | Vn              | BW = 22Hz to 22kHz                                                                                    |                   |      | 30   |       | μV <sub>RMS</sub> |

| Capacitive-Load Drive          | CL              | No sustained oscillation                                                                              | ns                |      | 200  |       | рF                |

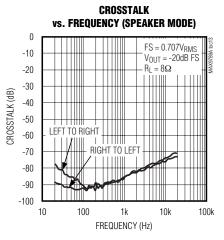

| Crosstalk                      |                 | L to R, R to L, $R_L = 8\Omega$ ,<br>$V_{OUT} = 70.7 \text{nV}_{RMS}$ , 20k<br>BW = 20Hz to 20kHz     |                   |      | -70  |       | dB                |

| Slew Rate                      | SR              |                                                                                                       |                   |      | 1.4  |       | V/µs              |

| HEADPHONE AMPLIFIER            | 1               |                                                                                                       |                   |      |      |       | •                 |

| _                              | _               | THD+N = 1%, f =                                                                                       | $R_L = 16\Omega$  |      | 100  |       |                   |

| Output Power                   | Pout            |                                                                                                       | $R_L = 32\Omega$  |      | 55   |       | mW                |

|                                |                 | $R_L = 32\Omega$ , FS = 0.300V<br>V <sub>OUT</sub> = 210mV <sub>RMS</sub> , 20I<br>BW = 20Hz to 20kHz | RMS,              |      | -77  |       | dB FS             |

| Total Harmonic Distortion Plus |                 | $R_L = 32\Omega$ , $P_{OUT} = 40$ m                                                                   |                   | 0.02 |      | %     |                   |

| Noise                          | THD+N           | $R_L = 16\Omega$ , $P_{OUT} = 60$ m                                                                   |                   |      | 0.03 |       | /6                |

|                                |                 | $R_L = 10k\Omega$ , FS = 0.707V<br>$V_{OUT} = 500mV_{RMS}$ , 20l<br>BW = 20Hz to 20kHz                |                   | -94  |      | dB FS |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO\_EN \ (MAX9789A \ only) = +5V, \ GND = PGND = CPGND = LDO\_SET \ (MAX9789A \ only) = 0V, \\ I_{LDO\_OUT} \ (MAX9789A \ only) = 0, \ C1 = C2 = C_{BIAS} = 1 \mu F. \ R_L = \infty, \ unless \ otherwise \ specified, \ GAIN1 = 0, \ GAIN2 = 5V \ (A_{VSP} = 10dB, A_{VHP} = 3.5dB), \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25°C.) \ (Note \ 1)$

| PARAMETER                             | SYMBOL           | COND                                                                                | ITIONS                                                                                              | MIN  | TYP  | MAX  | UNITS             |

|---------------------------------------|------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|-------------------|

|                                       |                  | $HPV_{DD} = 3V \text{ to } 5.5V,$                                                   | 70                                                                                                  | 95   |      |      |                   |

| Power-Supply Rejection Ratio (Note 5) | PSRR             | f = 1kHz, V <sub>RIPPLE</sub> = 20                                                  | 00mV <sub>P-P</sub> (Note 3)                                                                        |      | 84   |      | dB                |

| (Note 3)                              |                  | f = 10kHz, V <sub>RIPPLE</sub> = 2                                                  | 200mV <sub>P-P</sub> (Note 3)                                                                       |      | 63   |      |                   |

| Voltage Gain                          | Ay               |                                                                                     |                                                                                                     |      | 3.5  |      | dB                |

| Input Impedance                       | RIN              | Measured at headpho                                                                 | one amplifier inputs                                                                                | 20   | 40   | 80   | kΩ                |

| Output Offset Voltage                 | Vos              | T <sub>A</sub> = +25°C                                                              |                                                                                                     |      | ±2   | ±7   | mV                |

|                                       |                  | $R_L = 32\Omega$ , peak voltage                                                     |                                                                                                     |      | -60  |      |                   |

| Click-and-Pop Level                   | K <sub>CP</sub>  | A-weighted, 32 sample per second (Notes 2,                                          |                                                                                                     |      | -60  |      | dBV               |

|                                       |                  | $R_L = 32\Omega$ , $f = 1kHz$ , A<br>FS = 0.300V <sub>RMS</sub> , V <sub>OU</sub>   | •                                                                                                   |      | 89   |      | 10.50             |

| Dynamic Range                         | DR               | $R_L = 10k\Omega$ , $f = 1kHz$ , $R_L = 10k\Omega$ , $R_L = 10k\Omega$              | A-weighted,                                                                                         |      | 97   |      | dB FS             |

|                                       | 01.15            | $R_L = 32\Omega$ ,                                                                  | 22Hz to 22kHz                                                                                       |      | 100  |      |                   |

| Signal-to-Noise Ratio                 | SNR              | Pout = 60mW                                                                         | A-weighted                                                                                          |      | 103  |      | dB                |

| Noise                                 | Vn               | BW = 22Hz to 22kHz                                                                  |                                                                                                     |      | 12   |      | μV <sub>RMS</sub> |

| Capacitive-Load Drive                 | CL               | No sustained oscillation                                                            | ons                                                                                                 |      | 200  |      | pF                |

| Crosstalk                             |                  | L to R, R to L,<br>20kHz AES17                                                      | $\begin{aligned} R_L &= 32\Omega, \\ FS &= 0.300 V_{RMS}, \\ V_{OUT} &= 30 m V_{RMS} \end{aligned}$ |      | -74  |      | dB                |

| Ciossiain                             |                  | BW = 20Hz to 20kHz                                                                  | $R_L = 10k\Omega,$ $FS = 0.707V_{RMS},$ $V_{OUT} = 70.7mV_{RMS}$                                    |      | -77  |      | db                |

| Slew Rate                             | SR               |                                                                                     |                                                                                                     |      | 0.4  |      | V/µs              |

| ESD                                   | ESD              | Human Body Model (I                                                                 | HPR, HPL)                                                                                           |      | ±8   |      | kV                |

| Charge-Pump Frequency                 | fosc             |                                                                                     |                                                                                                     | 500  | 550  | 600  | kHz               |

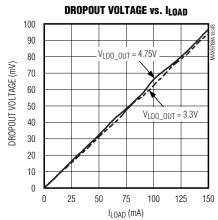

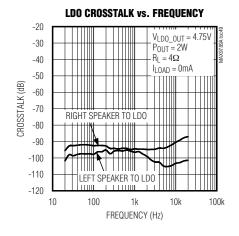

| LOW-DROPOUT LINEAR REGUL              | ATOR             |                                                                                     |                                                                                                     |      |      |      |                   |

| Regulator Input Voltage Range         | V <sub>DD</sub>  | Inferred from line regu                                                             | ulation                                                                                             | 4.5  |      | 5.5  | V                 |

| Cray and Characat                     | 1                | I <sub>OUT</sub> = 0mA                                                              |                                                                                                     |      | 0.1  | 0.16 | A                 |

| Ground Current                        | IGND             | $I_{OUT} = 120mA$                                                                   |                                                                                                     |      | -40  |      | mA mA             |

| Output Current                        | lout             |                                                                                     |                                                                                                     |      |      | 120  | mA                |

| Crosstalk                             |                  | V <sub>OUT</sub> = 4.75V, f = 1kH                                                   | lz, speaker P <sub>OUT</sub> = 2W                                                                   |      | -88  |      | dB                |

| Fixed Output Voltage Accuracy         |                  | I <sub>OUT</sub> = 1mA                                                              |                                                                                                     |      |      | ±1.5 | %                 |

| Adjustable Output Voltage Range       |                  |                                                                                     |                                                                                                     | 1.21 |      | 4.75 | V                 |

| LDO_SET Reference Voltage             | V <sub>SET</sub> |                                                                                     |                                                                                                     | 1.19 | 1.21 | 1.23 | V                 |

| LDO_SET Dual-Mode Threshold           |                  |                                                                                     |                                                                                                     |      | 200  |      | mV                |

| LDO_SET Input Bias Current (Note 4)   | ISET             |                                                                                     |                                                                                                     |      | ±20  | ±500 | nA                |

|                                       | .,               | $V_{OUT} = 4.75V$ (fixed output operation), $T_{A} = +25^{\circ}C$ $I_{OUT} = 50mA$ |                                                                                                     |      | 25   | 50   |                   |

| Dropout Voltage (Note 5)              | V <sub>DO</sub>  |                                                                                     |                                                                                                     |      | 75   | 150  | mV                |

4 \_\_\_\_\_\_*NIXIN*

### **ELECTRICAL CHARACTERISTICS (continued)**

(VDD = PVDD = CPVDD = HPVDD = LDO EN (MAX9789A only) = +5V, GND = PGND = CPGND = LDO SET (MAX9789A only) = 0V, ILDO\_OUT (MAX9789A only) = 0, C1 = C2 = C<sub>BIAS</sub> = 1μF. R<sub>L</sub> = ∞, unless otherwise specified, GAIN1 = 0, GAIN2 = 5V (A<sub>VSP</sub> = 10dB, A<sub>VHP</sub> = 3.5dB), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                   | SYMBOL           | CONDITI                                                                        | MIN              | TYP  | MAX  | UNITS |                   |

|-----------------------------|------------------|--------------------------------------------------------------------------------|------------------|------|------|-------|-------------------|

| Current Limit               | ILIM             |                                                                                |                  |      | 300  |       | mA                |

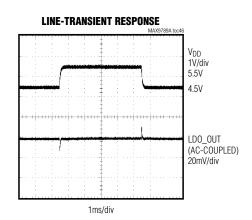

| Startup Time                |                  |                                                                                |                  |      | 20   |       | μs                |

| Line Regulation             |                  | V <sub>IN</sub> = 4.5V to 5.5V, LDO <sub>1</sub><br>I <sub>LDO_OUT</sub> = 1mA | -4.8             | +0.8 | +4.8 | mV/V  |                   |

| Load Regulation             |                  | V <sub>LDO_OUT</sub> = 4.75V,<br>1mA < I <sub>LDO_OUT</sub> < 120n             |                  | 0.2  |      | mV/mA |                   |

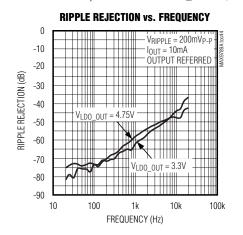

| Diamie Deigetien            |                  | VRIPPLE = 200mVp-p                                                             | f = 1kHz         |      | 59   |       | ٩D                |

| Ripple Rejection            |                  | I <sub>LDO_OUT</sub> = 10mA                                                    | f = 10kHz        |      | 42   |       | dB                |

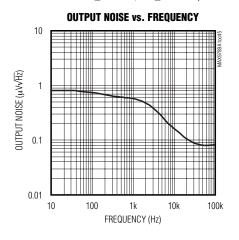

| Output Voltage Noise        |                  | 20Hz to 22kHz, C <sub>LDO_OUT</sub> = 2 x 1μF,<br>I <sub>LDO_OUT</sub> = 120mA |                  |      | 125  |       | μV <sub>RMS</sub> |

| DIGITAL INPUTS (SPKR_EN, HP | EN, MUTE,        | GAIN1, GAIN2, LDO_EN                                                           | (MAX9789A Only)) |      |      |       |                   |

| Input-Voltage High          | VINH             |                                                                                |                  | 2    |      | •     | V                 |

| Input-Voltage Low           | V <sub>INL</sub> |                                                                                |                  |      |      | 0.8   | V                 |

| Input Bias Current          |                  |                                                                                |                  |      |      | ±1    | μΑ                |

- Note 1: All devices are 100% production tested at room temperature. All temperature limits are guaranteed by design.

- Note 2: Specified at room temperature with an 8Ω resistive load connected across BTL output for speaker amplifier. Specified at room temperature with a  $32\Omega$  resistive load connected between HPR, HPL, and GND for headphone amplifier. Speaker and headphone mode transitions are controlled by SPKR\_EN and HP\_EN control pins, respectively.

- Note 3: Amplifier inputs AC-coupled to GND.

- Note 4: Maximum value is due to test limitations.

- Note 5: VLDO OUT = VLDO OUTNOMINAL 2%.

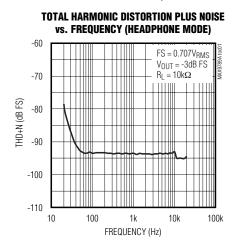

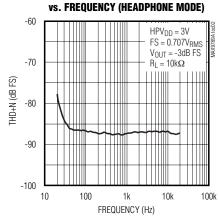

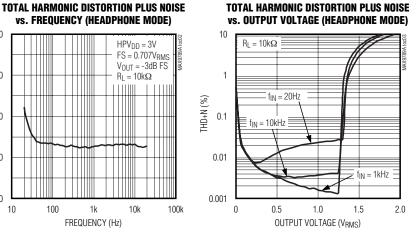

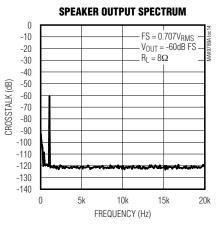

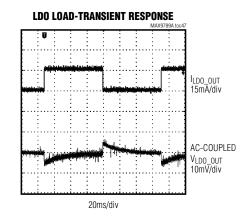

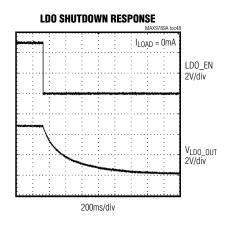

### Typical Operating Characteristics

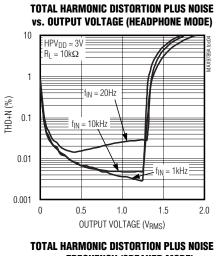

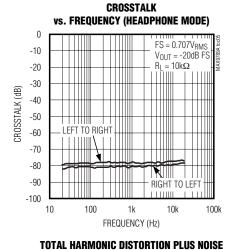

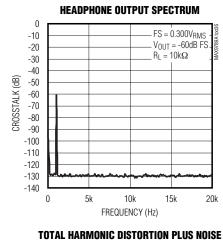

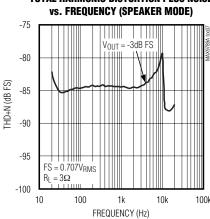

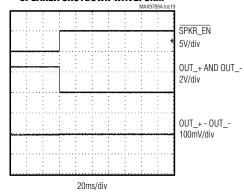

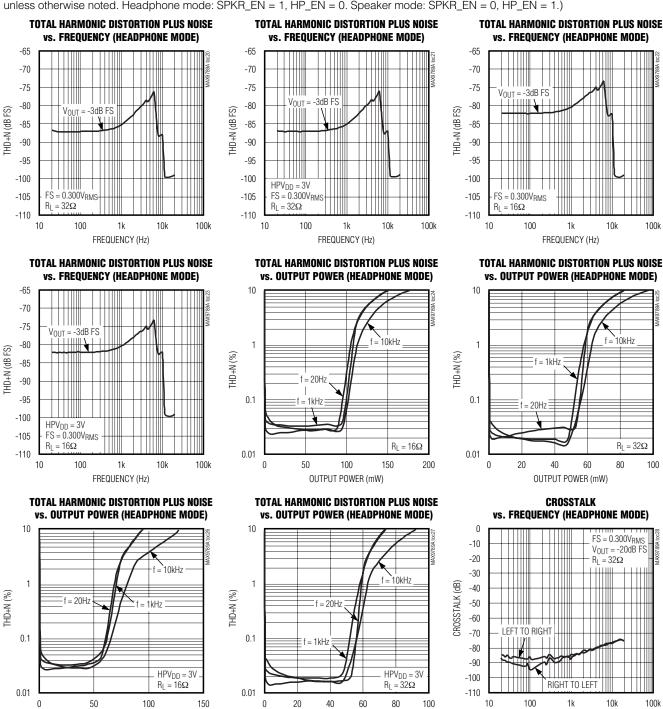

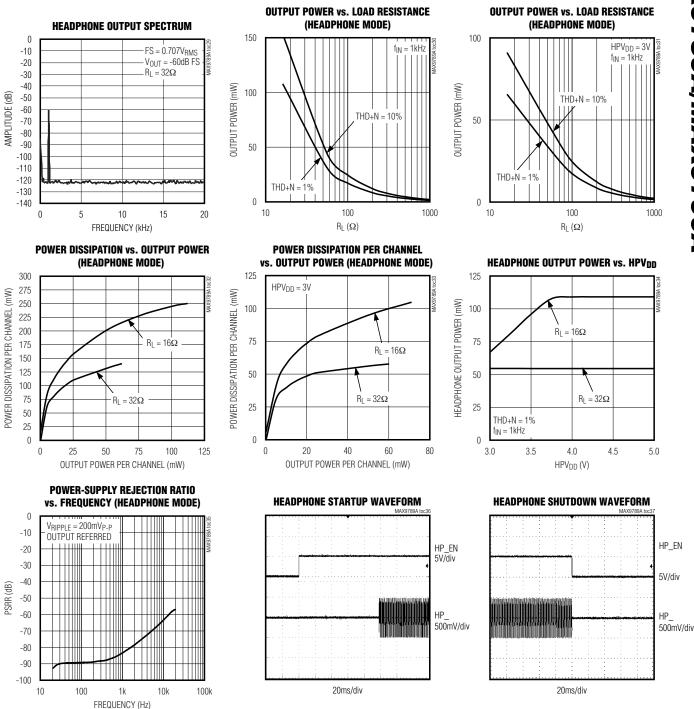

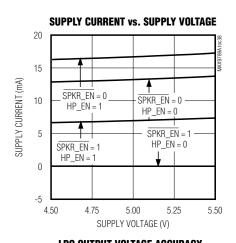

(VDD = PVDD = CPVDD = HPVDD = LDO\_EN = +5V, GND = PGND = CPGND = LDO\_SET = 0V, C1 = C2 = CBIAS = CIN = 1µF. RL = ∞, unless otherwise specified, GAIN1 = 0, GAIN2 = 1 (Aysp = 10dB, AyHp = 3.5dB), measurement BW = 20kHz AES17, TA = +25°C, unless otherwise noted. Headphone mode:  $\overline{SPKR\_EN} = 1$ ,  $HP\_EN = 0$ . Speaker mode:  $\overline{SPKR\_EN} = 0$ ,  $HP\_EN = 1$ .)

MIXIM

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO\_EN = +5V, GND = PGND = CPGND = LDO\_SET = 0V, C1 = C2 = C_{BIAS} = C_{IN} = 1\mu F. \ R_L = \infty, unless otherwise specified, GAIN1 = 0, GAIN2 = 1 (A_{VSP} = 10dB, A_{VHP} = 3.5dB), measurement BW = 20kHz AES17, <math>T_A = +25^{\circ}C$ , unless otherwise noted. Headphone mode:  $\overline{SPKR}_{EN} = 1$ , HP\_EN = 0. Speaker mode:  $\overline{SPKR}_{EN} = 0$ , HP\_EN = 1.)

6 \_\_\_\_\_\_/N/XI/VI

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO\_EN = +5V, GND = PGND = CPGND = LDO\_SET = 0V, C1 = C2 = C_{BIAS} = C_{IN} = 1\mu F. \ R_L = \infty, unless otherwise specified, GAIN1 = 0, GAIN2 = 1 (A_{VSP} = 10dB, A_{VHP} = 3.5dB), measurement BW = 20kHz AES17, <math>T_A = +25^{\circ}C$ , unless otherwise noted. Headphone mode:  $\overline{SPKR\_EN} = 1$ , HP\_EN = 0. Speaker mode:  $\overline{SPKR\_EN} = 0$ , HP\_EN = 1.)

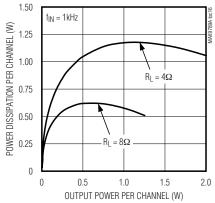

# POWER DISSIPATION PER CHANNEL vs. OUTPUT POWER (SPEAKER MODE)

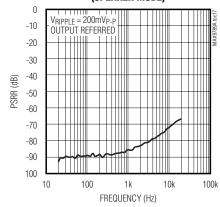

#### SPEAKER SHUTDOWN WAVEFORM

MIXIM

### \_Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO\_EN = +5V, GND = PGND = CPGND = LDO\_SET = 0V, C1 = C2 = C_{BIAS} = C_{IN} = 1\mu F. \ R_L = \infty, unless otherwise specified, GAIN1 = 0, GAIN2 = 1 (A_{VSP} = 10dB, A_{VHP} = 3.5dB), measurement BW = 20kHz AES17, T_A = +25°C, unless otherwise noted. Headphone mode: <math display="block">\overline{SPKR\_EN} = 1, HP\_EN = 0. \ Speaker mode: \overline{SPKR\_EN} = 0, HP\_EN = 1.)$

OUTPUT POWER (mW)

FREQUENCY (Hz)

MIXKN

Downloaded from Elcodis.com electronic components distributor

OUTPUT POWER (mW)

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO_EN = +5V$ ,  $GND = PGND = CPGND = LDO_SET = 0V$ ,  $C1 = C2 = C_{BIAS} = C_{IN} = 1\mu F$ .  $R_L = \infty$ , unless otherwise specified, GAIN1 = 0, GAIN2 = 1 ( $A_{VSP} = 10$ dB,  $A_{VHP} = 3.5$ dB), measurement BW = 20kHz AES17,  $T_A = +25$ °C, unless otherwise noted. Headphone mode:  $\overline{SPKR}_{EN} = 1$ ,  $HP_EN = 0$ . Speaker mode:  $\overline{SPKR}_{EN} = 0$ ,  $HP_EN = 1$ .)

/N/IXI/N \_\_\_\_\_

### Typical Operating Characteristics (continued)

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO\_EN = +5V, GND = PGND = CPGND = LDO\_SET = 0V, C1 = C2 = C_{BIAS} = C_{IN} = 1\mu F. \ R_L = \infty, unless otherwise specified, GAIN1 = 0, GAIN2 = 1 (A_{VSP} = 10dB, A_{VHP} = 3.5dB), measurement BW = 20kHz AES17, <math>T_A = +25^{\circ}C$ , unless otherwise noted. Headphone mode:  $\overline{SPKR}_{EN} = 1$ , HP\_EN = 0. Speaker mode:  $\overline{SPKR}_{EN} = 0$ , HP\_EN = 1.)

10 \_\_\_\_\_\_/N/1XI/VI

### **Typical Operating Characteristics (continued)**

$(V_{DD} = PV_{DD} = CPV_{DD} = HPV_{DD} = LDO_EN = +5V$ ,  $GND = PGND = CPGND = LDO_SET = 0V$ ,  $C1 = C2 = C_{BIAS} = C_{IN} = 1\mu F$ .  $R_L = \infty$ , unless otherwise specified, GAIN1 = 0, GAIN2 = 1 ( $A_{VSP} = 10$ dB,  $A_{VHP} = 3.5$ dB), measurement BW = 20kHz AES17,  $T_A = +25$ °C, unless otherwise noted. Headphone mode:  $\overline{SPKR}_{EN} = 1$ ,  $HP_EN = 0$ . Speaker mode:  $\overline{SPKR}_{EN} = 0$ ,  $HP_EN = 1$ .)

MIXIM

\_Pin Description

| PIN      |          |                   | FINATION                                                                                                                                                                                           |  |  |  |  |  |  |

|----------|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MAX9789A | MAX9790A | NAME              | FUNCTION                                                                                                                                                                                           |  |  |  |  |  |  |

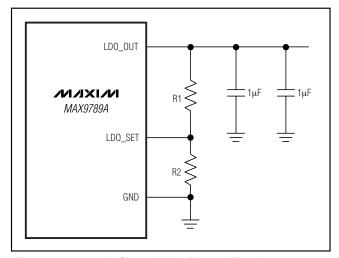

| 1        | _        | LDO_SET           | Regulator Feedback Input. Connect to GND for 4.75V fixed output. Connect to a resistor-divider for adjustable output. See Figure 1.                                                                |  |  |  |  |  |  |

| 2        | 2        | SPKR_INR          | Right-Channel Speaker Amplifier Input                                                                                                                                                              |  |  |  |  |  |  |

| 3        | 3        | SPKR_INL          | Left-Channel Speaker Amplifier Input                                                                                                                                                               |  |  |  |  |  |  |

| 4        | _        | LDO_EN            | LDO Enable. Connect LDO_EN to VDD to enable the LDO.                                                                                                                                               |  |  |  |  |  |  |

| 5, 21    | 5, 21    | PGND              | Power Ground. Star-connect to GND.                                                                                                                                                                 |  |  |  |  |  |  |

| 6        | 6        | OUTL+             | Left-Channel Speaker Amplifier Output, Positive Phase                                                                                                                                              |  |  |  |  |  |  |

| 7        | 7        | OUTL-             | Left-Channel Speaker Amplifier Output, Negative Phase                                                                                                                                              |  |  |  |  |  |  |

| 8, 18    | 8, 18    | PV <sub>DD</sub>  | Speaker Amplifier Power-Supply Input. Bypass with a 0.1µF capacitor to PGND.                                                                                                                       |  |  |  |  |  |  |

| 9        | 9        | CPV <sub>DD</sub> | Charge-Pump Power Supply. Connect a 1µF capacitor between CPVDD and PGND.                                                                                                                          |  |  |  |  |  |  |

| 10       | 10       | C1P               | Charge-Pump Flying Capacitor Positive Terminal. Connect a 1µF capacitor between C1P to C1N.                                                                                                        |  |  |  |  |  |  |

| 11       | 11       | CPGND             | Charge-Pump Ground. Connect directly to PGND plane.                                                                                                                                                |  |  |  |  |  |  |

| 12       | 12       | C1N               | Charge-Pump Flying Capacitor Negative Terminal. Connect a 1µF capacitor between C1P to C1N.                                                                                                        |  |  |  |  |  |  |

| 13       | 13       | CPVss             | Charge-Pump Output. Connect to PVSS.                                                                                                                                                               |  |  |  |  |  |  |

| 14       | 14       | PVss              | Headphone Amplifier Negative Power Supply. Connect a 1µF capacitor between PVSS and PGND.                                                                                                          |  |  |  |  |  |  |

| 15       | 15       | HPR               | Right-Channel Headphone Amplifier Output                                                                                                                                                           |  |  |  |  |  |  |

| 16       | 16       | HPL               | Left-Channel Headphone Amplifier Output                                                                                                                                                            |  |  |  |  |  |  |

| 17       | 17       | HPV <sub>DD</sub> | Headphone Amplifier Positive Power Supply. Connect a 10µF capacitor between HPV <sub>DD</sub> and PGND.                                                                                            |  |  |  |  |  |  |

| 19       | 19       | OUTR-             | Right-Channel Speaker Amplifier Output, Negative Phase                                                                                                                                             |  |  |  |  |  |  |

| 20       | 20       | OUTR+             | Right-Channel Speaker Amplifier Output, Positive Phase                                                                                                                                             |  |  |  |  |  |  |

| 22       | 22       | HP_EN             | Active-High Headphone Amplifier Enable                                                                                                                                                             |  |  |  |  |  |  |

| 23       | 23       | SPKR_EN           | Active-Low Speaker Amplifier Enable                                                                                                                                                                |  |  |  |  |  |  |

| 24       | 24       | BIAS              | Common-Mode Bias Voltage. Bypass with a 1µF capacitor to GND.                                                                                                                                      |  |  |  |  |  |  |

| 25       | 25       | MUTE              | Active-Low Mute Enable. Mutes speaker and headphone amplifiers.                                                                                                                                    |  |  |  |  |  |  |

| 26       | 26       | HP_INR            | Right-Channel Headphone Amplifier Input                                                                                                                                                            |  |  |  |  |  |  |

| 27       | 27       | HP_INL            | Left-Channel Headphone Amplifier Input                                                                                                                                                             |  |  |  |  |  |  |

| 28       | 4, 28    | GND               | Signal Ground. Star-connect to PGND.                                                                                                                                                               |  |  |  |  |  |  |

| 29       | _        | LDO_OUT           | LDO Output. Bypass with two 1µF capacitors to GND.                                                                                                                                                 |  |  |  |  |  |  |

| 30       | 30       | V <sub>DD</sub>   | Positive Power Supply and LDO Input (MAX9789A). Bypass with one 0.1µF capacitor and two 1µF capacitors to GND (MAX9789A). Bypass with one 0.1µF capacitor and one 1µF capacitor to GND (MAX9790A). |  |  |  |  |  |  |

| 31       | 31       | GAIN1             | Speaker Amplifier Gain Select 1                                                                                                                                                                    |  |  |  |  |  |  |

| 32       | 32       | GAIN2             | Speaker Amplifier Gain Select 2                                                                                                                                                                    |  |  |  |  |  |  |

| _        | 1, 29    | N.C.              | No Connection. Not internally connected.                                                                                                                                                           |  |  |  |  |  |  |

| EP       | EP       | EP                | Exposed Paddle. Connect to GND.                                                                                                                                                                    |  |  |  |  |  |  |

12 \_\_\_\_\_\_\_**/VI/XI/M**

### **Detailed Description**

The MAX9789A/MAX9790A combine a 2W BTL speaker amplifier with an 100mW DirectDrive headphone amplifier. These devices feature comprehensive click-and-pop suppression and programmable four-level speaker amplifier gain control. The MAX9789A/MAX9790A feature high +90dB PSRR, low 0.002% THD+N, industry-leading click-and-pop performance, low-power shutdown mode, and excellent RF immunity. The MAX9789A incorporates an integrated LDO that serves as a clean power supply for a CODEC or other circuits.

The MAX9789A/MAX9790A is Microsoft Windows Vista compliant. See Table 1 for a comparison of the Microsoft Windows Vista premium mobile specifications and MAX9789A/MAX9790A specifications.

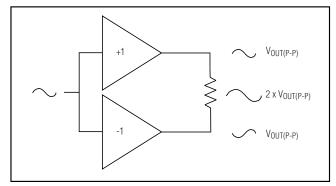

The speaker amplifiers use BTL architecture, doubling the voltage drive to the speakers and eliminating the need for DC-blocking capacitors. The output consists of two signals, identical in magnitude, but 180° out of phase.

The headphone amplifiers use Maxim's patented DirectDrive architecture to eliminate the bulky output DC-blocking capacitors required by traditional headphone amplifiers. A charge pump inverts a positive supply (CPVDD) to create a negative supply (CPVSS). The headphone amplifiers operate from these bipolar supplies with their outputs biased about GND. The benefit of the GND bias is that the amplifier outputs no longer have a DC component (typically VDD / 2). This feature eliminates the large DC-blocking capacitors required with conventional headphone amplifiers to

conserve board space and system cost, as well as improve low-frequency response.

The MAX9789A/MAX9790A feature programmable speaker amplifier gain, allowing the speaker gain to be set by the logic voltages applied to GAIN1 and GAIN2, while the headphone amplifiers feature a fixed 3.5dB gain. Both amplifiers feature an undervoltage lockout that prevents operation from an insufficient power supply and click-and-pop suppression that eliminates audible transients on startup and shutdown. The amplifiers include thermal overload and short-circuit protection, while the headphone amplifier outputs (IEC Air Discharge) can withstand ±8kV ESD strikes. An additional feature of the speaker amplifiers is that there is no phase inversion from input to output.

# Low-Dropout Linear Regulator (MAX9789A Only)

The MAX9789A's low-dropout (LDO) linear regulator can be used to provide a clean power supply to a CODEC or other circuitry. The LDO can be enabled independently of the audio amplifiers. Set LDO\_EN = VDD to enable the LDO or set LDO\_EN = GND to disable the LDO. The LDO is capable of providing up to 120mA continuous current and features Maxim's Dual Mode™ feedback, easily enabling a fixed 4.75V output or a user-adjustable output. When LDO\_SET is connected to GND, the output is internally set to 4.75V. The output voltage can be adjusted from 1.21V to 4.75V by connecting two external resistors as a voltage divider, at LDO\_SET (Figure 1).

Table 1. Windows Premium Mobile Vista Specifications vs. MAX9789A/MAX9790A Specifications

| DEVICE TYPE                                                                      | REQUIREMENT                       | WINDOWS PREMIUM MOBILE Vista SPECIFICATIONS | MAX9789A/MAX9790A<br>TYPICAL PERFORMANCE |  |  |

|----------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------|------------------------------------------|--|--|

|                                                                                  | THD+N                             | ≤ -65dB FS<br>[20Hz, 20kHz]                 | -94dB FS<br>[20Hz, 20kHz]                |  |  |

| Analog Line Output<br>Jack ( $R_L = 10k\Omega$ ,<br>FS = 0.707V <sub>RMS</sub> ) | Dynamic range with signal present | ≤ -80dB FS,<br>A-weighted                   | -97dB FS,<br>A-weighted                  |  |  |

| 1 3 = 0.707 VRMS)                                                                | Line output crosstalk             | ≤ -50dB<br>[20Hz, 20kHz]                    | -77dB<br>[20Hz, 20kHz]                   |  |  |

|                                                                                  | THD+N                             | ≤ -45dB FS<br>[20Hz, 20kHz]                 | -77dB FS<br>[20Hz, 20kHz]                |  |  |

| Analog Headphone<br>Out Jack ( $R_L = 32\Omega$ ,<br>$FS = 0.300V_{RMS}$ )       | Dynamic range with signal present | ≤ -60dB FS,<br>A-weighted                   | -89dB FS,<br>A-weighted                  |  |  |

| 1 0 = 0.000 VRIVIS)                                                              | Headphone output crosstalk        | ≤ -50dB<br>[20Hz, 20kHz]                    | -74dB<br>[20Hz, 20kHz]                   |  |  |

**Note:** THD+N, DR, FREQUENCY ACCURACY, and CROSSTALK should be measured in accordance with AES-17 audio measurements standards.

Dual Mode is a trademark of Maxim Integrated Products, Inc.

/**/**//X|/// \_\_\_\_\_\_\_ 13

The output voltage is set by the following equation:

$$V_{LDO\_OUT} = V_{LDO\_SET} \left(1 + \frac{R1}{R2}\right)$$

where  $V_{LDO\_SET} = 1.21V$ .

To simplify resistor selection:

$$R1 = R2 \left( \frac{V_{LDO}OUT}{1.21} - 1 \right)$$

Since the input bias current at LDO\_SET is typically less than 500nA (max), large resistance values can be used for R1 and R2 to minimize power consumption without compromising accuracy. The parallel combination of R1 and R2 should be less than  $1M\Omega$ .

#### **DirectDrive**

Conventional single-supply headphone amplifiers have their outputs biased about a nominal DC voltage ( $V_{DD}$  / 2) for maximum dynamic range. Large coupling capacitors are needed to block this DC bias from the headphones. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone amplifier.

Maxim's patented DirectDrive architecture uses a charge pump to create an internal negative supply voltage. It allows the MAX9789A/MAX9790A headphone amplifier output to be biased about GND. With no DC component, there is no need for the large DC-blocking

Figure 1. Adjustable Output Using External Feedback Resistors.

capacitors. Instead of two large capacitors (330 $\mu$ F typically required to meet Vista magnitude response specifications), the MAX9789A/MAX9790A charge pump requires only two small 1 $\mu$ F ceramic capacitors, conserving board space, reducing cost, and improving the low-frequency response of the headphone amplifier.

Previous attempts to eliminate the output coupling capacitors involved biasing the headphone return (sleeve) to the DC bias voltage of the headphone amplifiers. This method raised some issues:

- The sleeve is typically grounded to the chassis.

Using this biasing approach, the sleeve must be isolated from system ground, complicating product design.

- During an ESD strike, the amplifier's ESD structures are the only path to system ground. The amplifier must be able to withstand the full ESD strike.

- When using the headphone jack as a line out to other equipment, the bias voltage on the sleeve may conflict with the ground potential from other equipment, resulting in large ground loop current and possible damage to the amplifiers.

#### Low-Frequency Response

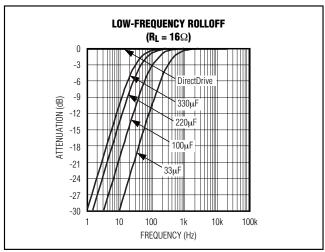

In addition to the cost and size disadvantages, the DC-blocking capacitors limit the low-frequency response of the amplifier and distort the audio signal:

The impedance of the headphone load and the DCblocking capacitor form a highpass filter with the -3dB point determined by:

$$f-3dB = \frac{1}{2\pi R_L C_{OUT}}$$

where R<sub>L</sub> is the impedance of the headphone and COUT is the value of the DC-blocking capacitor.

• The highpass filter is required by conventional single-ended, single-supply headphone amplifier to block the midrail DC component of the audio signal from the headphones. Depending on the -3dB point, the filter can attenuate low-frequency signals within the audio band. Larger values of COUT reduce the attenuation, but are physically larger, more expensive capacitors. Figure 2 shows the relationship between the size of COUT and the resulting low-frequency attenuation. Note the Vista's magnitude response specification calls for a -3dB point at 20Hz at the headphone jack. The -3dB point at 20Hz for a 32Ω headphone requires a 330µF blocking capacitor (Table 2).

Figure 2. Low-Frequency Attenuation of Common DC-Blocking Capacitor Values

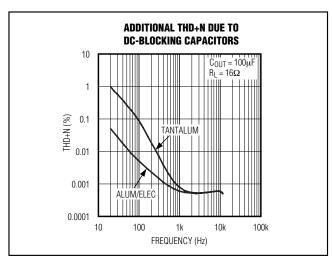

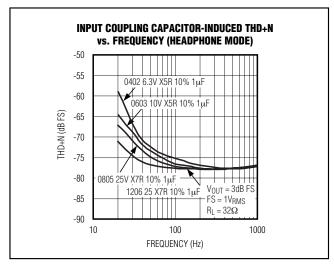

- The voltage coefficient of the capacitor, the change in capacitance due to a change in the voltage across the capacitor, distorts the audio signal. At frequencies around the -3dB point, this effect is maximized and the voltage coefficient appears as frequency-dependent distortion. Figure 3 shows the THD+N introduced by two different capacitor dielectrics. Note that around the -3dB point, THD+N increases dramatically.

- The combination of low-frequency attenuation and frequency-dependent distortion compromises audio reproduction. DirectDrive improves low-frequency reproduction in portable audio equipment that emphasizes low-frequency effects, such as multimedia laptops, MP3, CD, and DVD players (See Table 2).

**Table 2. Low-Frequency Rolloff**

| Cour (uE) | f <sub>-3dB</sub> (Hz) |                  |  |  |  |  |  |

|-----------|------------------------|------------------|--|--|--|--|--|

| Соит (µF) | $R_L = 16\Omega$       | $R_L = 32\Omega$ |  |  |  |  |  |

| 22        | 452                    | 226              |  |  |  |  |  |

| 33        | 301                    | 151              |  |  |  |  |  |

| 100       | 99                     | 50               |  |  |  |  |  |

| 220       | 45                     | 23               |  |  |  |  |  |

| 330*      | 30                     | 15               |  |  |  |  |  |

| 470       | 21                     | 11               |  |  |  |  |  |

<sup>\*</sup>Vista requirement for  $32\Omega$  load.

#### Charge Pump

The MAX9789A/MAX9790A feature a low-noise charge pump. The 550kHz switching frequency is well beyond the audio range, and does not interfere with the audio signals. The switch drivers feature a controlled switching

Figure 3. Distortion Contributed by DC-Blocking Capacitors

speed that minimizes noise generated by switching transients. Limiting the switching speed of the charge pump minimizes the di/dt noise caused by the parasitic bond wire and trace inductance.

#### BIAS

The MAX9789A/MAX9790A feature an internally generated, power-supply independent, common-mode bias voltage of 1.8V referenced to GND. BIAS provides both click-and-pop suppression and sets the DC bias level for the amplifiers. The BIAS pin should be bypassed to GND with a 1 $\mu$ F capacitor. No external load should be applied to BIAS. Any load lowers the BIAS voltage, affecting the overall performance of the device.

#### Headphone and Speaker Amplifier Gain

The MAX9789A/MAX9790A feature programmable speaker amplifier gain, set by the logic voltages applied to pins GAIN1 and GAIN2. Table 3 shows the logic combinations that can be applied to pins GAIN1 and GAIN2 and their affects on the speaker amplifier gain. The headphone amplifier gain is fixed at 3.5dB.

# Table 3. MAX9789A/MAX9790A Programmable Gain Settings

| MAX9789A/MAX9790A |       |                           |                             |  |  |  |  |  |  |  |  |

|-------------------|-------|---------------------------|-----------------------------|--|--|--|--|--|--|--|--|

| GAIN1             | GAIN2 | SPEAKER MODE<br>GAIN (dB) | HEADPHONE<br>MODE GAIN (dB) |  |  |  |  |  |  |  |  |

| 0                 | 0     | 6                         | 3.5                         |  |  |  |  |  |  |  |  |

| 0                 | 1     | 10                        | 3.5                         |  |  |  |  |  |  |  |  |

| 1                 | 0     | 15.6                      | 3.5                         |  |  |  |  |  |  |  |  |

| 1                 | 1     | 21.6                      | 3.5                         |  |  |  |  |  |  |  |  |

/**N**/**X**|/**N** \_\_\_\_\_\_\_ 15

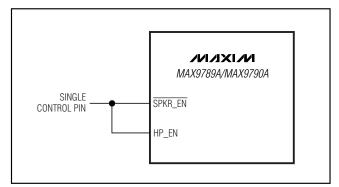

#### Speaker and Headphone Amplifier Enable

The MAX9789A/MAX9790A feature control inputs for the independent enabling of the speaker and headphone amplifiers, allowing both to be active simultaneously if required. Driving SPKR\_EN high disables the speaker amplifiers. Driving HP\_EN low independently disables the headphone amplifiers. For applications that require only one of the amplifiers to be on at a given time, SPKR\_EN and HP\_EN can be tied together allowing a single logic voltage to enable either the speaker or the headphone amplifier as shown in Figure 4.

#### MUTE

The MAX9789A/MAX9790A allow for the speaker and headphone amplifiers to be muted. By driving MUTE low, both the speaker and headphone amplifiers are muted. When muted, the speaker outputs remain biased at VDD / 2.

#### Shutdown

The MAX9789A/MAX9790A feature a low-power shutdown mode, drawing 0.3µA of supply current. By disabling the speaker, headphone amplifiers and the LDO (for MAX9789A), the MAX9789A/MAX9790A enter low-power shutdown mode. Set SPKR\_EN to VDD and HP\_EN and LDO\_EN to GND to disable the speaker amplifiers, headphone amplifiers, and LDO, respectively.

### Click-and-Pop Suppression

#### Speaker Amplifier

The MAX9789A/MAX9790A speaker amplifiers feature Maxim's comprehensive, industry-leading click-and-pop suppression. During startup, the click-and-pop suppression circuitry eliminates any audible transient sources internal to the device. When entering shutdown, the differential speaker outputs ramp to GND quickly and simultaneously.

Figure 4. Enabling Either the Speaker or Headphone Amplifier with a Single Control Pin

#### Headphone Amplifier

In conventional single-supply headphone amplifiers, the output-coupling capacitor is a major contributor of audible clicks and pops. Upon startup, the amplifier charges the coupling capacitor to its bias voltage, typically  $V_{\mbox{\scriptsize DD}}$  / 2. Likewise, during shutdown, the capacitor is discharged to GND. A DC shift across the capacitor results, which in turn, appears as an audible transient at the headphone. Since the MAX9789A/MAX9790A do not require output-coupling capacitors, no audible transient occurs.

Additionally, the MAX9789A/MAX9790A features extensive click-and-pop suppression that eliminates any audible transient sources internal to the device. The startup/shutdown waveform in the *Typical Operating Characteristics* shows that there are minimal spectral components in the audible range at the output.

### \_Applications Information

#### **BTL Speaker Amplifiers**

The MAX9789A/MAX9790A feature speaker amplifiers designed to drive a load differentially, a configuration referred to as bridge-tied load (BTL). The BTL configuration (Figure 5) offers advantages over the single-ended configuration, where one side of the load is connected to ground. Driving the load differentially doubles the output voltage compared to a single-ended amplifier operating under similar conditions. The doubling of the output voltage yields four times the output power at the load.

Since the differential outputs are biased at mid-supply, there is no net DC voltage across the load. This eliminates the need for DC-blocking capacitors required for single-ended amplifiers. These capacitors can be large, expensive, consume board space, and degrade low-frequency performance.

Figure 5. Bridge-Tied Load Configuration

#### **Mono Speaker Configuration**

The MAX9789A stereo BTL Class AB speaker amplifier can be configured to drive a mono speaker. Rather than combining the CODEC's left- and right-input signals in a resistive network prior to one channel of the speaker amplifier input, the transducer itself can be connected to the BTL speaker amplifier output as shown in Figure 6. When compared to the resistive network implementation, the configuration in Figure 6 will:

- 1) Eliminate noise pickup by eliminating the highimpedance node at the CODEC's left- and rightsignal mixing point. SNR performance will be improved as a result.

- Eliminate gain error by eliminating any resistive mismatch between the external resistance used to sum the left and right signals and the MAX9789A internal resistance.

#### **Power Dissipation and Heat Sinking**

Under normal operating conditions, the MAX9789A/MAX9790A can dissipate a significant amount of power. The maximum power dissipation for each package is given in the *Absolute Maximum Ratings* section under Continuous Power Dissipation, or can be calculated by the following equation:

$$P_{DISSPKG(MAX)} = \frac{T_{J(MAX)} - T_{A}}{\theta_{JA}}$$

where  $T_{J(MAX)}$  is +150°C,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the reciprocal of the derating factor in °C/W as specified in the *Absolute Maximum Ratings* section. For example,  $\theta_{JA}$  for the 32-pin TQFN-EP package is +40.2°C/W for a multilayer PC board.

Figure 6. Mono Signal Output Configuration for MAX9789A

#### **Output Power (Speaker Amplifier)**

The increase in power delivered by the BTL configuration directly results in an increase in internal power dissipation over the single-ended configuration. The maximum power dissipation for a given V<sub>DD</sub> and load is given by the following equation:

$$P_{\text{DISS}(MAX)} = \frac{2V_{\text{DD}}^2}{\pi^2 R_{\text{I}}}$$

If the power dissipation for a given application exceeds the maximum allowed for a given package, either reduce V<sub>DD</sub>, increase load impedance, decrease the ambient temperature, or add heat sinking to the device. Large output, supply, and ground PC board traces improve the maximum power dissipation in the package.

Thermal-overload protection limits total power dissipation in these devices. When the junction temperature exceeds +150°C, the thermal-protection circuitry disables the amplifier output stage. The amplifiers are enabled once the junction temperature cools by +15°C. This results in a pulsing output under continuous thermal-overload conditions as the device heats and cools.

#### **Power Supplies**

The MAX9789A/MAX9790A have separate supply pins for each portion of the device, allowing for the optimum combination of headroom and power dissipation and noise immunity. The speaker amplifiers are powered from PVDD. PVDD ranges from 4.5V to 5.5V. The headphone amplifiers are powered from HPVDD and PVSS. HPVDD is the positive supply of the headphone amplifiers and ranges from 3V to 5.5V. PVSS is the negative supply of the headphone amplifiers. Connect PVSS to CPVSS. The charge pump is powered by CPVDD. CPVDD ranges from 3V to 5.5V and should be the same potential as HPVDD. The charge pump inverts the voltage at CPVDD, and the resulting voltage appears at CPVSS. The internal LDO and the remainder of the device is powered by VDD.

# Component Selection Supply Bypassing

The MAX9789A/MAX9790A have separate supply pins for each portion of the device, allowing for the optimum combination of headroom and power dissipation and noise immunity.

#### Speaker Amplifier Power-Supply Input (PV<sub>DD</sub>)

The speaker amplifiers are powered from PV<sub>DD</sub>. PV<sub>DD</sub> ranges from 4.5V to 5.5V. Bypass PV<sub>DD</sub> with a 0.1µF capacitor to PGND. Note additional bulk capacitance is required at the device if long input traces between PV<sub>DD</sub> and the power source are used.

#### Headphone Amplifier Power-Supply Input (HPV<sub>DD</sub> and PV<sub>SS</sub>)

The headphone amplifiers are powered from HPVDD and PVss. HPVDD is the positive supply of the headphone amplifiers and ranges from 3.0V to 5.5V. Bypass HPVDD with a 10 $\mu$ F capacitor to PGND. PVss is the negative supply of the headphone amplifiers. Bypass PVss with a 1 $\mu$ F capacitor to PGND. Connect PVss to CPVss. The charge pump is powered by CPVDD. CPVDD ranges from 3.0V to 5.5V and should be the same potential as HPVDD. Bypass CPVDD with a 1 $\mu$ F capacitor to PGND. The charge pump inverts the voltage at CPVDD, and the resulting voltage appears at CPVss. A 1 $\mu$ F capacitor must be connected between C1N and C1P.

#### Power Supply and LDO Input (V<sub>DD</sub>)

The internal LDO and the remainder of the device is powered by VDD. VDD ranges from 4.5V to 5.5V. Bypass VDD with a 0.1µF capacitor to GND and two 1µF capacitors in parallel to GND. Note additional bulk capacitance is required at the device if long input traces between VDD and the power source are used.

#### Input Filtering

The input capacitor ( $C_{IN}$ ), in conjunction with the amplifier input resistance ( $R_{IN}$ ), forms a highpass filter that removes the DC bias from the incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN}C_{IN}}$$

$R_{IN}$  is the amplifier's internal input resistance value given in the *Electrical Characteristics*. Choose  $C_{IN}$  such that  $f_{-3dB}$  is well below the lowest frequency of interest. Setting  $f_{-3dB}$  too high affects the amplifier's low frequency response. Use capacitors with adequately low voltage coefficient dielectrics, such as 1206-sized X7R ceramic capacitors. Capacitors with higher voltage coefficients result in increased distortion at low frequencies (see Figure 8).

Figure 8. Input Coupling Capacitor-Induced THD vs. Frequency (Headphone Mode)

#### **BIAS Capacitor**

BIAS is the output of the internally generated DC bias voltage. The BIAS bypass capacitor, CBIAS improves PSRR and THD+N by reducing power supply and other noise sources at the common-mode bias node, and also generates the clickless/popless, startup/shutdown DC bias waveforms for the speaker and headphone amplifiers. Bypass BIAS with a 1µF capacitor to GND.

#### Charge-Pump Capacitor Selection

Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric.

#### Flying Capacitor (C1)

The value of the flying capacitor (C1) affects the load regulation and output resistance of the charge pump. A C1 value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Connect a 1µF capacitor between C1P and C1N.

#### Output Capacitor (C2)

The output capacitor value and ESR directly affect the ripple at CPVss. Increasing the value of C2 reduces output ripple. Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels.

#### CPV<sub>DD</sub> Bypass Capacitor (C3)

The CPV<sub>DD</sub> bypass capacitor (C3) lowers the output impedance of the power supply and reduces the impact of the MAX9789A/MAX9790A's charge-pump switching transients. Bypass CPV<sub>DD</sub> with  $1\mu$ F, the same value as C1, and place it physically close to the CPV<sub>DD</sub> and CPGND pins.

#### **Layout and Grounding**

Proper layout and grounding are essential for optimum performance. Use large traces for the power-supply inputs and amplifier outputs to minimize losses due to parasitic trace resistance, as well as route heat away from the device. Good grounding improves audio performance, minimizes crosstalk between channels, and prevents switching noise from coupling into the audio signal. Connect PGND and GND together at a single point on the PC board. Route PGND and all traces that carry switching transients away from GND and the traces and components in the audio signal path.

Connect C2 and C3 to the PGND plane. Connect PVss and CPVss together at C2. Place the charge-pump capacitors (C1, C2, and C3) as close as possible to the device. Bypass PVDD with a  $0.1\mu F$  capacitor to PGND. Place the bypass capacitors as close as possible to the device.

Use large, low-resistance output traces. As load impedance decreases, the current drawn from the device outputs increase. At higher current, the resistance of the output traces decrease the power delivered to the load. For example, if 2W is delivered from the speaker output to a  $4\Omega$  load through a  $100m\Omega$  trace, 49mW is consumed in the trace. If power is delivered through a  $10m\Omega$  trace, only 5mW is consumed in the trace. Large output, supply and GND traces also improve the power dissipation of the device.

The MAX9789A/MAX9790A thin QFN package features an exposed thermal pad on its underside. This pad lowers the package's thermal resistance by providing a direct heat conduction path from the die to the printed circuit board. Connect the exposed thermal pad to GND by using a large pad and multiple vias to the GND plane.

\_Block Diagrams

### \_Block Diagrams (continued)

23

# Windows Vista-Compliant, Stereo Class AB Speaker Amplifiers and DirectDrive Headphone Amplifiers

System Diagrams (continued)

M/XI/M \_\_\_\_\_

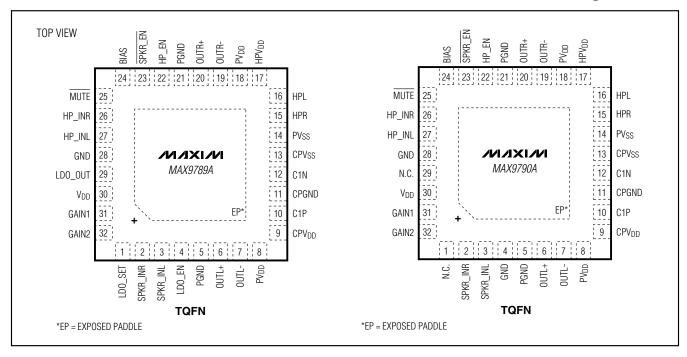

### Pin Configurations

# Simplified Block Diagrams (continued)

**Chip Information**

PROCESS: BICMOS

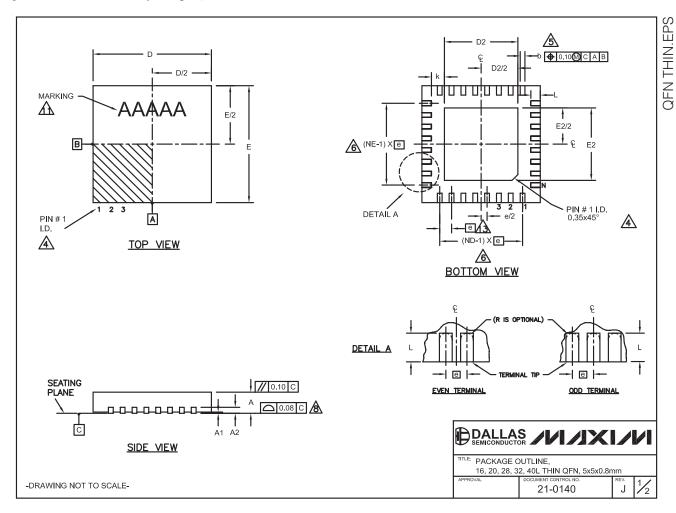

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

|        | COMMON DIMENSIONS |        |      |      |        |      |           |       |            |         |           |      |          |       |      |

|--------|-------------------|--------|------|------|--------|------|-----------|-------|------------|---------|-----------|------|----------|-------|------|

| PKG.   | 1                 | 6L 5x  | 5    | 2    | OL 5>  | :5   | 2         | 8L 5  | <b>√</b> 5 | 32L 5x5 |           |      | 40L 5x5  |       |      |

| SYMBOL | MIN.              | NOM.   | MAX. | MIN. | NOM.   | MAX. | MIN.      | NOM.  | MAX.       | MIN.    | NOM.      | MAX. | MIN.     | NOM.  | MAX. |

| Α      | 0.70              | 0.75   | 0.80 | 0.70 | 0.75   | 0.80 | 0.70      | 0.75  | 0.80       | 0.70    | 0.75      | 0.80 | 0.70     | 0.75  | 0.80 |

| A1     | 0                 | 0.02   | 0.05 | 0    | 0.02   | 0.05 | 0         | 0.02  | 0.05       | 0       | 0.02      | 0.05 | 0        | 0.02  | 0.05 |

| A2     | 0.                | 20 RE  | F.   | 0.   | 20 RE  | F.   | 0.        | 20 RE | F.         | 0.      | 20 RE     | F.   | 0.       | 20 RE | F.   |

| b      | 0.25              | 0.30   | 0.35 | 0.25 | 0.30   | 0.35 | 0.20      | 0.25  | 0.30       | 0.20    | 0.25      | 0.30 | 0.15     | 0.20  | 0.25 |

| D      | 4.90              | 5.00   | 5.10 | 4.90 | 5.00   | 5.10 | 4.90      | 5.00  | 5.10       | 4.90    | 5.00      | 5.10 | 4.90     | 5.00  | 5.10 |

| Е      | 4.90              | 5.00   | 5.10 | 4.90 | 5.00   | 5.10 | 4.90      | 5.00  | 5.10       | 4.90    | 5.00      | 5.10 | 4.90     | 5.00  | 5.10 |

| е      | 0                 | .80 BS | SC.  | 0    | .65 BS | SC.  | 0.50 BSC. |       | 0.50 BSC.  |         | 0.40 BSC. |      | SC.      |       |      |

| k      | 0.25              | -      | -    | 0.25 | -      | -    | 0.25      | -     | -          | 0.25    | -         | -    | 0.25     | -     | -    |

| L      | 0.30              | 0.40   | 0.50 | 0.45 | 0.55   | 0.65 | 0.45      | 0.55  | 0.65       | 0.30    | 0.40      | 0.50 | 0.30     | 0.40  | 0.50 |

| N      |                   | 16     |      |      | 20     |      |           | 28    |            | 32      |           |      | 40       |       |      |

| ND     |                   | 4      |      |      | 5      |      |           | 7     |            | 8       |           |      | 10       |       |      |

| NE     |                   | 4      |      |      | 5      |      | 7         |       | 8          |         | 10        |      |          |       |      |

| JEDEC  | 1                 | WHHE   | 3    |      | WHH    | )    | ٧         | \/HH□ | )-1        | ٧       | VHHD      | -2   | <b> </b> |       |      |

| NE   | 4    | 5    | 7      |   |

|------|------|------|--------|---|

| EDEC | WHHB | WHHC | WHHD-1 | Γ |

|      |      |      |        |   |

| NIO- | TEC. |

|------|------|

|      |      |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

⚠ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

$\triangle$  DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

⚠ ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR T2855-3 AND T2855-6.

WARPAGE SHALL NOT EXCEED 0.10 mm.

11. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

12. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |  |

|------------------------|------|------|------|------|------|------|--|--|--|

| PKG.                   | D2   |      | E2   |      |      |      |  |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |  |  |  |

| T1655-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T1655-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T1655N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T2055-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T2055-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T2055-5                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855-3                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855-4                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |  |

| T2855-5                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |  |

| T2855-6                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855-7                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |  |

| T2855-8                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855N-1               | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T3255-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255-5                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T4055-1                | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |  |

| T4055-2                | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |  |

PACKAGE OUTLINE, 16, 20, 28, 32, 40L THIN QFN, 5x5x0.8mm

21-0140