### LM2724A

# **High Speed 3A Synchronous MOSFET Driver**

### **General Description**

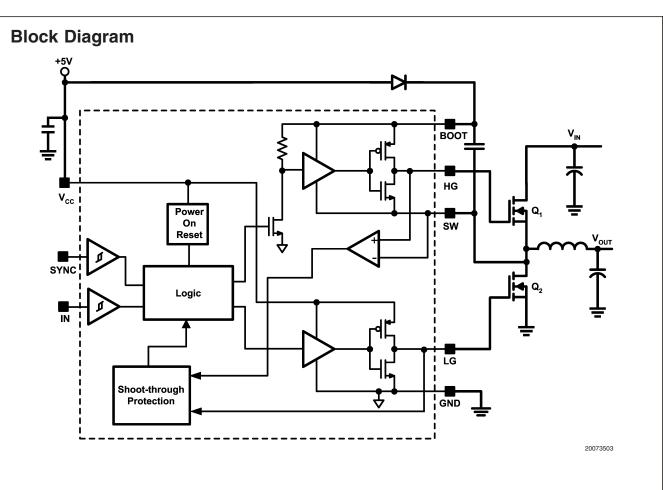

The LM2724A is a dual N-channel MOSFET driver which can drive both the top and bottom MOSFETs in a push-pull structure simultaneously. The LM2724A takes a logic input and splits it into two complimentary signals with a typical 20ns dead time in between. The built-in cross-conduction protection circuitry prevents the top and bottom MOSFETs from turning on simultaneously. With a bias voltage of 5V, the peak sourcing and sinking current for each driver of the LM2724A is about 3A. Input UVLO (Under-Voltage-Lock-Out) ensures that all the driver outputs stay low until the supply rail exceeds the power-on threshold during system power on, or after the supply rail drops below power-on threshold by a specified hysteresis during system power down. The cross-conduction protection circuitry detects both driver outputs and will not turn on a driver until the other driver output is low. The top gate voltage needed by the top MOSFET is obtained through an external boot-strap structure. When not switching, the LM2724A only draws up to

$195\mu A$  from the 5V rail. The synchronization operation of the bottom MOSFET can be disabled by pulling the SYNC pin to ground.

#### **Features**

- Shoot-through protection

- Input Under-Voltage-Lock-Out

- 3A peak driving current

- 195µA quiescent current

- 28V input voltage in buck configuration

- SO-8 and LLP packages

#### **Applications**

- High Current DC/DC Power Supplies

- High Input Voltage Switching Regulators

- Fast Transient Microprocessors

- Notebook Computers

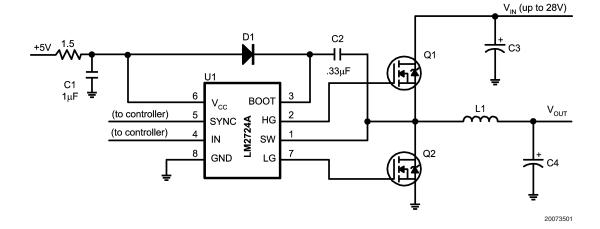

### **Typical Application**

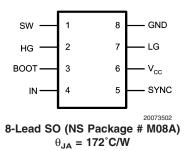

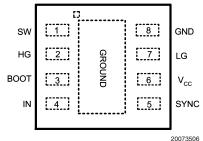

# **Connection Diagram**

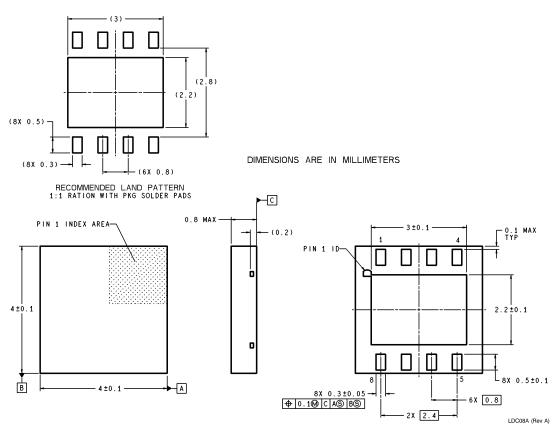

8-Lead LLP (NS Package # LDC08A)  $\theta_{JA} = 39^{\circ}\text{C/W}$

## **Ordering Information**

| Order Number | Size   | NSC Package<br>Drawing | Supplied As     |

|--------------|--------|------------------------|-----------------|

| LM2724AM     | SO-8   | M08A                   | 95 Units/Rail   |

| LM2724AMX    |        |                        | 2500 Units/Reel |

| LM2724ALD    | LDC08A | LDC08A                 | 1000 Units/Rail |

| LM2724ALDX   |        |                        | 4500 Units/Reel |

### **Pin Descriptions**

| Pin | Name            | Function                                                                         |  |  |

|-----|-----------------|----------------------------------------------------------------------------------|--|--|

| 1   | SW              | Top driver return. Should be connected to the common node of top and bottom FETs |  |  |

| 2   | HG              | Top gate drive output. Should be connected to the top FET gate.                  |  |  |

| 3   | воот            | Bootstrap. Accepts a bootstrap voltage for powering the high-side driver         |  |  |

| 4   | IN              | Accepts a logic control signal                                                   |  |  |

| 5   | SYNC            | Bottom gate enable                                                               |  |  |

| 6   | V <sub>CC</sub> | Connect to +5V supply                                                            |  |  |

| 7   | LG              | Bottom gate drive output. Should be connected to the bottom FET gate.            |  |  |

| 8   | GND             | Ground                                                                           |  |  |

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

V<sub>CC</sub>

7V

BOOT to SW

7V

BOOT to GND (Note 2)

35V

SW to GND

30V

Junction Temperature

+150°C

Power Dissipation

720mW (SO-8)

(Note 3)

3.2W (LLP-8)

Storage Temperature -65°C to 150°C ESD Susceptibility

Human Body Model (Note 4) 2.0 kV Soldering Time, Temperature 10sec., 300°C

### **Operating Ratings** (Note 1)

V<sub>CC</sub> 4.3V to 6.8V Junction Temperature Range -40°C to 125°C

# Electrical Characteristics LM2724A

$V_{CC}$  = BOOT = SYNC = 5V, SW = GND = 0V, unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_{.J} = +25$ °C. Limits appearing in **boldface** type apply over the entire operating temperature range.

| Symbol                 | Parameter                                              | Condition                               | Min | Тур  | Max | Units           |

|------------------------|--------------------------------------------------------|-----------------------------------------|-----|------|-----|-----------------|

| POWER SUPP             | PLY                                                    |                                         |     |      |     |                 |

| I <sub>q_op</sub>      | Operating Quiescent<br>Current                         | IN = 0V                                 |     | 145  | 195 | μА              |

| TOP DRIVER             | -                                                      |                                         |     |      |     |                 |

|                        | Peak Pull-Up Current                                   |                                         |     | 3.0  |     | Α               |

|                        | Pull-Up Rds_on                                         | $I_{BOOT} = I_{HG} = 0.3A$              |     | 1.2  |     | Ω               |

|                        | Peak Pull-down Current                                 |                                         |     | -3.2 |     | А               |

|                        | Pull-down Rds_on                                       | $I_{SW} = I_{HG} = 0.3A$                |     | 0.5  |     | Ω               |

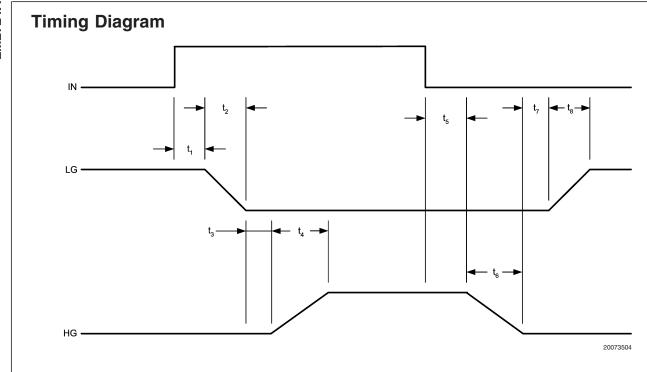

| t <sub>4</sub>         | Rise Time                                              | Timing Diagram, C <sub>LOAD</sub> =     |     | 17   |     | ns              |

| t <sub>6</sub>         | Fall Time                                              | 3.3nF                                   |     | 12   |     | ns              |

| t <sub>3</sub>         | Pull-Up Dead Time                                      | Timing Diagram                          |     | 19   |     | ns              |

| t <sub>5</sub>         | Pull-Down Delay                                        | Timing Diagram, from IN Falling Edge    |     | 27   |     | ns              |

| BOTTOM DRIV            | VER                                                    |                                         |     |      |     | '               |

|                        | Peak Pull-Up Current                                   |                                         |     | 3.2  |     | А               |

|                        | Pull-up Rds_on                                         | $I_{VCC} = I_{LG} = 0.3A$               |     | 1.1  |     | Ω               |

|                        | Peak Pull-down Current                                 |                                         |     | 3.2  |     | А               |

|                        | Pull-down Rds_on                                       | $I_{GND} = I_{LG} = 0.3A$               |     | 0.6  |     | Ω               |

| t <sub>8</sub>         | Rise Time                                              | Timing Diagram, C <sub>LOAD</sub> =     |     | 17   |     | ns              |

| t <sub>2</sub>         | Fall Time                                              | 3.3nF                                   |     | 14   |     | ns              |

| t <sub>7</sub>         | Pull-up Dead Time                                      | Timing Diagram                          |     | 22   |     | ns              |

| t <sub>1</sub>         | Pull-down Delay                                        | Timing Diagram                          |     | 13   |     | ns              |

| LOGIC                  | •                                                      |                                         |     |      |     | •               |

| $V_{uvlo\_up}$         | V <sub>CC</sub> Under-Voltage-Lock-Out Upper Threshold | V <sub>CC</sub> rises from 0V toward 5V |     |      | 4   | V               |

| $ m V_{uvlo\_dn}$      | V <sub>CC</sub> Under-Voltage-Lock-Out Lower Threshold | VCC falls from 5V toward<br>0V          | 2.5 |      |     | V               |

| V <sub>uvlo_hys</sub>  | V <sub>CC</sub> Under-Voltage-Lock-Out Hysteresis      | V <sub>CC</sub> falls from 5V toward 0V |     | 0.8  |     | V               |

| V <sub>IH_SYNC</sub>   | SYNC Pin High Input                                    | SYNC Pin High Input 55%                 |     |      |     |                 |

| V <sub>IL_SYNC</sub>   | SYNC Pin Low Input                                     |                                         | 25% |      | 25% | V <sub>CC</sub> |

| I <sub>leak_SYNC</sub> | SYNC Pin Leakage                                       | SYNC = 5V, Sink Current                 |     |      | 2   |                 |

|                        | Current                                                | SYNC = 0V, Source Current               |     |      | 10  | μA              |

# **Electrical Characteristics**

LM2724A (Continued)

$V_{CC}$  = BOOT = SYNC = 5V, SW = GND = 0V, unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire operating temperature range.

| Symbol                | Parameter                 | Condition                  | Min | Тур | Max | Units           |

|-----------------------|---------------------------|----------------------------|-----|-----|-----|-----------------|

| I <sub>leak_IN</sub>  | IN Pin Leakage Current    | IN = 0V, Source Current    |     |     | 2   | μΑ              |

|                       |                           | IN = 5V, Sink Current      |     |     | 10  |                 |

| t <sub>on_min1</sub>  | Minimum Positive Pulse    |                            |     |     |     |                 |

|                       | Width at IN Pin           |                            |     | 160 |     |                 |

|                       | (Note 5)                  |                            |     |     |     |                 |

| t <sub>on_min2</sub>  | Minimum Positive Pulse    |                            |     |     |     |                 |

|                       | Width at IN Pin for HG to |                            |     | 45  |     |                 |

|                       | Respond                   |                            |     | 45  |     |                 |

|                       | (Note 6)                  |                            |     |     |     |                 |

| t <sub>on_min3</sub>  | Minimum Positive Pulse    |                            |     |     |     |                 |

|                       | Width at IN Pin for LG to |                            |     | 10  |     |                 |

|                       | Respond                   |                            |     | 10  |     | ns              |

|                       | (Note 7)                  |                            |     |     |     |                 |

| t <sub>off_min1</sub> | Minimum Negative Pulse    |                            |     |     |     |                 |

|                       | Width at IN Pin for LG to |                            |     | 40  |     |                 |

|                       | Respond                   |                            |     | 40  |     |                 |

|                       | (Note 8)                  |                            |     |     |     |                 |

| t <sub>off_min2</sub> | Minimum Negative Pulse    |                            |     |     |     |                 |

|                       | Width at IN Pin for HG to |                            |     | 5   |     |                 |

|                       | Respond                   |                            |     |     |     |                 |

|                       | (Note 9)                  |                            |     |     |     |                 |

| V <sub>IH_IN</sub>    | IN High Level Input       | When IN pin goes high from | 55% |     |     |                 |

|                       | Voltage                   | 0V                         | 35% |     |     | V <sub>CC</sub> |

| $V_{IL\_IN}$          | IN Low Level Input        | When IN pin goes low from  |     |     | 25% | v cc            |

|                       | Voltage                   | 5V                         |     |     |     |                 |

|                       |                           |                            |     |     |     |                 |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating ratings are conditions under which the device operates correctly. The gaurnteed specifications apply only for the listed test conditions. Some performance characteristics may degrade when the part is not operated under listed conditions.

Note 2: If BOOT voltage exceeds this value, the ESD structure will degrade.

Note 3: Maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{JMAX}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_{A}$ . The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{MAX} = (T_{JMAX} - T_A) / \theta_{JA}$ . The junction-to-ambient thermal resistance,  $\theta_{JA}$ , for LM2724A is 172°C/W. For a  $T_{JMAX}$  of 150°C and  $T_A$  of 25°C, the maximum allowable power dissipation is 0.7W. The  $\theta_{JA}$ , for LM2724A LLP package is 39°C/W. For a  $T_{JMAX}$  of 150°C and  $T_A$  of 25°C, the maximum allowable power dissipation is 3.2W.

Note 4: ESD machine model susceptibility is 200V.

Note 5: If the positive pulse width at IN pin is below this value but above  $t_{on\_min2}$ , the pulse is internally stretched to  $t_{on\_min1}$ , so the HG width will be a constant value.

Note 6: If the positive pulse width at IN pin is below this value but above t<sub>on\_min3</sub>, then HG stops responding while LG still responds to the pulse.

Note 7: If the positive pulse width at IN pin is below this value, the pulse will be completely ignored. Neither HG or LG will respond to it.

Note 8: If the negative pulse width at IN pin is below this value but above toff\_min2, then LG stops responding while HG still responds.

Note 9: If the negative pulse width at IN pin is below this value, the pulse will be completely ignored. Neither HG or LG will respond to it.

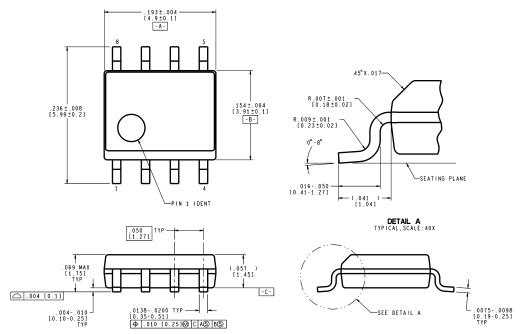

# Physical Dimensions inches (millimeters) unless otherwise noted

#### CONTROLLING DIMENSION IS INCH

M08A (Rev J)

8-Lead Small Outline Package Order Number LM2724AM, LM2724AMX NS Package Number M08A

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

8-Lead LLP Package

Order Number LM2724ALD, LM2724ALDX

NS Package Number LDC08A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Americas Customer Support Center Email: new feedback@nsc.ci

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.