EM MICROELECTRONIC - MARIN SA

# **3V Self Recovering Watchdog**

#### Description

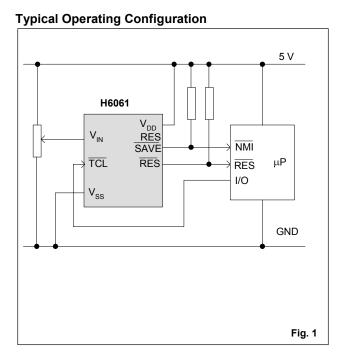

The H6061 is a combined initialiser, watchdog and voltage monitor. The circuit is a low voltage low power monolithic CMOS device combining a series of voltage comparators and a programmable timer on the same chip. The device is specially suited to telecommunications applications where 3 V working is expected, for functions such as supply voltage and microprocessor monitoring. The reset outputs are self recovering after a watchdog timeout, enabling the circuit to work with standalone systems without any external push-switch or control signal to restart after a watchdog timeout. The circuit provides a reset signal of both polarities. The state of the outputs is defined down to 1.6 V. An internal debouncer ensures power-up performance for fast-rise supply lines.

## Features

- Watchdog fully operational from 2.7 to 5.25 V

- Regulated DC voltage monitor, internal voltage reference

- □ Self recovering watchdog function: reset goes active after the 1st timeout period, reset goes inactive again after the 2nd timeout period, repeated active reset signal until the system recovers

- □ Standard timeout period and power-on reset time (100 ms), externally programmable from 3 ms to 3 mins if required

- □ Works down to 1.6 V supply voltage

- Low voltage alarm prior to reset on power-down

- Reset outputs of both polarities

- Open drain outputs

- □ SO8 package

#### Applications

- Microprocessor and microcontroller systems

- Depint of sales equipment

- Telecom products

- Automotive subsystems

- □ Microcontroller 68HC05 applications

# **Pin Assignment**

| V <sub>IN</sub><br>TCL<br>RC<br>V <sub>SS</sub> | H6061 | V <sub>DD</sub><br>RES<br>SAVE<br>RES |

|-------------------------------------------------|-------|---------------------------------------|

|                                                 |       | <br>Fig. 2                            |

# A COMPANY OF THE SWATCH GROUP

Downloaded from Elcodis.com electronic components distributor

2

# Absolute Maximum Ratings

| Parameter                                                   | Symbol            | Conditions       |

|-------------------------------------------------------------|-------------------|------------------|

| Voltage V <sub>DD</sub> to V <sub>SS</sub>                  | V <sub>DD</sub>   | – 0.3 to + 5.6 V |

| Voltage at any pin to V <sub>SS</sub>                       | V <sub>MIN</sub>  | - 0.3            |

| Voltage at any pin to V <sub>DD</sub>                       | V <sub>MAX</sub>  | + 0.3            |

| Voltage at $V_{IN}$ to $V_{SS}$                             | VINMAX            | + 12 V           |

| Current at any output                                       | I <sub>MAX</sub>  | ± 10 mA          |

| Storage temperature                                         | T <sub>STO</sub>  | -65°C to +150°C  |

| Electrostatic discharge max. to<br>MIL-STD-833C method 3014 | V <sub>Smax</sub> | 1000V            |

|                                                             |                   | Table 1          |

Stresses above these listed maximum ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

#### **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level.

## **Operating Conditions**

| Parameter                           | Symbol          | Min. | Max. | Units |

|-------------------------------------|-----------------|------|------|-------|

| Operating temperature<br>Industrial | T <sub>AI</sub> | -40  | +85  | °C    |

| Supply voltage                      | V <sub>DD</sub> | 2.7  | 5.25 | V     |

| Version 11,12                       | V <sub>IN</sub> | 0    | 12   | V     |

| RC-oscillator programming           |                 |      |      |       |

| External capacitance*               | C1              |      | 1    | μF    |

| External resistance                 | R1              | 10   |      | kΩ    |

\* Leakage < 1μA

Table 2

#### **Electrical Characteristics**

$V_{\text{DD}}$  = 5.0 V,  $T_{\text{A}}$  = –40 to +85 °C, unless otherwise specified

| Parameter                              | Symbol           | Test Conditions                                                        | Min. | Тур.                 | Max. | Units |

|----------------------------------------|------------------|------------------------------------------------------------------------|------|----------------------|------|-------|

| V <sub>DD</sub> activation threshold   | V <sub>ON</sub>  | T₄ = 25 °C                                                             | 2.3  |                      | 2.7  | V     |

| V <sub>DD</sub> deactivation threshold | VOFF             | T <sub>A</sub> = 25 °C                                                 |      | V <sub>ON</sub> -0.3 |      | V     |

| Supply current                         | I <sub>DD</sub>  | RC open, $\overline{\text{TCL}}$ at V <sub>DD</sub> or V <sub>SS</sub> |      | 80                   | 140  | μA    |

| Input V <sub>IN</sub> , TCL            |                  |                                                                        |      |                      |      |       |

| Leakage current                        | I <sub>P</sub>   | $V_{SS} < V_{IP} < V_{DD}$                                             |      | 0.005                | 1    |       |

|                                        |                  | $T_A = 80 \degree C$                                                   |      | 0.005                | I    | μA    |

| TCL input low level                    | VIL              |                                                                        |      |                      | 0.8  | V     |

| TCL input high level                   | VIH              |                                                                        | 2.4  |                      |      | V     |

| Leakage on pins SAVE , RES , RES       | I <sub>OLK</sub> | $V_{OUT} = V_{DD}$                                                     |      | 0.050                | 1    | μA    |

| O/P drive logic low                    | I <sub>OL</sub>  | V <sub>OL</sub> = 0.4 V                                                | 4    | 8                    |      | mA    |

|                                        | I <sub>OL</sub>  | $V_{DD}$ = 3.5 V; $V_{OL}$ = 0.4 V                                     | 2    |                      |      | mA    |

|                                        | IOL              | V <sub>DD</sub> = 1.6 V; V <sub>OL</sub> = 0.4 V                       | 80   |                      |      | μA    |

#### V<sub>IN</sub> Surveillance

Voltage thresholds at T\_A = 25  $^\circ\text{C}$

| Ver | rsion No. | Tł<br>V <sub>SH</sub> | reshol<br>V <sub>SL</sub> | ds<br>V <sub>RL</sub> | at V <sub>DD</sub> | Threshold Voltage<br>Tolerance | Threshold<br>Ratio* | Pin V <sub>IN</sub><br>Input |

|-----|-----------|-----------------------|---------------------------|-----------------------|--------------------|--------------------------------|---------------------|------------------------------|

|     | 25        | 1.54                  | 1.50                      | 1.46                  | 2.7 – 5.0 V        | ±10%                           | ±2%                 | ~100 MΩ                      |

\* Threshold ratio defined as  $V_{\text{SH}}$  /  $V_{\text{SL}}$  or  $V_{\text{SL}}$  /  $V_{\text{RL}}.$

#### **Timing Characteristics**

$V_{DD}$  = 5.0 V,  $T_A$  = -40 °C to +85 °C, unless otherwise specified

| Parameter                                   | Symbol            | Test Conditions                             | Min. | Тур.                | Max. | Units |

|---------------------------------------------|-------------------|---------------------------------------------|------|---------------------|------|-------|

| Propagation delays                          |                   |                                             |      |                     |      |       |

| TCL to output pins                          | T <sub>DIDO</sub> |                                             |      | 250                 | 500  | ns    |

| V <sub>IN</sub> to output pins              | T <sub>AIDO</sub> | Excluding debounce time T <sub>DB</sub>     |      | 4                   | 10   | μs    |

| Logic transition times on all output pins   | T <sub>TR</sub>   | Load 10 k $\Omega$ , 100 pF                 |      | 30                  | 100  | ns    |

| Timeout period                              | T <sub>TO</sub>   | RC open, unshielded, $T_A = 25 \ ^{\circ}C$ | 60   | 100                 | 160  | ms    |

| T <sub>TCL</sub> input pulse width          | T <sub>TCL</sub>  |                                             | 150  |                     |      | ns    |

| Power-on reset debounce                     | T <sub>DB</sub>   |                                             |      | T <sub>TO</sub> /64 |      | ms    |

| Fastest pulse V <sub>IN</sub> with debounce | T <sub>VINL</sub> | -40 to +85 °C                               | 10   |                     |      | μs    |

Table 5

H6061

Table 4

Table 3

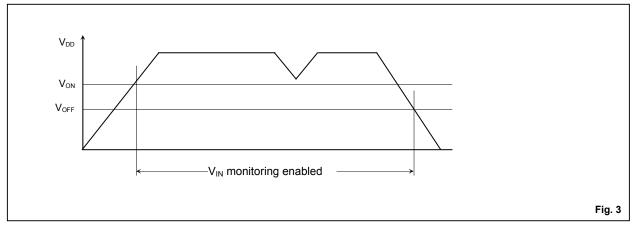

# Timing Waveforms Voltage Reaction: V<sub>DD</sub> Monitoring

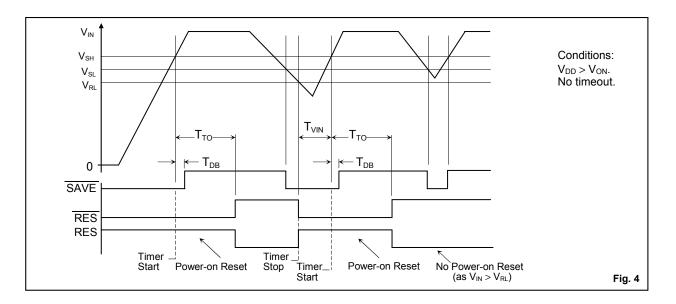

# Voltage Reaction: $V_{\mbox{\scriptsize IN}}$ Monitoring

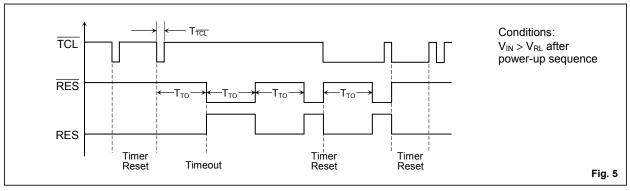

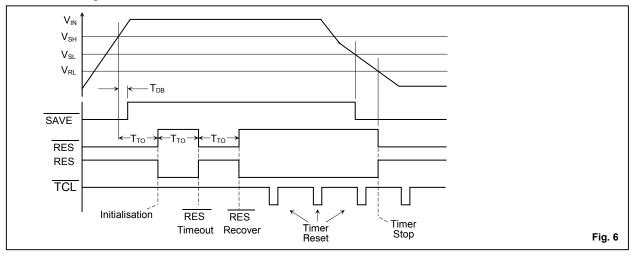

# **Timer Reaction**

# **Combined Voltage and Timer Reaction**

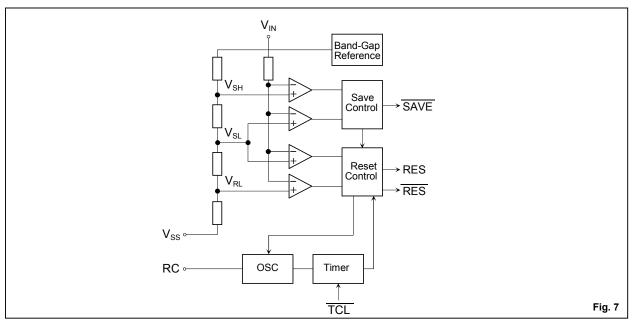

# Block Diagram

#### **Pin Description**

| Pin | Name            | Function                          |

|-----|-----------------|-----------------------------------|

| 1   | V <sub>IN</sub> | Voltage monitoring input          |

| 2   | TCL             | Timer clear input signal          |

| 3   | RC              | RC oscillator tuning input        |

| 4   | Vss             | GND terminal                      |

| 5   | RES             | Reset output, open drain          |

| 6   | SAVE            | Save output, open drain           |

| 7   | RES             | Positive reset output, open drain |

| 8   | V <sub>DD</sub> | Positive supply voltage           |

Table 6

#### Functional Description Thresholds and Outputs

The H6061 has open-drain outputs and voltage thresholds on pin  $V_{IN}$  of typically 1.5 V.

#### Internal Voltage Comparators

The voltage comparators detect the voltage applied to pin  $V_{\text{IN}}$  and compare it with thresholds  $V_{\text{SH}},\,V_{\text{SL}}$  and  $V_{\text{RL}}.$  The H6061 is designed for monitoring regulated DC voltages and has bandgap thresholds independent of  $V_{DD}$ . The reaction of the H6061 to voltage changes on pin  $V_{IN}$  is given in Fig. 4. During powering-up, the outputs are active. After  $V_{\text{IN}}$  reaches the  $V_{\text{SH}}$  level, pin  $\overline{\text{SAVE}}$  deactivates after a short debounce time  $T_{DB}$  to allow for fast ramp-ups. The initialization time  $T_{TO}$  then passes before the two reset outputs go inactive. Thereafter, when the voltage on pin  $V_{\ensuremath{\mathbb{N}}\xspace}$ falls below the  $V_{\text{SL}}$  level, pin  $\overline{\text{SAVE}}$  goes active low as a first warning. If V<sub>IN</sub> then drops below the V<sub>RL</sub> level, the reset signals go active and are guaranteed down to 1.6 V. The reset outputs react also to timeouts (see "Timer clearing"). Note that when the supply voltage  $V_{DD}$  is below the level V<sub>OFF</sub> (about 2.2 V), all outputs are in the active state for any allowed voltage of VIN.

#### Voltage Programming

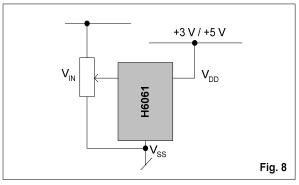

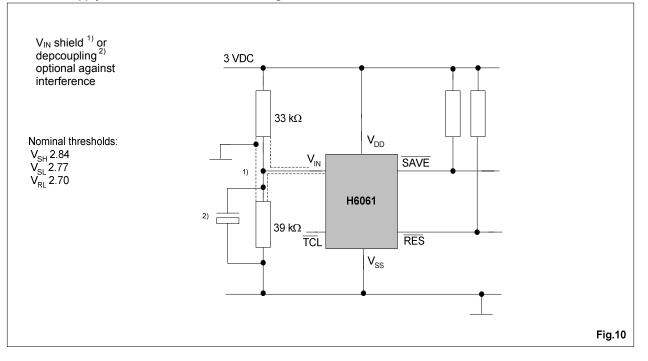

The H6061 was designed to give the best compromise in normal usage (see Table 3). Its voltage threshold can be programmed by an external resistor divider or a potentiometer to react at proportionally higher voltage levels (see Fig. 8 below).

Voltage Programming

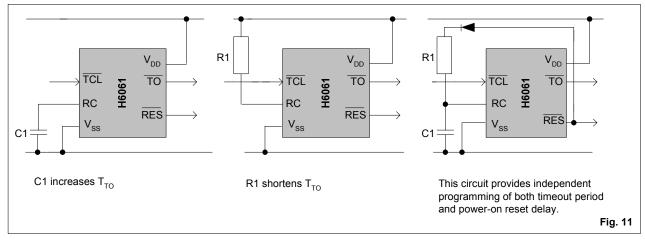

#### **Timer Programming**

A single timeout period  $T_{TO}$  is used for the initialization reset duration and the watchdog timeout. With pin RC unconnected, the on-chip RC oscillator and divider chain give a timeout period  $T_{TO}$  of typically 100 ms. A resistor to  $V_{DD}$  will shorten this time, and a capacitor to  $V_{SS}$  will lengthen it (see Fig. 11). An approximation for calculating trial values given in milliseconds by the formula:

$$T_{TO} = \begin{bmatrix} 0.75 + \frac{(32 + C_1) \bullet 1.6}{4.8 + \frac{V_{DD} - 0.8}{R_1}} \end{bmatrix} \bullet 8.192$$

$R_{1 \text{ min.}}$  = 10 k $\Omega$ ,  $C_{1 \text{ max.}}$  = 1  $\mu$ F If  $R_1$  is in M $\Omega$  and  $C_1$  in pF,  $T_{TO}$  will be in ms.

Choice of component values must be determined in practice. To have a square wave of period  $2T_{TO}$ , simply connect pin  $\overline{TCL}$  to  $V_{DD}$  or  $V_{SS}$  and take the signal output from a reset pin.

#### **Timer Clearing**

A negative edge or pulse at the  $\overline{TCL}$  input longer than 150 ns will clear the timer and deactivate the reset outputs under normal running conditions (see Fig. 3).  $\overline{TCL}$  will however have no effect either when  $V_{DD} < V_{OFF}$  or during the initialization period before the deactivation of the reset pins.

#### **Combined Voltage and Timer Action**

In Fig. 6 is a typical sequence of power-up, watchdog run, and power-down. During initialization the SAVE pin deactivates one debounce delay time  $T_{\text{DB}}$  after  $V_{\text{IN}}$  rises above  $V_{\text{SH}},$  or when the power line  $V_{\text{DD}}$  rises above  $V_{\text{ON}},$ whichever happens last. The reset pins only deactivate one timeout period  $T_{TO}$  afterwards to free the watchdog timer and end the initialization. Note that either  $V_{IN}$  falling below V<sub>RL</sub> threshold or V<sub>DD</sub> below V<sub>ON</sub> will cause an initialization upon recovery. Following initialization, the watchdog timer will time out after time  $T_{TO}$  unless at least one  $\overline{TCL}$  pulse clears it. On timeout the reset pins reactivate for a further  $T_{TO}$  period before deactivating again for another try. A TCL pulse will deactivate any timeout reset, and another TCL pulse must follow within a time  $T_{TO}$  to keep reset inactive. If no TCL pulses come at all, the reset pins go square-wave. Power-down overrides all this however. A falling voltage on  $V_{IN}$  gives a warning  $\overline{SAVE}$  = 0 signal at  $V_{IN}$  =  $V_{SL}$  before activating the reset pins as soon as  $V_{\text{IN}}$  drops below  $V_{\text{RL}}$ The H6061 has fixed thresholds and low hysteresis for monitoring regulated DC lines. Additional protection is provided in case  $V_{DD}$  supply falls over about 10% below  $V_{ON}$ which thereupon activates all outputs at once.

# Typical Applications

#### Selection of Watchdogs for Each Application

The H6061 is designed for monitoring regulated DC voltages anywhere between 2.7 and 5.25 V. Typically, it is used to monitor  $V_{DD}$  with pin  $V_{IN}$  tied to the midpoint of a voltage divider (see Fig. 8). This arrangement has the advantage of being able to trigger at selectable voltage limits, i. e. it can be used where the regulated voltage is below 5 VDC.

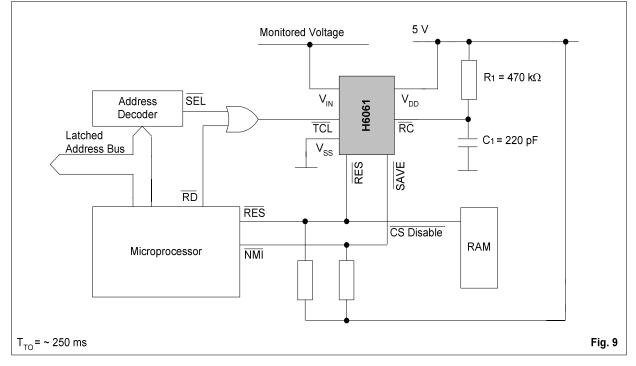

#### Industrial Heavy-Duty Utilisation

The H6061 debounce protects against reactions due to fastrise power lines, but absolute maximum ratings must be respected. With its flexibility of voltage programming and supply voltage the H6061 can allow for voltage drops along supply lines, so it can be placed remotely, like on plug-in boards (see Fig. 9). The H6061 is suitable for supply voltages down to 2.7 VDC. As the H6061 is designed to be sensitive to voltage changes, fast switching lines, like address/data bus lines should not be run between the V<sub>DD</sub> and V<sub>SS</sub> supply lines near the H6061 without ground-plane shielding. Tracks from components to pin RC must be kept very short. Pin RC if left free should be shielded with a ground ring in noisy environments. The H6061 has only 40 mV hysteresis specially for monitoring regulated DC. Pin V<sub>IN</sub> must be protected from any significant mains ripple or RFI (see Fig. 10). It should be placed as near as possible to the point where voltage is to be monitored. Pin V<sub>IN</sub> is protected by an internal resistor (nominal 15 k $\Omega$ ) against voltages in excess of V<sub>DD</sub>. In some environments this may however pick up enough mains ripple or RFI to distort the voltage detection thresholds or even cause unwanted sporadic resets in the absence of adequate shielding or filtering on V<sub>IN</sub>.

The H6061 has sufficient immunity to ripple and interference on the  $V_{\text{DD}}$  supply line, but if it is important that a system meet severe criteria for injected spikes and RFI, then care must be taken also decouple  $V_{DD}$  from these influences, as system protection must continue even under these conditions. With normal series voltage regulators, the regulated 5 VDC output voltage follows the DC rough voltage within 1.5 V on powering up. If the application has pin V<sub>IN</sub> monitoring the DC rough, the internal inputs to the on-chip comparators will not rise above V<sub>DD</sub> if the H6061 is correctly programmed. With switched-mode power supplies however, the DC-rough voltage on power-up rises almost to its working level before the 5 VDC line starts to ramp up. The H6061 has been specially designed to work under these extreme conditions but care must be taken not to exceed absolute maximum ratings. In addition to the voltage monitoring on pin  $V_{IN}$ , a final protection is given by the H6061 monitoring its own V<sub>DD</sub> supply. If a system malfunction causes V<sub>DD</sub> to fall below V<sub>OFF</sub> even though pin VIN stays high, then all outputs go active at once.

# Combined Supply Monitor, Initializer and Watchdog

# External Programming of RC Oscillator

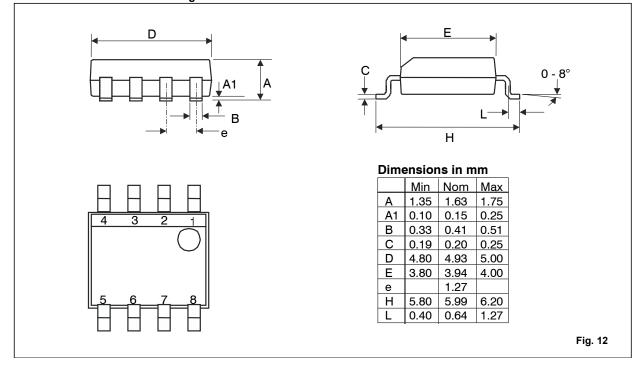

#### Package Information Dimensions of 8-Pin SOIC Package

# **Ordering Information**

When ordering, please specify the complete Part Number

| Part Number  | Version | Package    | Delivery<br>Form | Package Marking<br>(first line) | Temperature    |

|--------------|---------|------------|------------------|---------------------------------|----------------|

| H6061V25SO8A | V25     | 8-pin SOIC | Stick            | 606125                          | -40°C to +85°C |

| H6061V25SO8B | V25     | 8-pin SOIC | Tape&Reel        | 606125                          | -40 C 10 +85 C |

Note: other versions are no longer available

EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.

© EM Microelectronic-Marin SA, 07/04, Rev. H

Downloaded from Elcodis.com electronic components distributor