HD-6402

# **CMOS Universal Asynchronous Receiver Transmitter (UART)**

March 1997

#### **Features**

- 8.0MHz Operating Frequency (HD-6402B)

- 2.0MHz Operating Frequency (HD-6402R)

- Low Power CMOS Design

- Programmable Word Length, Stop Bits and Parity

- · Automatic Data Formatting and Status Generation

- Compatible with Industry Standard UARTs

- Single +5V Power Supply

- CMOS/TTL Compatible Inputs

## Description

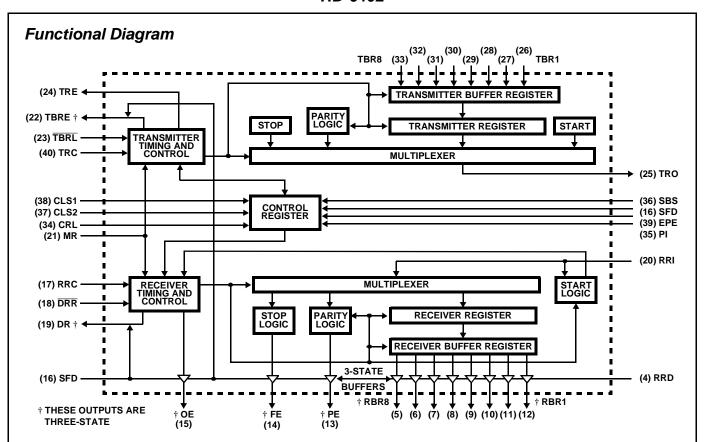

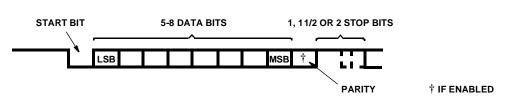

The HD-6402 is a CMOS UART for interfacing computers or microprocessors to an asynchronous serial data channel. The receiver converts serial start, data, parity and stop bits. The transmitter converts parallel data into serial form and automatically adds start, parity and stop bits. The data word length can be 5, 6, 7 or 8 bits. Parity may be odd or even. Parity checking and generation can be inhibited. The stop bits may be one or two or one and one-half when transmitting 5-bit code.

The HD-6402 can be used in a wide range of applications including modems, printers, peripherals and remote data acquisition systems. Utilizing the Intersil advanced scaled SAJI IV CMOS process permits operation clock frequencies up to 8.0MHz (500K Baud). Power requirements, by comparison, are reduced from 300mW to 10mW. Status logic increases flexibility and simplifies the user interface.

## Ordering Information

| PACKAGE     | TEMPERATURE RANGE | 2MHz = 125K BAUD | 8MHz = 500K BAUD | PKG. NO. |

|-------------|-------------------|------------------|------------------|----------|

| Plastic DIP | -40°C to +85°C    | HD3-6402R-9      | HD3-6402B-9      | E40.6    |

| CERDIP      | -40°C to +85°C    | HD1-6402R-9      | HD1-6402B-9      | F40.6    |

| SMD#        | -55°C to +125°C   | 5962-9052501MQA  | 5962-9052502MQA  | F40.6    |

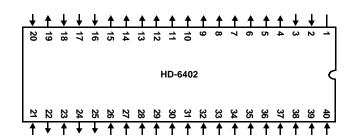

#### **Pinout**

#### HD-6402 (PDIP, CERDIP) **TOP VIEW**

|      |    |   | -  |      |

|------|----|---|----|------|

| Vcc  | 1  | O | 40 | TRC  |

| NC   | 2  |   | 39 | EPE  |

| GND  | 3  |   | 38 | CLS1 |

| RRD  | 4  |   | 37 | CLS2 |

| RBR8 | 5  |   | 36 | SBS  |

| RBR7 | 6  |   | 35 | PI   |

| RBR6 | 7  |   | 34 | CRL  |

| RBR5 | 8  |   | 33 | TBR8 |

| RBR4 | 9  |   | 32 | TBR7 |

| RBR3 | 10 |   | 31 | TBR6 |

| RBR2 | 11 |   | 30 | TBR5 |

| RBR1 | 12 |   | 29 | TBR4 |

| PE   | 13 |   | 28 | TBR3 |

| FE   | 14 |   | 27 | TBR2 |

| OE   | 15 |   | 26 | TBR1 |

| SFD  | 16 |   | 25 | TRO  |

| RRC  | 17 |   | 24 | TRE  |

| DRR  | 18 |   | 23 | TBRL |

| DR   | 19 |   | 22 | TBRE |

| RRI  | 20 |   | 21 | MR   |

## **Control Definition**

| CONTROL WORD |       |    |     |     | CHARACTER FORMAT |           |            |           |  |

|--------------|-------|----|-----|-----|------------------|-----------|------------|-----------|--|

| CLS 2        | CLS 1 | PI | EPE | SBS | START BIT        | DATA BITS | PARITY BIT | STOP BITS |  |

| 0            | 0     | 0  | 0   | 0   | 1                | 5         | ODD        | 1         |  |

| 0            | 0     | 0  | 0   | 1   | 1                | 5         | ODD        | 1.5       |  |

| 0            | 0     | 0  | 1   | 0   | 1                | 5         | EVEN       | 1         |  |

| 0            | 0     | 0  | 1   | 1   | 1                | 5         | EVEN       | 1.5       |  |

| 0            | 0     | 1  | Х   | 0   | 1                | 5         | NONE       | 1         |  |

| 0            | 0     | 1  | Х   | 1   | 1                | 5         | NONE       | 1.5       |  |

| 0            | 1     | 0  | 0   | 0   | 1                | 6         | ODD        | 1         |  |

| 0            | 1     | 0  | 0   | 1   | 1                | 6         | ODD        | 2         |  |

| 0            | 1     | 0  | 1   | 0   | 1                | 6         | EVEN       | 1         |  |

| 0            | 1     | 0  | 1   | 1   | 1                | 6         | EVEN       | 2         |  |

| 0            | 1     | 1  | Х   | 0   | 1                | 6         | NONE       | 1         |  |

| 0            | 1     | 1  | Х   | 1   | 1                | 6         | NONE       | 2         |  |

| 1            | 0     | 0  | 0   | 0   | 1                | 7         | ODD        | 1         |  |

| 1            | 0     | 0  | 0   | 1   | 1                | 7         | ODD        | 2         |  |

| 1            | 0     | 0  | 1   | 0   | 1                | 7         | EVEN       | 1         |  |

| 1            | 0     | 0  | 1   | 1   | 1                | 7         | EVEN       | 2         |  |

| 1            | 0     | 1  | Х   | 0   | 1                | 7         | NONE       | 1         |  |

| 1            | 0     | 1  | Х   | 1   | 1                | 7         | NONE       | 2         |  |

| 1            | 1     | 0  | 0   | 0   | 1                | 8         | ODD        | 1         |  |

| 1            | 1     | 0  | 0   | 1   | 1                | 8         | ODD        | 2         |  |

| 1            | 1     | 0  | 1   | 0   | 1                | 8         | EVEN       | 1         |  |

| 1            | 1     | 0  | 1   | 1   | 1                | 8         | EVEN       | 2         |  |

| 1            | 1     | 1  | Χ   | 0   | 1                | 8         | NONE       | 1         |  |

| 1            | 1     | 1  | Х   | 1   | 1                | 8         | NONE       | 2         |  |

# Pin Description

| PIN | TYPE | SYMBOL            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   |      | V <sub>CC</sub> † | Positive Voltage Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2   |      | NC                | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3   |      | GND               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | I    | RRD               | A high level on RECEIVER REGISTER DISABLE forces the receiver holding out-puts RBR1-RBR8 to high impedance state.                                                                                                                                                                                                                                                                                                                                                               |

| 5   | 0    | RBR8              | The contents of the RECEIVER BUFFER REGIS-<br>TER appear on these three-state outputs. Word for<br>mats less than 8 characters are right justified to<br>RBR1.                                                                                                                                                                                                                                                                                                                  |

| 6   | 0    | RBR7              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7   | 0    | RBR6              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8   | 0    | RBR5              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9   | 0    | RBR4              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10  | 0    | RBR3              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11  | 0    | RBR2              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12  | 0    | RBR1              | See Pin 5-RBR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13  | 0    | PE                | A high level on PARITY ERROR indicates received<br>parity does not match parity programmed by contro<br>bits. When parity is inhibited this output is low.                                                                                                                                                                                                                                                                                                                      |

| 14  | 0    | FE                | A high level on FRAMING ERROR indicates the first stop bit was invalid.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | 0    | OE                | A high level on OVERRUN ERROR indicates the<br>data received flag was not cleared before the las<br>character was transferred to the receiver buffer<br>register.                                                                                                                                                                                                                                                                                                               |

| 16  | I    | SFD               | A high level on STATUS FLAGS DISABLE forces the outputs PE, FE, OE, DR, TBRE to a high impedance state.                                                                                                                                                                                                                                                                                                                                                                         |

| 17  | I    | RRC               | The Receiver register clock is 16X the receiver data rate.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18  | I    | DRR               | A low level on DATA RECEIVED RESET clears the data received output DR to a low level.                                                                                                                                                                                                                                                                                                                                                                                           |

| 19  | 0    | DR                | A high level on DATA RECEIVED indicates a character has been received and transferred to the receiver buffer register.                                                                                                                                                                                                                                                                                                                                                          |

| 20  | I    | RRI               | Serial data on RECEIVER REGISTER INPUT is clocked into the receiver register.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21  | I    | MR                | A high level on MASTER RESET clears PE, FE, OE and DR to a low level and sets the transmitter register empty (TRE) to a high level 18 clock cycles after MR falling edge. MR does not clear the receiver buffer register. This input must be pulsed at leas once after power up. The HD-6402 must be maste reset after power up. The reset pulse should mee V <sub>IH</sub> and t <sub>MR</sub> . Wait 18 clock cycles after the falling edge of MR before beginning operation. |

| 22  | 0    | TBRE              | A high level on TRANSMITTER BUFFER REGIS-<br>TER EMPTY indicates the transmitter buffer registe<br>has transferred its data to the transmitter register<br>and is ready for new data.                                                                                                                                                                                                                                                                                           |

| 23  | I    | TBRL              | A low level on TRANSMITTER BUFFER REGIS TER LOAD transfers data from inputs TBR1-TBR8 into the transmitter buffer register. A low to high transition on TBRL initiates data transfer to the transmitter register. If busy, transfer is automatically delayed so that the two characters are transmitted end to end.                                                                                                                                                             |

| PIN | TYPE | SYMBOL | DESCRIPTION                                                                                                                                                                                                    |

|-----|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | 0    | TRE    | A high level on TRANSMITTER REGISTER EMP-<br>TY indicates completed transmission of a charac-<br>ter including stop bits.                                                                                      |

| 25  | 0    | TRO    | Character data, start data and stop bits appear serially at the TRANSMITTER REGISTER OUTPUT.                                                                                                                   |

| 26  | I    | TRB1   | Character data is loaded into the TRANSMITTER BUFFER REGISTER via inputs TBR1-TBR8. For character formats less than 8 bits the TBR8, 7 and 6 inputs are ignored corresponding to their programmed word length. |

| 27  | ı    | TBR2   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 28  | I    | TBR3   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 29  | ı    | TBR4   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 30  | ı    | TBR5   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 31  | ı    | TBR6   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 32  | ı    | TBR7   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 33  | I    | TBR8   | See Pin 26-TBR1.                                                                                                                                                                                               |

| 34  | I    | CRL    | A high level on CONTROL REGISTER LOAD loads the control register with the control word. The control word is latched on the falling edge of CRL. CRL may be tied high.                                          |

| 35  | I    | PI     | A high level on PARITY INHIBIT inhibits parity generation, parity checking and forces PE output low.                                                                                                           |

| 36  | I    | SBS    | A high level on STOP BIT SELECT selects 1.5 stop bits for 5 character format and 2 stop bits for other lengths.                                                                                                |

| 37  | I    | CLS2   | These inputs program the CHARACTER<br>LENGTH SELECTED (CLS1 low CLS2 low 5 bits)<br>(CLS1 high CLS2 low 6 bits) (CLS1 low CLS2<br>high 7 bits) (CLS1 high CLS2 high 8 bits.)                                   |

| 38  | I    | CLS1   | See Pin 37-CLS2.                                                                                                                                                                                               |

| 39  | I    | EPE    | When PI is low, a high level on EVEN PARITY ENABLE generates and checks even parity. A low level selects odd parity.                                                                                           |

| 40  | I    | TRC    | The TRANSMITTER REGISTER CLOCK is 16X the transmit data rate.                                                                                                                                                  |

$<sup>\</sup>dagger~A~0.1\mu\text{F}$  decoupling capacitor from the  $V_{CC}$  pin to the GND is recommended.

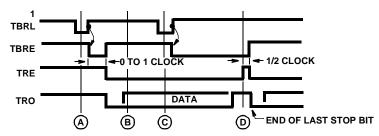

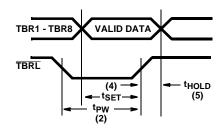

## **Transmitter Operation**

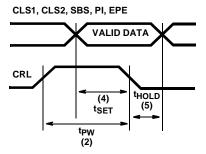

The transmitter section accepts parallel data, formats the data and transmits the data in serial form on the Transmitter Register Output (TRO) terminal (See serial data format). Data is loaded from the inputs TBR1-TBR8 into the Transmitter Buffer Register by applying a logic low on the Transmitter Buffer Register Load ( $\overline{\text{TBRL}}$ ) input (A). Valid data must be present at least  $t_{\text{Set}}$  prior to and  $t_{\text{hold}}$  following the rising edge of  $\overline{\text{TBRL}}$ . If words less than 8 bits are used, only the least significant bits are transmitted. The character is right justified, so the least significant bit corresponds to TBR1 (B).

The rising edge of TBRL clears Transmitter Buffer Register Empty (TBRE). 0 to 1 Clock cycles later, data is transferred to the transmitter register, the Transmitter Register Empty (TRE) pin goes to a low state, TBRE is set high and serial data information is transmitted. The output data is clocked by Transmitter Register Clock (TRC) at a clock rate 16 times the data rate. A second low level pulse on TBRL loads data into the Transmitter Buffer Register (C). Data transfer to the transmitter register is delayed until transmission of the current data is complete (D). Data is automatically transferred to the transmitter register and transmission of that character begins one clock cycle later.

FIGURE 1. TRANSMITTER TIMING (NOT TO SCALE)

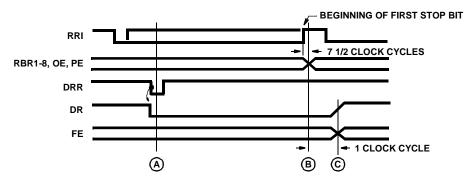

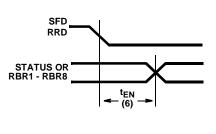

## **Receiver Operation**

Data is received in serial form at the Receiver Register Input (RRI). When no data is being received, RRI must remain high. The data is clocked through the Receiver Register Clock (RRC). The clock rate is 16 times the data rate. A low level on Data Received Reset ( $\overline{DRR}$ ) clears the Data Receiver (DR) line (A). During the first stop bit data is transferred from the Receiver Register to the Receiver Buffer Register (RBR) (B). If the word is less than 8 bits, the unused most significant bits will be a logic low. The output

character is right justified to the least significant bit RBR1. A logic high on Overrun Error (OE) indicates overruns. An overrun occurs when DR has not been cleared before the present character was transferred to the RBR. One clock cycle later DR is reset to a logic high, and Framing Error (FE) is evaluated (C). A logic high on FE indicates an invalid stop bit was received, a framing error. A logic high on Parity Error (PE) indicates a parity error.

FIGURE 2. RECEIVER TIMING (NOT TO SCALE)

FIGURE 3. SERIAL DATA FORMAT

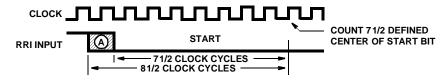

#### Start Bit Detection

The receiver uses a 16X clock timing. The start bit could have occurred as much as one clock cycle before it was detected, as indicated by the shaded portion (A). The center of the start bit is defined as clock count 7 1/2. If the receiver clock is a

symmetrical square wave, the center of the start bit will be located within  $\pm 1/2$  clock cycle,  $\pm 1/32$  bit or 3.125% giving a receiver margin of 46.875%. The receiver begins searching for the next start bit at the center of the first stop bit.

FIGURE 4.

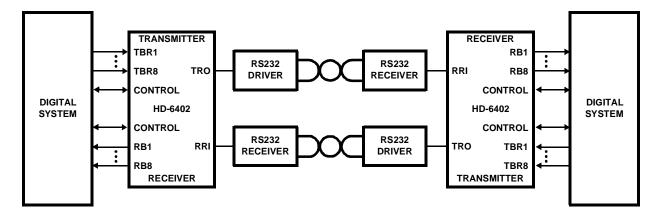

## Interfacing with the HD-6402

FIGURE 5. TYPICAL SERIAL DATA LINK

#### HD-6402

### **Absolute Maximum Ratings**

# Thermal Information

| Supply Voltage                                                          |

|-------------------------------------------------------------------------|

| Input, Output or I/O Voltage Applied GND -0.5V to V <sub>CC</sub> +0.5V |

| Storage Temperature Range65°C to +150°C                                 |

| Junction Temperature+175°C                                              |

| Lead Temperature (Soldering 10s)+300°C                                  |

| ESD Classification Class 1                                              |

| Thermal Resistance (Typical) | $\theta_{\sf JA}$ |                     |

|------------------------------|-------------------|---------------------|

| CERDIP Package               | 50°C/W            | 12 <sup>0</sup> C/W |

| PDIP Package                 | 50°C/W            | N/A                 |

| Gate Count                   |                   | 1643 Gates          |

#### **Operating Conditions**

## **DC Electrical Specifications** $V_{CC}$ = 5.0V $\pm$ 10%, $T_{A}$ = -40°C to +85°C (HD-6402R-9, HD-6402B-9)

|                 |                                     | LIM                         | LIMITS |       |                                                                                                       |

|-----------------|-------------------------------------|-----------------------------|--------|-------|-------------------------------------------------------------------------------------------------------|

| SYMBOL          | PARAMETER                           | MIN                         | MAX    | UNITS | CONDITIONS                                                                                            |

| V <sub>IH</sub> | Logical "1" Input Voltage           | 2.0                         | -      | V     | V <sub>CC</sub> = 5.5V                                                                                |

| V <sub>IL</sub> | Logical "0" Input Voltage           | -                           | 0.8    | V     | V <sub>CC</sub> = 4.5V                                                                                |

| II              | Input Leakage Current               | -1.0                        | 1.0    | μΑ    | $V_{IN}$ = GND or $V_{CC}$ , $V_{CC}$ = 5.5 $V$                                                       |

| V <sub>OH</sub> | Logical "1" Output Voltage          | 3.0<br>V <sub>CC</sub> -0.4 | -      | V     | $I_{OH}$ = -2.5mA, $V_{CC}$ = 4.5V $I_{OH}$ = -100 $\mu$ A                                            |

| V <sub>OL</sub> | Logical "0" Output Voltage          | -                           | 0.4    | V     | $I_{OL} = +2.5$ mA, $V_{CC} = 4.5$ V                                                                  |

| I <sub>O</sub>  | Output Leakage Current              | -1.0                        | 1.0    | μΑ    | $V_O = GND \text{ or } V_{CC}, V_{CC} = 5.5V$                                                         |

| ICCSB           | Standby Supply Current              | -                           | 100    | μΑ    | V <sub>IN</sub> = GND or V <sub>CC</sub> ; V <sub>CC</sub> = 5.5V,<br>Output Open                     |

| ICCOP           | Operating Supply Current (See Note) | -                           | 2.0    | mA    | V <sub>CC</sub> = 5.5V, Clock Freq. = 2MHz,<br>V <sub>IN</sub> = V <sub>CC</sub> or GND, Outputs Open |

NOTE: Guaranteed, but not 100% tested

### **Capacitance** $T_A = +25^{\circ}C$

|                    |        |                                                             | LIMIT   |       |

|--------------------|--------|-------------------------------------------------------------|---------|-------|

| PARAMETER          | SYMBOL | CONDITIONS                                                  | TYPICAL | UNITS |

| Input Capacitance  | CIN    | Freq. = 1MHz, all measurements are referenced to device GND | 25      | pF    |

| Output Capacitance | COUT   | VICE GND                                                    | 25      | pF    |

### AC Electrical Specifications $V_{CC}$ = 5.0V $\pm$ 10%, $T_A$ = -40°C to +85°C (HD-6402R-9, HD6402B-9)

|                       |                              | LIMITS H | TS HD-6402R LIMITS HD-6402B |      |     |       |                        |

|-----------------------|------------------------------|----------|-----------------------------|------|-----|-------|------------------------|

| SYMBOL                | PARAMETER                    | MIN      | MAX                         | MIN  | MAX | UNITS | CONDITIONS             |

| (1) fCLOCK            | Clock Frequency              | D.C.     | 2.0                         | D.C. | 8.0 | MHz   | $C_L = 50pF$           |

| (2) t <sub>PW</sub>   | Pulse Widths, CRL, DRR, TBRL | 150      | -                           | 75   | -   | ns    | See Switching Waveform |

| (3) t <sub>MR</sub>   | Pulse Width MR               | 150      | -                           | 150  | -   | ns    |                        |

| (4) t <sub>SET</sub>  | Input Data Setup Time        | 50       | -                           | 20   | -   | ns    |                        |

| (5) t <sub>HOLD</sub> | Input Data Hold Time         | 60       | -                           | 20   | -   | ns    |                        |

| (6) t <sub>EN</sub>   | Output Enable Time           | -        | 160                         | -    | 35  | ns    |                        |

# Switching Waveforms

FIGURE 6. DATA INPUT CYCLE

FIGURE 7. CONTROL REGISTER LOAD CYCLE

FIGURE 8. STATUS FLAG OUTPUT ENABLE TIME OR DATA OUT-PUT ENABLE TIME

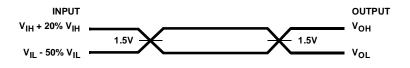

## A.C. Testing Input, Output Waveform

#### FIGURE 9.

NOTE: A.C. Testing: All input signals must switch between V<sub>IL</sub> - 50% V<sub>IL</sub> and V<sub>IH</sub> + 20% V<sub>IH</sub>. Input rise and fall times are driven at 1ns/V.

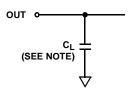

#### **Test Circuit**

FIGURE 10.

NOTE: Includes stray and jig capacitance,  $C_L = 50pF$ .

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withous notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com