intersil

#### July 29, 2005

#### Datasheet

### **CMOS Manchester Encoder-Decoder**

The HD-6409 Manchester Encoder-Decoder (MED) is a high speed, low power device manufactured using self-aligned silicon gate technology. The device is intended for use in serial data communication, and can be operated in either of two modes. In the converter mode, the MED converts Non return-to-Zero code (NRZ) into Manchester code and decodes Manchester code into Nonreturn-to-Zero code. For serial data communication, Manchester code does not have some of the deficiencies inherent in Nonreturn-to-Zero code. For instance, use of the MED on a serial line eliminates DC components, provides clock recovery, and gives a relatively high degree of noise immunity. Because the MED converts the most commonly used code (NRZ) to Manchester code, the advantages of using Manchester code are easily realized in a serial data link.

In the Repeater mode, the MED accepts Manchester code input and reconstructs it with a recovered clock. This minimizes the effects of noise on a serial data link. A digital phase lock loop generates the recovered clock. A maximum data rate of 1MHz requires only 50mW of power.

Manchester code is used in magnetic tape recording and in fiber optic communication, and generally is used where data accuracy is imperative. Because it frames blocks of data, the HD-6409 easily interfaces to protocol controllers.

### **Ordering Information**

| PACKAGE                          | TEMPERATURE<br>RANGE | 1 MEGABIT/SEC           | PKG.<br>DWG. # |

|----------------------------------|----------------------|-------------------------|----------------|

| PDIP                             | -40°C to +85°C       | HD3-6409-9              | E20.3          |

| SOIC                             | -40°C to +85°C       | HD9P6409-9              | M20.3          |

| SOIC<br>(Pb-free)                | -40°C to +85°C       | HD9P6409-9Z<br>(Note)   | M20.3          |

| SOIC Tape &<br>Reel<br>(Pb-free) | -40°C to +85°C       | HD9P6409-9Z96<br>(Note) | M20.3          |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- · Converter or Repeater Mode

- Independent Manchester Encoder and Decoder Operation

- Static to One Megabit/sec Data Rate Guaranteed

- Low Bit Error Rate

- Digital PLL Clock Recovery

- On Chip Oscillator

- Low Operating Power: 50mW Typical at +5V

- · Pb-Free Plus Anneal Available (RoHS Compliant)

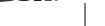

### **Pinouts**

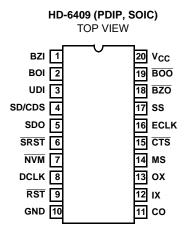

## Block Diagram

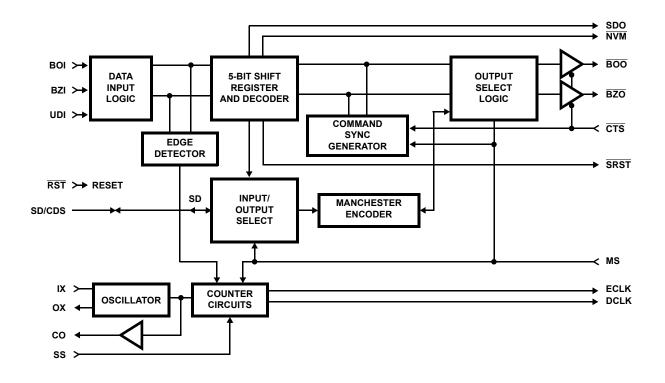

## Logic Symbol

# **Pin Description**

| PIN<br>NUMBER | ТҮРЕ | SYMBOL          | NAME                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------------|------|-----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1             | I    | BZI             | Bipolar Zero Input              | Used in conjunction with pin 2, Bipolar One Input (BOI), to input Manchester II encoded data to the decoder, BZI and BOI are logical complements. When using pin 3, Unipolar Data Input (UDI) for data input, BZI must be held high.                                                                                                                                                                                                                                                                                                                    |  |

| 2             | I    | BOI             | Bipolar One Input               | Used in conjunction with pin 1, Bipolar Zero Input (BZI), to input Manchester II encoded data to the decoder, BOI and BZI are logical complements. When using pin 3, Unipolar Data Input (UDI) for data input, BOI must be held low.                                                                                                                                                                                                                                                                                                                    |  |

| 3             | I    | UDI             | Unipolar Data Input             | An alternate to bipolar input (BZI, BOI), Unipolar Data Input (UDI) is used to input Manchester II encoded data to the decoder. When using pin 1 (BZI) and pin 2 (BOI) for data input, UDI must be held low.                                                                                                                                                                                                                                                                                                                                            |  |

| 4             | I/O  | SD/CDS          | SerialData/Command<br>Data Sync | In the converter mode, SD/CDS is an input used to receive serial NRZ data. NRZ data accepted synchronously on the falling edge of encoder clock output (ECLK). In the repeater mode, SD/CDS is an output indicating the status of last valid sync pattern received. A high indicates a command sync and a low indicates a data sync pattern                                                                                                                                                                                                             |  |

| 5             | 0    | SDO             | Serial Data Out                 | The decoded serial NRZ data is transmitted out synchronously with the decoder clock (DCLK). SDO is forced low when $\overrightarrow{\text{RST}}$ is low.                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 6             | 0    | SRST            | Serial Reset                    | In the converter mode, $\overline{\text{SRST}}$ follows $\overline{\text{RST}}$ . In the repeater mode, when $\overline{\text{RST}}$ goes low $\overline{\text{SRST}}$ goes low and remains low after $\overline{\text{RST}}$ goes high. $\overline{\text{SRST}}$ goes high only when $\overline{\text{RST}}$ is high, the reset bit is zero, and a valid synchronization sequence is received.                                                                                                                                                         |  |

| 7             | 0    | NVM             | Nonvalid Manchester             | A low on $\overline{\text{NVM}}$ indicates that the decoder has received invalid Manchester data and present data on Serial Data Out (SDO) is invalid. A high indicates that the sync pulse and data were valid and SDO is valid. $\overline{\text{NVM}}$ is set low by a low on $\overline{\text{RST}}$ , and remains low after $\overline{\text{RST}}$ goes high until valid sync pulse followed by two valid Manchester bits is received.                                                                                                            |  |

| 8             | 0    | DCLK            | Decoder Clock                   | The decoder clock is a 1X clock recovered from BZI and BOI, or UDI to synchronously output received NRZ data (SDO).                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 9             | I    | RST             | Reset                           | In the converter mode, a low on RST forces SDO, DCLK, NVM, and SRST low. A high on RST enables SDO and DCLK, and forces SRST high. NVM remains low after RST goes high until a valid sync pulse followed by two Manchester bits is received, after which it goes high. In the repeater mode, RST has the same effect on SDO, DCLK and NVM as in the converter mode. When RST goes low, SRST goes low and remains low after RST goes high. SRST goes high only when RST is high, the reset bit is zero and a valid synchronization sequence is received. |  |

| 10            | I    | GND             | Ground                          | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 11            | 0    | CO              | Clock Output                    | Buffered output of clock input $I_X$ . May be used as clock signal for other peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 12            | I    | ١ <sub>X</sub>  | Clock Input                     | $I_X$ is the input for an external clock or, if the internal oscillator is used, $I_X$ and $O_X$ are used for the connection of the crystal.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 13            | 0    | OX              | Clock Drive                     | If the internal oscillator is used, $O_X$ and $I_X$ are used for the connection of the crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 14            | I    | MS              | Mode Select                     | MS must be held low for operation in the converter mode, and high for operation in the repeater mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 15            | I    | CTS             | Clear to Send                   | In the converter mode, a high disables the encoder, forcing outputs $\overline{BOO}$ , $\overline{BZO}$ high and $\overline{ECLK}$ low. A high to low transition of $\overline{CTS}$ initiates transmission of a Command sync pulse. A low on $\overline{CTS}$ enables $\overline{BOO}$ , $\overline{BZO}$ , and $\overline{ECLK}$ . In the repeater mode, the function of $\overline{CTS}$ is identical to that of the converter mode with the exception that a transition of $\overline{CTS}$ does not initiate a synchronization sequence.           |  |

| 16            | 0    | ECLK            | Encoder Clock                   | In the converter mode, ECLK is a 1X clock output used to receive serial NRZ data to SD/CDS. In the repeater mode, ECLK is a 2X clock which is recovered from BZI and BOI data by the digital phase locked loop.                                                                                                                                                                                                                                                                                                                                         |  |

| 17            | I    | SS              | Speed Select                    | A logic high on SS sets the data rate at 1/32 times the clock frequency while a low sets the data rate at 1/16 times the clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 18            | 0    | BZO             | Bipolar Zero Output             | $\overline{\text{BZO}}$ and its logical complement $\overline{\text{BOO}}$ are the Manchester data outputs of the encoder.<br>The inactive state for these outputs is in the high state.                                                                                                                                                                                                                                                                                                                                                                |  |

| 19            | 0    | BOO             | Bipolar One Out                 | See pin 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 20            | I    | V <sub>CC</sub> | V <sub>CC</sub>                 | $V_{CC}$ is the +5V power supply pin. A $0.1\mu F$ decoupling capacitor from $V_{CC}$ (pin-20) to GND (pin-10) is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

NOTE: (I) Input (O) Output

intersil

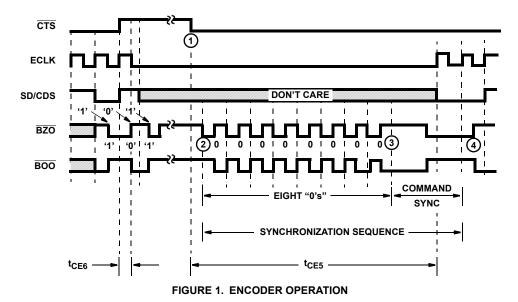

# **Encoder Operation**

The encoder uses free running clocks at 1X and 2X the data rate derived from the system clock I<sub>X</sub> for internal timing.  $\overline{\text{CTS}}$  is used to control the encoder outputs, ECLK,  $\overline{\text{BOO}}$  and  $\overline{\text{BZO}}$ . A free running 1X ECLK is transmitted out of the encoder to drive the external circuits which supply the NRZ data to the MED at pin SD/CDS.

A low on  $\overline{\text{CTS}}$  enables encoder outputs ECLK,  $\overline{\text{BOO}}$  and  $\overline{\text{BZO}}$ , while a high on  $\overline{\text{CTS}}$  forces  $\overline{\text{BZO}}$ ,  $\overline{\text{BOO}}$  high and holds ECLK low. When  $\overline{\text{CTS}}$  goes from high to low (1), a synchronization sequence is transmitted out on  $\overline{\text{BOO}}$  and  $\overline{\text{BZO}}$ . A synchronization sequence consists of eight Manchester "0" bits followed by a command sync pulse. (2)

A command sync pulse is a 3-bit wide pulse with the first 1 1/2 bits high followed by 1 1/2 bits low. ③ Serial NRZ data is clocked into the encoder at SD/CDS on the high to low transition of ECLK during the command sync pulse. The NRZ data received is encoded into Manchester II data and transmitted out on BOO and BZO following the command sync pulse. ④ Following the synchronization sequence, input data is encoded and transmitted out continuously without parity check or word framing. The length of the data block encoded is defined by CTS. Manchester data out is inverted.

# Decoder Operation

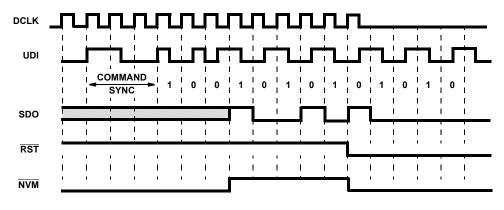

The decoder requires a single clock with a frequency 16X or 32X the desired data rate. The rate is selected on the speed select with SS low producing a 16X clock and high a 32X clock. For long data links the 32X mode should be used as this permits a wider timing jitter margin. The internal operation of the decoder utilizes a free running clock synchronized with incoming data for its clocking.

The Manchester II encoded data can be presented to the decoder in either of two ways. The Bipolar One and Bipolar Zero inputs will accept data from differential inputs such as a comparator sensed transformer coupled bus. The Unipolar Data input can only accept noninverted Manchester II encoded data i.e. Bipolar One Out through an inverter to Unipolar Data Input. The decoder continuously monitors this data input for valid sync pattern. Note that while the MED encoder section can generate only a command sync pattern, the decoder can recognize either a command or data sync pattern. A data sync is a logically inverted command sync.

4

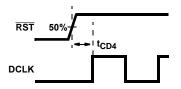

There is a three bit delay between UDI, BOI, or BZI input and the decoded NRZ data transmitted out of SDO.

Control of the decoder outputs is provided by the  $\overline{\text{RST}}$  pin. When  $\overline{\text{RST}}$  is low, SDO, DCLK and  $\overline{\text{NVM}}$  are forced low. When  $\overline{\text{RST}}$  is high, SDO is transmitted out synchronously with the recovered clock DCLK. The  $\overline{\text{NVM}}$  output remains low after a low to high transition on  $\overline{\text{RST}}$  until a valid sync pattern is received.

The decoded data at SDO is in NRZ format. DCLK is provided so that the decoded bits can be shifted into an external register on every high to low transition of this clock. Three bit periods after an invalid Manchester bit is received on UDI, or BOI, NVM goes low synchronously with the questionable data output on SDO. FURTHER, THE DECODER DOES NOT REESTABLISH PROPER DATA DECODING UNTIL ANOTHER SYNC PATTERN IS RECOGNIZED.

FIGURE 2. DECODER OPERATION

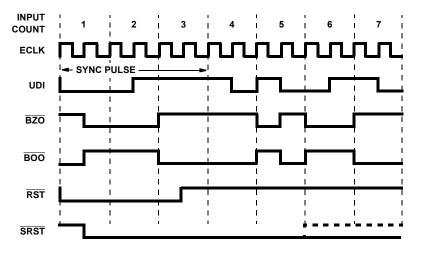

## **Repeater Operation**

Manchester II data can be presented to the repeater in either of two ways. The inputs Bipolar One In and Bipolar Zero In will accept data from differential inputs such as a comparator or sensed transformer coupled bus. The input Unipolar Data In accepts only noninverted Manchester II coded data. The decoder requires a single clock with a frequency 16X or 32X the desired data rate. This clock is selected to 16X with Speed Select low and 32X with Speed Select high. For long data links the 32X mode should be used as this permits a wider timing jitter margin.

The inputs UDI, or BOI, BZI are delayed approximately 1/2 bit period and repeated as outputs BOO and BZO. The 2X ECLK is transmitted out of the repeater synchronously with BOO and BZO.

A low on  $\overline{\text{CTS}}$  enables ECLK,  $\overline{\text{BOO}}$ , and  $\overline{\text{BZO}}$ . In contrast to the converter mode, a transition on CTS does not initiate a synchronization sequence of eight 0's and a command sync. The repeater mode does recognize a command or data sync pulse. SD/CDS is an output which reflects the state of the most recent sync pulse received, with high indicating a command sync and low indicating a data sync.

When RST is low, the outputs SDO, DCLK, and NVM are low, and SRST is set low. SRST remains low after RST goes high and is not reset until a sync pulse and two valid manchester bits are received with the reset bit low. The reset bit is the first data bit after the sync pulse. With RST high, NRZ Data is transmitted out of Serial Data Out synchronously with the 1X DCLK.

FIGURE 3. REPEATER OPERATION

## Manchester Code

Nonreturn-to-Zero (NRZ) code represents the binary values logic-O and logic-1 with a static level maintained throughout the data cell. In contrast, Manchester code represents data with a level transition in the middle of the data cell. Manchester has bandwidth, error detection, and synchronization advantages over NRZ code.

The Manchester II code Bipolar One and Bipolar Zero shown below are logical complements. The direction of the transition indicates the binary value of data. A logic-0 in Bipolar One is defined as a Low to high transition in the middle of the data cell, and a logic-1 as a high to low mid bit transition, Manchester II is also known as Biphase-L code.

The bandwidth of NRZ is from DC to the clock frequency fc/2, while that of Manchester is from fc/2 to fc. Thus, Manchester can be AC or transformer coupled, which has considerable advantages over DC coupling. Also, the ratio of maximum to minimum frequency of Manchester extends one octave, while the ratio for NRZ is the range of 5-10 octaves. It is much easier to design a narrow band than a wideband amp.

Secondly, the mid bit transition in each data cell provides the code with an effective error detection scheme. If noise produces a logic inversion in the data cell such that there is no transition, an error indiction is given, and synchronization must be re-established. This places relatively stringent requirements on the incoming data.

The synchronization advantages of using the HD-6409 and Manchester code are several fold. One is that Manchester is a self clocking code. The clock in serial data communication defines the position of each data cell. Non self clocking codes, as NRZ, often require an extra clock wire or clock track (in magnetic recording). Further, there can be a phase variation between the clock and data track. Crosstalk between the two may be a problem. In Manchester, the serial data stream contains both the clock and the data, with the position of the mid bit transition representing the clock, and the direction of the transition representing data. There is no phase variation between the clock and the data.

A second synchronization advantage is a result of the number of transitions in the data. The decoder resynchronizes on each transition, or at least once every data cell. In contrast, receivers using NRZ, which does not necessarily have transitions, must resynchronize on frame bit transitions, which occur far less often, usually on a character basis. This more frequent resynchronization eliminates the cumulative effect of errors over successive data cells. A final synchronization advantage concerns the HD-6409's sync pulse used to initiate synchronization. This three bit wide pattern is sufficiently distinct from Manchester data that a false start by the receiver is unlikely.

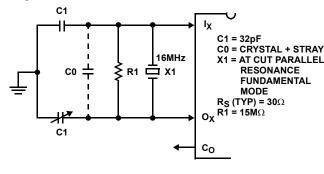

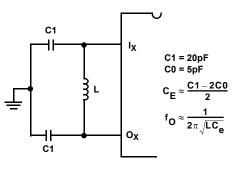

FIGURE 5. CRYSTAL OSCILLATOR MODE

6

LC Oscillator Mode

FIGURE 6. LC OSCILLATOR MODE

intersil

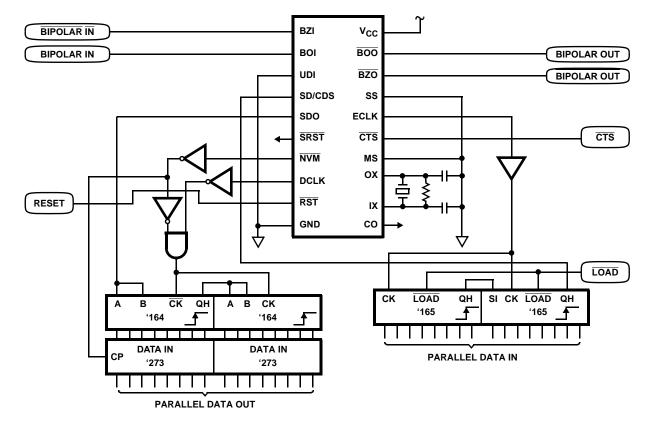

Using the 6409 as a Manchester Encoded UART

FIGURE 7. MANCHESTER ENCODER UART

#### **Absolute Maximum Ratings**

| Supply Voltage               | +7.0V                               |

|------------------------------|-------------------------------------|

| Input, Output or I/O Voltage | .GND -0.5V to V <sub>CC</sub> +0.5V |

| ESD Classification           | Class 1                             |

#### **Thermal Information**

| Thermal Resistance (Typical)                              | $\theta_{JA}$ | $\theta$ JC |

|-----------------------------------------------------------|---------------|-------------|

| PDIP Package                                              | 75°C/W        | N/A         |

| SOIC Package                                              | 100°C/W       | N/A         |

| Storage Temperature Range<br>Maximum Junction Temperature | 65°C to       | ) +150°C    |

| Ceramic Package                                           |               | +175°C      |

| Plastic Package                                           |               | +150°C      |

| Maximum Lead Temperature (Soldering 10s)                  |               | +300°C      |

| ( Lead Tips Only for Surface Mount Packag                 | es)           |             |

### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Operating Conditions**

| Operating Temperature Range40°C to +85°C |  |

|------------------------------------------|--|

| Operating Voltage Range+4.5V to +5.5V    |  |

| Input Rise and Fall Times                |  |

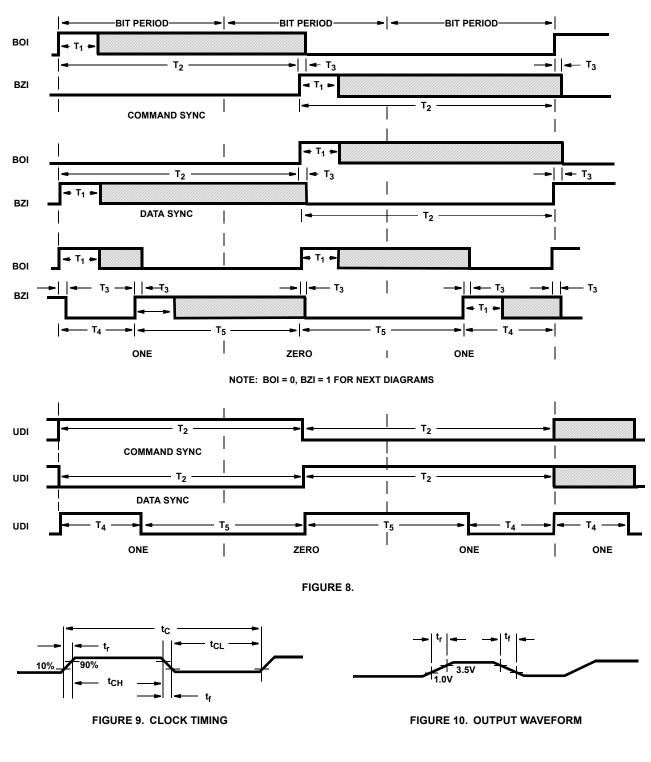

| Sync. Transition Span (t2) 1.5 DBP Typical, (Notes 1, 2)     |

|--------------------------------------------------------------|

| Short Data Transition Span (t4) 0.5DBP Typical, (Notes 1, 2) |

| Long Data Transition Span (t5) 1.0DBP Typical, (Notes 1, 2)  |

| Zero Crossing Tolerance (tCD5)(Note 3)                       |

NOTES:

- 1. DBP-Data Bit Period, Clock Rate = 16X, one DBP = 16 Clock Cycles; Clock Rate = 32X, one DBP = 32 Clock Cycles.

- 2. The input conditions specified are nominal values, the actual input waveforms transition spans may vary by  $\pm 2 I_X$  clock cycles (16X mode) or  $\pm 6 I_X$  clock cycles (32X mode).

- 3. The maximum zero crossing tolerance is ±2 I<sub>X</sub> clock cycles (16X mode) or ±6 I<sub>X</sub> clock cycles (32 mode) from the nominal.

| SYMBOL           | PARAMETER                                        | MIN                  | MAX                 | UNITS | (NOTE 1) TEST CONDITIONS                                                 |

|------------------|--------------------------------------------------|----------------------|---------------------|-------|--------------------------------------------------------------------------|

| VIH              | Logical "1" Input Voltage                        | 70% V <sub>CC</sub>  | -                   | V     | V <sub>CC</sub> = 4.5V                                                   |

| VIL              | Logical "0" Input Voltage                        | -                    | 20% V <sub>CC</sub> | V     | V <sub>CC</sub> = 4.5V                                                   |

| VIHR             | Logic "1" Input Voltage (Reset)                  | V <sub>CC</sub> -0.5 | -                   | V     | V <sub>CC</sub> = 5.5V                                                   |

| V <sub>ILR</sub> | Logic "0" Input Voltage (Reset)                  | -                    | GND +0.5            | V     | V <sub>CC</sub> = 4.5V                                                   |

| VIHC             | Logical "1" Input Voltage (Clock)                | V <sub>CC</sub> -0.5 | -                   | V     | V <sub>CC</sub> = 5.5V                                                   |

| V <sub>ILC</sub> | Logical "0" Input Voltage (Clock)                | -                    | GND +0.5            | V     | V <sub>CC</sub> = 4.5V                                                   |

| Ц                | Input Leakage Current (Except I <sub>X</sub> )   | -1.0                 | +1.0                | μA    | $V_{IN}$ = $V_{CC}$ or GND, $V_{CC}$ = 5.5V                              |

| I                | Input Leakage Current (I <sub>X</sub> )          | -20                  | +20                 | μA    | $V_{IN}$ = $V_{CC}$ or GND, $V_{CC}$ = 5.5V                              |

| Ι <sub>Ο</sub>   | I/O Leakage Current                              | -10                  | +10                 | μA    | $V_{OUT}$ = $V_{CC}$ or GND, $V_{CC}$ = 5.5V                             |

| V <sub>OH</sub>  | Output HIGH Voltage (All Except O <sub>X</sub> ) | V <sub>CC</sub> -0.4 | -                   | V     | I <sub>OH</sub> = -2.0mA, V <sub>CC</sub> = 4.5V (Note 2)                |

| V <sub>OL</sub>  | Output LOW Voltage (All Except O <sub>X</sub> )  | -                    | 0.4                 | V     | I <sub>OL</sub> = +2.0mA, V <sub>CC</sub> = 4.5V (Note 2)                |

| ICCSB            | Standby Power Supply Current                     | -                    | 100                 | μA    | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.5V$ ,<br>Outputs Open              |

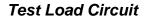

| ICCOP            | Operating Power Supply Current                   | -                    | 18.0                | mA    | f = 16.0MHz, $V_{IN}$ = $V_{CC}$ or GND<br>$V_{CC}$ = 5.5V, $C_L$ = 50pF |

| F <sub>T</sub>   | Functional Test                                  | -                    | -                   | -     | (Note 1)                                                                 |

### **DC Electrical Specifications** V<sub>CC</sub> = $5.0V \pm 10\%$ , T<sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C (HD-6409-9)

NOTES:

1. Tested as follows: f = 16MHz, V<sub>IH</sub> = 70% V<sub>CC</sub>, V<sub>IL</sub> = 20% V<sub>CC</sub>, V<sub>OH</sub>  $\ge$  V<sub>CC</sub>/2, and V<sub>OL</sub>  $\le$  V<sub>CC</sub>/2, V<sub>CC</sub> = 4.5V and 5.5V.

2. Interchanging of force and sense conditions is permitted

| •                |                    |     |       |                                               |

|------------------|--------------------|-----|-------|-----------------------------------------------|

| SYMBOL           | PARAMETER          | ТҮР | UNITS | TEST CONDITIONS                               |

| C <sub>IN</sub>  | Input Capacitance  | 10  | pF    | All measurements are referenced to device GND |

| C <sub>OUT</sub> | Output Capacitance | 12  | pF    |                                               |

#### Capacitance T<sub>A</sub> = +25°C, Frequency = 1MHz

#### AC Electrical Specifications $V_{CC} = 5.0V \pm 10\%$ , $T_A = -40^{\circ}C$ to +85°C (HD-6409-9)

| SYMBOL           | PARAMETER                                                                                  | MIN                | MAX                | UNITS | (NOTE 1) TEST CONDITIONS                |

|------------------|--------------------------------------------------------------------------------------------|--------------------|--------------------|-------|-----------------------------------------|

| f <sub>C</sub>   | Clock Frequency                                                                            | -                  | 16                 | MHz   | -                                       |

| t <sub>C</sub>   | Clock Period                                                                               | 1/f <sub>C</sub>   | -                  | sec   | -                                       |

| t <sub>1</sub>   | Bipolar Pulse Width                                                                        | t <sub>C</sub> +10 | -                  | ns    | -                                       |

| t <sub>3</sub>   | One-Zero Overlap                                                                           | -                  | t <sub>C</sub> -10 | ns    | -                                       |

| t <sub>CH</sub>  | Clock High Time                                                                            | 20                 | -                  | ns    | f = 16.0MHz                             |

| t <sub>CL</sub>  | Clock Low Time                                                                             | 20                 | -                  | ns    | f = 16.0MHz                             |

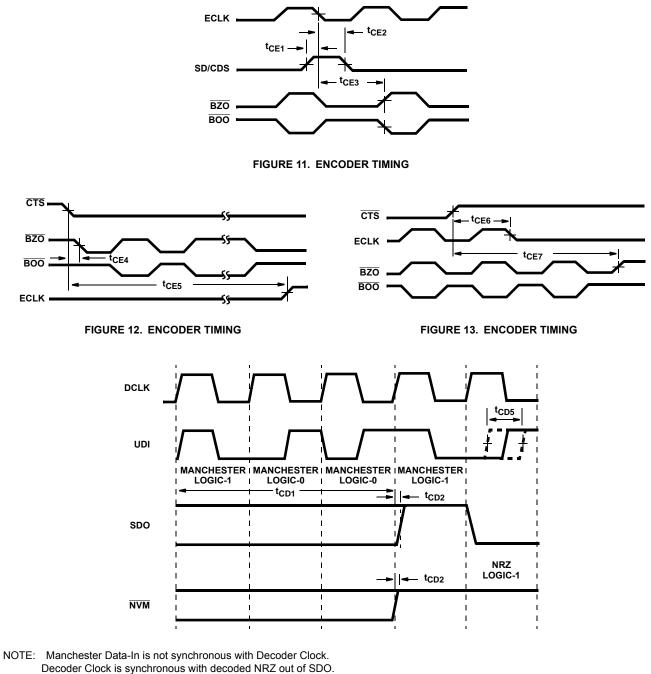

| t <sub>CE1</sub> | Serial Data Setup Time                                                                     | 120                | -                  | ns    | -                                       |

| t <sub>CE2</sub> | Serial Data Hold Time                                                                      | 0                  | -                  | ns    | -                                       |

| t <sub>CD2</sub> | DCLK to SDO, NVM                                                                           | -                  | 40                 | ns    | -                                       |

| t <sub>R2</sub>  | ECLK to BZO                                                                                | -                  | 40                 | ns    | -                                       |

| t <sub>r</sub>   | Output Rise Time (All except Clock)                                                        | -                  | 50                 | ns    | From 1.0V to 3.5V, $C_L$ = 50pF, Note 2 |

| t <sub>f</sub>   | Output Fall Time (All except Clock)                                                        | -                  | 50                 | ns    | From 3.5V to 1.0V, $C_L$ = 50pF, Note 2 |

| t <sub>r</sub>   | Clock Output Rise Time                                                                     | -                  | 11                 | ns    | From 1.0V to 3.5V, $C_L$ = 20pF, Note 2 |

| t <sub>f</sub>   | Clock Output Fall Time                                                                     | -                  | 11                 | ns    | From 3.5V to 1.0V, $C_L$ = 20pF, Note 2 |

| t <sub>CE3</sub> | ECLK to BZO, BOO                                                                           | 0.5                | 1.0                | DBP   | Notes 2, 3                              |

| t <sub>CE4</sub> | CTS Low to BZO, BOO Enabled                                                                | 0.5                | 1.5                | DBP   | Notes 2, 3                              |

| t <sub>CE5</sub> | CTS Low to ECLK Enabled                                                                    | 10.5               | 11.5               | DBP   | Notes 2, 3                              |

| t <sub>CE6</sub> | CTS High to ECLK Disabled                                                                  | -                  | 1.0                | DBP   | Notes 2, 3                              |

| t <sub>CE7</sub> | $\overline{\text{CTS}}$ High to $\overline{\text{BZO}}$ , $\overline{\text{BOO}}$ Disabled | 1.5                | 2.5                | DBP   | Notes 2, 3                              |

| t <sub>CD1</sub> | UDI to SDO, NVM                                                                            | 2.5                | 3.0                | DBP   | Notes 2, 3                              |

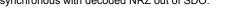

| t <sub>CD3</sub> | RST Low to CDLK, SDO, NVM Low                                                              | 0.5                | 1.5                | DBP   | Notes 2, 3                              |

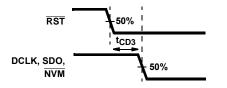

| t <sub>CD4</sub> | RST High to DCLK, Enabled                                                                  | 0.5                | 1.5                | DBP   | Notes 2, 3                              |

| t <sub>R1</sub>  | UDI to BZO, BOO                                                                            | 0.5                | 1.0                | DBP   | Notes 2, 3                              |

| t <sub>R3</sub>  | UDI to SDO, NVM                                                                            | 2.5                | 3.0                | DBP   | Notes 2, 3                              |

NOTES:

1. AC testing as follows: f = 4.0MHz,  $V_{IH}$  = 70%  $V_{CC}$ ,  $V_{IL}$  = 20%  $V_{CC}$ , Speed Select = 16X,  $V_{OH} \ge V_{CC}/2$ ,  $V_{OL} \le V_{CC}/2$ ,  $V_{CC}$  = 4.5V and 5.5V. Input rise and fall times driven at 1ns/V, Output load = 50pF.

2. Guaranteed via characteristics at initial device design and after major process and/or design changes, not tested.

3. DBP-Data Bit Period, Clock Rate = 16X, one DBP = 16 Clock Cycles; Clock Rate = 32X, one DBP = 32 Clock Cycles.

## **Timing Waveforms**

Timing Waveforms (Continued)

FIGURE 15. DECODER TIMING

FIGURE 16. DECODER TIMING

11 intersil

FIGURE 18. TEST LOAD CIRCUIT

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com