Data Sheet

August 2005

**Features**

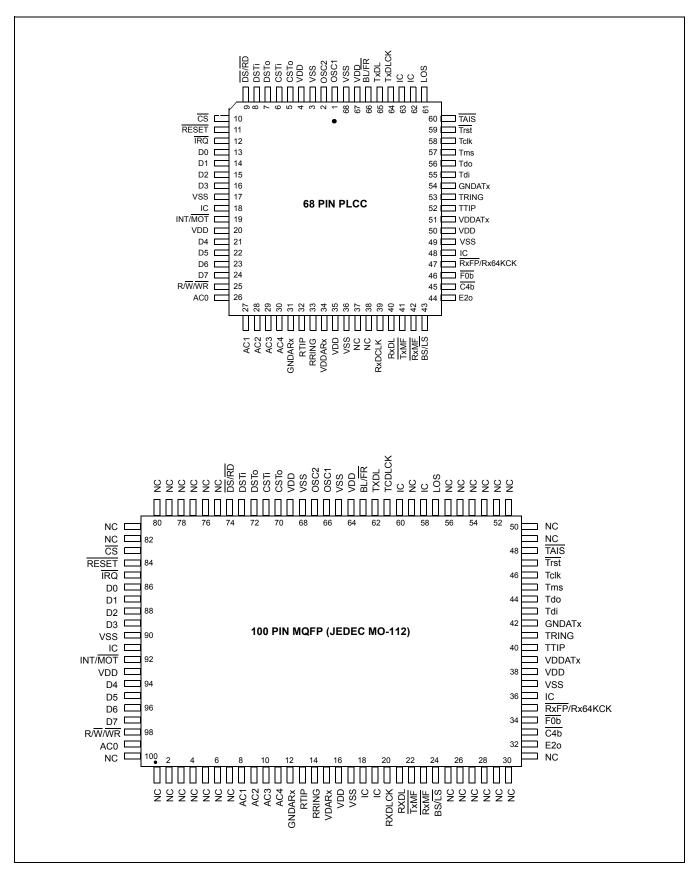

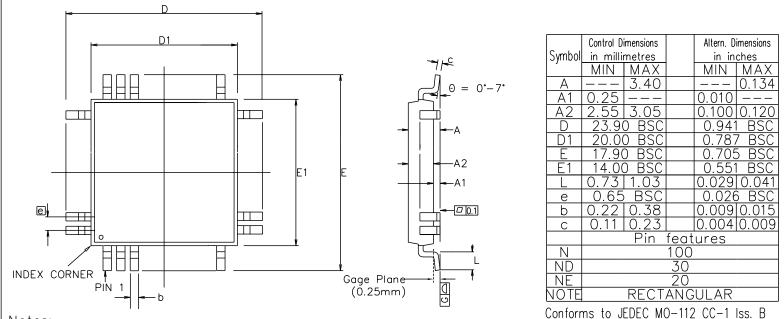

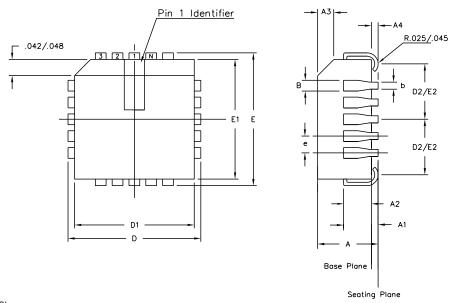

Combined PCM 30 framer, Line Interface Unit (LIU) and link controllers in a 68 pin PLCC or 100 pin MQFP package

- Selectable bit rate data link access with optional S<sub>a</sub> bits HDLC controller (HDLC0) and channel 16 HDLC controller (HDLC1)

- LIU dynamic range of 20 dB

- Enhanced performance monitoring and programmable error insertion functions

- · Low jitter DPLL for clock generation

- Operating under synchronized or free run mode

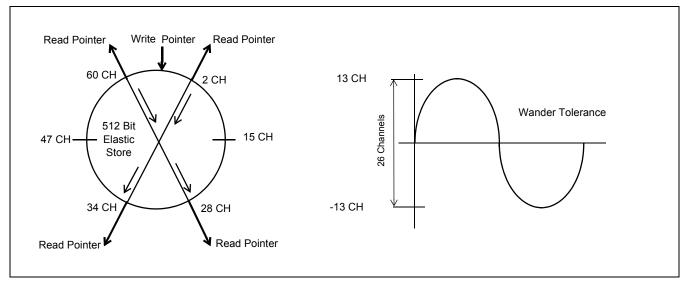

- Two-frame receive elastic buffer with controlled slip direction indication

- · Selectable transmit or receive jitter attenuator

- Intel or Motorola non-multiplexed parallel microprocessor interface

- CRC-4 updating algorithm for intermediate path points of a message-based data link application

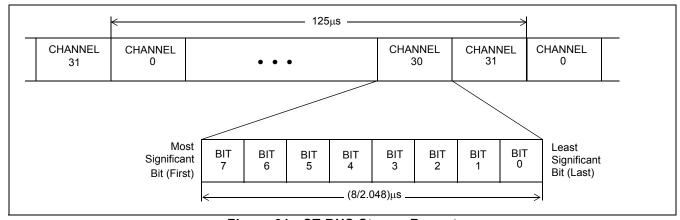

- ST-BUS/GCI 2.048 Mbit/s backplane bus for both data and signalling

# Ordering Information

68 Pin PLCC Tape & Reel MT9075BPR MT9075BL 100 Pin MQFP Travs MT9075BP 68 Pin PLCC **Tubes** MT9075BPR1 68 Pin PLCC\* Tape & Reel MT9075BP1 68 Pin PLCC\* Tubes 100 Pin MQFP\* Travs MT9075BL1 \*Pb Free Matte Tin -40°C to +85°C

# **Applications**

- E1 add/drop multiplexers and channel banks

- · CO and PBX equipment interfaces

- · Primary Rate ISDN nodes

- · Digital Cross-connect Systems (DCS)

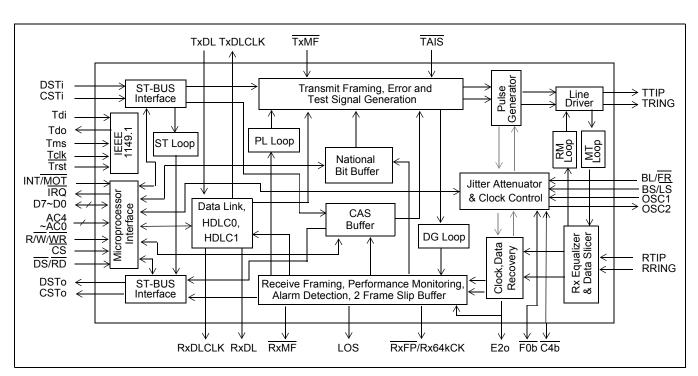

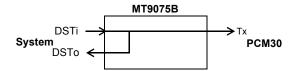

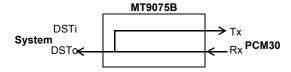

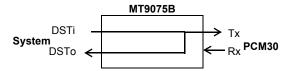

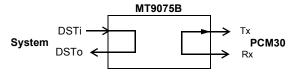

Figure 1 - Functional Block Diagram

# **Description**

The MT9075B is a single chip device which integrates an advanced PCM 30 framer with a Line Interface Unit (LIU).

The framer interfaces to a 2.048 Mbit/s backplane and provides selectable rate data link access with optional HDLC controllers for  $S_a$  bits and channel 16. The LIU interfaces the framer functions to the PCM 30 transformer-isolated four wire line.

The MT9075B meets or supports the latest ITU-T Recommendations including G.703, G.704, G.706, G.732, G.775, G.796, G.823 for PCM 30, and I.431 for ISDN primary rate. It also meets or supports ETSI ETS 300 011, ETS 300 166 and ETS 300 233 as well as BS 6450.

Figure 2 - Pin Connections

# **Pin Description**

| Piı  | n #  |                 | <b>D</b> 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PLCC | MQFP | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 1    | 66   | OSC1            | Oscillator Input. This pin is either connected via a 20.000 MHz crystal to OSC2 where a crystal is used, or is directly driven when a 20.000 MHz oscillator is employed (see Figures 6 and 7). CMOS input switching level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 2    | 67   | OSC2            | cillator Output. Not suitable for driving other devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 3    | 68   | V <sub>SS</sub> | egative Power Supply (Input). Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 4    | 69   | $V_{DD}$        | Positive Power Supply (Input). Digital supply (+5V $\pm$ 5%).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

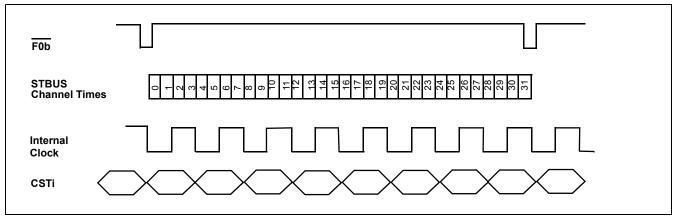

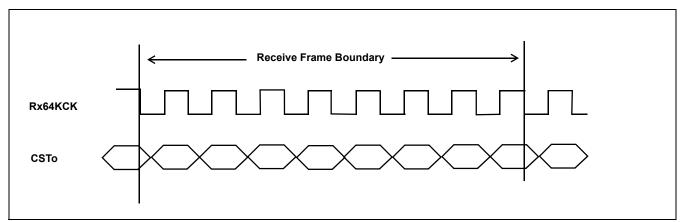

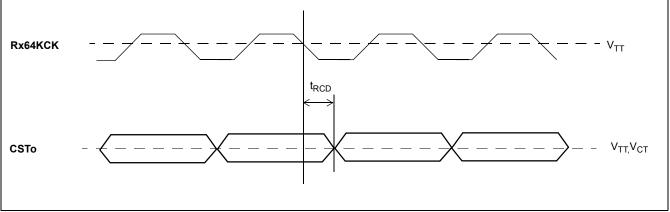

| 6    | 70   | CSTo            | Control ST-BUS Output. CSTo carries one of the following two serial streams for CAS and CCS respectively:  (i) A 2.048 Mbit/s ST-BUS status stream which contains the 30 receive signalling nibbles (ABCDZZZZ or ZZZZABCD). The most significant nibbles of each ST-BUS time slot are valid and the least significant nibbles of each ST-BUS time slot are tristated when control bit MSN (page 01H, address 1AH, bit 1) is set to 1. If MSN=0, the position of the valid and tristated nibbles is reversed.  (ii) A 64 kb/s output when the 64 KHz common channel signalling option is selected (page 01H, address 1AH, bit 0, 64KCCS =1) for channel 16.  Control ST-BUS Input. CSTi carries one of the following two serial streams for CAS and |  |  |  |  |  |

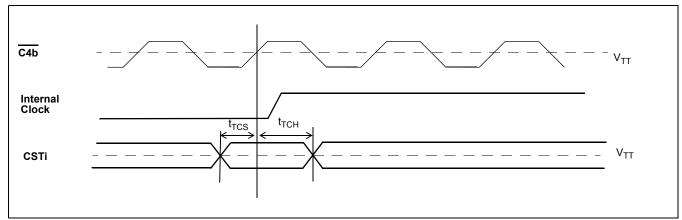

| •    | ,,   | 6311            | CCS respectively:  (i) A 2.048 Mbit/s ST-BUS control stream which contains the 30 transmit signalling nibbles (ABCDXXXX or XXXXABCD) when page 01H, address 1AH, bit 3, RPSIG=0. When RPSIG=1 this pin has no function. The most significant nibbles of each ST-BUS time slot are valid and the least significant nibbles of each ST-BUS time slot are ignored when control bit MSN (page 01H, address 1AH, bit 1) is set to 1. If MSN=0, the position of the valid and ignored nibbles is reversed.  (ii) A 64 kb/s input when the 64 KHz common channel signalling option is selected (page 01H, address 1AH, bit 0, 64KCCS =1) for channel 16.                                                                                                  |  |  |  |  |  |

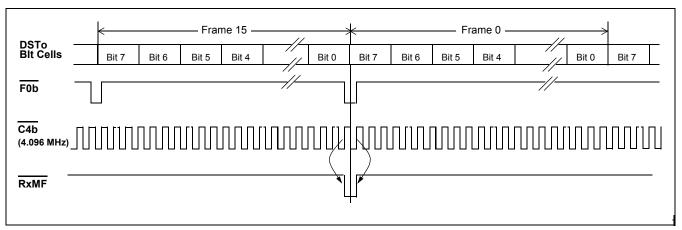

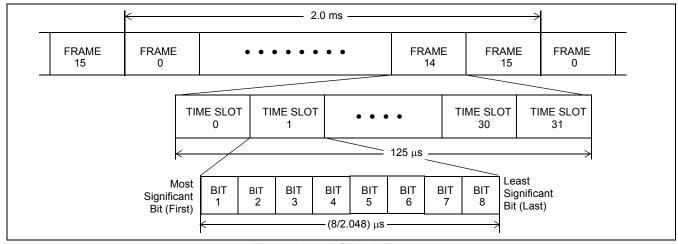

| 7    | 72   | DSTo            | <b>Data ST-BUS Output.</b> A 2.048 Mbit/s serial stream which contains the 30 PCM or data channels received on the PCM 30 line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

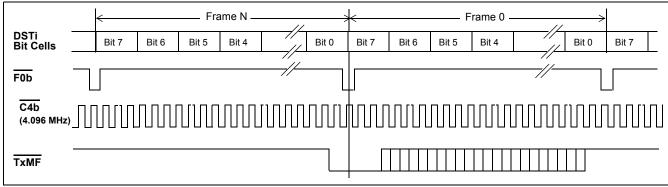

| 8    | 73   | DSTi            | <b>Data ST-BUS Input.</b> A 2.048 Mbit/s serial stream which contains the 30 PCM or data channels to be transmitted on the PCM 30 line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

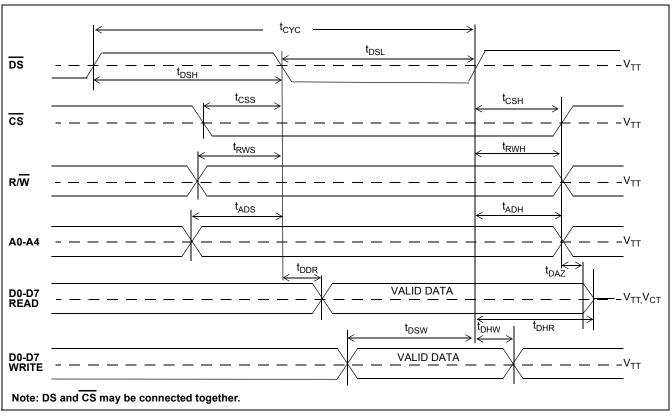

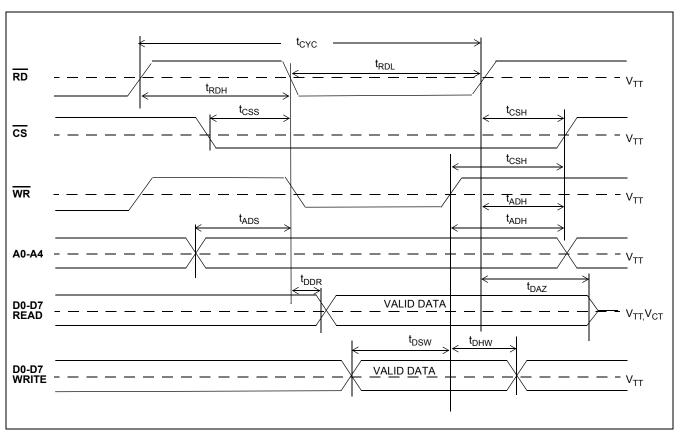

| 9    | 74   | DS/RD           | Data/Read Strobe (Input). In Motorola mode (DS), this input is the active low data strobe of the microprocessor interface. In Intel mode (RD), this input is the active low read strobe of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 10   | 83   | cs              | Chip Select (Input). This active low input enables the non-multiplexed parallel microprocessor interface of the MT9075B. When $\overline{\text{CS}}$ is set to high, the microprocessor interface is idle and all bus I/O pins will be in a high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 11   | 84   | RESET           | <b>RESET (Input).</b> This active low input puts the MT9075B in a reset condition. RESET should be set to high for normal operation. The MT9075B should be reset after power-up. The RESET pin must be held low for a minimum of $1\mu$ sec. to reset the device properly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

# Pin Description (continued)

| Pir        | n #         | Nama          | Description.                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC       | MQFP        | Name          | Description                                                                                                                                                                                                                                                                                                                                                                          |

| 12         | 85          | ĪRQ           | <b>Interrupt Request (Output).</b> A low on this output pin indicates that an interrupt request is presented. IRQ is an open drain output that should be connected to $V_{DD}$ through a pullup resistor. An active low $\overline{CS}$ signal is not required for this pin to function.                                                                                             |

| 13 -<br>16 | 86-<br>89   | D0 - D3       | <b>Data 0 to Data 3 (Three-state I/O).</b> These signals combined with D4-D7 form the bidirectional data bus of the microprocessor interface (D0 is the least significant bit).                                                                                                                                                                                                      |

| 17         | 90          | VSS           | Negative Power Supply (Input). Digital ground.                                                                                                                                                                                                                                                                                                                                       |

| 18         | 91          | IC            | Internal Connection. Tie to V <sub>SS</sub> (Ground) for normal operation.                                                                                                                                                                                                                                                                                                           |

| 19         | 92          | INT/MOT       | <b>Intel/Motorola Mode Selection (Input).</b> A high on this pin configures the processor interface for the Intel parallel non-multiplexed bus type. A low configures the processor interface for the Motorola parallel non-multiplexed type.                                                                                                                                        |

| 20         | 93          | VDD           | Positive Power Supply (Input). Digital supply (+5V $\pm$ 5%).                                                                                                                                                                                                                                                                                                                        |

| 21 -<br>24 | 94-<br>97   | D4 - D7       | Data 4 to Data 7 (Three-state I/O). These signals combined with D0-D3 form the bidirectional data bus of the microprocessor interface (D7 is the most significant bit).                                                                                                                                                                                                              |

| 25         | 98          | R/W/WR        | Read/Write/Write Strobe (Input). In Motorola mode (R/W), this input controls the direction of the data bus D[0:7] during a microprocessor access. When R/W is high, the parallel processor is reading data from the MT9075B. When low, the microprocessor is writing data to the MT9075B. For Intel mode (WR), this active low write strobe configures the data bus lines as output. |

| 26 -<br>30 | 99,<br>8-11 | AC0 -<br>AC4  | Address/Control 0 to 4 (Inputs). Address and control inputs for the microprocessor interface. AC0 is the least significant input.                                                                                                                                                                                                                                                    |

| 31         | 12          | GNDARx        | Receive Analog Ground (Input). Analog ground for the LIU receiver.                                                                                                                                                                                                                                                                                                                   |

| 32<br>33   | 13<br>14    | RTIP<br>RRING | Receive TIP and RING (Inputs). Differential inputs for the receive line signal - must be transformer coupled (See Figure 4).                                                                                                                                                                                                                                                         |

| 34         | 15          | VDDARx        | Receive Analog Power Supply (Input). Analog supply for the LIU receiver (+5V $\pm$ 5%).                                                                                                                                                                                                                                                                                              |

| 35         | 16          | VDD           | Positive Power Supply (Input). Digital supply (+5V $\pm$ 5%).                                                                                                                                                                                                                                                                                                                        |

| 36         | 17          | VSS           | Negative Power Supply (Input). Digital ground.                                                                                                                                                                                                                                                                                                                                       |

| 37         | 18          | IC            | Internal Connection. Must be left open for normal operation.                                                                                                                                                                                                                                                                                                                         |

| 38         | 19          | IC            | Internal Connection. Must be left open for normal operation.                                                                                                                                                                                                                                                                                                                         |

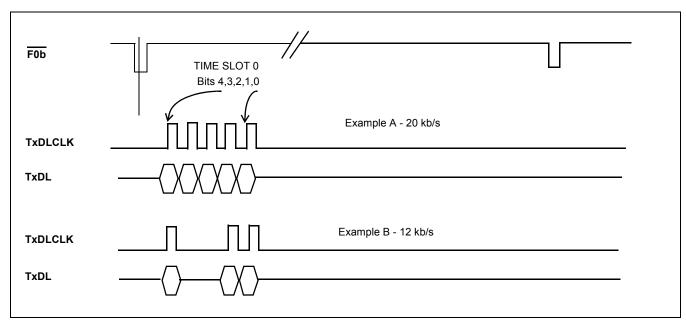

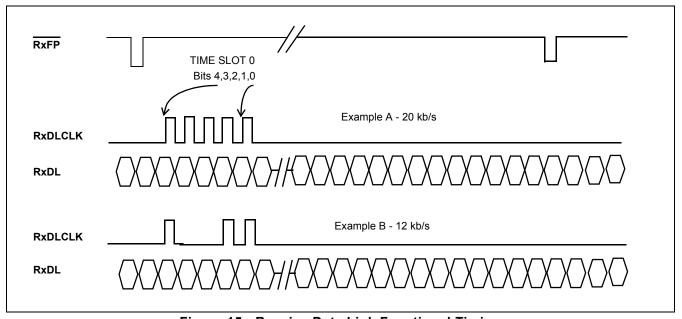

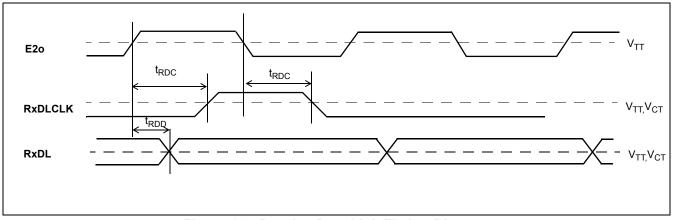

| 39         | 20          | RxDLCLK       | <b>Receive Data Link Clock (Output)</b> . A gapped clock signal derived from a 2.048 Mbit/s clock, available for an external device to clock in RxDL data (at 4, 8, 12, 16 or 20 kHz) on the rising edge.                                                                                                                                                                            |

| 40         | 21          | RxDL          | Receive Data Link (Output). A 2.048 Mbit/s data stream containing received line data after HDB3 decoding. This data is clocked out with the rising edge of E2o.                                                                                                                                                                                                                      |

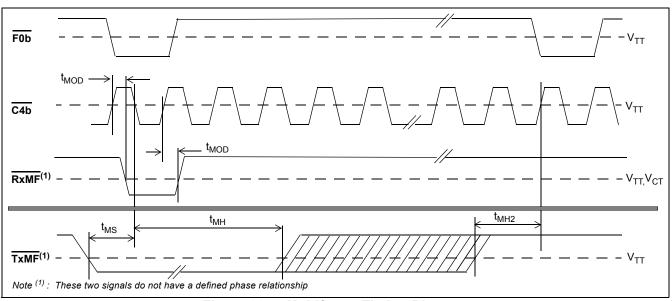

| 41         | 22          | TxMF          | <b>Transmit Multiframe Boundary (Input)</b> . An active low input used to set the transmit multiframe boundary (CAS or CRC multiframe). The MT9075B will generate its own multiframe if this pin is held high. This input is usually pulled high for most applications.                                                                                                              |

# Pin Description (continued)

| Pir      | า #      | Nissan             | December 1 and 1 a |

|----------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC     | MQFP     | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 42       | 23       | RxMF               | Receive Multiframe Boundary (Output). An output pulse delimiting the received multiframe boundary. The next frame output on the data stream (DSTo) is basic frame zero on the PCM 30 link. This receive multiframe signal can be related to either the receive CRC multiframe (page 01H, address 10H, bit 6, MFSEL=1) or the receive signalling multiframe (MFSEL=0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

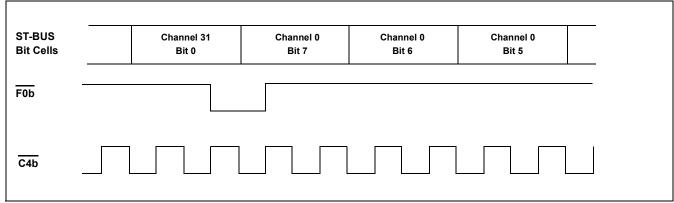

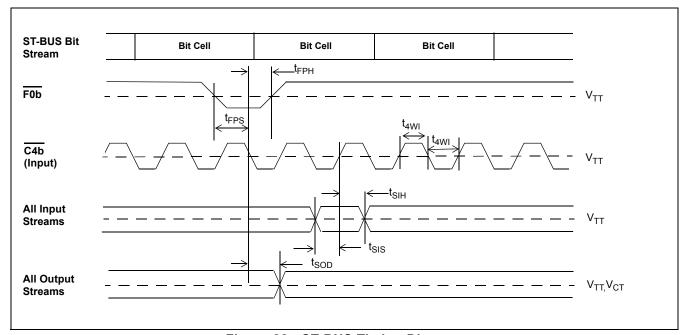

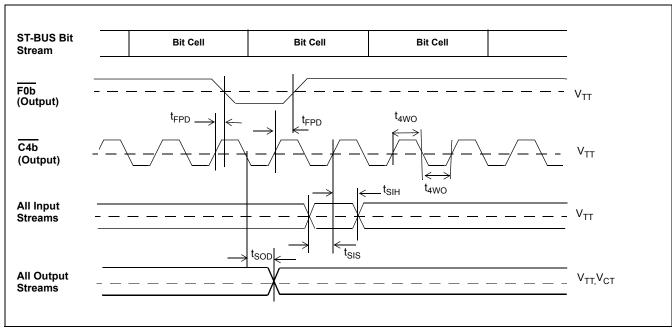

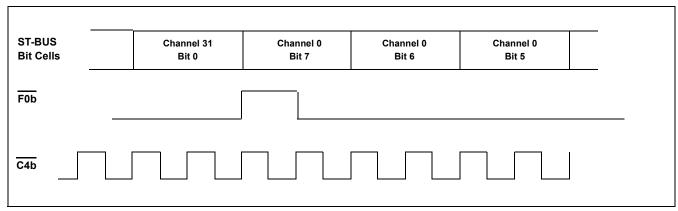

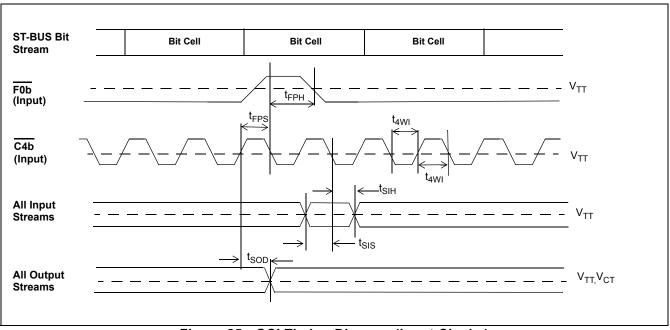

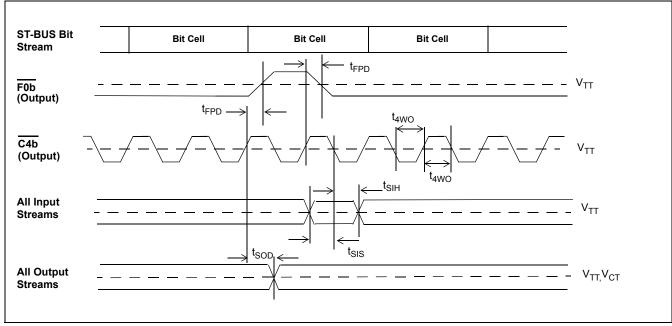

| 43       | 24       | BS/LS              | System Bus Synchronous/Line Synchronous Selection (Input). If high, $\overline{C4b}$ and $\overline{F0b}$ will be inputs; if low, $\overline{C4b}$ and $\overline{F0b}$ will be outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 44       | 32       | E2o                | <b>2.048 MHz Extracted Clock (Output).</b> The clock extracted from the received signal and used internally to clock in data received on RTIP and RRING.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

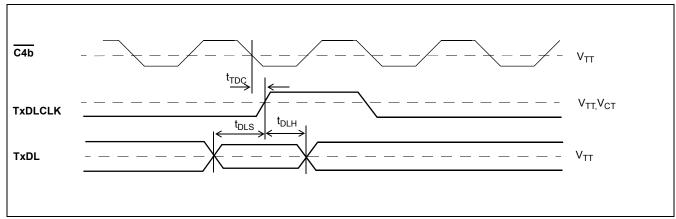

| 45       | 33       | C4b                | <b>4.096 MHz System Clock (Input/Output)</b> . $\overline{C4b}$ is the clock for the ST-BUS sections and transmit serial PCM data of the MT9075B. In the free-run (BL/ $\overline{FR}$ =0) or line synchronous mode (BL/ $\overline{FR}$ =1 and $\overline{BS/LS}$ =0) this signal is an output, while in the system bus synchronous mode (BS/ $\overline{LS}$ =1) this signal is an input clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 46       | 34       | F0b                | Frame Pulse (Input/Output). This is the ST-BUS or GCI frame synchronization signal, which delimits the 32 channel frame of CSTi, CSTo, DSTi, DSTo and the PCM30 link. In the free-run (BL/FR=0) or loop synchronous mode (BL/FR=1 and BS/LS=0) this signal is an output, while in the Bus Synchronous mode (BL/FR=1 and BS/LS=0) this signal is an input. The GCI/ST-BUS selection is made under software control. Page 02H, address 13H, bit 0, GCI/ST=1 selects GCI frame pulse; GCI/ST=0 selects ST-BUS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 47       | 35       | RxFP/Rx6<br>4KCK   | Receive Frame Pulse/Receive CCS Clock (Output). An 8 kHz pulse signal, which is low for one extracted clock period. This signal is synchronized to the receive PCM 30 basic frame boundary.  When 64KCCS (page 01H, address 1AH, bit 0) is set to 1, this pin outputs a 64 kHz clock derived by dividing down the extracted 2.048 MHz clock. This clock is used to clock CCS data out of pin CSTo in the CCS mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 48       | 36       | IC                 | Internal Connection. Must be left open for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 49       | 37       | V <sub>SS</sub>    | Negative Power Supply (Input). Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 50       | 38       | V <sub>DD</sub>    | Positive Power Supply (Input). Digital supply (+5V ± 5%).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 51       | 39       | VDD <sub>ATx</sub> | <b>Transmit Analog Power Supply (Input).</b> Analog supply for the LIU transmitter (+5V $\pm$ 5%).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 52<br>53 | 40<br>41 | TTIP<br>TRING      | <b>Transmit TIP and RING (Outputs).</b> Differential outputs for the transmit line signal - must be transformer coupled (See Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 54       | 42       | $GND_{ATx}$        | Transmit Analog Ground (Input). Analog ground for the LIU transmitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 55       | 43       | Tdi                | IEEE 1149.1 Test Data Input. If not used, this pin should be pulled high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 56       | 44       | Tdo                | IEEE 1149.1 Test Data Output. If not used, this pin should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 57       | 45       | Tms                | IEEE 1149.1 Test Mode Selection (Input). If not used, this pin should be pulled high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 58       | 46       | Tclk               | IEEE 1149.1 Test Clock Signal (Input). If not used, this pin should be pulled high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 59       | 47       | Trst               | IEEE 1149.1 Reset Signal (Input). If not used, this pin should be held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Pin Description (continued)

| Piı  | n #                                       | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------|-------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PLCC | MQFP                                      | Name    |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 60   | 48                                        | TAIS    | <b>Transmit Alarm Indication Signal (Input).</b> An active low on this input causes the MT9075B to transmit an AIS (all ones signal) on TTIP and TRING pins. TAIS should be set to high for normal data transmission.                                                                                                                                                                                                          |  |  |  |  |

| 61   | 57                                        | LOS     | oss of Signal or Synchronization (Output). When high, and LOS/LOF (page 02hddress 13H bit 2) is zero, this signal indicates that the receive portion of the MT9075le either not detecting an incoming signal (bit LLOS on page 03H address 18H is one) of detecting a loss of basic frame alignment condition (bit SYNC on page 03H address 0H is one). If LOS/LOF=1, a high on this pin indicates a loss of signal condition. |  |  |  |  |

| 62   | 58                                        | IC      | nternal Connection. Tie to V <sub>SS</sub> (Ground) for normal operation.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|      | 59                                        | NC      | No Connection. Leave open for normal operation.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 63   | 60                                        | IC      | Internal Connection. Tie to V <sub>SS</sub> (Ground) for normal operation.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 64   | 61                                        | TxDLCLK | <b>Transmit Data Link Clock (Output).</b> A gapped clock signal derived from a gated 2.048 Mbit/s clock for transmit data link at 4, 8, 12, 16 or 20 kHz. The transmit data link data (TxDL) is clocked in on the rising edge of TxDLCLK. TxDLCLK can also be used to clock DL data out of an external serial controller.                                                                                                      |  |  |  |  |

| 65   | 62                                        | TxDL    | <b>Transmit Data Link (Input)</b> . An input serial stream of transmit data link data at 4, 8, 12, 16 or 20 kbit/s composed of 488ns-wide bit cells which are multiplexed into selected national bits of the PCM 30 transmit signal.                                                                                                                                                                                           |  |  |  |  |

| 66   | 63                                        | BL/FR   | <b>Bus or Line/Freerun (Input).</b> If this pin is set to high, the MT9075B is in the System Bus or Line Synchronous mode depending on the BS/LS pin. If low, the MT9075B is in the free run mode.                                                                                                                                                                                                                             |  |  |  |  |

| 67   | 64                                        | VDD     | Positive Power Supply (Input). Digital supply (+5V $\pm$ 5%).                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 68   | 65                                        | VSS     | Negative Power Supply (Input). Digital ground.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|      | 1-7,<br>25-31,<br>49-56,<br>75-82,<br>100 | NC      | No Connection. Leave open for normal operation.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

#### **Device Overview**

The MT9075B is an advanced PCM 30 framer with an on-chip Line Interface Unit (LIU) that meets or supports the latest ITU-T Recommendations for PCM 30 and ISDN primary rate including G.703, G.704, G.706, G.775, G.796, G.732, G.823 and I.431. It also meets or supports the layer 1 requirements of ETSI ETS 300 011, ETS 300 166, ETS 300 233 and BS6450.

The Line Interface Unit (LIU) of the MT9075B interfaces the digital framer functions to the PCM 30 transformer-isolated four wire line. The transmit portion of the MT9075B LIU consists of a digital buffer, a digital-to-analog converter and a differential line driver. The receiver portion of the LIU consists of an input signal peak detector, an optional two-stage equalizer, a smoothing filter, data and clock slicers and a clock extractor. The optional equalizer allows for error free reception of data with a line attenuation of up to 20 dB.

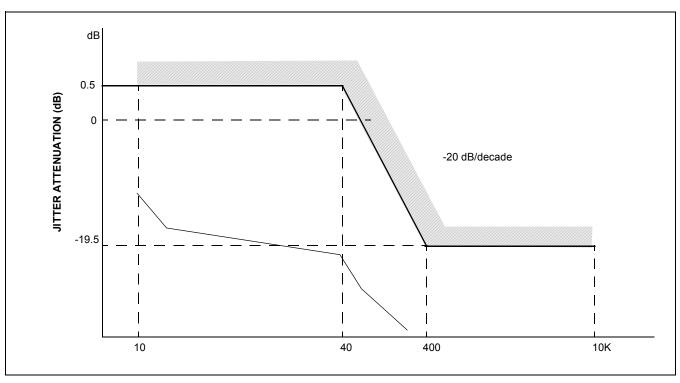

The LIU also contains a Jitter Attenuator (JA), which can be configured to either the transmit or receive path. The JA will attenuate jitter from 2.5 Hz and roll-off at a rate of 20 dB/decade. Its intrinsic jitter is less than 0.02 UI.

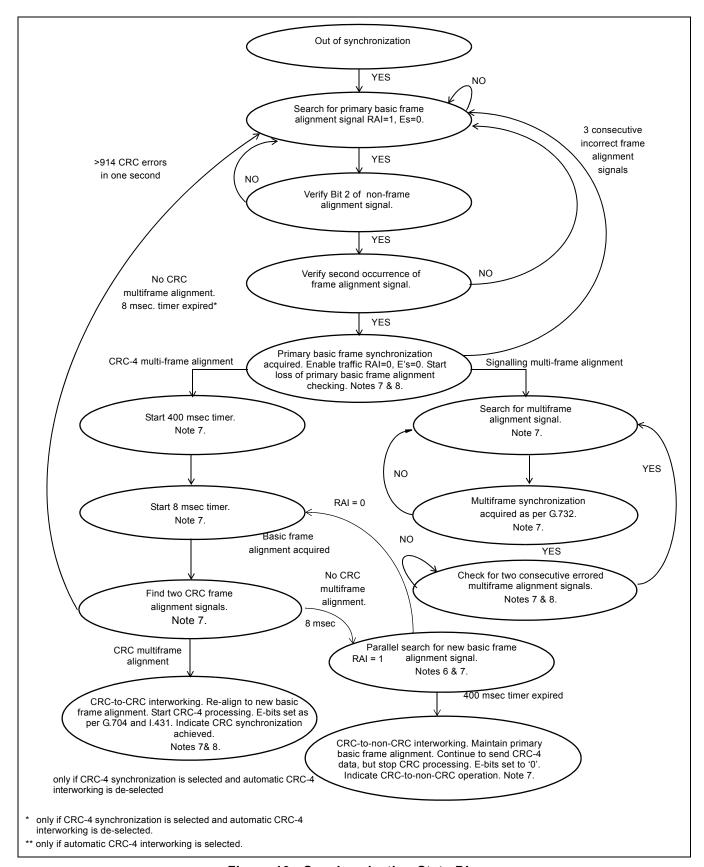

The digital portion of the MT9075B connects an incoming stream of time multiplexed PCM channels (at 2.048 Mbit/s) to the transmit payload of the E1 trunk, while the receive payload is connected to the ST-BUS or GCI 2.048 Mbit/s backplane bus for both data and signalling. Control, reporting and conditioning of the line is implemented via a parallel microprocessor interface. The MT9075B framing algorithm allows automatic interworking between CRC-4 and non-CRC-4 interfaces.

The S<sub>a</sub> bits can be accessed by the MT9075B in the following four ways:

- Single byte registers;

- Five byte transmit and receive national bit buffers;

- Data link pins TxDL, RxDL, RxDLCLK and TxDLCLK;

- · HDLC Controller with a 128 byte FIFO.

The MT9075B operates in either termination or transparent modes selectable via software control. In the termination mode the CRC-4 calculation is performed as part of the framing algorithm. In the transmit transparent mode, no framing or signalling is imposed on the data transmit from DSTi on the line. In addition, the MT9075B optionally allows the data link maintenance channel to be modified and updates the CRC-4 remainder bits to reflect the modification. All channel, framing and signalling data passes through the device unaltered. This is useful for intermediate point applications of a PCM 30 link where the data link data is modified, but the error information transported by the CRC-4 bits must be passed to the terminating end. In the receive transparent mode, the received line data is channelled to DSTo with framing operations disabled, consequently, the data passes through the slip buffer and drives DSTo with an arbitrary alignment.

The MT9075B has a comprehensive suite of status, alarm, performance monitoring and reporting features. These include counters for BPVs, CRC errors, E-bit errors, errored frame alignment signals, BERT, and RAI and continuous CRC errors. Also, included are transmission error insertion for BPVs, CRC-4 errors, frame and non-frame alignment signal errors, payload errors and loss of signal errors.

A complete set of loopback functions is provided, which includes digital, remote, ST-BUS, payload, metallic, local and remote time slot.

The MT9075B also contains a comprehensive set of maskable interrupts and an interrupt vector function. Interrupt sources consist of synchronization status, alarm status, counter indication and overflow, timer status, slip indication, maintenance functions and receive channel associated signalling bit changes. A special set of maskable interrupts have been included for sensing changes in the state of the national use bits and nibbles, in compliance to emerging ETS requirements.

The MT9075B system timing may be slaved to the line, operated in freerun mode, or controlled by an external timing source.

# **Functional Description**

#### MT9075B Line Interface Unit (LIU)

## Receiver

The receiver portion of the MT9075B LIU consists of an input signal peak detector, an optional two-stage equalizer, a smoothing filter, adaptive threshold comparators, data and clock slicers, and a clock extractor. Receive equalization gain can be set via software control or it can be determined automatically by the peak detectors.

The output of the receive equalizer is conditioned by a smoothing filter and is passed on to the clock and data slicer. The clock slicer output signal drives a phase locked loop, which generates the extracted clock (E2o). This extracted clock is used to sample the output of the data comparator.

The LOS output pin (pin 61 in PLCC, pin 57 in MQFP) is user selectable, by setting control bit LOS/LOF (page 02H, register 13H, bit 2), to indicate a loss of signal or loss of basic frame synchronization condition. In addition, a status

bit, LLOS (bit 4 in page 3, register 18H) is provided to indicate the presence of a loss signal condition. The occurrence of a loss signal condition is defined as per I.431, i.e., when the incoming signal amplitude is more than 20 dB below the nominal amplitude for a time duration of at least 1 ms.

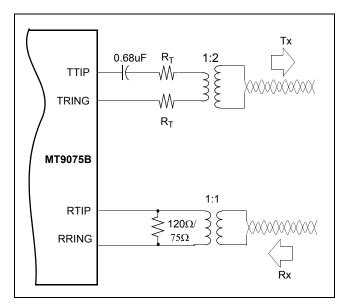

The receive LIU circuit requires a terminating resistor of either 120  $\Omega$  or 75  $\Omega$  across the device side of the receive1:1 transformer as shown in Figure 4. The return loss of the receiver, complying with G.703, is greater than:

- 12 dB from 51 kHz to 102 kHz;

- 18 dB from 102 kHz to 2048 kHz:

- 14 dB from 2048 kHz to 3072 kHz.

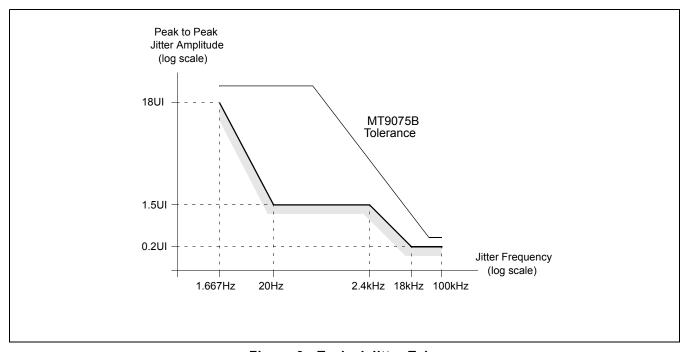

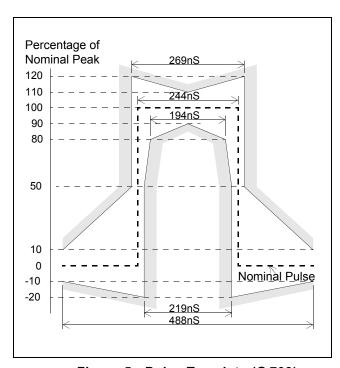

The jitter tolerance of the MT9075B clock extractor circuit exceeds the requirements of G.823 (Figure 3).

#### **Transmitter**

The MT9075B differential line driver is designed to drive a 1:2 step-up transformer (see Figure 4). A 0.68 uF capacitor is required between the TTIP and the transmit transformer. Resistors  $R_T$  (as shown in Figure 4) are for termination for transmit return loss. The values of  $R_T$  may be optimized for 120  $\Omega$  lines, 75  $\Omega$  lines or set at an intermediary value to serve both applications. Program the Transmit Pulse Control Word (address 1FH page 1) to adjust the pulse amplitude accordingly. Alternatively, the pulse level and shape may be discretely programmed by writing to the Customer Pulse Level registers (addresses 1CH to 1FH, page 2) and setting the Custom Transmit Pulse bit high (bit 3 of the Transmit Pulse Control Word).

Figure 3 - Typical Jitter Tolerance

Figure 4 - Analog Line Interface

The template for the transmitted pulse, as specified in G703, is shown in Figure 5. The nominal peak voltage of a mark is 3 volts for 120  $\Omega$  twisted pair applications and 2.37 volts for 75  $\Omega$  coax applications. The ratio of the amplitude of the transmit pulses generated by TTP and TRING is between 0.95 and 1.05.

Figure 5 - Pulse Template (G.703)

## **Transformer Recommendation**

Table 1 shows a list of recommended transformers for the MT9075B line interface.

| Manufacturer      | For Tx   | For Rx   |

|-------------------|----------|----------|

| Filtran           | 5721-1   | 5721-2   |

| Pulse Engineering | PE-65351 | PE-64934 |

| Midcom            | 50027    | 50026    |

| OSEC              | 02934/A  | 02935/A  |

Table 1 - Transformer Manufacturers and Part Numbers

# **Timing Source**

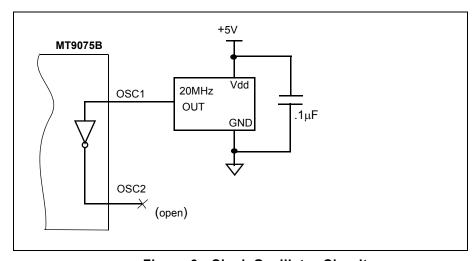

The MT9075B can use either a clock or crystal, connecting to pins OSC1 and OSC2, as the reference timing source.

Figure 6 shows a 20 MHz clock oscillator, with 50 ppm tolerance, directly connected to the OSC1 pin of the MT9075B.

Figure 6 - Clock Oscillator Circuit

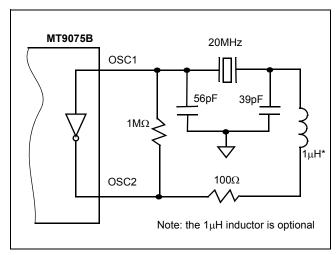

Alternatively, a crystal oscillator may be used. A complete oscillator circuit made up of a crystal, resistors and capacitors is shown in Figure 7. The crystal specification is as follows.

$Frequency: 20 \, MHz \\ Tolerance: 50 \, ppm \\ Oscillation \, Mode: Fundamental \\ Resonance \, Mode: Parallel \\ Load \, Capacitance: 32 \, pF \\ Maximum \, Series \, Resistance: 35 \, \Omega \\ Approximate \, Drive \, Level: 1 \, mW$

Figure 7 - Crystal Oscillator Circuit

## **Jitter Attenuator (JA)**

The MT9075B Jitter Attenuator (JA), which consists of a Phase Locked Loop (PLL) and data FIFO, can be used on either the transmit or receive side of the interface.

On the transmit side the  $\overline{\text{C4b}}$  signal clocks the data into the FIFO, the PLL de-jitters the  $\overline{\text{C4b}}$  clock and the resulting clean  $\overline{\text{C4b}}$  signal clocks the data out of the FIFO.

When the JA is selected on the receive side, the extracted clock signal clocks the data into the FIFO. The same clock feeds the PLL and the resulting de-jittered clock is used to clock the data out of the FIFO.

The JA meets the jitter transfer characteristics as proposed by G.823 and the relevant recommendations as shown in Figure 8. The JA FIFO depth can be selected to be from 16 to 128 words deep, in multiples of 16 (2-bit) words. Its read pointer can be centered by changing the JFC bit (address 18H of page 02H) to provide maximum jitter tolerance. If the read pointer should come within 4 bits of either end of the FIFO, the read clock frequency will be increased or decreased by 0.0625 UI to correct the situation. The maximum time needed to centre is  $T_{max}$ = 3904\*Depth ns, where Depth is the selected JA FIFO depth. During this time the JA will not attenuate jitter.

To ensure normal operation, the JA FIFO depth should be set in software to be larger than the anticipated maximum UI of input jitter.

#### **Clock Jitter Attenuation Modes**

MT9075B has three basic jitter attenuation modes of operation, selected by the BS/LS and BL/FR control pins.

- System Bus Synchronous Mode

- · Line Synchronous Mode

- Free-run mode

Figure 8 - Typical Jitter Attenuation Curve

| Mode Name           | BS/LS | BL/FR | JAS | JAT/JAR | Note                                                                       |

|---------------------|-------|-------|-----|---------|----------------------------------------------------------------------------|

| SysBusSync1         | 1     | 1     | 1   | 1       | JA on Tx side; No JA on Rx side                                            |