# LH1594/LH1595

#### DESCRIPTION

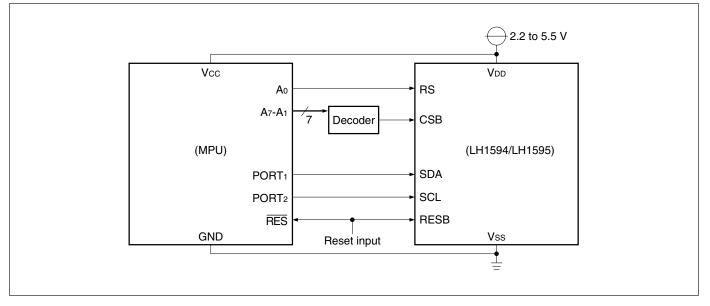

The LH1594/LH1595 are LCD drivers with a built-in character ROM suitable for driving small scale dotmatrix LCD panels, and which are capable of being directly connected to the bus line of a microcomputer. The 8-bit parallel or serial data transferred from a microcomputer is used to generate LCD drive signals for displaying characters. Incorporating a character ROM which has font characters configured in the format of 5 x 8 dots and a character RAM which allows the user to define characters, the LH1594/LH1595 provide a higher freedom of display. Since the LH1594/LH1595 have 80 output pins for a segment drive circuit and 17 output pins for a common drive circuit in a single chip, a display system for 16 characters x 2 lines can be implemented easily. The LH1594/LH1595 enable an LCD system for battery-operated, handcarrying information equipment by securing lower power consumption and wider operating voltage range.

### FEATURES

• Built-in CGROM : 240 characters

(5 x 8 x 240 = 9 600 bits)

Built-in CGRAM : 8 characters

(5 x 8 x 8 = 320 bits)

• Built-in SEGRAM : 80 segments

```

(16 \times 7 = 112 \text{ bits})

```

- Built-in display data RAM : 32 characters (32 x 8 = 256 bits)

- Format of font character : 5 x 8 dots including 1 dot which also serves to display a cursor

- General 8-bit MPU interface : Possible to directly connect 80-family or 68-family MPU to bus line

- Possible to make serial interface (I<sup>2</sup>C BUS\* format is for LH1594)

- Ratio of display duty cycle : 1/8, 1/9, 1/16 or 1/17 (selectable by command)

## 80-Segment and 17-Common Outputs LCD Driver IC with A Built-in CGROM

- Abundant command functions

- Display of 2 lines by 16 characters

- Display ON/OFF

- Normal/reverse display control

- Busy flag readout

- Cursor display

- Blinking : per character

- Display double fonts lengthwise

- Power saving mode

- LCD drive power circuit

- Built-in booster circuit : Two or three times voltage boost is possible

- Built-in voltage converter : Generates LCD drive voltages (V0, V1, V2, V3 and V4) based on the boosted voltage

- Built-in power bias ratio :

1/4 or 1/5 bias (selectable by command)

- Built-in electronic volume : Controllable in 16 steps

- Supply voltages

Logic system : +2.2 to +5.5 V

- LCD drive system : +4.0 to +11.0 V

- Operating temperature : –30 to +85  $^\circ\text{C}$

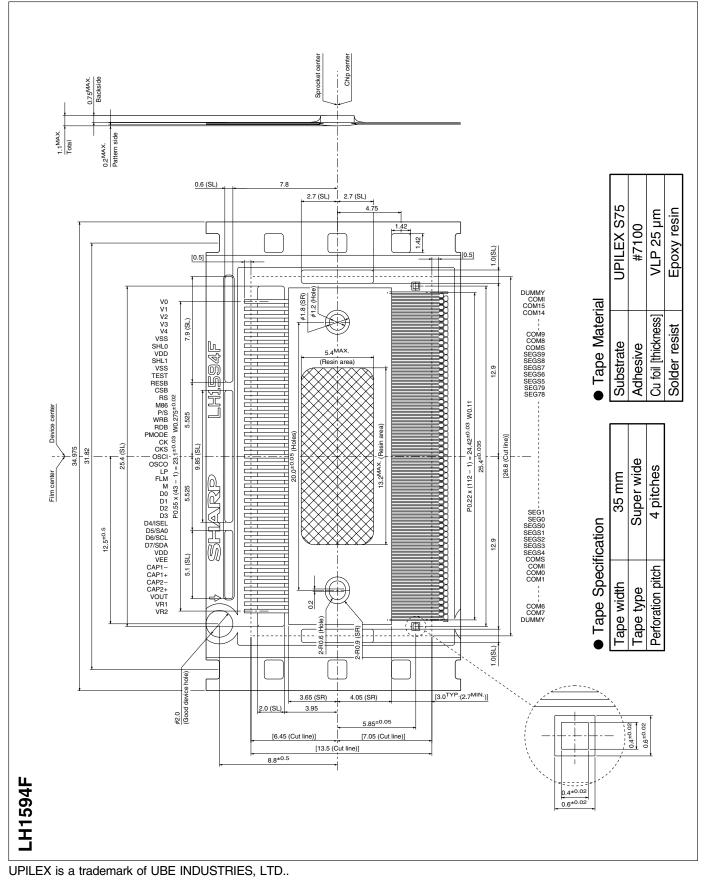

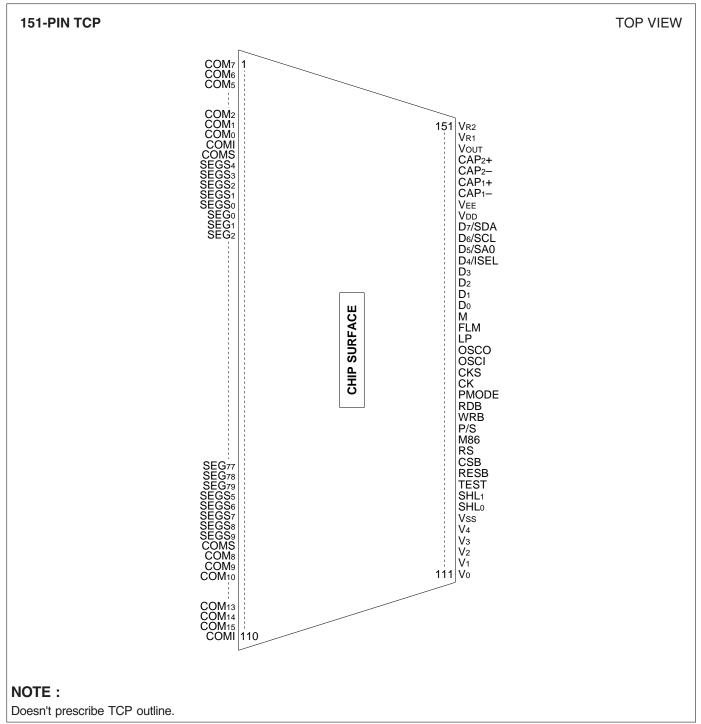

- Package : 151-pin TCP (Tape Carrier Package)

- \* Purchase of I<sup>2</sup>C components of Sharp Corporation, or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

#### **PIN CONNECTIONS**

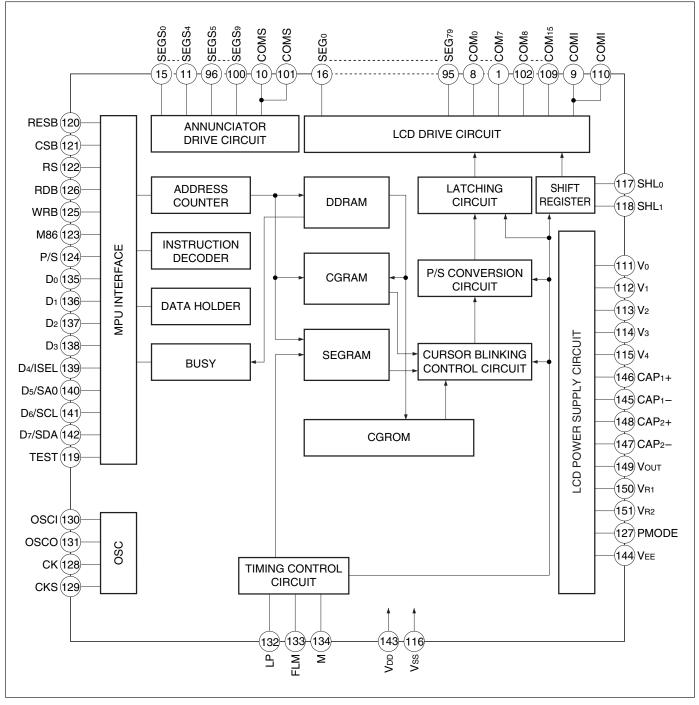

#### **BLOCK DIAGRAM**

## **1. PIN DESCRIPTION**

## 1.1. Power Supply Pins

| SYMBOL | I/O          | DESCRIPTION                                                                          |  |  |  |  |  |  |

|--------|--------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Vdd    | Power supply | ower supply pin for logic, connected to +2.2 to +5.5 V.                              |  |  |  |  |  |  |

| Vss    | Power supply | Ground pin, connected to 0 V.                                                        |  |  |  |  |  |  |

|        |              | Bias power supply pins for LCD drive voltage.                                        |  |  |  |  |  |  |

|        |              | • When using an external power supply, convert impedance by using resistance-        |  |  |  |  |  |  |

|        |              | division of LCD drive power supply or operational amplifier before adding voltage to |  |  |  |  |  |  |

| Vo     |              | the pins.                                                                            |  |  |  |  |  |  |

| V1     |              | When using the external power supply, maintain the following power supply            |  |  |  |  |  |  |

| V2     | Power supply | conditions.                                                                          |  |  |  |  |  |  |

| V3     |              | VSS < V4 < V3 < V2 < V1 < V0                                                         |  |  |  |  |  |  |

| V4     |              | • When the power supply circuit is ON, LCD drive voltage of Vo to V4 are generated   |  |  |  |  |  |  |

|        |              | by the internal booster circuit and voltage converter.                               |  |  |  |  |  |  |

|        |              | • When using the internal power supply, be sure to connect each capacitor between    |  |  |  |  |  |  |

|        |              | Vo to V4 and Vss.                                                                    |  |  |  |  |  |  |

## 1.2. LCD Power Supply Circuit Pins

| SYMBOL | I/O            | DESCRIPTION                                                                          |

|--------|----------------|--------------------------------------------------------------------------------------|

| CAP1+  | 0              | Connecting pin for the internal booster's capacitor + side.                          |

| CAP1+  | 0              | The capacitor is connected between CAP1- and CAP1+.                                  |

| CAP1-  | 0              | Connecting pin for the internal booster's capacitor - side.                          |

| CAFI-  | 0              | The capacitor is connected between CAP1+ and CAP1                                    |

| CAP2+  | 0              | Connecting pin for the internal booster's capacitor + side.                          |

| CAP2+  | 0              | The capacitor is connected between CAP2- and CAP2+.                                  |

| CAP2-  | о              | Connecting pin for the internal booster's capacitor - side.                          |

| CAF2-  |                | The capacitor is connected between CAP2+ and CAP2                                    |

| VEE    | Devuer Oversky | Voltage supply pin for generating boosted voltage in the internal booster circuit.   |

| VEE    | Power Supply   | Usually the same voltage level as VDD.                                               |

| Vout   | Power Supply/  | Output pin of boosted voltage in the internal booster circuit.                       |

| V001   | 0              | The capacitor must be connected between Vss and Vout.                                |

| VR1    |                | Used as input pins for voltage converter.                                            |

| VR2    | I              | Voltage must be input between the VEE and VOUT pins by voltage divided by resistors. |

|        |                | Pin for controlling LCD power supply.                                                |

| PMODE  | I              | A combination of PMODE pin and ON/OFF command of power supply (PON)                  |

|        |                | enables selection of a specific drive operation.                                     |

## 1.3. System Bus Pins

| SYMBOL            | I/O | DESCRIPTION                                                                                     |

|-------------------|-----|-------------------------------------------------------------------------------------------------|

|                   |     | • When set to parallel interface mode (P/S = "H").                                              |

|                   |     | Used as an 8-bit bi-directional data bus (D7 to D0), which is connected to 8-bit MPU            |

|                   |     | data bus.                                                                                       |

|                   |     | • When set to serial interface mode (P/S="L").                                                  |

|                   |     | Used as serial interface signals (SDA, SCL, SA0, ISEL).                                         |

|                   |     | [SDA]                                                                                           |

| Do                |     | LH1594 : I/O pin for the I <sup>2</sup> C BUS data line when serial interface is selected.      |

| D0<br>D1          |     | Must be connected to a positive power supply via pull-up resistor.                              |

|                   |     | LH1595 : Serial-data input pin at time of serial interface selection.                           |

| D2<br>D3          |     | [SCL]                                                                                           |

| D3<br>D4/ISEL     | I/O | LH1594 : Input pin for the I <sup>2</sup> C BUS clock signal when serial interface is selected. |

| D4/ISEL<br>D5/SA0 |     | Must be connected to a positive power supply via pull-up resistor.                              |

| D5/SAU<br>D6/SCL  |     | LH1595 : Serial clock pin at time of serial interface selection.                                |

| Do/SCL<br>D7/SDA  |     | [SA0]                                                                                           |

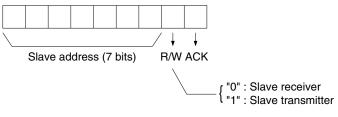

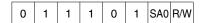

| D//SDA            |     | LH1594 : Used for LSB bit of slave address for I <sup>2</sup> C BUS (7 bits width).             |

|                   |     | Must be fixed to "H" or "L".                                                                    |

|                   |     | LH1595 : Must be set to "L". If set to "H", LH1595 operation is not warranty.                   |

|                   |     | [ISEL]                                                                                          |

|                   |     | LH1594 : Used to identify I <sup>2</sup> C BUS. When using I <sup>2</sup> C BUS, fix to "H".    |

|                   |     | If ISEL is set to "L", LH1594 operation is not warranty.                                        |

|                   |     | LH1595 : Must be set to "L". If set to "H", LH1595 operation is not warranty.                   |

| CSB               | 1   | Chip selection input pin that decoded address bus signal is input.                              |

|                   |     | Distinguishes display RAM data/commands of D7 to D0 data transferred from MPU.                  |

| RS                | 1   | 1 : The data of D7 to D0 show the display RAM data.                                             |

|                   |     | 0 : The data of D7 to D0 show the command data.                                                 |

| RESB              | I   | Initialized by setting to "L". The reset signals of the system are normally input. Reset        |

|                   | •   | operation is performed in accordance with RESB signal level.                                    |

|                   |     | In connecting to 80-family MPU :                                                                |

|                   |     | This RDB is a pin for connecting the RDB signal of 80-family MPU. When the                      |

| RDB               |     | signal enters in the "L" state, the data bus of this IC turns to the "output" state.            |

| (E)               |     | In connecting to 68-family MPU :                                                                |

|                   |     | This RDB becomes a pin for connecting the enable clock signal of 68-family MPU.                 |

|                   |     | When the signal enters in the "H" state, the data bus of this IC turns to the "active"          |

|                   |     | state.                                                                                          |

| SYMBOL | I/O | DESCRIPTION                                                                       |

|--------|-----|-----------------------------------------------------------------------------------|

|        |     | In connecting to 80-family MPU :                                                  |

|        |     | This WRB is a pin for connecting the WRB signal of 80-family MPU, and when        |

|        |     | WRB signal is "L", this pin is "active".                                          |

| WBB    |     | The data bus signal is input at the rising edge of WRB signal.                    |

| (R/W)  | I   | In connecting to 68-family MPU :                                                  |

|        |     | This WRB becomes a pin for connecting the R/W signal of controlling read/write of |

|        |     | 68-family MPU.                                                                    |

|        |     | R/W = "H" : Read                                                                  |

|        |     | R/W = "L" : Write                                                                 |

|        |     | MPU interface-type shift pin.                                                     |

| M86    | I   | M86 = "H" : 68-family interface                                                   |

| WIGO   |     | M86 = "L" : 80-family interface                                                   |

|        |     | Fixed to either "H" or "L".                                                       |

|        |     | Used to shift between parallel interface and serial interface.                    |

| P/S    | I   | P/S = "H" for parallel interface. Fix SDA and SCL pins to either "H" or "L".      |

| 1/3    |     | P/S = "L" for serial interface. Fix D3 to D0 pins to High-Z, RDB and WRB pins to  |

|        |     | either "H" or "L".                                                                |

| TEST   | I   | For testing. Fix to "L".                                                          |

## 1.4. LCD Drive Circuit Signals

| SYMBOL     | I/O | DESCRIPTION                                                                             |  |  |  |  |

|------------|-----|-----------------------------------------------------------------------------------------|--|--|--|--|

| LP         | 0   | The latching signal of display data to count up the display line counter at the rising, |  |  |  |  |

|            | 0   | and to output the LCD drive signals at the falling.                                     |  |  |  |  |

|            |     | Output pin for LCD display synchronous signals (first line marker).                     |  |  |  |  |

| FLM        | 0   | When FLM pin is set to "H", the display starting line address is preset in the display  |  |  |  |  |

|            |     | line counter.                                                                           |  |  |  |  |

| М          | 0   | Output pin for alternating signals of LCD drive output.                                 |  |  |  |  |

|            |     | Segment output pins for LCD drive.                                                      |  |  |  |  |

|            | Ο   | According to the data of the display data,                                              |  |  |  |  |

|            |     | non-lighted at "0", lighted at "1" (Normal mode)                                        |  |  |  |  |

|            |     | non-lighted at "1", lighted at "0" (Reverse mode)                                       |  |  |  |  |

|            |     | and, by a combination of M signal and display data, one signal level among Vo, V2,      |  |  |  |  |

|            |     | V3, and Vss is selected.                                                                |  |  |  |  |

| SEG0-SEG79 |     | M Signal                                                                                |  |  |  |  |

|            |     | Display Data                                                                            |  |  |  |  |

|            |     | Normal ModeV2V0V3VssReverse ModeV0V2VssV3                                               |  |  |  |  |

| SYMBOL       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| COM0-COM15   | Ο   | Common output pins for LCD drive.         By a combination of the scanning data and M signal, one signal level among Vo, V1,         V4 and Vss is selected.         Data       M         H       H         V1         H       V1         H       L         V1         H       L         V2         V3         V4         V4                                |  |  |  |  |  |

| СОМІ         | Ο   | Common output pin for marker display.When executing duty + 1 (PLUS) command, it functions as a common output pin.Having two output pins for COMI, they output same level. It is able to select outputpin for COMI when wiring pattern.Duty + 1 ONDuty + 1 OFFCOMI stateCOM16 (when displaying 2 lines),<br>COM8 (when displaying 1 line)                    |  |  |  |  |  |

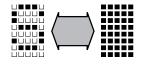

| COMS         | 0   | Common drive output pin for static LCD drive (for annunciator display).<br>Having two output pins for COMS, they output same level. It is able to select output pin for COMS when wiring pattern.<br>When DA = "0", outputs Vss level.                                                                                                                      |  |  |  |  |  |

| SEGS0-SEGS9  | 0   | Segment drive output pin for static LCD drive (for annunciator display).<br>One level is selected from VDD and Vss levels depending on the combination of COMS signal and display data.<br>When DA = "0", outputs Vss level.                                                                                                                                |  |  |  |  |  |

| SHL₀<br>SHL1 | I   | Input pin to control the transfer direction of the segment and common signal output data.<br>SHL0 = "0" : Segment data display direction is SEG0 to SEG79.<br>SHL0 = "1" : Segment data display direction is SEG79 to SEG0.<br>SHL1 = "0" : Common data display direction is COM0 to COM15.<br>SHL1 = "1" : Common data display direction is COM15 to COM0. |  |  |  |  |  |

## 1.5. Pins for Oscillation Circuit

| SYMBOL | I/O                                | DESCRIPTION                                                                            |  |  |  |

|--------|------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| OSCI   | I                                  | Foodbook registence connecting his for the internal coellation circuit                 |  |  |  |

| OSCO   | 0                                  | Feedback-resistance connecting pin for the internal oscillation circuit.               |  |  |  |

|        | Input pin of display master clock. |                                                                                        |  |  |  |

| СК     |                                    | When using CK pin as an input of the master clock, fix OSCI pin to Vss.                |  |  |  |

|        | I                                  | When using the internal oscillation circuit as the display master clock, fix CK pin to |  |  |  |

|        | Vss.                               |                                                                                        |  |  |  |

|        |                                    | Selection input pin of display master clock.                                           |  |  |  |

| CKS    | I                                  | CKS = "H" : Input the external clock to CK pin.                                        |  |  |  |

|        |                                    | CKS = "L" : The internal oscillation circuit by using OSCI and OSCO pins is used.      |  |  |  |

\* Master clock : Clock for oscillation circuit or external clock.

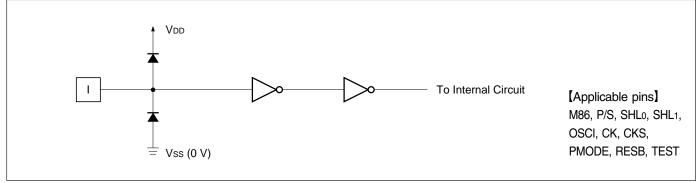

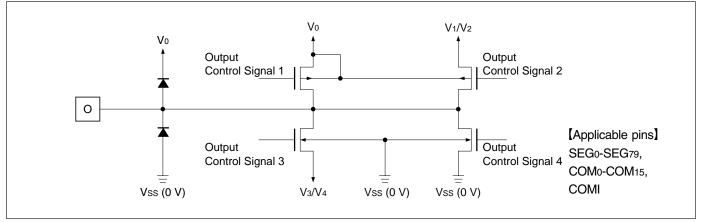

## 1.6. Input/Output Circuits

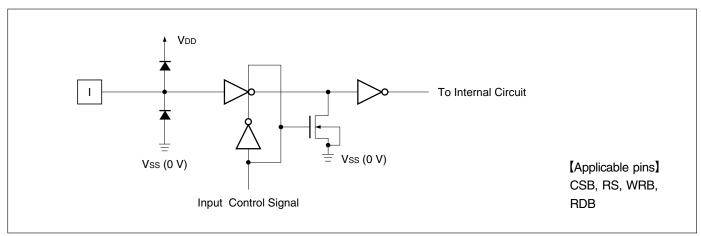

Fig. 1 Input Circuit (1)

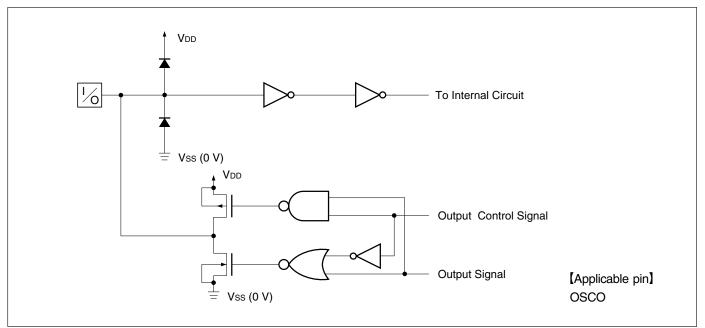

Fig. 2 Input Circuit (2)

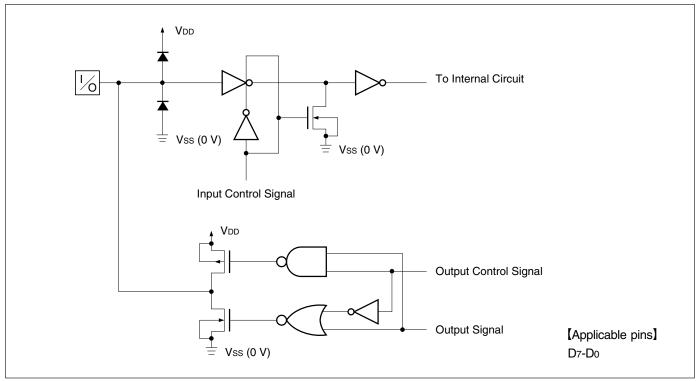

Fig. 3 Input/Output Circuit (1)

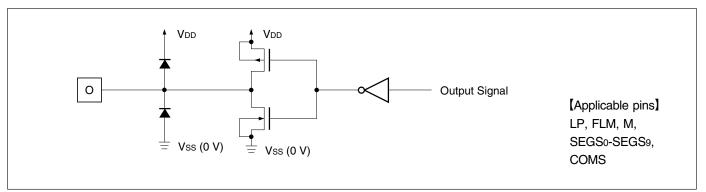

Fig. 4 Input/Output Circuit (2)

Fig. 5 Output Circuit

#### 2. FUNCTIONAL DESCRIPTION

#### 2.1. MPU Interface

#### 2.1.1. INTERFACE TYPE SELECTION

The LH1594/LH1595 transfer data through 8-bit parallel I/O (D7 to D0) or serial data input (SDA, SCL).

The selection between parallel interface and serial interface is made by setting the state of P/S pin to "H" or "L".

| P/S | I/F TYPE | CSB                        | RS   | RDB | WRB | M86 | SDA | SCL | DATA BUS |

|-----|----------|----------------------------|------|-----|-----|-----|-----|-----|----------|

| Н   | Parallel | CSB                        | RS   | RDB | WRB | M86 | _   | -   | D7 to D0 |

| L   | Serial   | – (LH1594)<br>CSB (LH1595) | ```' | -   | _   | _   | SDA | SCL | -        |

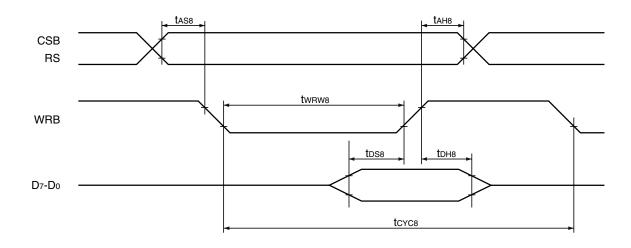

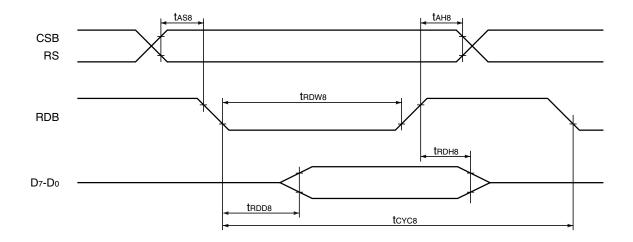

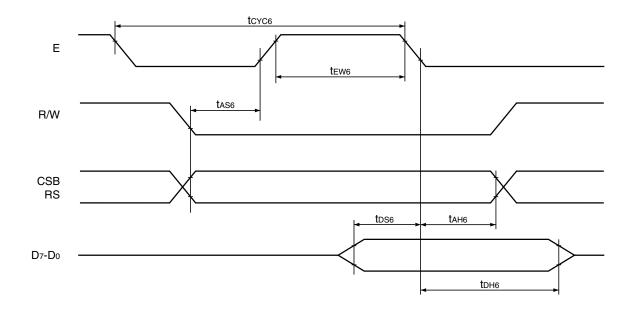

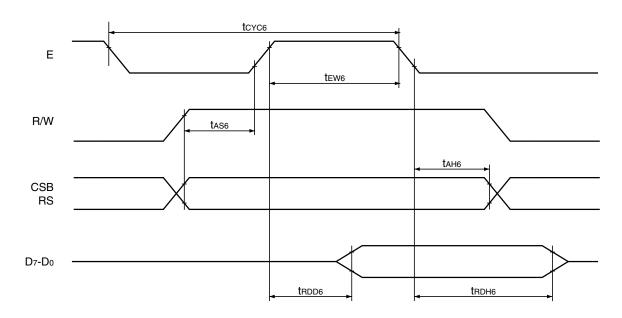

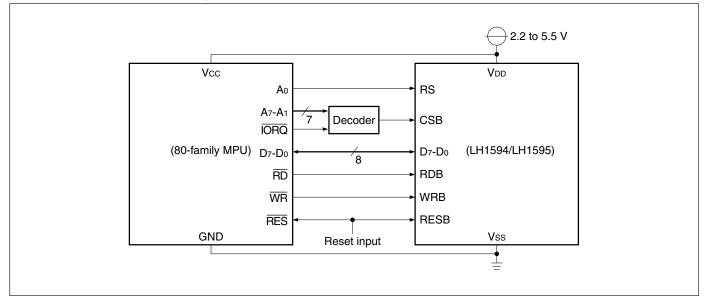

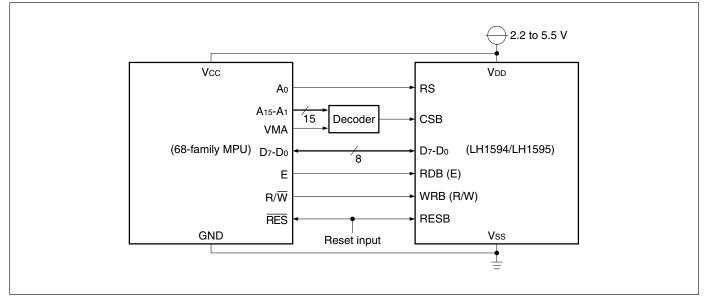

#### 2.1.2. PARALLEL INPUT

The LH1594/LH1595 can transfer data in parallel by directly connecting 8-bit MPU to the data bus when parallel interface is selected with P/S pin.

As an 8-bit MPU, either 80-family MPU interface or 68-family MPU interface is selected with M86 pin.

| M86 | MPU TYPE      | CSB | RS | RDB | WRB | DATA     |

|-----|---------------|-----|----|-----|-----|----------|

| Н   | 68-family MPU | CSB | RS | Е   | R/W | D7 to Do |

| L   | 80-family MPU | CSB | RS | RDB | WRB | D7 to Do |

#### 2.1.3. DATA IDENTIFICATION

The LH1594/LH1595 can identify the data of 8-bit data bus by combinations of RS, RDB and WRB signals.

| RS | 68-FAMILY | 80-FA | MILY | FUNCTION             |

|----|-----------|-------|------|----------------------|

| no | R/W       | RDB   | WRB  | FUNCTION             |

| 0  | 1         | 0     | 1    | Reads out busy flags |

| 0  | 0         | 1     | 0    | Writes to commands   |

| 1  | 1         | 0     | 1    | Reads from data RAM  |

| 1  | 0         | 1     | 0    | Writes to data RAM   |

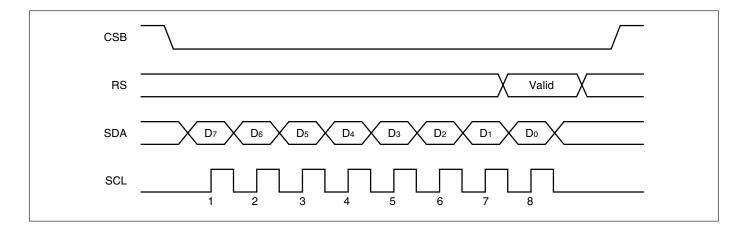

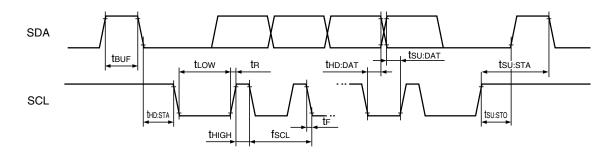

#### 2.1.4. SERIAL INTERFACE [FOR LH1594]

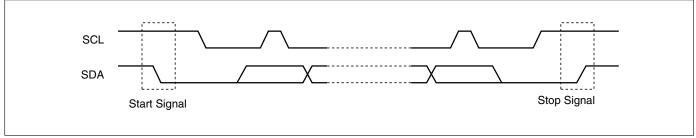

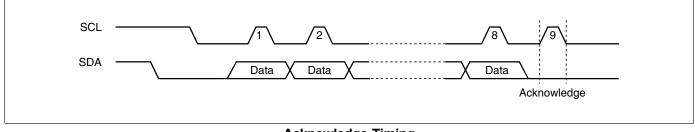

The serial interface for the LH1594 is  $I^2C$  BUS format.  $I^2C$  BUS is for bi-directional two-line communication between different ICs or other modules.

LH1594 always operates as a slave device, so sending data of start and stop is controlled by start/stop bits which are sent by master device.

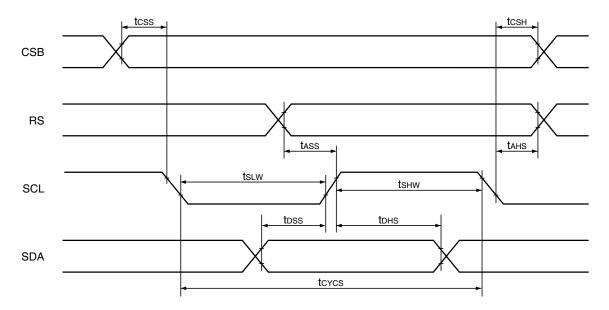

#### [FOR LH1595]

The serial interface of LH1595 can accept inputs of SDA and SCL in the chip selection state (CSB = "L"). When not in the chip selection state, the internal shift register and counter are reset to their initial condition.

Serial data SDA are input sequentially in order of D7 to D0 at the rising edge of serial clock (SCL) and are converted into 8-bit parallel data (by serial to parallel conversion) at the rising edge of the 8th serial clock, being processed in accordance with the data.

The identification whether the serial data inputs (SDA) are display data or commands is judged by input to RS pin.

RS = "H" : Display data

RS = "L" : Commands

After completing 8-bit data transferring, or when making no access, be sure to set serial clock input (SCL) to "L".

Protection of SDA and SCL signals against external noise should be taken in actual wiring. To prevent the successive recognition errors of transferring data from external noise, release the chip selection state (CSB = "H") at every completion of 8-bit data transferring.

#### 2.2. Busy Flag

When the busy flag is "1", this indicates that the LH1594/LH1595 are internally operating. In this state, the LH1594/LH1595 do not accept the next instruction. As shown in the command function table, the busy flag is output to the data bus D7 when RS is "0" or R/W is "1" (for the 68-family interface), and when RS is "0" or RDB is "0" (for the 80-family interface). The busy flag is generated only when the display clear command or the ACL command is executed. It must be confirmed that the busy flag is "0" before the next instruction can be executed.

#### 2.3. Address Counter (AC)

The address counter (AC) is used to address the DDRAM, CGRAM, or SEGRAM. When the addressing instruction is written into the AC, the address information is transferred to the AC. Simultaneously, the instruction also determines which RAM is to be selected among the DDRAM, CGRAM, and SEGRAM. After data is written into (read out from) the DDRAM, CGRAM, or SEGRAM, the AC is automatically counted up or down by one. As shown in the command function table, the AC outputs data to the data buses D6 to Do when RS is "0" and R/W is "1" (for the 68-family interface).

#### 2.4. Display Data RAM (DDRAM)

The DDRAM stores display data presented with 8bit character codes. Its capacity is 32 characters in a format of 8 bits.

#### 2.5. Character Generator ROM (CGROM)

The CGROM generates 240 different character patterns in a format of 5 x 8 dots from 8-bit character codes.

#### 2.6. Character Generator RAM (CGRAM)

The CGRAM allows user-written programs to freely overwrite characters. Eight different types of characters can be written in a format of 5 x 8 dots.

#### 2.7. Segment RAM (SEGRAM)

The SEGRAM allows user-written programs to freely control icons and marks. When the COMI outputs the selection signal, the data stored in the SEGRAM is read out to display 80 segments.

### 2.8. Timing Generation Circuit

The timing generation circuit generates the timing signals to operate the internal circuits, including the DDRAM, CGROM, CGRAM, and SEGRAM, as well as those for segment and common drive outputs. Readout of the display data to the LCD drive circuit is completely independent of MPU. Therefore, a MPU that has no relationship the read-out operation of the display data can access it.

## 2.9. Cursor Blinking Control Circuit

This circuit generates the cursor, the blinking cursor, or the reverse-display cursor. The cursor or the blinking cursor appears in the digit that corresponds to the address in the DDRAM which is specified in the address counter.

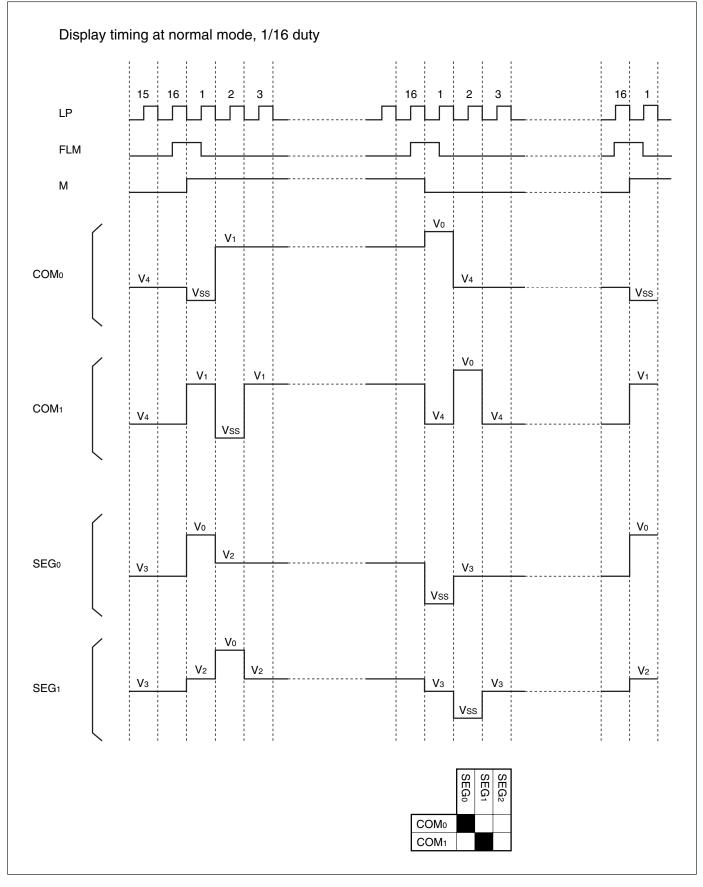

## 2.10. Output Timing of LCD Driver

#### 2.11. LCD Drive Circuit

This drive circuit generates 4 levels of LCD drive voltage. The circuit has 80 segment outputs and 17 common outputs and outputs combined display data and M signal. Character data is transferred by 80 bits from the CGROM or the CGRAM to the segment drive circuit.

One of the common outputs, COMI is for marker display only. A common drive circuit that has a shift register sequentially outputs common scan signals.

#### 2.12. Oscillation Circuit

The frequency of this CR oscillator is controlled by the feedback resistor RF.

The output from this oscillator is used as the timing signal source of the display and the boosting clock to the booster circuit.

If external clock is used, maintain OSCI pin at Vss and OSCO pin open (NC), and feed the clock to CK pin.

The duty cycle of the external clock must be 50%.

The CKS pin is used to select either internal oscillation circuit or external clock.

| CKS | <b>OSCILLATION CIRCUIT</b> | EXTERNAL CLOCK |

|-----|----------------------------|----------------|

| L   | Enabled                    | Disabled       |

| Н   | Disabled                   | Enabled        |

#### 2.13. Annunciator Circuit

This is the drive circuit which generates 2-value levels for static LCD drive. This circuit provides displaying annunciators for icons or marks. It consists of common drivers (COMS x 2) and 10 segment drivers (SEGS0 to SEGS9). One level is selected from VDD and Vss levels for static LCD drive. When this circuit is not displaying annunciator, it outputs Vss level.

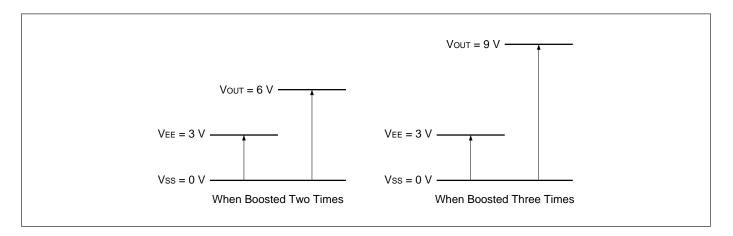

#### 2.14. Power Supply Circuit

This circuit supplies voltages necessary to drive an LCD. The circuit consists of booster circuit and voltage converter.

Boosted voltage from the booster circuit is fed to

the voltage converter which converts this high input voltage into V<sub>0</sub>, V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>4</sub> which are used to drive the LCD.

This internal power supply should not be used to drive a large LCD panel containing many pixels or a large LCD panel that has large capacity consisting of more than one chip. Otherwise, display quality will degrade considerably. Instead, use an external power supply.

This internal power supply is controlled by the power supply circuit ON/OFF command (PON).

When the internal power supply is turned off, the booster circuit and voltage converter are also turned off.

When using the external power supply, turn off the internal power supply, disconnect pins CAP1+, CAP1-, CAP2+, CAP2-, VOUT, VEE, VR1 and VR2, and keep PMODE pin at Vss. Then, feed external LCD drive voltages to pins V0, V1, V2, V3 and V4.

This circuit can be changed by the state of PMODE pin.

|     | PMODE | BOOSTER  | VOLTAGE   | EXTERNAL           | NOTE |  |

|-----|-------|----------|-----------|--------------------|------|--|

| PUN |       | CIRCUIT  | CONVERTER | VOLTAGE INPUT      | NOTE |  |

| 0   | 0     | Disabled | Disabled  | V0, V1, V2, V3, V4 | 1    |  |

| 0   | 1     | Disabled | Disabled  | V0, V1, V2, V3, V4 | 1    |  |

| 1   | 0     | Enabled  | Enabled   | _                  |      |  |

| 1   | 1     | Disabled | Enabled   | Vout, Vr1, Vr2     | 2    |  |

#### NOTES :

Because the booster circuit and voltage converter are not functioning, disconnect pins CAP1+, CAP1-, CAP2+, CAP2-, VOUT, VEE, VR1, and VR2.

Apply external LCD drive voltages to corresponding pin.

Because the booster circuit is not functioning, disconnect pins CAP1+, CAP1-, CAP2+, CAP2- and VEE.

Derive the voltage source to be supplied to the voltage converter from Vout pin and then output LCD drive voltage to VR1, and VR2 pins. The voltage level at VR1 and VR2 pins must be VR2 ≤ VR1 ≤ Vout.

#### 2.15. Booster Circuit

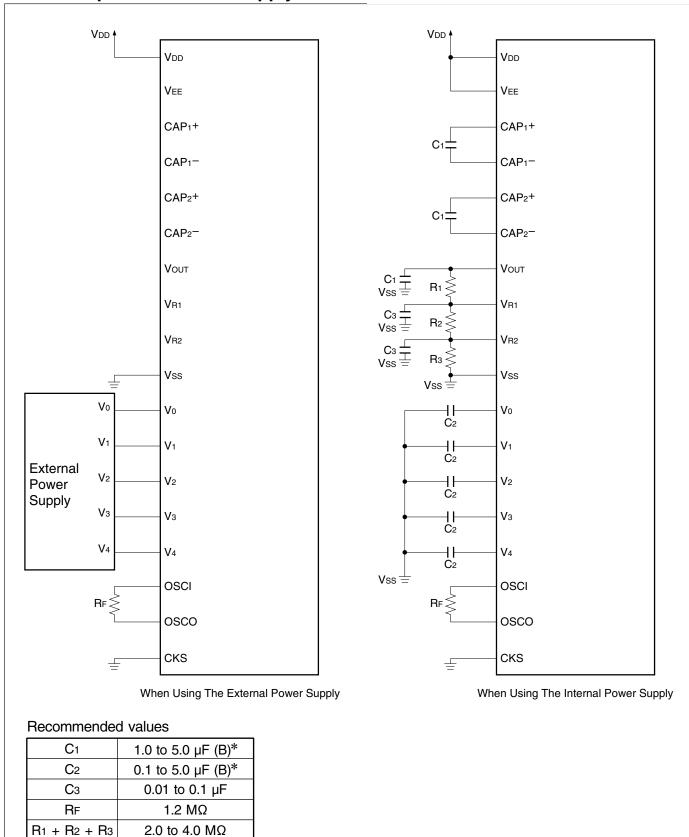

Placing capacitor C1 across CAP1+ and CAP1and across CAP2+ and CAP2- and across VOUT and Vss boosts the voltage coming from VEE and Vss three times and outputs the boosted voltage to VOUT pin.

Placing C1 across CAP1+ and CAP1- and shorting together pins CAP1+ and CAP2+ limits the output on VOUT pin to two times the input voltage.

Since the booster circuit uses the clock derived

from the internal oscillation circuit or external clock as the boosting clock, the internal oscillation circuit must be enabled, or if external clock is selected, it must be fed to CK pin.

The output level at the VOUT pin does not exceed the recommended maximum operating voltage (11.0 V) when the voltage is boosted. If this value is exceeded, the operation of the LH1594/LH1595 are not covered by warranty.

#### 2.16. Voltage Control Circuit

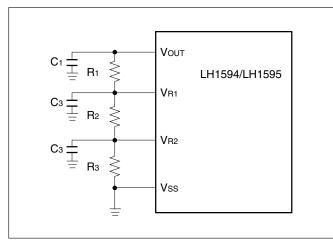

The boosted voltage at the VOUT pin is connected to the VR1 and VR2 pins and then the LCD drive voltages (V0, V1, V2, V3, and V4) are generated via the voltage converter circuit. The input level at the VR1 and VR2 must meet the electric potential condition of VR1  $\geq$  VR2. The internal electronic volume divides the electric potential between the VR1 and VR2 into 16 segments.

Since the VR1 and VR2 pins have high input impedance, the input voltage levels at the VR1 and VR2 are determined by the resistance ratio of R1, R2, and R3. The current flowing between the VOUT and VSS pins is determined by the combined resistance of R1, R2, and R3.

Therefore, R1, R2, and R3 must be selected in accordance with the above current as well as the input voltage levels at the VR1 and VR2.

The boosted voltage at the VOUT pin originates from the voltage supplied at the VEE pin.

Thus, the DC path current generated with R1, R2, and R3 connected between the VOUT and Vss pins is supplied as current at the VEE pin. The electric current value, three times larger than the DC path current generated between the VOUT and Vss pins when the voltage is tripled, is added as supply current at the VEE pin (two times larger current is added for doubled voltage). Take sufficient care that the input levels at the VR1 and VR2 pins do not fluctuate with external noise (connect capacitor C3).

**Example of Voltage Control Circuit**

#### 2.17. Electronic Volume

The voltage converter incorporates an electronic volume, which allows the LCD drive voltage level Vo to be controlled with a command and also allows the tone of LCD to be controlled.

If 4-bit data is stored in the register of the electronic volume, one level can be selected among 16 voltage values for the LCD drive voltage V<sub>0</sub>.

The voltage control range of the electronic volume is determined by the input voltage levels at the VR1 and VR2. This means that the voltage range of (VR1 to VR2) is the controllable voltage range of the electronic volume. The electric potential relation between the VR1 and VR2 pins must be VR1  $\geq$  VR2. The input voltage levels at the VR1 and VR2 pins must be selected in accordance with the voltage levels to be obtained with the electronic volume.

#### 2.18. LCD Drive Voltage Generation Circuit

The voltage converter contains the voltage generation circuit. The LCD drive voltages other than Vo, that is, V1, V2, V3 and V4, are obtained by dividing Vo through a resistor network. The LCD drive voltages from LH1594/LH1595 are biased at 1/4 or 1/5.

When using the internal power supply, connect a stabilizing capacitor C<sub>2</sub> to each of pins V<sub>0</sub> to V<sub>4</sub>.

The capacitance of C<sub>2</sub> should be determined while observing the LCD panel to be used. In this case, connect a capacitor C<sub>3</sub> to stabilize input voltage to VR1 and VR2. A value of C<sub>3</sub> can be defined selectively.

## 2.19. Example of Power Supply Circuit

\* B characteristics must be used with C1 and C2.

#### 2.20. Initialization

The LH1594/LH1595 are initialized by setting RESB pin to "L". Normally, RESB pin is initialized together with MPU by connecting to the reset pin of MPU. When power is ON, be sure to reset operation.

| PARAMETER              | PIN DESCRIPTION                             |

|------------------------|---------------------------------------------|

| Function               | RE = 0 : Writes to expanded                 |

|                        | register disabled.                          |

|                        | BE = 0 : SEGRAM blink OFF                   |

|                        | DUB = 0 : Normal display mode               |

|                        | (Displaying double                          |

|                        | fonts lengthwise OFF)                       |

|                        | BT = 0 : Blinking type is normal/           |

|                        | reverse display.                            |

| Entry mode             | I/D = 1 : Increments by one.                |

|                        | S = 0 : No shift occurs.                    |

| Display mode           | NL = 0 : Displays 2 lines.                  |

| Display control (1)    | D = 0 : Display OFF                         |

|                        | C = 0 : Cursor OFF                          |

|                        | B = 0 : Blink OFF                           |

| Display control (2)    | PLUS = 0 : 1/16 duty                        |

|                        | REV = 0 : Normal display                    |

|                        | ALON = 0 : Normal display                   |

| Power control          | HALT = 0 : Power saving OFF                 |

|                        | PON = 0: Power supply circuit OFF           |

|                        | ACL = 0 : ACL operation OFF                 |

|                        | BIAS : 1/5 bias                             |

| Register in electronic | (1, 1, 1, 1)                                |

| volume                 |                                             |

| Annunciator control    | DA = 0 : Annunciator display                |

|                        | OFF                                         |

|                        | I0 to $I9 = (0, 0, 0, 0, 0, 0, 0, 0, 0, 0)$ |

| RAM data               | DDRAM : Not determined.                     |

|                        | CGRAM : Not determined.                     |

|                        | SEGRAM : Not determined.                    |

#### **3. PRECAUTIONS**

## Precautions when connecting or disconnecting the power supply

This IC may be permanently damaged by a high current which may flow if voltage is supplied to the LCD drive power supply while the logic system power supply is floating. The details are as follows.

- ① When using an external power supply

- When connecting the power supply After connecting the logic system power supply, make reset operation and then apply external LCD drive voltages to corresponding pins. (Vo, V1, V2, V3, V4 or VOUT, VR1 and VR2)

- When disconnecting the power supply After executing HALT command, disconnect external LCD drive voltages and then disconnect the logic system power supply.

- 2 When using the internal power supply

- When connecting the power supply After connecting the logic system power supply, make reset operation and then execute PON command.

- When disconnecting the power supply After executing HALT command, disconnect the logic system power supply.

It is advisable to connect the serial resistor (50 to 100  $\Omega$ ) or fuse to the LCD drive power VOUT or Vo of the system as a current limiter. Set up a suitable value of the resistor in consideration of the display grade.

## 4. COMMAND FUNCTION

Since the instructions for the LH1594/LH1595 are executed within execution cycle time, the MPU can be operated at a high speed without a waiting time.

The busy state check is only necessary when the display clear command or the ACL command is executed.

## 4.1. Command Function Table

| INSTRUCTION             |      | INSTRUCTION CODE |    |    |    |       |       |      |          | DESCRIPTION |                                               |  |

|-------------------------|------|------------------|----|----|----|-------|-------|------|----------|-------------|-----------------------------------------------|--|

| INSTRUCTION             | RE   | RS               | D7 | D6 | D5 | D4    | Dз    | D2   | D1       | Do          | DESCRIPTION                                   |  |

| RAM data write          | 0/1  | 1                |    |    | ١  | NRITE | E DAT | 4    |          |             | Writes to data RAM.                           |  |

| RAM data read           | 0/1  | 1                |    |    |    | READ  | DATA  | Ą    |          |             | Reads from data RAM.                          |  |

| Display clear set       | 0/1  | 0                | 0  | 0  | 0  | 0     | 0     | 0    | 0        | 1           | Specifies address 0 from DDRAM                |  |

|                         | 0/1  | 0                | 0  | 0  |    |       |       |      |          | •           | in AC after clearing all display.             |  |

| Cursor home set         | 0/1  | 0                | 0  | 0  | 0  | 0     | 0     | 0    | 1        | *           | Allocates address 0 for DDRAM                 |  |

|                         | 0/1  | 0                | 0  | 0  |    |       |       |      | <b>'</b> |             | in AC and resets shifted display.             |  |

| Entry mode set          | 0    |                  |    |    |    |       |       |      | I/D      | s           | Specifies cursor moving direction             |  |

|                         | •    | 0                | 0  | 0  | 0  | 0     | 0     | 1    |          |             | and whether or not to shift display.          |  |

| Display mode set        | 1    |                  |    |    |    |       |       |      | *        | NL          | Sets display 2 lines or 1 line (NL).          |  |

|                         |      |                  |    |    |    |       |       |      |          |             | Turns ON/OFF all display (D). Turns           |  |

| Display control (1) set | 0    |                  |    |    |    |       |       | D    | С        | В           | ON/OFF cursor (C). Specifies blinking         |  |

|                         |      | 0                | 0  | 0  | 0  | 0     | 1     |      |          |             | character indicated by cursor (B).            |  |

|                         |      | Ŭ                | Ŭ  | Ū  |    |       |       |      |          |             | Specifies duty + 1 (PLUS).                    |  |

| Display control (2) set | 1    |                  |    |    |    |       |       | PLUS | REV      | ALON        | Displays data in reverse display (REV).       |  |

|                         |      |                  |    |    |    |       |       |      |          |             | Turns ON all display (ALON).                  |  |

| Cursor/display shift    | 0    |                  |    |    |    |       | S/C   | R/L  | *        | *           | Moves cursor and shifts display               |  |

| set                     | 0    |                  |    |    |    |       | 0,0   |      | •••      |             | without changing data in DDRAM.               |  |

|                         |      | 0                | 0  | 0  | 0  | 1     |       |      |          |             | Specifies HALT ON (HALT).                     |  |

| Power control set       | 1    | Ŭ                | Ū  | Ū  |    |       | BIAS  | HALT | PON      | ACI         | Turns ON power supply circuit (PON).          |  |

|                         |      |                  |    |    |    |       |       |      |          |             | Specifies resetting (ACL).                    |  |

|                         |      |                  |    |    |    |       |       |      |          |             | Sets bias ratio (BIAS).                       |  |

|                         |      |                  |    |    |    |       |       |      |          |             | Enables writes to expanded register (RE).     |  |

| Function set            | 0/1  | 0                | 0  | 0  | 1  | BE    | DUB   | RE   | вт       | *           | Enables blinking for SEGRAM (BE).             |  |

|                         | 0, 1 | Ŭ                | Ū  | Ū  |    |       |       |      |          |             | Enables display double font lengthwise (DUB). |  |

|                         |      |                  |    |    |    |       |       |      |          |             | Sets blinking character type (BT).            |  |

| CGRAM address set       | 0    | 0                | 0  | 1  |    |       | AC    | CG   |          |             | Sets CGRAM address.                           |  |

| SEGRAM address set      | 1    |                  |    |    | *  | *     |       |      | EG       |             | Sets SEGRAM address.                          |  |

| DDRAM address set       | 0    | 0                | 1  | 0  | *  |       |       | ADD  |          |             | Sets DDRAM address.                           |  |

| Electronic volume set   | 1    |                  | •  |    | *  | *     |       |      | OL       |             | Sets electronic volume.                       |  |

| Annunciator control     | 0    | 0                | 1  | 1  | 15 | l4    | 13    | 12   | 1        | 10          | ( , ,                                         |  |

| set                     | 1    | -                | -  | •  | DA | *     | 19    | 18   | 17       | 16          | Enables display annunciator (DA).             |  |

| Busy flag/address       | 0/1  | 0                | BF | *  |    |       | А     | С    |          |             | Reads out busy flag and data                  |  |

| read                    |      | -                |    |    |    |       |       | -    |          |             | from AC.                                      |  |

\* mark means "Don't care".

#### 4.2. Write Data to RAM

| RE  | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|-----|----|----|----|----|----|----|----|----|----|

| 0/1 | 1  | D  | D  | D  | D  | D  | D  | D  | D  |

Writes binary 8-bit data D7 to D0 to the CGRAM or DDRAM or SEGRAM.

The RAM is to be written into is determined by the previous specification of CGRAM or DDRAM or

4.3. Read Data to RAM

| RE  | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|-----|----|----|----|----|----|----|----|----|----|

| 0/1 | 1  | D  | D  | D  | D  | D  | D  | D  | D  |

Reads binary 8-bit data D7 to D0 from the CGRAM or DDRAM or SEGRAM.

The most recent set address command determines the RAM is to be read. After writing, the address

#### 4.4. Display Clear Register Set

| <br> |    |    |    |    |    |    |    |    |    |

|------|----|----|----|----|----|----|----|----|----|

| RE   | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

| 0/1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

Space code "20H" (for 32 characters) is written to all addresses in the DDRAM. The address counter specifies DDRAM address 0.

If the display is shifted, it is reset in place. This means that the display is cleared and the cursor or blinking cursor, if displayed, returns to the left end in the first line.

Set the I/D of the increment mode to "Increment". "S" will not change. When the clearing of the display starts, the busy flag is generated. Therefore, to execute an instruction after clearing the display, monitor the busy flag and then execute the next instruction after checking that the flag has been released; or allow a waiting period of 34 times the master clock frequency.

#### 4.5. Cursor Home Register Set

| RE  | RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | Do |

|-----|----|----|----|----|----|----|----|----|----|

| 0/1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | *  |

\* mark means "Don't care".

Specify DDRAM address 0 in the address counter. If the display is shifted, it is reset in place. The data in the DDRAM remains unchanged. The cursor or the blinking cursor, if displayed, returns to the left end in the first line.

D2

D1

D0

D

D

D

automatically increments or decrements by 1, in

SEGRAM address setting. After writing, the address

automatically increments or decrements by 1, in

accordance with the entry mode.

accordance with the entry mode.

#### 4.6. Entry Mode Register Set

|    |    | U  |    |    |    |    |    |     |    |

|----|----|----|----|----|----|----|----|-----|----|

| RE | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1  | Do |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | I/D | S  |

When the extended register enable bit (RE) is "0", the following I/D, and S bits are accessed :

- I/D : When any character code is written into or read out from the DDRAM, the DDRAM address is shifted by +1 (I/D = 1) or -1 (I/D = 0). In case of +1, the cursor or the blinking cursor moves to the right. This is also applicable when any data is written into or read out from the CGRAM or SEGRAM.

- S : If S = 1, the entire display is shifted to either the left or right when any character code is written into the DDRAM. If I/D = 1, the entire display is

shifted to the left; or if I/D = 0, the entire display is shifted to the right. Therefore, if I/D = 1, the cursor looks stationary with only the display shifted. When any character code is read out from the DDRAM, the display is not shifted. If S =0, the display remains unshifted. When any data is written into or read out from the CGRAM or SEGRAM, the display also remains unshifted.

When duty + 1 command is ON (PLUS = 1), if S = 1 and any code is written into DDRAM, the line that COMI scans is also shifted, so that this command is allowed only when duty + 1 command is OFF (PLUS = 0) state.

#### 4.7. Display Mode Register Set

| RE | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|----|----|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | *  | NL |

\* mark means "Don't care".

When the extended register enable bit (RE) is "1", the following NL bit is accessed :

NL : This command selects the displaying lines.

NL = "0" : Displays 2 lines. Display duty ratio is 1/16.

NL = "1" : Displays 1 line. Display duty ratio is 1/8.

#### 4.8. Display Control (1) Register Set

| -  |    | •  |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|

| RE | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | D  | С  | В  |

When the extended register enable bit (RE) is "0", the following D, C, and B bits are accessed :

- D : Turns ON the display if D = 1; or turns OFF the display if D = 0. Since the data in the DDRAM is retained, the display can be resumed by specifying D = 1.

- C : Displays the cursor if C = 1; or hides the cursor if C = 0. Even if the cursor is hidden, I/D and other features remain

#### 4.9. Display Control (2) Register Set

unchanged when the display data is written. The cursor is shown with 5 dots in the 8th line.

B : Blinks the character in the cursor position if B = 1. This blinking turns ON/OFF all dots displayed in reverse. The blinking frequency is 300 ms when fosc = 55 kHz and displays 2 lines. This value varies in proportion to the inverse number of fosc.

| _ |    |    |    | /  |    |    |    |      |     |      |

|---|----|----|----|----|----|----|----|------|-----|------|

|   | RE | RS | D7 | D6 | D5 | D4 | Dз | D2   | D1  | Do   |

|   | 1  | 0  | 0  | 0  | 0  | 0  | 1  | PLUS | REV | ALON |

When the extended register enable bit (RE) is "1", the PLUS, REV, and ALON bits are accessed. Once the specified values are stored in this register, they are retained even if the RE bit is set to "0".

- PLUS : Specifies "duty + 1". Toggles the display duty. The COMI pin functions as the COM8 (when displaying 1 line) or COM16 (when displaying 2 lines) for marker. When the COMI is scanned, the data in the SEGRAM is output as display data from the segment driver.

- PLUS = "0" : Sets the display duty to 1/8 (when displaying 1 line) or 1/16 (when displaying 2 lines).

- PLUS = "1" : Sets the display duty to 1/9 (when displaying 1 line) or 1/17 (when displaying 2 lines).

REV : Toggles between normal and reverse videos for display.

REV = "0" : Normal video

REV = "1" : Reverse video

ALON : Toggles between normal and fully lit-up displays regardless the data type in the DDRAM. The setting of this bit takes priority over that of REV. ALON = "0" : Normal display

ALON = "1" : Fully lit-up display

#### 4.10. Cursor/Display Shift Register Set

| RE | RS | D7 | D6 | D5 | D4 | Dз  | D2  | D1 | Do |

|----|----|----|----|----|----|-----|-----|----|----|

| 0  | 0  | 0  | 0  | 0  | 1  | S/C | R/L | *  | *  |

|    |    |    |    |    |    |     |     |    |    |

\* mark means "Don't care".

When the extended register enable bit (RE) is "0", the following S/C and R/L bits may be set.

The cursor position or the display is shifted to the left or right without writing the display data or reading it out. This may be used to modify or search the display. The cursor movement from the 1st to 2nd line occurs after the 16th digit in the 1st line. Note that all the lines are shifted simultaneously.

When duty + 1 command is ON (PLUS = 1), if S = 1 and any code is written into DDRAM, the line that COMI scans is also shifted, so that this command is allowed only when duty + 1 command is OFF (PLUS = 0) state.

| S/C | R/L | ACTION                                                              |

|-----|-----|---------------------------------------------------------------------|

| 0   | 0   | Shifts cursor to left (counts down the AC by one).                  |

| 0   | 1   | Shifts cursor to right (counts up the AC by one).                   |

| 1   | 0   | Shifts entire display to left. Cursor moves as display is shifted.  |

| 1   | 1   | Shifts entire display to right. Cursor moves as display is shifted. |

If only the display shift is made, the address counter (AC) remains unchanged.

#### 4.11. Power Control Register Set

|    |    |    | -  |    |    |      |      |     |     |

|----|----|----|----|----|----|------|------|-----|-----|

| RE | RS | D7 | D6 | D5 | D4 | Dз   | D2   | D1  | Do  |

| 1  | 0  | 0  | 0  | 0  | 1  | BIAS | HALT | PON | ACL |

BIAS : This command selects the displaying bias ratio. BIAS = "0" : 1/5 bias

BIAS = "1" : 1/4 bias

HALT : Turns ON/OFF the power saving mode. When the LH1594/LH1595 enter the power saving mode, the supply current can be reduced to nearly the standby current value.

HALT = "0" : Normal mode

HALT = "1" : Power saving mode

The internal state in the power saving mode is described below.

• The oscillation and power circuits are stopped.

- The LCD drive is disabled. The output from the segment and common drivers are made at the Vss level.

- The clock input at the CK pin is inhibited.

- PON : Turns ON/OFF the internal power supply circuit.

- PON = "0" : Turns OFF the power supply circuit.

- PON = "1" : Turns ON the power supply circuit.

The booster circuit and the voltage converter become active when the power supply circuit is turned on. The operating section in the circuits varies depending on the setting of the PMODE pin. See **Table in Section 2.14.** for details.

ACL : The internal circuit can be initialized.

ACL = "0" : Normal mode.

ACL = "1" : ACL operation is ON.

When the ACL command is turned on, the busy flag is generated. Therefore, to execute an instruction after ACL

operation, monitor the busy flag and then execute the next instruction after checking that the flag has been released; or allow a waiting period of 2 times the master clock frequency.

#### 4.12. Function Register Set

| RE  | RS | D7 | D6 | D5 | D4 | Dз  | D2 | D1 | Do |

|-----|----|----|----|----|----|-----|----|----|----|

| 0/1 | 0  | 0  | 0  | 1  | BE | DUB | RE | BT | *  |

|     |    |    |    |    |    | •   |    |    |    |

\* mark means "Don't care".

- RE : This bit is the enable bit for extended register. If RE = "1", the extended function setting can be accessed. When setting instruction, it is necessary to follow the state of RE bit. (refer to "INSTRUCTION CODE" in section 4.1..) RE bit consists of register, once the specified value is stored in this register, it is retained the value.

- BE : When BE = "1", the information which is stored in the SEGRAM using its upper 2

bits is used to allow for blinking the display data from the SEGRAM.

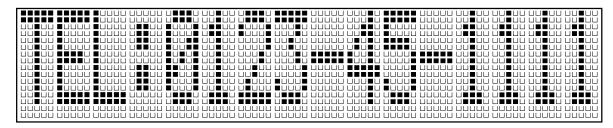

DUB : This bit is toggled the display double fonts lengthwise.

DUB = "0" : Displays normal mode.

DUB = "1" : Displays double fonts lengthwise. **NOTES :**

- Double fonts lengthwise can display only first line.

- Not using these setting, when displaying 1 line mode. (NL = 1)

Example of Display (DUB = "1")

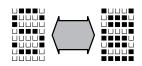

- BT : This command selects the character blinking type.

- BT = "0" : Displaying normal/reverse per 32 frames.

Example of Display (BT = "0")

Example of Display (BT = "1")

#### 4.13. CGRAM Address Register Set

| RE | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|----|----|----|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 1  | А  | А  | А  | А  | А  | А  |

If the extended register enable bit (RE) is "0", CGRAM addresses may be specified.

In the above example, the address shown in binary

#### 4.14. SEGRAM Address Register Set

| RE  | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|-----|----|----|----|----|----|----|----|----|----|

| 1   | 0  | 0  | 1  | *  | *  | А  | А  | А  | А  |

| . I |    |    |    |    |    |    |    |    |    |

\* mark means "Don't care".

If the extended register enable bit (RE) is "1", SEGRAM addresses may be specified.

The SEGRAM address shown in binary number for

#### 4.15. DDRAM Address Register Set

| RE | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|----|----|----|----|----|----|----|----|----|----|

| 0  | 0  | 1  | 0  | *  | Α  | А  | А  | А  | Α  |

|    |    |    |    |    |    |    |    |    |    |

\* mark means "Don't care".

If the extended register enable bit (RE) is "0", DDRAM addresses may be specified.

The DDRAM address shown in binary number for

"AAAAA" is allocated in the address counter. Subsequently data is written into or read from the MPU in reference to the DDRAM.

#### 4.16. Electronic Volume Register Set

| RE | RS | D7 | D6 | D5 | D4 | Dз  | D2    | D1 | Do  |

|----|----|----|----|----|----|-----|-------|----|-----|

| 1  | 0  | 1  | 0  | *  | *  | MSB | ••••• |    | LSB |

\* mark means "Don't care".

The LCD drive voltage V<sub>0</sub> output from the internal power supply circuit can be controlled and the display tone on the LCD can be also controlled.

The LCD drive voltage V<sub>0</sub> takes one out of 16 voltage values by setting 4-bit data register.

If the electronic volume is not used, specify (1, 1, 1, 1) in the 4-bit data register. After the LH1594/LH1595 are reset, the 4-bit data register is automatically set to (1, 1, 1, 1).

| MSB |   | ••••• | LSB | Vo      |

|-----|---|-------|-----|---------|

| 0   | 0 | 0     | 0   | Smaller |

|     |   |       |     |         |

| 1   | 1 | 1     | 1   | Larger  |

Downloaded from <u>Elcodis.com</u> electronic components distributor

"AAAA" is allocated in the address counter. Subsequently data is written into or read from the MPU in reference to the SEGRAM.

number for "AAAAAA" is allocated in the address

counter. Subsequently data is written into or read

from the MPU in reference to the CGRAM.

#### 4.17. Annunciator Control Register Set

| RE | RS | D7 | D6 | D5 | D4         | Dз | D2 | D1 | Do |

|----|----|----|----|----|------------|----|----|----|----|

| 0  | 0  | 4  | 4  | l5 | <b>I</b> 4 | 13 | 12 | 1  | 10 |

| 1  | 0  | I  | Ι  | DA | *          | 19 | 18 | I7 | 16 |

\* mark means "Don't care".

- I0 to I9 : These bits are setting data for annunciator. Io to I9 correspond to SEGS0 to SEGS9 for static LCD drive outputs.

- DA : When DA = "1", output pin for static LCD drive (for annunciator display). One level is selected from VDD and Vss levels depending on the combination of COMS signal and display data (I0 to I9). When DA = "0", outputs Vss level.

Example of Outputs for Annunciator (DA = "1", I0 = "0", I1 = "1")

#### 4.18. Busy Flag/Address Read

| RE   | RS | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|------|----|----|----|----|----|----|----|----|----|

| 0/1  | 0  | BF | *  | А  | Α  | A  | A  | A  | А  |

| <br> |    |    | "  |    |    |    |    |    |    |

\* mark means "Don't care".

"BF = 1" indicates that the LH1594/LH1595 are internally operating and the next instruction is not accepted until "BF = 0".

The busy flag is only generated when the display is cleared or the ACL command is executed. Therefore, any other instruction can be executed without monitoring the busy flag. Simultaneously, the address counter value presented in binary number for "AAAAAA" is read out. The address counter is used by the DDRAM, CGRAM, and SEGRAM. The data read out from the RAMs is determined by specifying a command before reading out.

## 4.19. Example of Instructions vs. Display

|     |      | -          | I     | NST        | RUC        | TION | 1  |    |    |            |                                               |

|-----|------|------------|-------|------------|------------|------|----|----|----|------------|-----------------------------------------------|

| NO. | RS   | <b>D</b> 7 | D6    | <b>D</b> 5 | <b>D</b> 4 | D3   | D2 | D1 | D0 | DISPLAY    | ACTION                                        |

| 1   | Pow  | /er C      | N     |            |            |      |    |    |    |            | No display appears.                           |

| -   |      |            |       |            |            |      |    |    |    |            |                                               |

| 2   |      | ction      |       |            |            |      |    |    |    |            | "0" is written to RE bit.                     |

|     | 0    | 0          | 0     | 1          | *          | *    | 0  | 0  | *  |            |                                               |

| 3   |      | olay o     |       |            |            |      |    |    |    |            | Display is cleared.                           |

|     | 0    | 0          | 0     | 0          | 0          | 0    | 0  | 0  | 1  |            |                                               |

| 4   | -    |            |       | DFF (      |            | ol   |    |    |    |            | Turns ON display and cursor. If display is    |

|     | 0    | 0          | 0     | 0          | 0          | 1    | 1  | 1  | 0  | -          | cleared, display is filled with blank spaces. |

| 5   | Entr | y mo       | ode s | set        |            |      |    |    |    |            | Counts up address by one and moves            |

| 5   | 0    | 0          | 0     | 0          | 0          | 0    | 1  | 1  | 0  | -          | cursor to right when data is written to RAM.  |

| 6   | DDF  | RAM        | data  | ı writ     | е          |      |    |    |    | S_         | Writes "S".                                   |

| 0   | 1    | 0          | 1     | 0          | 1          | 0    | 0  | 1  | 1  | o_         | Willes 3.                                     |

| 7   |      |            |       |            | :          |      |    |    |    |            |                                               |

| 1   |      |            |       |            | :          |      |    |    |    |            |                                               |

| 8   | DDF  | RAM        | data  | ı writ     | е          |      |    |    |    | SHARP_     | Writes "P".                                   |

| 0   | 1    | 0          | 1     | 0          | 1          | 0    | 0  | 0  | 0  |            | Willes T.                                     |

| 9   | DDF  | RAM        | add   | ress       | set        |      |    |    |    | SHARP      | Sets DDRAM address so that cursor is          |

| 9   | 0    | 1          | 0     | *          | 1          | 0    | 0  | 0  | 0  | _          | positioned at the top of 2nd line.            |

| 10  | DDF  | RAM        | data  | ı writ     | е          |      |    |    |    | SHARP      | Writes "L".                                   |

| 10  | 1    | 0          | 1     | 0          | 0          | 1    | 1  | 0  | 0  | L_         |                                               |

| 11  |      |            |       |            | :          |      |    |    |    |            |                                               |

|     |      |            |       |            | :          |      |    |    |    |            |                                               |

| 12  | DDF  | RAM        | data  | ı writ     | е          |      |    |    |    | SHARP      | Writes "R".                                   |

| 12  | 1    | 0          | 1     | 0          | 1          | 0    | 0  | 1  | 0  | LCDDRIVER_ |                                               |

| 13  |      |            |       |            | :          |      |    |    |    |            |                                               |

| 10  |      |            |       |            | :          |      |    |    |    |            |                                               |

| 14  | Cur  | sor h      | ome   |            |            |      |    |    |    | SHARP      | Resets both display and cursor in place       |

| 14  | 0    | 0          | 0     | 0          | 0          | 0    | 0  | 1  | *  | LCDDRIVER  | (address 0).                                  |

\* mark means "Don't care".

## **5. CONFIGURATION OF CGROM**

Character codes vs. character patterns

| Low | order | High order |  |

|-----|-------|------------|--|

|     |       |            |  |

|     |       |            |  |

|          | 0000             | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|----------|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| XXXX0000 | CG<br>RAM<br>(1) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0001 | CG<br>RAM<br>(2) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0010 | CG<br>RAM<br>(3) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0011 | CG<br>RAM<br>(4) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0100 | CG<br>RAM<br>(5) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0101 | CG<br>RAM<br>(6) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0110 | CG<br>RAM<br>(7) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX0111 | CG<br>RAM<br>(8) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1000 | CG<br>RAM<br>(1) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1001 | CG<br>RAM<br>(2) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1010 | CG<br>RAM<br>(3) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1011 | CG<br>RAM<br>(4) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1100 | CG<br>RAM<br>(5) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1101 | CG<br>RAM<br>(6) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1110 | CG<br>RAM<br>(7) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| XXXX1111 | CG<br>RAM<br>(8) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

#### 6. CONFIGURATION OF CGRAM

|    | С  | HAF        | ACT        | ER         | COD | E  |    | 0          | CGR        | AM A |            | RES        | S          |            |    | CG         | RAN        | I DA       | TA |    |    |

|----|----|------------|------------|------------|-----|----|----|------------|------------|------|------------|------------|------------|------------|----|------------|------------|------------|----|----|----|

| D7 | D6 | <b>D</b> 5 | <b>D</b> 4 | <b>D</b> 3 | D2  | D1 | D0 | <b>A</b> 5 | <b>A</b> 4 | Аз   | <b>A</b> 2 | <b>A</b> 1 | <b>A</b> 0 | <b>D</b> 7 | D6 | <b>D</b> 5 | <b>D</b> 4 | <b>D</b> 3 | D2 | D1 | D0 |

| 0  | 0  | 0          | 0          | *          | 0   | 0  | 0  | 0          | 0          | 0    | 0          | 0          | 0          | *          | *  | *          | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 0          | 0          | 1          |            |    |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 0          | 1          | 0          |            |    |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 0          | 1          | 1          |            |    |            | 0          | 1          | 0  | 1  | 0  |

|    |    |            |            |            |     |    |    |            |            |      | 1          | 0          | 0          |            |    |            | 0          | 0          | 1  | 0  | 0  |

|    |    |            |            |            |     |    |    |            |            |      | 1          | 0          | 1          |            |    |            | 0          | 0          | 1  | 0  | 0  |

|    |    |            | ١          | 1          |     |    |    |            | ¥          |      | 1          | 1          | 0          |            | V  |            | 0          | 0          | 1  | 0  | 0  |

|    |    |            |            | •          |     |    |    |            | ,          |      | 1          | 1          | 1          |            | •  |            | 0          | 0          | 0  | 0  | 0  |

|    |    |            |            | :          |     |    |    |            | :          |      |            |            |            |            | :  |            |            |            |    |    |    |

| 0  | 0  | 0          | 0          | *          | 1   | 1  | 1  | 1          | 1          | 1    | 0          | 0          | 0          | *          | *  | *          | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 0          | 0          | 1          |            |    |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 0          | 1          | 0          |            |    |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 0          | 1          | 1          |            |    |            | 1          | 1          | 1  | 1  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 1          | 0          | 0          |            |    |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            |            |      | 1          | 0          | 1          |            |    |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            |            |     |    |    |            | V          |      | 1          | 1          | 0          |            | ¥  |            | 1          | 0          | 0  | 0  | 1  |

|    |    |            |            | •          |     |    |    |            | •          |      |            |            |            |            | ,  |            | 0          | 0          | 0  | 0  | 0  |

CGRAM addresses vs. character codes (DDRAM) and character patterns (CGRAM).

\* mark means "Don't care".

Upper section : Character pattern 1 (Y display) Lower section : Character pattern 2 (H display)

#### NOTES:

- 1. Character code bits D<sub>2</sub> to D<sub>0</sub> correspond to CGRAM addresses A<sub>5</sub> to A<sub>3</sub> (3 bits : 8 types).

- CGRAM addresses A<sub>2</sub> to A<sub>0</sub> correspond to line positions of the character pattern (3 bits : 8 lines).

- The columns of the character pattern are laid out with bit 0 allocated to the right end. Therefore, the pattern of bits 4 to 0 is displayed.

- If the upper 4 bits (D7 to D4) of the character code are zeros, the CGRAM is selected. Since bit D3 is "Don't care", "00H" and "08H" are the same CGRAM address.

- 5. If the CGRAM data is "1", data is displayed; if "0", data isn't displayed.

#### 7. CONFIGURATION OF SEGRAM

| SEG | RAM        | ADDR       | ESS |    |    | SI | EGRA        | M DA        | ГА          |             |             |

|-----|------------|------------|-----|----|----|----|-------------|-------------|-------------|-------------|-------------|

| Аз  | <b>A</b> 2 | <b>A</b> 1 | A0  | D7 | D6 | D5 | D4          | Dз          | D2          | D1          | Do          |

| 0   | 0          | 0          | 0   | B1 | Bo | *  | S0          | S1          | S2          | S3          | S4          |

| 0   | 0          | 0          | 1   | B1 | Bo | *  | <b>S</b> 5  | S6          | <b>S</b> 7  | S8          | S9          |

| 0   | 0          | 1          | 0   | B1 | Bo | *  | S10         | S11         | S12         | <b>S</b> 13 | S14         |

| 0   | 0          | 1          | 1   | B1 | Bo | *  | <b>S</b> 15 | <b>S</b> 16 | S17         | S18         | S19         |

| 0   | 1          | 0          | 0   | B1 | Bo | *  | S20         | S21         | S22         | <b>S</b> 23 | S24         |

| 0   | 1          | 0          | 1   | B1 | Bo | *  | S25         | S26         | S27         | S28         | S29         |

| 0   | 1          | 1          | 0   | B1 | Bo | *  | <b>S</b> 30 | <b>S</b> 31 | S32         | <b>S</b> 33 | S34         |

| 0   | 1          | 1          | 1   | B1 | Bo | *  | <b>S</b> 35 | <b>S</b> 36 | S37         | S38         | S39         |

| 1   | 0          | 0          | 0   | B1 | Bo | *  | S40         | S41         | S42         | <b>S</b> 43 | S44         |

| 1   | 0          | 0          | 1   | B1 | Bo | *  | <b>S</b> 45 | <b>S</b> 46 | S47         | S48         | S49         |

| 1   | 0          | 1          | 0   | B1 | Bo | *  | S50         | <b>S</b> 51 | <b>S</b> 52 | <b>S</b> 53 | <b>S</b> 54 |

| 1   | 0          | 1          | 1   | B1 | Bo | *  | S55         | <b>S</b> 56 | S57         | <b>S</b> 58 | S59         |

| 1   | 1          | 0          | 0   | B1 | Bo | *  | <b>S</b> 60 | <b>S</b> 61 | S62         | <b>S</b> 63 | S64         |

| 1   | 1          | 0          | 1   | B1 | Bo | *  | <b>S</b> 65 | <b>S</b> 66 | S67         | S68         | S69         |

| 1   | 1          | 1          | 0   | B1 | Bo | *  | <b>S</b> 70 | S71         | S72         | <b>S</b> 73 | S74         |

| 1   | 1          | 1          | 1   | B1 | Bo | *  | <b>S</b> 75 | <b>S</b> 76 | S77         | S78         | S79         |

#### SEGRAM addresses vs. display patterns

\* mark means "Don't care".

D7 and D6 : Blink control

D4 to D0 : Pattern displayed

#### NOTES :

- 1. Data stored in the SEGRAM is output for one-line display when COMI is selected.

- 2. Pins S0 to S79 are segment drive pins. Pin S0 is shown at the left end on the screen.

- 3. After output at pin S79, output at pin S0 is repeated.

- 4. For SEGRAM data, the lower 5 bits are used for display data.

- 5. If BE bit in the function set register is set to "1", the upper 1 bit (D7) in SEGRAM is used to control the blinking of the lower 5-bit pattern. When D7 is set to "1", the lower 5-bit display blinks. If bit D6 is "1", only the pattern of bit D4 can be blinked.

- 6. If SEGRAM data is "1", data is displayed; if "0", data isn't displayed.

## 8. CONFIGURATION OF DDRAM

Display positions vs. display data RAM (DDRAM) addresses

|                                      |     | DIGIT |     |     |     |     |     |     |     |      |      |      |      |      |      |      |

|--------------------------------------|-----|-------|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|

|                                      | 1st | 2nd   | 3rd | 4th | 5th | 6th | 7th | 8th | 9th | 10th | 11th | 12th | 13th | 14th | 15th | 16th |

| COM <sub>0</sub> to COM <sub>7</sub> | 00  | 01    | 02  | 03  | 04  | 05  | 06  | 07  | 08  | 09   | 0A   | 0B   | 0C   | 0D   | 0E   | 0F   |

| COM8 to COM15                        | 10  | 11    | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19   | 1A   | 1B   | 1C   | 1D   | 1E   | 1F   |

The above addressing is used because 16 digits are displayed. The DDRAM stores data for 32 characters.

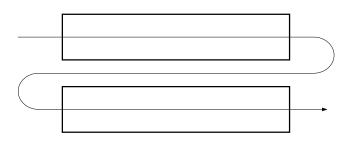

If the display data is shifted, the DDRAM addresses are changed as follows :

Shift to right

|                                      |     |     |     |     |     |     |     | DIC | GIT |      |      |      |      |      |      |      |

|--------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|

|                                      | 1st | 2nd | 3rd | 4th | 5th | 6th | 7th | 8th | 9th | 10th | 11th | 12th | 13th | 14th | 15th | 16th |