# **INT200**

# Low-side Driver IC

# Low-side Drive and High-side Control with Simultaneous Conduction Lockout

## **Product Highlights**

#### **5 V CMOS Compatible Control Inputs**

- · Combines logic inputs for low and high-side drives

- · Schmidt-triggered inputs for noise immunity

#### **Built-in High-voltage Level Shifters**

- Integrated level shifters simplify high-side interface

- Can withstand up to 800 V for direct interface to the INT201 high-side driver

- Pulsed high-voltage level shifters reduce power consumption

### Gate Drive Output for an External MOSFET

- Provides 300 mA sink/150 mA source current

- Can drive MOSFET gate at up to 15 V

- External MOSFET allows flexibility in design for various motor sizes

#### **Built-in Protection Features**

- · Simultaneous conduction lockout protection

- · UV lockout

## **Description**

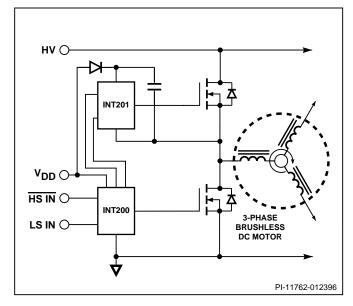

The INT200 Low-side driver IC provides gate drive for an external low-side MOSFET switch and high-side level shifting. When used in conjunction with the INT201 high-side driver, the INT200 provides a simple, cost-effective interface between low-voltage control logic and high-voltage loads. The INT200 is designed to be used with rectified 110 V or 220 V supplies. Both high-side and low-side switches can be controlled independently from ground-referenced 5 V logic inputs on the low side driver.

Built-in protection logic prevents both switches from turning on at the same time and shorting the high voltage supply. Pulsed level shifting saves power and provides enhanced noise immunity. The circuit is powered from a nominal 15 V supply to provide adequate gate drive for external N-channel MOSFETs.

Applications include motor drives, electronic ballasts, and uninterruptible power supplies. The INT200 can also be used to implement full- bridge and multi-phase configurations.

The INT 200 is available in 8-pin plastic DIP and SOIC packages.

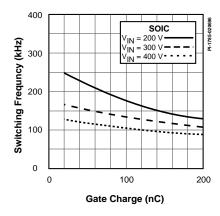

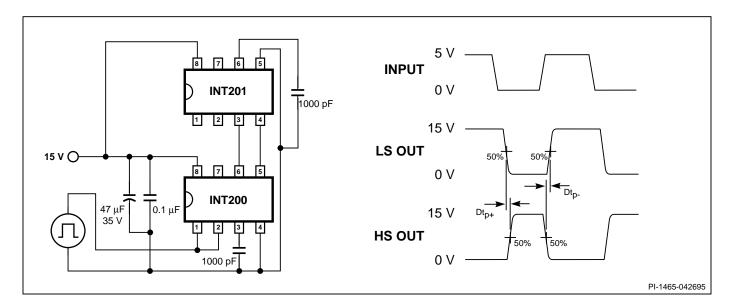

Figure 1. Typical Application

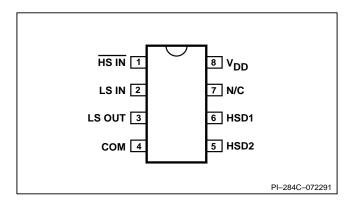

Figure 2. Pin Configuration.

| ORDERING INFORMATION |                    |                      |  |  |

|----------------------|--------------------|----------------------|--|--|

| PART<br>NUMBER       | PACKAGE<br>OUTLINE | ISOLATION<br>VOLTAGE |  |  |

| INT200PFI1           | P08A               | 600 V                |  |  |

| INT200TFI1           | T08A               | 600 V                |  |  |

| INT200PFI2           | P08A               | 800 V                |  |  |

| INT200TFI2           | T08A               | 800 V                |  |  |

## **Pin Functional Description**

#### **Pin 1:**

Active-low logic-level input HS IN controls the pulse circuit which signals the INT201 high-side driver.

#### **Pin 2:**

Active-high logic level input **LS IN** controls the low side driver output.

#### **Pin 3:**

**LS OUT** is the driver output which controls the low-side MOSFET.

#### **Pin 4:**

**COM** connection; analog reference point for the circuit.

#### **Pin 5:**

Level shift output **HSD 2** signals the high-side driver to turn off. One short, precise pulse is sent on each positive transition of  $\overline{\text{HS IN}}$ .

#### **Pin 6:**

Level shift output **HSD 1** signals the high-side driver to turn on. Two short, precise pulses are sent on each negative transition of HS IN.

#### **Pin 7:**

N/C for creepage distance.

#### Pin 8:

$V_{\rm DD}$  supplies power to the logic, high-side interface, and low-side driver.

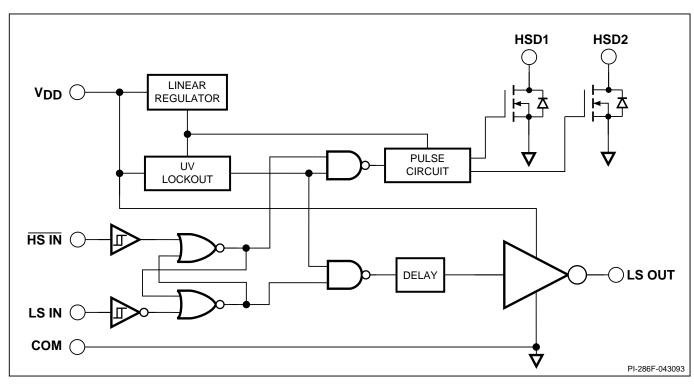

Figure 3. Functional Block Diagram of the INT200

## **INT200 Functional Description**

#### 5 V Regulator

The 5 V linear regulator circuit provides the supply voltage for the control logic and high-voltage level shift circuit. This allows the logic section to be directly compatible with 5 V CMOS logic without the need of an external 5 V supply.

#### **Undervoltage Lockout**

The undervoltage lockout circuit disables the LS OUT pin and both HSD pins whenever the  $V_{\rm DD}$  power supply falls below typically 9.0 V, and maintains this condition until the  $V_{\rm DD}$  power supply rises above typically 9.35 V. This guarantees that both MOSFETs will remain off during power-up or fault conditions.

#### HSD1/HSD2

The HSD1 and HSD2 outputs are connected to integrated high-voltage N-channel MOSFET transistors which perform the level-shifting function for communication to the high-side driver. Controlled current capability allows the drain voltage to float with the high-side driver. Two individual channels produce a true differential communication channel for accurately controlling the high-side driver in the presence of fast moving high-voltage waveforms.

#### **Pulse Circuit**

The pulse circuit provides the two high-voltage level shifters with precise timing signals. Two pulses are sent over HSD1 to signal the high-side driver to turn on. One pulse is sent over HSD2 to signal the high-side driver to turn off. The combination of differential communication with the precise timing provides maximum immunity to noise.

#### **Conduction Latch**

An RS latch prevents the low-side driver and high-side driver from being on at the same time, regardless of the input signals.

#### **Delay Circuit**

The delay circuit matches the low-side propagation delay with the combination of the pulse circuit, high voltage level shift, and high-side driver propagation delays. This ensures that the low-side driver and high-side driver will never be on at the same time during switching transitions in either direction.

#### **Driver**

The CMOS drive circuit provides drive power to the gate of the MOSFET used on the low side of the half bridge circuit. The driver consists of a CMOS buffer capable of driving an external transistor gate at up to 15 V.

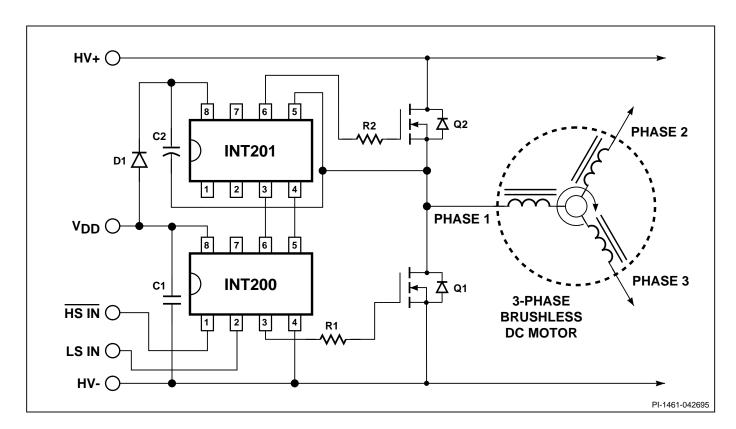

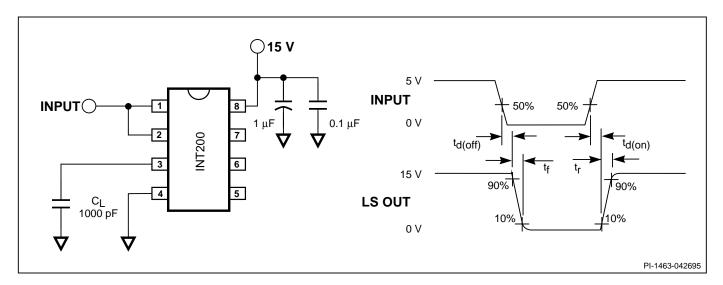

Figure 4. Using the INT200 and INT201 in a 3-phase Configuration.

## **General Circuit Operation**

One phase of a three-phase brushless DC motor drive circuit is shown in Figure 4 to illustrate an application of the INT200/201. The LS IN signal directly controls MOSFET Q1. The HS IN signal causes the INT200 to command the INT201 to turn MOSFET Q2 on or off as required. The INT200 will ignore input signals that would command both Q1 and Q2 to conduct simultaneously, protecting against shorting the HV+ bus to HV-.

Local bypassing for the low-side driver is provided by C1. Bootstrap bias for the high-side driver is provided by D1 and C2. Slew rate and effects of parasitic oscillations in the load waveforms are controlled by resistors R1 and R2.

The inputs are designed to be compatible with 5 V CMOS logic levels and should not be connected to V<sub>DD</sub>. Normal CMOS power supply sequencing should be observed. The order of signal application

should be V<sub>DD</sub>, logic signals, and then HV+. V<sub>DD</sub> should be supplied from a low impedance voltage source.

The length of time that the high-side can remain on is limited by the size of the bootstrap capacitor. Applications with extremely long high-side on times require special techniques discussed in AN-10.

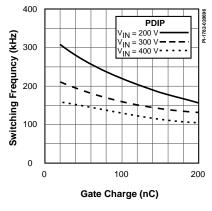

Maximum frequency of operation is limited by power dissipation due to high-voltage switching, gate charge, and bias power. Figure 5 indicates the maximum switching frequency as a function of input voltage and gate charge. For higher ambient temperatures, the switching frequency should be derated linearly.

Figure 5. Switching Frequency versus Gate Charge for a) PDIP and b) SOIC.

Figure 6. Using the INT200 and INT201 to Drive a Fluorescent Lamp.

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>                                                                                                                                                                           |                                                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| HSD1/HSD2 Voltage (1 Suffix)       600 V         (2 Suffix)       800 V         HSD1/HSD2 Slew Rate       10 V/ns         V <sub>DD</sub> Voltage       16.5 V         Logic Input Voltage       -0.3V to 5.5 V | Power Dissipation  PF Suffix $(T_A = 25^{\circ}C)$ |  |  |  |

| LS OUT Voltage                                                                                                                                                                                                  | Thermal Impedance ( $\theta_{JA}$ )  PF Suffix     |  |  |  |

| Parameter                     | Symbol                           | Conditions (Unless Otherwise Specified) $V_{DD} = 15 \text{ V, COM} = 0\text{V}$ $T_{A} = -40 \text{ to } 85^{\circ}\text{C}$ | Min      | Тур     | Max       | Units |

|-------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|---------|-----------|-------|

| LOGIC                         |                                  |                                                                                                                               |          |         |           |       |

| Input Current,<br>High or Low | I <sub>IH,</sub> I <sub>IL</sub> | V <sub>IH</sub> = 4.0 V<br>V <sub>IL</sub> = 1.0 V                                                                            | 0<br>-20 | 10<br>0 | 150<br>20 | μΑ    |

| Input Voltage<br>High         | V <sub>IH</sub>                  |                                                                                                                               | 4.0      |         |           | V     |

| Input Voltage<br>Low          | V <sub>IL</sub>                  |                                                                                                                               |          |         | 1.0       | V     |

| Input Voltage<br>Hysteresis   | V <sub>HY</sub>                  |                                                                                                                               | 0.3      | 0.7     |           | V     |

| HSD OUTPUTS                   |                                  |                                                                                                                               |          |         |           |       |

| Breakdown                     | B\/                              | 1 Suffix                                                                                                                      | 600      | 700     |           | V     |

| Voltage                       | BV <sub>DSS</sub>                | 2 Suffix                                                                                                                      | 800      | 900     |           | V     |

| Off-State<br>Output Current   | I <sub>HSD(OFF)</sub>            | $V_{HSD1}, V_{HSD2} = 500 \text{ V}$                                                                                          |          | 0.1     | 15        | μΑ    |

| On-State<br>Output Current    | I <sub>HSD(ON)</sub>             | $V_{HSD1}$ , $V_{HSD2} = 10 \text{ V}$                                                                                        | 5        | 25      |           | mA    |

| On-State<br>Pulse Width       | t <sub>HSD(ON)</sub>             |                                                                                                                               |          |         | 156       | ns    |

| Output<br>Capacitance         | C <sub>oss</sub>                 | $V_{HSD1}$ , $V_{HSD2} = 25 \text{ V}$                                                                                        |          | 10      |           | pF    |

| Parameter                        | Symbol              | Conditions (Unless Otherwise Specified) $V_{DD} = 15 \text{ V, COM} = 0 \text{V}$ $T_{A} = -40 \text{ to } 85^{\circ}\text{C}$ |                           | Min                  | Тур                  | Max  | Units |

|----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|----------------------|------|-------|

| LS OUT                           |                     |                                                                                                                                |                           |                      |                      |      |       |

| Output Voltage<br>High           | V <sub>OH</sub>     | I <sub>o</sub> = -20 mA                                                                                                        |                           | V <sub>DD</sub> -1.0 | V <sub>DD</sub> -0.5 |      | V     |

| Output Voltage<br>Low            | V <sub>OL</sub>     | I <sub>o</sub> = 40 mA                                                                                                         |                           |                      | 0.3                  | 1.0  | V     |

| Output Short<br>Circuit Current  | l <sub>os</sub>     | See Note 1                                                                                                                     | $V_o = 0V$ $V_o = V_{DD}$ | 300                  |                      | -150 | mA    |

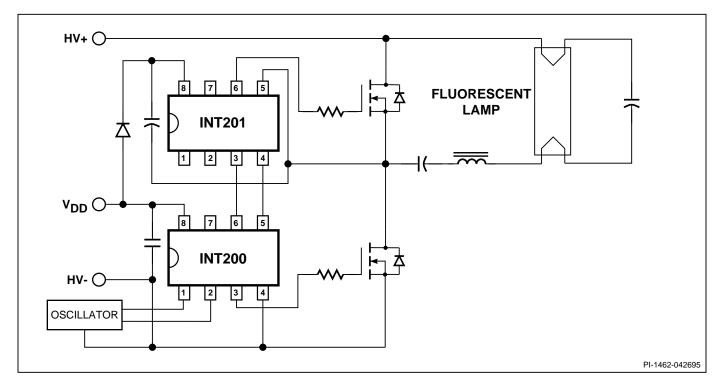

| Turn-on Delay<br>Time            | t <sub>d(on)</sub>  | See F                                                                                                                          | See Figure 7              |                      | 0.6                  | 1.0  | μs    |

| Rise<br>Time                     | t <sub>r</sub>      | See Figure 7                                                                                                                   |                           |                      | 80                   | 120  | ns    |

| Turn-off Delay<br>Time           | t <sub>d(off)</sub> | See Figure 7                                                                                                                   |                           |                      | 0.5                  | 1    | μs    |

| Fall<br>Time                     | t <sub>f</sub>      | See Figure 7                                                                                                                   |                           |                      | 50                   | 100  | ns    |

| SYSTEM RESPO                     | NSE                 |                                                                                                                                |                           |                      |                      |      |       |

| Deadtime (Low<br>Off to High On) | Dt <sub>P+</sub>    | See Figure 8                                                                                                                   |                           | 0                    | 450                  |      | ns    |

| Deadtime (High<br>Off to Low On) | Dt <sub>p.</sub>    | See Figure 8                                                                                                                   |                           | 0                    | 300                  |      | ns    |

| UNDERVOLTAGE LOCKOUT             |                     |                                                                                                                                |                           |                      |                      |      |       |

| Input UV<br>Trip-off Voltage     | $V_{DD(UV)}$        |                                                                                                                                |                           | 8.5                  | 9.0                  | 10   | V     |

| Input UV<br>Hysteresis           |                     |                                                                                                                                |                           | 175                  | 350                  |      | mV    |

| SUPPLY                           |                     |                                                                                                                                |                           |                      |                      |      |       |

| Supply<br>Current                | I <sub>DD</sub>     | See Figure 2                                                                                                                   |                           |                      | 1.5                  | 3.0  | mA    |

| Supply<br>Voltage                | V <sub>DD</sub>     |                                                                                                                                |                           | 10                   |                      | 16   | V     |

#### NOTES:

- 1. Applying a short circuit to the LS OUT pin for more than 500  $\mu s$  will exceed the thermal rating of the package, resulting in destruction of the part.

- 2.  $V_{DD}$  supply must have less than 30  $\Omega$  output impedance.

Figure 7. Switching Time Test Circuit.

Figure 8. Dead Time Test Circuit.

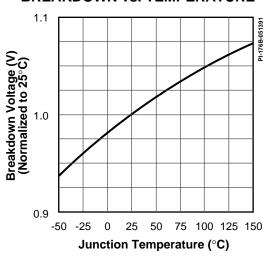

## **BREAKDOWN vs. TEMPERATURE**

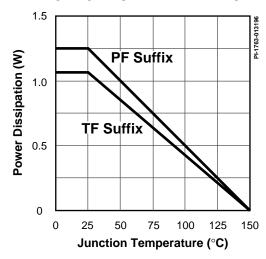

#### **PACKAGE POWER DERATING**

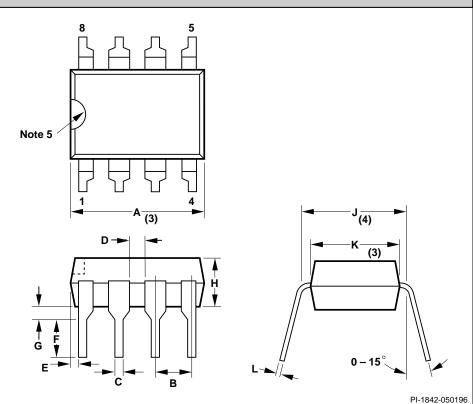

#### **P08A Plastic DIP-8**

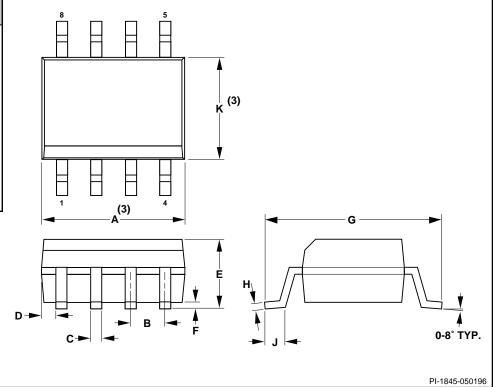

| Dim. | inches   | mm        |

|------|----------|-----------|

| Α    | .395 MAX | 10.03 MAX |

| В    | .090110  | 2.29-2.79 |

| С    | .015021  | 0.38-0.53 |

| D    | .040 TYP | 1.02 TYP  |

| E    | .015030  | 0.38-0.76 |

| F    | .125 MIN | 3.18 MIN  |

| G    | .015 MIN | 0.38 MIN  |

| н    | .125135  | 3.18-3.43 |

| J    | .300320  | 7.62-8.13 |

| K    | .245255  | 6.22-6.48 |

| L    | .009015  | 0.23-0.38 |

- Notes:

1. Package dimensions conform to JEDEC specification MS-001-AB for standard dual inline (DIP) package .300 inch row spacing (PLASTIC) 8 leads (issue B, 7/85).

2. Controlling dimensions: inches.

3. Dimensions are for the molded body and do not include mold flash or other progrusions.

- not include mold flash or other protrusions.

Mold flash or protrusions shall not exceed .010 inch (.25 mm) on any side.

- 4. These dimensions measured with the leads constrained to be perpendicular to package bottom.

5. Pin 1 orientation identified by end notch or

- dot adjacent to Pin 1.

**T08A Plastic SO-8**

| DIM         | inches                                  | mm                                 |

|-------------|-----------------------------------------|------------------------------------|

| A<br>B<br>C | 0.189-0.197<br>0.050 TYP<br>0.014-0.019 | 4.80-5.00<br>1.27 TYP<br>0.35-0.49 |

| D<br>E      | 0.014-0.019<br>0.012 TYP<br>0.053-0.069 | 0.35-0.49<br>0.31 TYP<br>1.35-1.75 |

| F<br>G      | 0.004-0.010                             | 0.10-0.25<br>5.80-6.20             |

| H<br>J      | 0.007-0.010<br>0.021-0.045              | 0.19-0.25<br>0.51-1.14             |

| K           | 0.150-0.157                             | 3.80-4.00                          |

- 1. Package dimensions conform to JEDEC specification MS-012-AA for standard small specification MS-012-AA for standard small outline (SO) package, 8 leads, 3.75 mm (.150 inch) body width (issue A, June 1985).

2. Controlling dimensions are in mm.

3. Dimensions are for the molded body

- and do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .15 mm (.006 inch) on any

- 4. Pin 1 side identified edge by chamfer on top of the package body or indent on Pin 1

## Notes

# Notes

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein, nor does it convey any license under its patent rights or the rights of others.

PI Logo and **TOPSwitch** are registered trademarks of Power Integrations, Inc. ©Copyright 1994, Power Integrations, Inc. 477 N. Mathilda Avenue, Sunnyvale, CA 94086

#### WORLD HEADQUARTERS

Power Integrations, Inc. 477 N. Mathilda Avenue Sunnyvale, CA 94086 USA

Main: 408•523•9200 Customer Service: Phone: 408•523•9265 Fax: 408•523•9365

#### **JAPAN**

Power Integrations, K.K. Keihin-Tatemono 1st Bldg. 12-20 Shin-Yokohoma 2-Chome, Kohoku-ku Yokohama-shi, Kanagawa 222 Japan

Phone: 81•(0)•45•471•1021 Fax: 81•(0)•45•471•3717

#### **AMERICAS**

For Your Nearest Sales/Rep Office Please Contact Customer Service Phone: 408•523•9265

Fax: 408•523•9365

#### ASIA & OCEANIA

For Your Nearest Sales/Rep Office Please Contact Customer Service

Phone: 408•523•9265 Fax: 408•523•9365

#### **EUROPE & AFRICA**

Power Integrations (Europe) Ltd.

Mountbatten House

Fairacres

Windsor SL4 4LE United Kingdom

Phone: 44•(0)•1753•622•208 Fax: 44•(0)•1753•622•209

#### APPLICATIONS HOTLINE

World Wide 408•523•9260

#### APPLICATIONS FAX

Americas 408•523•9361

Europe/Africa 44•(0)•1753•622•209

Japan 81•(0)•45•471•3717 Asia/Oceania 408•523•9364