# MC8T14 MC8T24

### TRIPLE LINE RECEIVERS WITH HYSTERESIS

... specifically designed to meet the input/output specifications for IBM 360/370 Systems (IBM specification GA 22-6974-0). Each receiver incorporates hysteresis to provide high noise immunity and also high input impedance to minimize loading on the related driver.

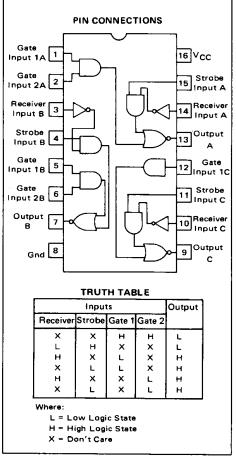

- Each Channel Can Be Independently Strobed

- High Speed tpLH = tpHL = 20 ns

- Input Gating Provided on Each Line

- Operates on a Single +5.0 V Power Supply

- Fully Compatible with MTTL or MDTL Logic Systems

- Input Hysteresis Results in High Noise Immunity

# TYPICAL APPLICATION 1/2 MC8T13 or 1/2 MC8T23 Coaxial Cable RT RT

# TRIPLE LINE RECEIVERS WITH HYSTERESIS SILICON MONOLITHIC INTEGRATED CIRCUIT

### MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted.)

| Rating                                                                                | Symbol                    | Value       | Unit                     |  |

|---------------------------------------------------------------------------------------|---------------------------|-------------|--------------------------|--|

| Power Supply Voltage                                                                  | Vcc                       | 7.0         | Vdc                      |  |

| Receiver Input Voltage (V <sub>CC</sub> = 0)                                          | VI(R)                     | 7.0<br>6.0  | Vdc<br>————              |  |

| Strobe or Gate Input Voltage                                                          | V <sub>I</sub> (S) or (G) | 5.5         | Vdc                      |  |

| Output Voltage                                                                        | Vo                        | 7.0         | Vdc                      |  |

| Output Current                                                                        | 10                        | ±100        | mA                       |  |

| Power Dissipation (Package Limitation) Ceramic Package Derate above 25 <sup>0</sup> C | PD                        | 1000<br>6.7 | mW<br>mW/ <sup>O</sup> C |  |

| Plastic Package<br>Derate above 25 <sup>0</sup> C                                     |                           | 830<br>6.7  | mW<br>mW/ <sup>O</sup> C |  |

| Junction Temperature<br>Ceramic Package<br>Plastic Package                            | τυ                        | 175<br>150  | °C                       |  |

| Operating Ambient Temperature Range                                                   | TA                        | 0 to +75    | °C                       |  |

| Storage Temperature Range                                                             | T <sub>stg</sub>          | -65 to +150 | °C                       |  |

## **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, $4.75 \le V_{CC} \le 5.25 \text{ V}$ and $0^{O}\text{C} \le T_{A} \le 75^{O}\text{C}$ )

|                                                                                                                                    | -                         | N        | 1C8T1                                            | 4                                                | M        | C8T24      | 1     |          |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|--------------------------------------------------|--------------------------------------------------|----------|------------|-------|----------|

| Characteristic                                                                                                                     | Symbol                    | Min      | Тур                                              | Max                                              | Min      | Тур        | Max   | Unit     |

| Gate or Strobe Input Voltage — High Logic State                                                                                    | VIH(G) or (S)             | 2.0      | -                                                | _                                                | 2.0      | -          |       | ٧        |

| Gate or Strobe Input Voltage - Low Logic State                                                                                     | VIL(G) or (S)             |          | _                                                | 0.8                                              | -        | 1          | 0.8   | <b>V</b> |

| Receiver Input Voltage — High Logic State                                                                                          | VIH(R)                    | 2.0      | _                                                | _                                                | 1.7      | -          | -     | Vdc      |

| Receiver Input Voltage — Low Logic State                                                                                           | VIL(R)                    |          | _                                                | 0.8                                              | -        | _          | 0.7   | Vdc      |

| Receiver Input Hysteresis (1)                                                                                                      | VH(R)                     | 0.3      | 0.5                                              | -                                                | 0.2      | 0.4        | -     | ٧        |

| $(V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}, V_{IL}(G) = 0, V_{IH}(S) \approx 4.5 \text{ V})$                               |                           |          | <u> </u>                                         |                                                  |          |            |       |          |

| Input Clamp Voltage                                                                                                                | VIC(G) or (S)             | -        | -                                                | 1.5                                              | -        | -          | 1.5   | ٧        |

| $(V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}, I_1 = -12 \text{ mA})$ (Strobe or Gate Inputs)                                 |                           | <u> </u> |                                                  |                                                  |          |            |       |          |

| Input Breakdown Voltage                                                                                                            | VI(G) or (S)              | 5.5      | -                                                | -                                                | 5.5      | -          | -     | ٧        |

| (VCC = 5.0 V, I <sub>1</sub> = 10 mA) (Strobe or Gate Inputs)                                                                      | <u> </u>                  |          | <u> </u>                                         |                                                  |          | ļ          |       |          |

| Receiver Input Current — High Logic State                                                                                          | liH(R)                    |          |                                                  | 0.17                                             |          |            |       | mA       |

| $(V_{IH(R)} = 3.8  V)$                                                                                                             |                           | _        | _                                                | 0.17                                             | _        |            | 0.17  |          |

| $(V_{IH}(R) = 3.11 \text{ V})$                                                                                                     |                           |          | 1 -                                              | _                                                | l _      | _          | 5.0   | 1        |

| $(V_{1H(R)} = 7.0 \text{ V})$                                                                                                      | }                         |          | _                                                | l _                                              | l _      |            | 5.0   |          |

| (V <sub>IH</sub> (R) = 6.0 V, V <sub>CC</sub> = 0 V)                                                                               | <sup>1</sup> 1H(G) or (S) | 1        | <del>                                     </del> | <del>                                     </del> | <u> </u> |            | t     | μА       |

| Gate or Strobe Input Current – High Logic State                                                                                    | TH(G) or (S)              |          | _                                                | 40                                               | _        | _          | 40    |          |

| (V <sub>IH</sub> (S) = 4.5 V, V <sub>IH</sub> (R) = 3.11 V)<br>(V <sub>I</sub> H(G) = 4.5 V)                                       |                           | _        | _                                                | 40                                               | _        | _          | 40    |          |

| Gate or Strobe Input Current — Low Logic State                                                                                     | IL(G) or (S)              | -0.1     | -                                                | -1.6                                             | -0.1     |            | -1.6  | mĀ       |

| (VIL(G) or (S) = 0.4 V, VIL(R) = 0 V)                                                                                              | 12,2,                     |          |                                                  | ļ                                                | ŀ        |            |       |          |

| Output Voltage - High Logic State                                                                                                  | Voн                       |          |                                                  |                                                  |          |            |       | ٧        |

| $(V_{IH(R)} = 2.0 \text{ V}, V_{IH(S)} = 2.0 \text{ V}, V_{IL(G)} = 0.8 \text{ V}, I_{OH} = -800 \mu\text{A})$                     |                           | 2.6      | 3.5                                              |                                                  | -        |            | -     |          |

| $(V_{IH(R)} = 0.8 \text{ V}, V_{IL(S)} = 0.8 \text{ V}, V_{IL(G)} = 0.8 \text{ V}, t_{OH} = -800 \mu\text{A})$                     |                           | 2.6      | 3.5                                              | -                                                | _        | -          | -     |          |

| $(V_{1H(B)} = 1.7 \text{ V}, V_{1H(S)} = 2.0 \text{ V}, V_{1L(G)} = 0.8 \text{ V}, I_{OH} = -800 \mu\text{A})$                     |                           | <b>-</b> | -                                                | -                                                | 2.6      | 3.4        | -     |          |

| $(V_{IH(R)} = 0.7 \text{ V}, V_{IL(S)} = 0.8 \text{ V}, V_{IL(G)} = 0.8 \text{ V}, I_{OH} = -800 \mu\text{A})$                     |                           |          |                                                  | ļ-                                               | 2.6      | 3.4        | ↓-    | <b>.</b> |

| Output Voltage - Low Logic State                                                                                                   | VOL                       |          |                                                  | ١.,                                              |          |            |       | V        |

| $(V_{IL(R)} = 0.8 \text{ V}, V_{IH(S)} = 2.0 \text{ V}, V_{IL(G)} = 0.8 \text{ V}, I_{OL} = 16 \text{ mA})$                        |                           | -        |                                                  | 0.4                                              | -        | -          | _     | 1        |

| $(V_{IL}(R) = 0.8 \text{ V}, V_{IL}(S) = 0.8 \text{ V}, V_{IH}(G) = 2.0 \text{ V}, I_{OL} = 16 \text{ mA})$                        |                           | -        | -                                                | 0.4                                              | -        | -          | 0.4   |          |

| $(V_{IL}(R) = 0.7 \text{ V}, V_{IH}(S) = 2.0 \text{ V}, V_{IL}(G) = 0.8 \text{ V}, I_{OL} = 16 \text{ mA})$                        |                           | _        | -                                                | -                                                | _        | _          | 0.4   | ŀ        |

| $(V_{IL}(R) = 0.7 \text{ V, } V_{IL}(S) = 0.8 \text{ V, } V_{IH}(G) = 2.0 \text{ V, } I_{OL} = 16 \text{ mA})$                     | <u> </u>                  |          | <del>  _</del> _                                 | <del>  _</del>                                   | <b>-</b> | <b>↓</b> _ | 1 0.4 |          |

| Output Short-Circuit Current (2)                                                                                                   | los                       | -50      | _                                                | -100                                             |          | l _        | l _   | mΑ       |

| $(V_{IH}(R) = 3.8 \text{ V}, V_{IL}(G) = 0 \text{ V}, V_{IL}(S) = 0, V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C})$            |                           | -50      | _                                                | -100                                             | -50      | _          | -100  | I        |

| $(V_{IH(R)} = 3.11 \text{ V}, V_{IL(G)} = 0 \text{ V}, V_{IL(S)} = 0 \text{ V}, V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C})$ | ļ                         |          | -                                                | 72                                               |          | 60         | 72    | mA       |

| Power Supply Current                                                                                                               | ¹cc                       | -        | 60                                               | 1 12                                             | -        | ١٣٠        | 12    | "I"A     |

| (V <sub>CC</sub> = 5.25 V, T <sub>A</sub> = 25°C)                                                                                  | <u> </u>                  |          | ┸                                                | <u>i                                    </u>     |          | <u> </u>   | 1     | <u> </u> |

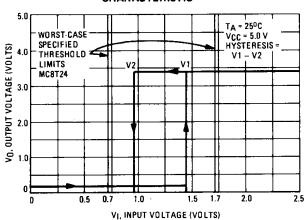

<sup>(1)</sup> The Input Hysteresis is defined as the difference the input voltage at which the output begins to go from the high logic state to the low logic state and the input voltage which causes the output to begin to go from the low logic state to the high logic state.

<sup>(2)</sup> Only one output may be shorted at a time.

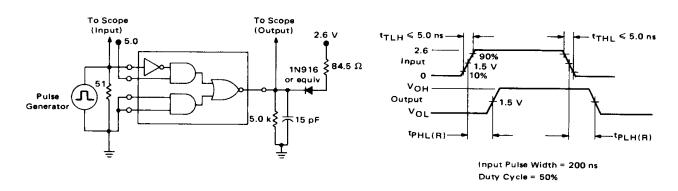

### SWITCHING CHARACTERISTICS ( $V_{CC} = 5.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                                                          | Symbol              | M   |     |     |      |

|--------------------------------------------------------------------|---------------------|-----|-----|-----|------|

|                                                                    |                     | Min | Тур | Max | Unit |

| Propagation Delay Time - Receiver Input to High Logic State Output | <sup>t</sup> PLH(R) | -   | 20  | 30  | ns   |

| Propagation Delay Time Receiver Input to Low Logic State Output    | <sup>t</sup> PHL(R) | -   | 20  | 30  | ns   |

| Propagation Delay Time Strobe Input to High Logic State Output     | ФLH(S)              | -   |     |     | ns   |

| Propagation Delay Time Strobe Input to Low Logic State Output      | tPHL(S)             | -   | _   | _   | ns   |

| Propagation Delay Time Gate Input to High Logic State Output       | <sup>‡</sup> PLH(G) | -   | _   | Ī - | ns   |

| Propagation Delay Time Gate Input to Low Logic State Output        | tPHL(G)             | -   | _   | -   | ns   |

FIGURE 1 – RECEIVER PROPAGATION DELAY TIMES  $\psi_{LH(R)}$  and  $\psi_{HL(R)}$  TEST CIRCUIT AND WAVEFORMS

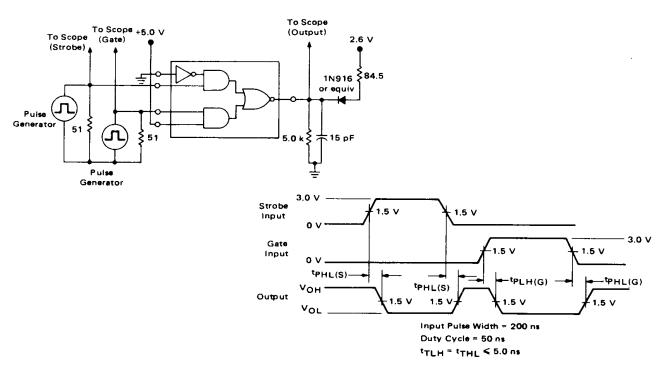

FIGURE 2 - GATE AND STROBE PROPAGATION DELAY TIME TEST CIRCUIT AND WAVEFORMS

FIGURE 3 – TYPICAL RECEIVER HYSTERESIS CHARACTERISTIC

### FIGURE 4 - HYSTERESIS TEST CIRCUIT

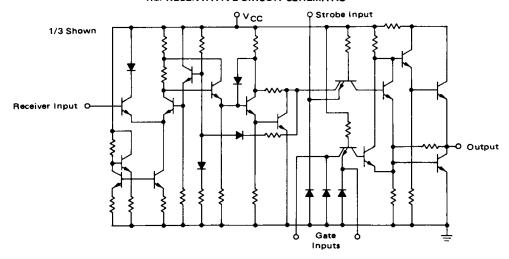

### REPRESENTATIVE CIRCUIT SCHEMATIC