# GX214A Monolithic 4x1 Video Multiplexer

## DATA SHEET

### FEATURES

- low cost

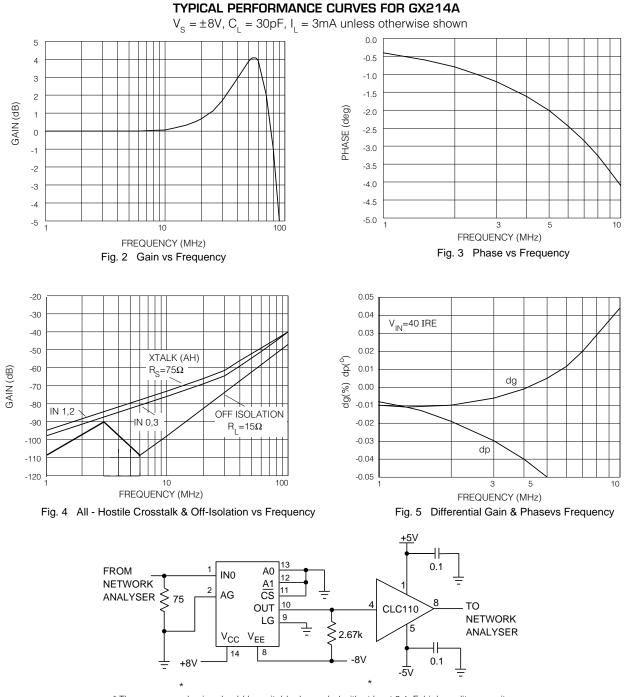

- differential gain at 3.58 MHz, 0.05% max.

- differential phase at 3.58 MHz, 0.05 deg. max.

- off-isolation better than 90 dB at 10 MHz

- all hostile crosstalk at 3.58 MHz, 75 dB typ. (R $_{\rm IN}{=}$  75  $\Omega$ )

- make-before-break switching

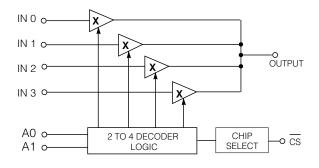

#### FUNCTIONAL BLOCK DIAGRAM

### TRUTH TABLE

| CS | A1 | A0 | OUTPUT |

|----|----|----|--------|

| 0  | 0  | 0  | IN 0   |

| 0  | 0  | 1  | IN 1   |

| 0  | 1  | 0  | IN 2   |

| 0  | 1  | 1  | IN 3   |

| 1  | Х  | Х  | HI - Z |

X = DON'T CARE

### ORDERING INFORMATION

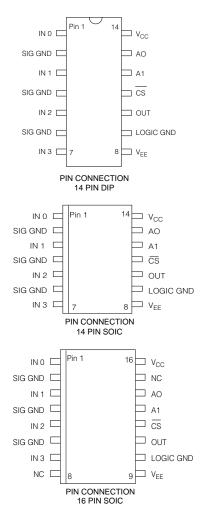

| Part Number  | Package Type | Temperature Range |  |  |

|--------------|--------------|-------------------|--|--|

| GX214 - ACDB | 14 Pin DIP   | 0° to 70°C        |  |  |

| GX214 - ACKC | 16 Pin SOIC  | 0° to 70°C        |  |  |

| GX214 - ACKB | 14 Pin SOIC  | 0° to 70°C        |  |  |

### CIRCUIT DESCRIPTION

The GX214A is a low cost 4x1 video multiplexer containing four analog video switches and a 2 to 4 decoder. A Chip Select input allows paralleled GX214As to be operated in a switching matrix.

The GX214A represents a fully buffered, unilateral transmission path when enabled. When disabled, the output is high impedance.

The device operates from  $\pm 7.5$  V to  $\pm 9.5$  V supplies with TTL and 5 V CMOS compatible input logic levels.

### APPLICATIONS

- CATV and CCTV systems

- low cost video routing

Document No. 520 - 5 - 1

GENNUM CORPORATION P.O. Box 489, Stn A, Burlington, Ontario, Canada L7R 3Y3 tel. (905) 632-2996 fax: (905) 632-5946 Japan Branch: A-302 Miyamae Village, 2-10-42 Miyamae, Suginami-ku, Tokyo 168, Japan tel. (03) 3334-7700 fax: (03) 3247-8839 Downloaded from Elecodis.com electronic components distributor

### ABSOLUTE MAXIMUM RATINGS

| Parameter                   | Value                            | Parameter                         | Value                                                     |

|-----------------------------|----------------------------------|-----------------------------------|-----------------------------------------------------------|

| Supply Voltage              | ±10.0 V                          | Lead Temperature (Soldering, 10 S | ec) $260 \text{ °C}$                                      |

| Operating Temperature Range | 0 °C ≤ T <sub>A</sub> ≤ 70 °C    | Analog Input Voltage              | -4 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> +0.3 V |

| Storage Temperature Range   | -65 °C ≤ T <sub>S</sub> ≤ 150 °C | Logic Input Voltage               | 0 V $\leq$ V <sub>L</sub> $\leq$ 5.5 V                    |

## NOTE: A short from output to ground or either supply will destroy the device.

For  $R_{EXT}$  use a 2.67 k $\Omega$  1%,  $^{1}/_{4}$  W resistor.

## $\textbf{ELECTRICAL CHARACTERISTICS} \quad V_{S} = \pm 8 \text{ V DC}, \ 0^{\circ}\text{C} < \text{T}_{A} < 70 \ ^{\circ}\text{C}, \ \text{R}_{L} = 2.67 \text{ k}\Omega \text{ to } \text{V}_{\text{EE}}, \ \text{C}_{L} = 30 \text{pF} \ \text{I}_{L} = 3 \text{mA}$

|         | PARAMETER                      | SYMBOL                | CONDITIONS                                                                             | MIN  | TYP  | MAX          | UNITS |

|---------|--------------------------------|-----------------------|----------------------------------------------------------------------------------------|------|------|--------------|-------|

|         | Supply Voltage                 | ±V <sub>S</sub>       |                                                                                        | 7.5  | 8.0  | 9.5          | V     |

| DC      |                                | I+                    | Chip selected ( $\overline{CS}=0$ )                                                    | -    | 14   | 20           | mA    |

| SUPPLY  |                                |                       | Chip not selected ( $\overline{CS}=1$ )                                                | -    | 0.5  | 0.85         | mA    |

|         | Supply Current                 | I-                    | Chip selected (CS=0)                                                                   | -    | 13   | 18           | mA    |

|         | not including $I_{L}$          |                       | Chip not selected (CS=1)                                                               | -    | 0.58 | 0.88         | mA    |

|         | Analog Output<br>Voltage Swing | V <sub>OUT</sub>      | Extremes before<br>clipping occurs                                                     | -    | -    | +5.0<br>-1.2 | V     |

| STATIC  | Analog Input Bias<br>Current   | I <sub>IN</sub>       |                                                                                        | -    | 25   | -            | μΑ    |

|         | Output Offset Voltage          | V <sub>OS</sub>       | $75\Omega$ resistor on each input to ground                                            | +5   | -30  | -70          | mV    |

|         | Turn-On Time                   | t <sub>on</sub>       | Control input to appearance of signal at output.                                       | -    | 250  | 400          | ns    |

|         | Turn-Off Time                  | t <sub>OFF</sub>      | Control input to disappear-<br>ance of signal at output.                               | 500  | 750  | -            | ns    |

| LOGIC   | Logic Input                    | V <sub>IH</sub>       | 1                                                                                      | 2.4  | -    | -            | V     |

|         | Thresholds                     | V <sub>IL</sub>       | 0                                                                                      | -    | -    | 0.6          | V     |

|         | Logic Input                    | I <sub>BIAS</sub>     | Chip Selected A0,A1 = 1                                                                | -    | -    | 1            | nA    |

|         | Bias Current                   |                       | Chip Selected A0,A1 = 0                                                                | -    | -    | 2            | μA    |

|         | Insertion Loss                 | I.L.                  | 1V p-p sine or sq. wave<br>at 100 kHz                                                  | 0.05 | 0.08 | 0.11         | dB    |

|         | Bandwidth (-3dB)               | B.W.                  |                                                                                        | 65   | 85   | -            | MHz   |

|         | Input Resistance               | R <sub>IN</sub>       | Chip selected $(\overline{CS} = 0)$                                                    | 900  | -    | -            | kΩ    |

| DYNAMIC | Input Capacitance              | C <sub>IN</sub>       | Chip selected $(\overline{CS} = 0)$                                                    | -    | 2.0  | -            | pF    |

|         |                                |                       | Chip not selected (CS=1)                                                               | -    | 2.2  | -            | pF    |

|         | Output Resistance              | R <sub>OUT</sub>      | Chip selected (CS=0)                                                                   | -    | 14   | -            | Ω     |

|         | Output Capacitance             | C <sub>OUT</sub>      | Chip not selected $(\overline{CS}=1)$                                                  | -    | 12   | -            | pF    |

|         | Differential Gain              | dg                    | at 3.58 MHz                                                                            | -    | -    | 0.05         | %     |

|         | Differential Phase             | dp                    | V <sub>IN</sub> = 40 IRE                                                               | -    | -    | 0.05         | deg.  |

|         | All Hostile Crosstalk          | X <sub>TALK(AH)</sub> | Sweep on 3 inputs 1V p-p<br>4th input has 75 $\Omega$ resistor<br>to gnd. $f = 10$ MHz | 72   | 75   | -            | dB    |

|         | Chip Disabled Crosstalk        | X <sub>TALK(CD)</sub> | One xpt on output to ground $f = 10 \text{ MHz}$                                       | 90   | 100  | -            | dB    |

520 - 5 - 1

#### **APPLICATION INFORMATION**

The circuit layout of any wideband circuit is critical. Good high frequency design practice, proper lead dress and PCB component placement along with a well regulated and decoupled power supply will assure optimum performance of the crosspoint.

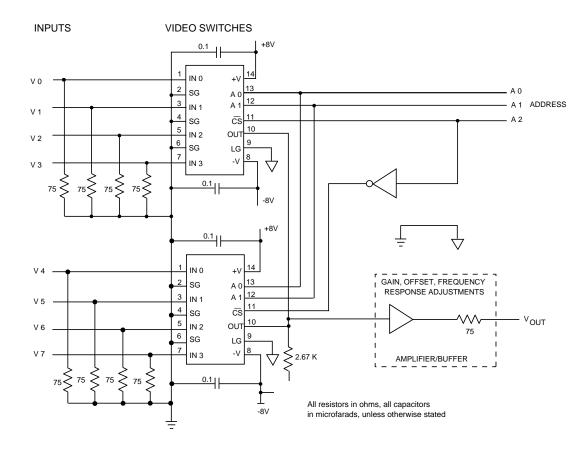

The GX214A is non-inverting. The inputs are buffered and require 75 $\Omega$  line terminating resistors when driven from 75 $\Omega$  cable. The inputs may be driven directly from an amplifier which has low output impedance.

The output of the GX214A must be buffered to drive 7  $\Omega$  lines. The addition of an amplifier/buffer also allows adjustments to be made to the gain, offset and frequency response of the circuit.

Signal Ground (SG) pins 2, 4 and 6 must be joined together and preferably form part of a ground plane. The Signal Ground must also be connected to the  $\pm 8V$  power supply ground. The potential of the Logic Ground (LG) pin 9 can deviate from the Signal Ground by  $\pm 0.5V$  maximum. Alternatively, the signal and logic grounds can be joined together at one point only. An external load current of 2 to 8mA should be supplied from each output bus to negative supply. For most applications a load resistor of  $2.67k\Omega$ , 1% is recommended to minimize offset drift with temperature. In order to improve differential phase and tighten the insertion loss tolerance, an external constant current active load may be substituted for the load resistor. Note however, that since only one GX214A output drives the output bus at any one time, only one external load is needed for the bus.

A typical application is shown below. Two GX214A ICs are paralleled to form an  $8\times1$  crosspoint matrix. The three address lines make use of the A0, A1 and  $\overline{CS}$  inputs. If more than two devices are used in parallel, a decoder is necessary in order to generate the extra address inputs.

Depending on the application and the speed of the logic family used, latches may be required for synchronization where timing delays are critical. The active switching circuitry of the GX214A ensures low crosstalk and high performance over an input voltage range of -1.2 to +5.0 volts.

Fig. 1 8x1 Video Multiplexer Incorporating Two GX214A Devices

\* The power supply pins should be suitably decoupled with at least 0.1μF, high quality capacitors All resistors in ohms, all capacitors in microfarads unless otherwise stated.

The TEST SET UP shown is for INPUT 0 tests. Similar circuitry is used for each input INPUT in order to test FREQUENCY RESPONSE and PHASE DELAY. For OFF-ISOLATION, all switches are disabled (CHIP SELECT = logic 1) and a second enabled GX214A is connected to the output bus. For ALL-HOSTILE CROSSTALK, three OFF switches are driven from the generator and the fourth is terminated with a 75 $\Omega$  resistor. For the DIFFERENTIAL GAIN and PHASE tests, the output is AC coupled to the output amplifier and the input level from the generator is modulated with a step signal varying between 0 volts DC and 0.714 volts DC.

#### CAUTION

ELECTROSTATIC SENSITIVE DEVICES DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

#### DOCUMENT IDENTIFICATION

PRODUCT PROPOSAL

This data has been compiled for market investigation purposes only, and does not constitute an offer for sale.

ADVANCE INFORMATION NOTE

This product is in development phase and specifications are subject to change without notice. Gennum reserves the right to remove the product at any time. Listing the product does not constitute an offer for sale.

PRELIMINARY DATA SHEET

The product is in a preproduction phase and specifications are subject to change without notice.

DATA SHEET

The product is in production. Gennum reserves the right to make changes at any time to improve reliability, function or design, in order to provide the best product possible.

REVISION NOTES .

Block diagram added, new test circuit, revised electrical characteristics, new application circuit, all new response graphs.

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement. © Copyright July 1990 Gennum Corporation. Revision Date: February 1993. All rights reserved. Printed in Canada.