# LM4651 & LM4652 *Overture*™ Audio Power Amplifier 170W Class D Audio Power Amplifier Solution

# **General Description**

The IC combination of the LM4651 driver and the LM4652 power MOSFET provides a high efficiency, Class D subwoofer amplifier solution.

The LM4651 is a fully integrated conventional pulse width modulator driver IC. The IC contains short circuit, under voltage, over modulation, and thermal shut down protection circuitry. It contains a standby function, which shuts down the pulse width modulation and minimizes supply current. The LM4652 is a fully integrated H-bridge power MOSFET IC in a TO-220 power package. Together, these two IC's form a simple, compact high power audio amplifier solution complete with protection normally seen only in Class AB amplifiers. Few external components and minimal traces between the IC's keep the PCB area small and aids in EMI control.

The near rail-to-rail switching amplifier substantially increases the efficiency compared to Class AB amplifiers. This high efficiency solution significantly reduces the heat sink size compared to a Class AB IC of the same power level. This two-chip solution is optimum for powered subwoofers and self powered speakers.

# **Key Specifications**

- Output power into  $4\Omega$  with < 10% THD. 170W (Typ)

- THD at 10W,  $4\Omega$ , 10 500Hz. < 0.3% THD (Typ)

- Maximum efficiency at 125W 85% (Typ)

- Standby attenuation. >100dB (Min)

#### **Features**

- Conventional pulse width modulation.

- Externally controllable switching frequency.

- 50kHZ to 200kHz switching frequency range.

- Integrated error amp and feedback amp.

- Turn-on soft start and under voltage lockout.

- Over modulation protection (soft clipping).

- Short circuit current limiting and thermal shutdown protection.

- 15 Lead TO-220 isolated package.

- Self checking protection diagnostic.

### **Applications**

- Powered subwoofers for home theater and PC's

- Car booster amplifier

- Self-powered speakers

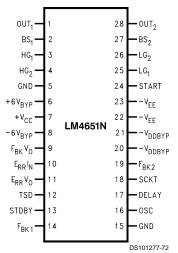

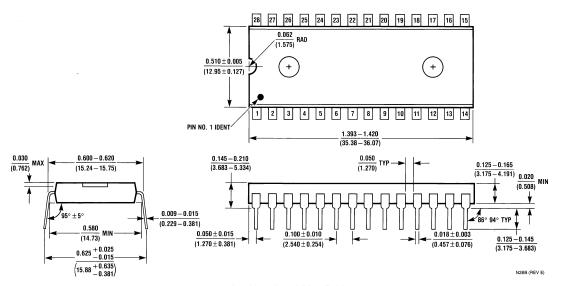

# **Connection Diagrams**

#### LM4651 Plastic Package

Top View Order Number LM4651N See NS Package Number N28B

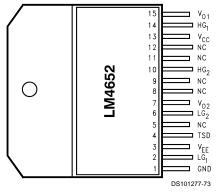

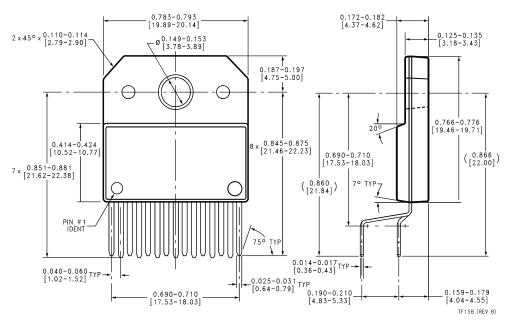

#### LM4652 Plastic Package (Note 8)

Isolated TO-220 Package Order Number LM4652TF See NS Package Number TF15B or Non-Isolated TO-220 Package Order Number LM4652TA See NS Package Number TA15A

Overture® is a registered trademark of National Semiconductor Corporation.

Junction Temperature (Note 6)

N, TA and TF Package (10 seconds)

Soldering Information

Storage Temperature

#### Absolute Maximum Ratings (Notes 1, 2) Operating Ratings (Notes 1, 2) If Military/Aerospace specified devices are required, $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ Temperature Range please contact the National Semiconductor Sales Office/ Supply Voltage |V<sup>+</sup>| + |V<sup>-</sup>| 22V to 44V Distributors for availability and specifications. Supply Voltage Thermal Resistance Output Current (LM4652) 10A LM4651 N Package Power Dissipation (LM4651) (Note 3) 1.5W $\theta JA$ 52°C/W Power Dissipation (LM4652) (Note 3) 32W $\theta$ JC 22°C/W ESD Susceptibility (LM4651) (Note 4) 2000V LM4652 (pins 2,6,10,11) 500V LM4652 TF, TO-220 Package ESD Susceptibility (LM4651) (Note 5) 200V 43°C/W LM4652 (pins 2,6,10,11) 100V 2.0°C/W $\theta$ JC

$\theta JA$

$\theta$ JC

LM4652 T, TO-220 Package

37°C/W

1.0°C/W

### System Electrical Characteristics for LM4651 and LM4652 (Notes 1, 2)

-40°C to + 150°C

150°C

260°C

The following specifications apply for  $+V_{CC} = +20V$ ,  $-V_{EE} = -20V$ ,  $f_{SW} = 125kHz$ ,  $f_{IN} = 100Hz$ ,  $R_L = 4\Omega$ , unless otherwise specified. Typicals apply for  $T_A = 25^{\circ}C$ . For specific circuit values, refer to Figure 1 (Typical Audio Application Circuit).

| Symbol            | Parameter                               | Conditions                                                                                                                                                                                          | LM4651 & LM4652 |          |

|-------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|

| Symbol            | Parameter                               | Conditions                                                                                                                                                                                          | Typical         | Units    |

| I <sub>ca</sub>   | Total Quiescent Power Supply<br>Current | $V_{\text{CIN}}$ = 0V, L $_{\text{O}}$ = 0mA, $ I_{\text{VCC+}} $ + $ I_{\text{VEE-}} $ $R_{\text{DLY}}$ = 0 $\Omega$ $R_{\text{DLY}}$ = 10k $\Omega$                                               | 237<br>124      | mA<br>mA |

| I <sub>STBY</sub> | Standby Current                         | $V_{PIN}13 = 5V$ , Stby: On                                                                                                                                                                         | 17              | mA       |

| A <sub>M</sub>    | Standby Attenuation                     | V <sub>PIN</sub> 13 = 5V, Stby: On                                                                                                                                                                  | >115            | dB       |

|                   |                                         | $R_L = 4\Omega$ , 1% THD                                                                                                                                                                            | 125             | W        |

|                   |                                         | $R_L = 4\Omega$ , 10% THD                                                                                                                                                                           | 155             | W        |

| n                 | Output Bouer (Continuous Average)       | $R_L = 8\Omega$ , 1% THD                                                                                                                                                                            | 75              | W        |

| Po                | Output Power (Continuous Average)       | $R_L = 8\Omega$ , 10% THD                                                                                                                                                                           | 90              | W        |

|                   |                                         | $f_{SW} = 75kHz, R_L = 4\Omega, 1\% THD$                                                                                                                                                            | 135             | W        |

|                   |                                         | $f_{SW} = 75kHz$ , $R_L = 4\Omega$ , 10% THD                                                                                                                                                        | 170             | W        |

| η                 | Efficiency at P <sub>O</sub> = 5W       | $P_O = 5W$ , $R_{DLY} = 5k\Omega$                                                                                                                                                                   | 55              | %        |

| η                 | Efficiency<br>(LM4651 & LM4652)         | P <sub>O</sub> = 125W, THD = 1%                                                                                                                                                                     | 85              | %        |

|                   | Device Dissination                      | P <sub>O</sub> = 125W, THD = 1% (max)                                                                                                                                                               | 22              | W        |

| Pd                | Power Dissipation<br>(LM4651 + LM4652)  | $f_{SW} = 75kHz, P_O = 135W,$<br>THD = 1% (max)                                                                                                                                                     | 22              | W        |

| THD+N             | Total Harmonic Distortion Plus Noise    | 10W, $10Hz \le f_{IN} \le 500Hz$ , $A_V = 18 \text{ dB}$<br>$10Hz \le BW \le 80kHz$                                                                                                                 | 0.3             | %        |

| € <sub>OUT</sub>  | Output Noise                            | A Weighted, no signal, $R_L = 4\Omega$                                                                                                                                                              | 550             | μV       |

| SNR               | Signal to Maine Datio                   | A-Wtg, $P_{out}$ = 125W, $R_L$ $4\Omega$                                                                                                                                                            | 92              | dB       |

|                   | Signal-to-Noise Ratio                   | 22kHz BW, $P_{out}$ = 125W, $R_L$ $4\Omega$                                                                                                                                                         | 89              | dB       |

| V <sub>os</sub>   | Output Offset Voltage                   | $V_{IN} = 0V$ , $I_{O} = 0$ mA, $R_{OFFSET} = 0$ $\Omega$                                                                                                                                           | 0.7             | V        |

| PSRR              | Power Supply Rejection Ratio            | $\begin{aligned} R_L &= 4\Omega, \ 10 \text{Hz} \leq \text{BW} \leq 30 \text{kHz} \\ + V_{\text{CC}_{AC}} &= -V_{\text{EE}_{AC}} = 1 V_{\text{RMS}}, \ f_{\text{AC}} = 120 \text{Hz} \end{aligned}$ | 37              | dB       |

### Electrical Characteristics for LM4651 (Notes 1, 2, 7)

The following specifications apply for  $+V_{CC} = +20V$ ,  $-V_{EE} = -20V$ ,  $f_{SW} = 125$ kHz, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ . For specific circuit values, refer to Figure 1 (Typical Audio Application Circuit).

| Symbol                                            | Parameter                       | Conditions                                                                             | LM4651 |         |     |       |

|---------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------|--------|---------|-----|-------|

| Syllibol                                          | Farameter                       | Conditions                                                                             | Min    | Typical | Max | Units |

| I <sub>cq</sub>                                   | Total Quiescent Current         | LM4652 not connected, $I_O = 0$ mA, $ I_{VCC+}  +  I_{VEE-} $ , $R_{DLY} = 0$ $\Omega$ | 15     | 36      | 45  | mA    |

| Standby V <sub>IL</sub> Standby Low Input Voltage |                                 | Not in Standby Mode                                                                    |        |         | 0.8 | V     |

| V <sub>IH</sub>                                   | Standby High Input Voltage      | In Standby Mode                                                                        | 2.5    | 2.0     |     | V     |

| f                                                 | Switching Frequency Range       | $R_{OSC} = 15k\Omega$                                                                  |        | 65      |     | kHz   |

| I <sub>SW</sub>                                   | Switching Frequency Range       | $R_{OSC} = 0\Omega$                                                                    |        | 200     |     | kHz   |

| f <sub>SWerror</sub>                              | 50% Duty Cycle Error            | $R_{OSC} = 4k\Omega$ , $f_{SW} = 125kHz$                                               |        | 1       | 3   | %     |

| T <sub>dead</sub>                                 | Dead Time                       | $R_{DLY} = 0\Omega$                                                                    |        | 27      |     | ns    |

| T <sub>OverMod</sub>                              | Over Modulation Protection Time | Pulse Width Measured at 50%                                                            |        | 310     |     | ns    |

### Electrical Characteristics for LM4652 (Notes 1, 2, 7)

The following specifications apply for  $+V_{CC} = +20V$ ,  $-V_{EE} = -20V$ , unless otherwise specified. Limits apply for  $T_A = 25$ °C. For specific circuit values, refer to Figure 1 (Typical Audio Application Circuit).

| Cumbal                | Parameter                            | Conditions                                                     | LM4652 |         |     |                 |

|-----------------------|--------------------------------------|----------------------------------------------------------------|--------|---------|-----|-----------------|

| Symbol                | Parameter                            | Conditions                                                     | Min    | Typical | Max | Units           |

| V <sub>(BR)</sub> DSS | Drain-to-Source Breakdown<br>Voltage | VGS = 0                                                        |        | 55      |     | V               |

| I <sub>DSS</sub>      | Drain-to-Source Leakage Current      | $VDS = 44V_{DC}, VGS = 0V$                                     |        | 1.0     |     | mA              |

| VGS <sub>th</sub>     | Gate Threshold Voltage               | $VDS = VGS$ , $ID = 1mA_{DC}$                                  |        | 0.85    |     | V               |

| R <sub>DS(ON)</sub>   | Static Drain-to-Source On Resistance | $VGS = 6V_{DC}, ID = 6A_{DC}$                                  |        | 200     | 300 | mΩ              |

| t <sub>r</sub>        | Rise Time                            | $VGD = 6V_{DC}$ , $VDS = 40V_{DC}$ , $R_{GATE}$<br>= $0\Omega$ |        | 25      |     | ns              |

| t <sub>f</sub>        | Fall Time                            | $VGD = 6V_{DC}$ , $VDS = 40V_{DC}$ , $R_{GATE}$<br>= $0\Omega$ |        | 26      |     | ns              |

| I <sub>D</sub>        | Maximum Saturation Drain Current     | $VGS = 6V_{DC}, VDS = 10V_{DC}$                                | 8      | 10      |     | A <sub>DC</sub> |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 2: All voltages are measured with respect to the GND pin unless otherwise specified.

Note 3: For operating at case temperatures above 25°C, the LM4651 must be de–rated based on a 150°C maximum junction temperature and a thermal resistance of  $\theta_{JA}$  = 62 °C/W (junction to ambient), while the LM4652 must be de–rated based on a 150°C maximum junction temperature and a thermal resistance of  $\theta_{JC}$  = 2.0 °C/W (junction to case) for the isolated package (TF) or a thermal resistance of  $\theta_{JC}$  = 1.0 °C/W (junction to case) for the non-isolated package (T).

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Machine Model, 220pF-240pF discharge through all pins.

Note 6: The operating junction temperature maximum,  $T_{jmax}$  is  $150^{\circ}C.$

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: The LM4652TA package TA15A is a non-isolated package, setting the tab of the device and the heat sink at -V potential when the LM4652 is directly mounted to the heat sink using only thermal compound. If a mica washer is used in addition to thermal compound,  $\theta_{CS}$  (case to sink) is increased, but the heat sink will be isolated from -V.

### Electrical Characteristics for LM4652 (Notes 1, 2, 7) (Continued)

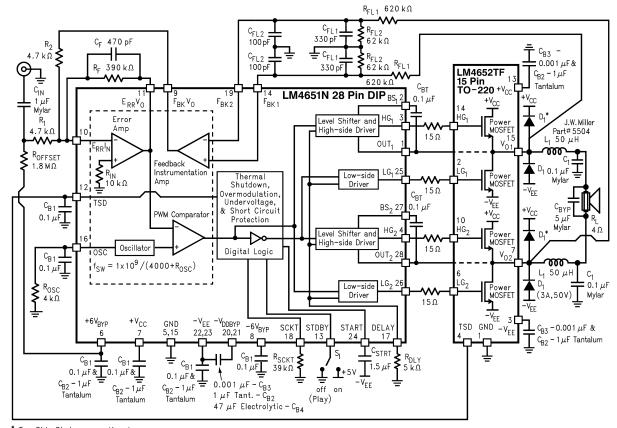

\* Top Side Diodes are optional. Depends on Application.

DS101277-68

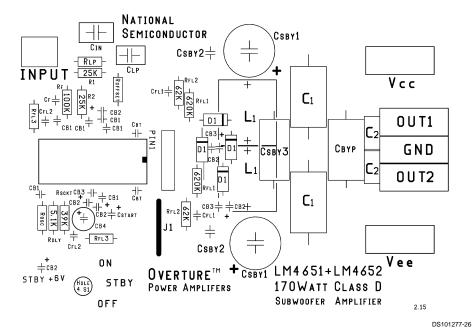

FIGURE 1. Typical Application Circuit and Test Circuit

# LM4651 Pin Descriptions

| Pin No. | Symbol                           | Description                                                                                                                                                                                                          |  |

|---------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | OUT₁                             | The reference pin of the power MOSFET output to the gate drive circuitry.                                                                                                                                            |  |

| 2,27    | BS <sub>1</sub> ,BS <sub>2</sub> | The bootstrap pin provides extra bias to drive the upper gates, HG <sub>1</sub> ,HG <sub>2</sub> .                                                                                                                   |  |

| 3       | HG₁                              | High-Gate #1 is the gate drive to a top side MOSFET in the H-Bridge.                                                                                                                                                 |  |

| 4       | HG <sub>2</sub>                  | High-Gate #2 is the gate drive to a top side MOSFET in the H-Bridge.                                                                                                                                                 |  |

| 5,15    | GND                              | The ground pin for all analog circuitry.                                                                                                                                                                             |  |

| 6       | +6V <sub>BYP</sub>               | The internally regulated positive voltage output for analog circuitry. This pin is available for internal regulator bypassing only.                                                                                  |  |

| 7       | +V <sub>CC</sub>                 | The positive supply input for the IC.                                                                                                                                                                                |  |

| 8       | -6V <sub>BYP</sub>               | The internally regulated negative voltage output for analog circuitry. This pin is available for internal regulator bypassing only.                                                                                  |  |

| 9       | $F_{BK}V_{O}$                    | The feedback instrumentation amplifier output pin.                                                                                                                                                                   |  |

| 10      | $E_RRI_N$                        | The error amplifier inverting input pin. The input audio signal and the feedback signal are summed at this input pin.                                                                                                |  |

| 11      | $E_{RR}V_{O}$                    | The error amplifier output pin.                                                                                                                                                                                      |  |

| 12      | TSD                              | The thermal shut down input pin for the thermal shut down output of the LM4652.                                                                                                                                      |  |

| 13      | STBY                             | Standby function input pin. This pin is CMOS compatible.                                                                                                                                                             |  |

| 14      | FBK₁                             | The feedback instrumentation amplifier pin. This must be connected to the feedback filter from $V_{O1}$ (pin 15 on the LM4652).                                                                                      |  |

| 16      | OSC                              | The switching frequency oscillation pin. Adjusting the resistor from 15.5k $\Omega$ to $0\Omega$ changes the switching frequency from 75kHz to 225kHz.                                                               |  |

| 17      | Delay                            | The dead time setting pin.                                                                                                                                                                                           |  |

| 18      | SCKT                             | Short circuit setting pin. Minimum setting is 10A.                                                                                                                                                                   |  |

| 19      | FBK <sub>2</sub>                 | The feedback instrumentation amplifier pin. This must be connected to the feedback filter from $V_{O2}$ (pin 7 on the LM4652).                                                                                       |  |

| 20,21   | -V <sub>DDBYP</sub>              | The regulator output for digital blocks. This pin is for bypassing only.                                                                                                                                             |  |

| 22,23   | -V <sub>EE</sub>                 | The negative voltage supply pin for the IC.                                                                                                                                                                          |  |

| 24      | START                            | The start up capacitor input pin. This capacitor adjusts the start up time of the diagnostic sequence for the modulator. Refer to <b>Start up Sequence and Timing</b> in the <b>Application Information</b> section. |  |

| 25      | LG₁                              | Low-Gate #1 is the gate drive to a bottom side MOSFET in the H-Bridge.                                                                                                                                               |  |

| 26      | LG <sub>2</sub>                  | Low-Gate #2 is the gate drive to a bottom side MOSFET in the H-Bridge.                                                                                                                                               |  |

| 28      | OUT <sub>2</sub>                 | The reference pin of the power MOSFET output to the gate drive circuitry.                                                                                                                                            |  |

# **LM4652 Pin Descriptions**

| Pin No. | Symbol           | Description                                                                                        |  |

|---------|------------------|----------------------------------------------------------------------------------------------------|--|

| 1       | GND              | A ground reference for the thermal shut down circuitry.                                            |  |

| 2       | LG <sub>1</sub>  | Low-Gate #1 is the gate input to a bottom side MOSFET in the H-Bridge.                             |  |

| 3       | -V <sub>EE</sub> | The negative voltage supply input for the power MOSFET H-Bridge.                                   |  |

| 4       | TSD              | The thermal shut down flag pin. This pin transitions to 6V when the die temperature exceeds 150°C. |  |

| 5       | NC               | No connection                                                                                      |  |

| 6       | LG <sub>2</sub>  | Low-Gate #2 is the gate input to a bottom side MOSFET in the H-Bridge.                             |  |

| 7       | VO <sub>2</sub>  | The switching output pin for one side of the H-Bridge.                                             |  |

| 8       | NC               | No connection.                                                                                     |  |

| 9       | NC               | No connection.                                                                                     |  |

| 10      | HG <sub>2</sub>  | High-Gate #2 is the gate input to a top side MOSFET in the H-Bridge.                               |  |

| 11      | NC               | No connection.                                                                                     |  |

| 12      | NC               | No connection.                                                                                     |  |

| 13      | +V <sub>CC</sub> | The positive voltage supply input for the power MOSFET H-Bridge.                                   |  |

| 14      | HG₁              | High-Gate #1 is the gate input to a top side MOSFET in the H-Bridge.                               |  |

| 15      | VO <sub>2</sub>  | The switching output pin for one side of the H-Bridge.                                             |  |

Note: **NC**, no connect pins are floating pins. It is best to connect the pins to GND to minimize any noise from being coupled into the pins.

# **External Components Description** (Refer to Figure 1)

| Components |                                  | Functional Description                                                                                                                                                                                                                            |  |

|------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.         | R <sub>1</sub>                   | Works with R <sub>2</sub> , R <sub>fl1</sub> and R <sub>fl2</sub> to set the gain of the system. Gain = $[(R_2/R_1) \times ((R_{fl1} + R_{fl2})/R_{fl2}) - (R_2/R_1) + .5]$ .                                                                     |  |

| 2.         | R <sub>2</sub>                   | See description above for R₁.                                                                                                                                                                                                                     |  |

| 3.         | R <sub>f</sub>                   | Sets the gain and bandwidth of the system by creating a low pass filter for the Error Amplifier's feedback with $C_f$ . 3dB pole is at $f_C = 1/(2\pi R_f C_f)$ (Hz).                                                                             |  |

| 4.         | C <sub>f</sub>                   | See description above for R <sub>f</sub> .                                                                                                                                                                                                        |  |

| 5.         | R <sub>fl1</sub>                 | Provides a reduction in the feedback with $R_{fl2}$ . $R_{fl1}$ should be 10 X $R_{fl2}$ minimum to reduce effects on the pole created by $R_{fl2}$ and $C_{fl1}$ . See also note for $R_1$ , $R_2$ for effect on System Gain.                    |  |

| 6.         | R <sub>fl2</sub>                 | $R_{fl2}$ and $C_{fl1}$ creates a low pass filter with a pole at $f_C = 1/(2\pi R_{fl2}C_{fl1})$ (Hz). See also note for $R_1$ , $R_2$ for effect on System Gain.                                                                                 |  |

| 7.         | C <sub>fl1</sub>                 | See description above for R <sub>fl2</sub> .                                                                                                                                                                                                      |  |

| 8.         | R <sub>fl3</sub>                 | Establish the second pole for the low pass filter in the feedback path at $f_C = 1/(2\pi R_{fl3}C_{fl2})$ (Hz).                                                                                                                                   |  |

| 9.         | C <sub>fl2</sub>                 | See description above for R <sub>fl3</sub> .                                                                                                                                                                                                      |  |

| 10.        | L <sub>1</sub>                   | Combined with $C_{BYP}$ creates a 2-pole, low pass output filter that has a -3dB pole at $f_C$ = $1/[2\pi(L_12C_{BYP})_{1/2}]$ (Hz).                                                                                                              |  |

| 11.        | C <sub>1</sub>                   | Filters high frequency noise from the amplifier's output to ground. Recommended value is $0.1\mu F$ to $1\mu F$ .                                                                                                                                 |  |

| 12.        | $C_{byp}$                        | See description for L <sub>1</sub> .                                                                                                                                                                                                              |  |

| 13.        | C <sub>B1</sub> -C <sub>B4</sub> | Bypass capacitors for V <sub>CC</sub> , V <sub>EE</sub> , analog and digital voltages (V <sub>DD</sub> , +6V, -6V). See <b>Supply Bypassing and High Frequency PCB Design</b> in the <b>Application Information</b> section for more information. |  |

| 14.        | B <sub>BT</sub>                  | Provides the bootstrap capacitance for the boot strap pin.                                                                                                                                                                                        |  |

| 15.        | R <sub>DLY</sub>                 | Sets the dead time or break before make to $T_{DLY} = (1.7x10^{-12}) (500 + R_{DLY})$ (seconds).                                                                                                                                                  |  |

| 16.        | $C_{START}$                      | Controls the startup time with $T_{START} = (8.5x10^4) C_{START}$ (seconds).                                                                                                                                                                      |  |

| 17.        | R <sub>SCKT</sub>                | Sets the output short circuit current with $I_{SCKT} = (1x10^5)/(10k\Omega \parallel R_{SCKT})$ (A).                                                                                                                                              |  |

| 18.        | R <sub>OSC</sub>                 | Controls the switching frequency with $f_{SW} = 1 \times 10^9 / (4000 + R_{OSC})$ (Hz).                                                                                                                                                           |  |

| 19.        | D <sub>1</sub>                   | Schottky diode to protect the output MOSFETs from fly back voltages.                                                                                                                                                                              |  |

# External Components Description (Refer to Figure 1) (Continued)

| Components                                                    |                     | Functional Description                                                                                                                   |  |

|---------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 20. C <sub>SBY1</sub> , C <sub>SBY2</sub> , C <sub>SBY3</sub> |                     | Supply de-coupling capacitors. See <b>Supply Bypassing</b> in the <b>Application Information</b> section.                                |  |

| 21.                                                           | R <sub>OFFSET</sub> | Provides a small DC voltage at the input to minimize the output DC offset seen by the load. This also minimize power on pops and clicks. |  |

| 22.                                                           | C <sub>IN</sub>     | Blocks DC voltages from being coupled into the input and blocks the DC voltage created by R <sub>OFFSET</sub> from the source.           |  |

| 23.                                                           | R <sub>gate</sub>   | Slows the rise and fall time of the gate drive voltages that drive the output FET's.                                                     |  |

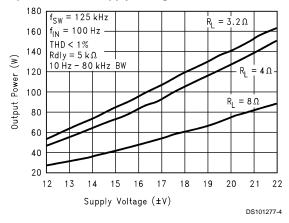

# **Typical Performance Characteristics**

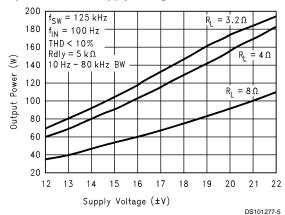

#### **Output Power vs. Supply Voltage**

#### **Output Power vs. Supply Voltage**

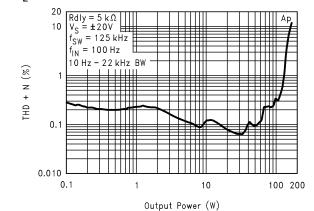

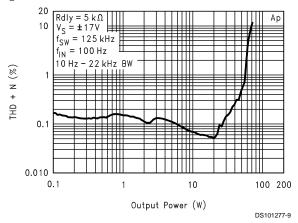

# THD+N vs. Output Power $R_L = 4\Omega$

# THD+N vs. Output Power

DS101277-6

# Typical Performance Characteristics (Continued)

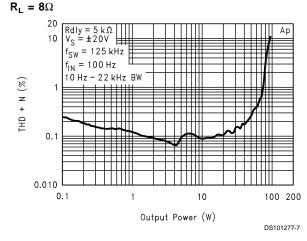

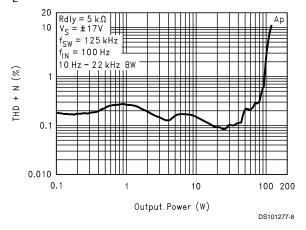

#### THD+N vs. Output Power

$R_L = 4\Omega$

#### THD+N vs. Output Power

$R_L = 8\Omega$

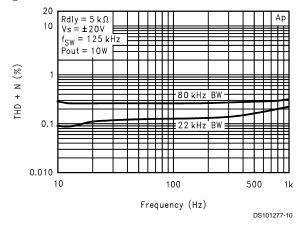

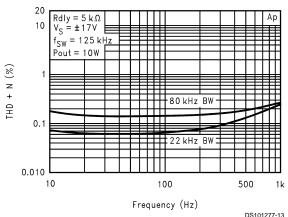

### THD+N vs. Frequency vs. Bandwidth

$R_L = 4\Omega$

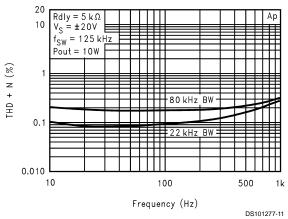

### THD+N vs. Frequency vs. Bandwidth

$R_L = 8\Omega$

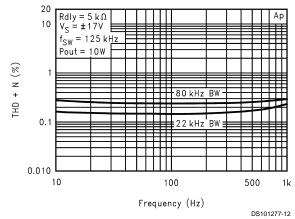

### THD+N vs. Frequency vs. Bandwidth

$R_L = 4\Omega$

#### THD+N vs. Frequency vs. Bandwidth

$R_L = 8\Omega$

# **Typical Performance Characteristics (Continued)**

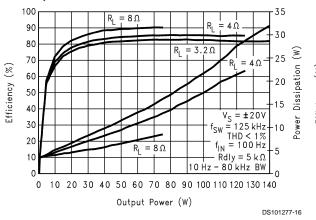

# Power Dissipation & Efficiency vs. Output Power

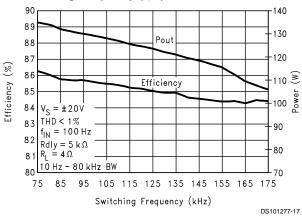

# Clipping Power Point & Efficiency vs. Switching Frequency (f<sub>SW</sub>)

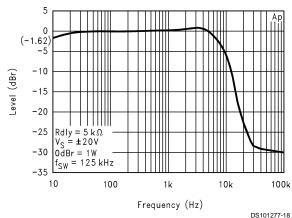

### Frequency Response

$R_L = 4\Omega$

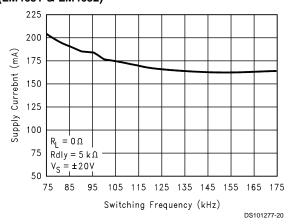

# Supply Current vs. Switching Frequency (LM4651 & LM4652)

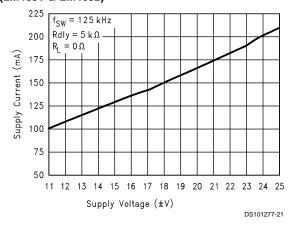

# Supply Current vs. Supply Voltage (LM4651 & LM4652)

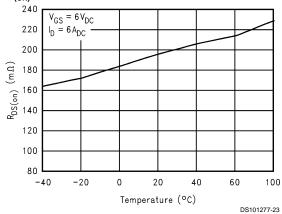

$R_{\mathrm{DS}_{(\mathrm{ON})}}$  vs. Temperature

# **Application Information**

#### **GENERAL FEATURES**

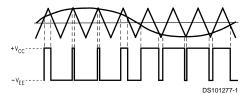

System Functional Information: The LM4651 is a conventional pulse width modulator/driver. As Figure 2 shows the incoming audio signal is compared with a triangle waveform with a much higher frequency than the audio signal (not drawn to scale). The comparator creates a variable duty cycle squarewave. The squarewave has a duty cycle proportional to the audio signal level. The squarewave is then properly conditioned to drive the gates of power MOSFETs in an H-bridge configuration, such as the LM4652. The pulse train of the power MOSFETs are then fed into a low pass filter (usually a LC) which removes the high frequency and delivers an amplified replica of the audio input signal to the load.

FIGURE 2. Conventional Pulse Width Modulation

Standby Function: The standby function of the LM4651 is CMOS compatible, allowing the user to perform a muting of the music as well as turning off all power MOSFETs by shutting down the pulse width waveform. Standby has the added advantage of minimizing the quiescent current. Because standby shuts down the pulse width waveform, the attenuation of the music is complete (>120dB), EMI is minimized, and any output noise is eliminated since there is no modulation waveform. By placing a logic '1' or 5V at pin 13, the standby function will be enabled. A logic '0' or 0V at pin 13 will disable the standby function allowing modulation by the input signal.

**Under Voltage Protection:** The under voltage protection disables the output driver section of the LM4651 while the supply voltage is below  $\pm$  10.5V. This condition can occur as power is first applied or when low line, changes in load resistance or power supply sag occurs. The under voltage protection ensures that all power MOSFETs are off, eliminating any shoot-through current and minimizing pops or clicks during turn-on and turn-off. The under voltage protection gives the digital logic time to stabilize into known states providing a popless turn on.

Start Up Sequence and Self-Diagnostic Timing: The LM4651 has an internal soft start feature (see Figure 3) that ensures reliable and consistent start-up while minimizing turn-on thumps or pops. During the start-up cycle the system is in standby mode. This start-up time is controlled externally by adjusting the capacitance (C<sub>START</sub>) value connected to the START pin. The start-up time can be controlled by the capacitor value connected to the START pin given by Equation (1) or (2):

$$t_{START} = (8.4x10^4)C_{START}$$

(seconds) (1)

$$C_{START} = T_{START}/(8.5x10^4) \quad (Farads) \tag{2}$$

The value of  $C_{START}$  sets the time it takes for the IC to go though the start-up sequence and the frequency that the diagnostic circuitry checks to see if an error condition has been corrected. An Error condition occurs if current limit, thermal shut down, under voltage detection, or standby are sensed. The self-diagnostic circuit checks to see if any one of these error flags has been removed at a frequency set by the  $C_{START}$  capacitor. For example, if the value of  $C_{START}$  is  $10\mu F$  then the diagnostic circuitry will check approximately every second to see if an error condition has been corrected. If the error condition is no longer present, the LM4651/52 will return to normal operation.

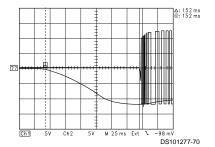

FIGURE 3. Startup Timing Diagram

Current Limiting and Short Circuit Protection: The resistor value connected between the SCKT pin and GND determines the maximum output current. Once the output current is higher than the set limit, the short circuit protection turns all power MOSFETs off. The current limit is set to a minimum of 10A internally but can be increased by adjusting the value of the  $R_{\rm SCKT}$  resistor. Equation (3) shows how to find  $R_{\rm SCKT}$ .

$$I_{SCKT} = 1X10^{5}/(10k\Omega \parallel R_{SCKT}) \qquad (Amps) \qquad (3)$$

This feature is designed to protect the MOSFETs by setting the maximum output current limit under short circuit conditions. It is designed to be a fail-safe protection when the output terminals are shorted or a speaker fails and causes a short circuit condition.

Thermal Protection The LM4651 has internal circuitry (pin 12) that is activated by the thermal shutdown output signal from the LM4652 (pin 4). The LM4652 has thermal shut down circuitry that monitors the temperature of the die. The voltage on the TSD pin (pin 4 of the LM4652) goes high (6V) once the temperature of the LM4652 die reaches 150°C. This pin should be connected directly to the TSD pin of the LM4651 (pin 12). The LM4651 disables the pulse width waveform when the LM4652 transmits the thermal shutdown flag. The pulse width waveform remains disabled until the TSD flag from the LM4652 goes low, signaling the junction temperature has cooled to a safe level.

**Dead Time Setting** The DELAY pin on the LM4651 allows the user to set the amount of dead time or break before make of the system. This is the amount of time one pair of FETs are off before another pair is switched on. Increased dead time will reduce the shoot through current but has the disadvantage of increasing THD. The dead time should be

reduced as the desired bandwidth of operation increases. The dead time can be adjusted with the  $R_{\text{DLY}}$  resistor by Equation (4):

$$T_{DLY} = 1.7x10^{-12} (500 + R_{DLY})$$

(Seconds) (4)

Currently, the recommended value is  $5k\Omega$ .

**Oscillator Control:** The modulation frequency is set by an external resistor,  $R_{\rm OSC}$ , connected between pin 16 and GND. The modulation frequency can be set within the range of 50kHz to 225kHz according to the design requirements. The values of  $R_{\rm OSC}$  and  $f_{\rm OSC}$  can be found by Equation (5) and (6):

$$f_{OSC} = 1x10^9 / (4000 + R_{OSC})$$

(Hz) (5)

$$R_{OSC} = (1x10^9/f_{OSC}) - 4000$$

(0)

Equations (5) and (6) are for  $R_{DLY}=0.$  Using a value of  $R_{DLY}$  greater than zero will increase the value needed for  $R_{OSC}.$  For  $R_{DLY}=5k\Omega,\ R_{OSC}$  will need to be increased by about  $2k\Omega.$  As the graphs show, increasing the switching frequency will reduce the THD but also decreases the efficiency and maximum output power level before clipping. Increasing the switching frequency increases the amount of loss because switching currents lower the efficiency across the output power range. A higher switching frequency also lowers the maximum output power before clipping or the 1% THD point occur.

Over-Modulation Protection: The over-modulation protection is an internally generated fixed pulse width signal that prevents any side of the H-bridge power MOSFETs from remaining active for an extended period of time. This condition can result when the input signal amplitude is higher than the internal triangle waveform. Lack of an over modulation signal can increase distortion when the amplifier's output is clipping. Figure 4 shows how the over modulation protection works.

FIGURE 4. Over Modulation Protection

The over modulation protection also provides a 'soft clip' type response on the top of a sine wave. This minimum pulse time is internally set and cannot be adjusted. As the switching frequency increases this minimum time becomes a higher percentage of the period ( $T_{\text{PERIOD}} = 1/f_{\text{SW}}$ ). Because the over modulation protection time is a higher percentage of the period, the peak output voltage is lower and, therefore, the output power at clipping is lower for the same given supply rails and load.

Feedback Amplifier and Filter: The purpose of the feedback amplifier is to differentially sample the output and provide a single-ended feedback signal to the error amplifier to close the feedback loop. The feedback is taken directly from the switching output before the demodulating LC filter to avoid the phase shift caused by the output filter. The signal fed back is first low pass filtered with a single pole or dual pole RC filter to remove the switching frequency and its harmonics. The differential signal, derived from the bridge output, goes into the high input impedance instrumentation amplifier that is used as the feedback amplifier. The instrumentation amplifier has an internally fixed gain of 1. The use of an instrumentation amplifier serves two purposes. First, it's input are high impedance so it doesn't load down the output stage. Secondly, an IA has excellent common-mode rejection when its gain setting resistors are properly matched. This feature allows the IA to derive the true feedback signal from the differential output, which aids in improving the system performance.

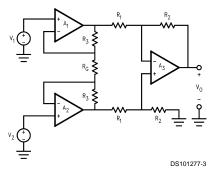

FIGURE 5. Feedback instrumentation Amplifier Schematic

**Error Amplifier:** The purpose of the error amplifier is to sum the input audio signal with the feedback signal derived from the output. This inverting amplifier's gain is externally configurable by resistors Rf and R1. The parallel feedback capacitor and resistor form a low pass filter that limits the frequency content of the input audio signal and the feedback signal. The pole of the filter is set by Equation (7).

$$f_{IP} = 1/(2\pi R_f C_f)$$

(Hz) (7)

On-Board Regulators: The LM4651 has its own internal supply regulators for both analog and digital circuits. Separate ±6V regulators exist solely for the analog amplifiers, oscillator and PWM comparators. A separate voltage regulator powers the digital logic that controls the protection, level shifting, and high-/low-side driver circuits. System performance is enhanced by bypassing each regulator's output. The ±6V regulator outputs, labeled +6V<sub>BYP</sub> (pin 6) and -6V<sub>BYP</sub> (pin 8) should be bypassed to ground. The digital regulator output,  $-V_{DDBYP}$  (pins 20 & 21) should be bypassed to  $-V_{EE}$  (pins 22 & 23). The voltage level of  $-V_{DDBYP}$ should be always be 6V closer to ground than the negative rail,  $-V_{EE}$ . As an example, if  $-V_{EE} = -20V$ , then  $-V_{DDBYP}$ should equal -14V. Recommended capacitor values and type can be found in Figure 1, Typical audio Application Circuit.

#### **APPLICATIONS HINTS**

#### Introduction

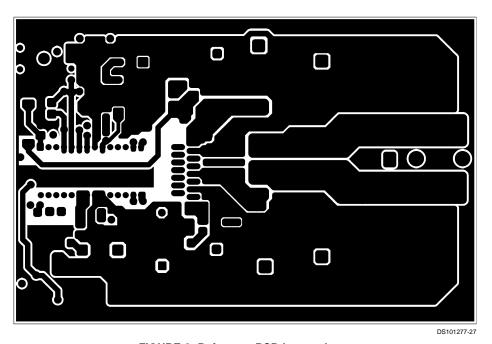

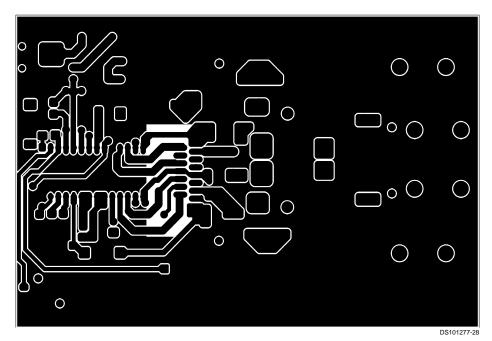

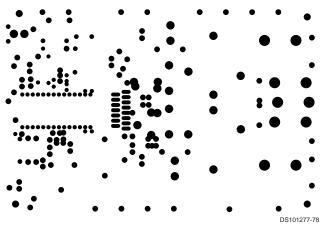

National Semiconductor (NSC) is committed to providing application information that assists our customers in obtaining the best performance possible from our products. The following information is provided in order to support this commitment. The reader should be aware that the optimization of performance was done using a reference PCB designed by NSC and shown in Figure 7 through 11. Variations in performance can occur because of physical changes in the printed circuit board and the application. Therefore, the designer should know that component value changes may be required in order to optimize performance in a given application. The values shown in this data sheet can be used as a starting point for evaluation purposes. When working with high frequency circuits, good layout practices are also critical to achieving maximum performance.

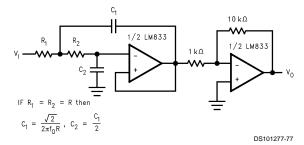

#### Input Pre-Amplifier with Subwoofer Filter

The LM4651 and LM4652 Class D solution is designed for low frequency audio applications where low gain is required. This necessitates a pre–amplifier stage with gain and a low pass audio filter. An inexpensive input stage can be designed using National's LM833 audio operational amplifier and a minimum number of external components. A gain of 10 (20dB) is recommended for the pre–amplifier stage. For a subwoofer application, the pole of the low pass filter is normally set within the range of 60Hz – 180Hz. For a clean sounding subwoofer the filter should be at least a second-order filter to sharply roll off the high frequency audio signals. A higher order filter is recommended for stand-alone self-powered subwoofer applications. Figure 6 shows a simple input stage with a gain of 10 and a second-order low pass filter.

FIGURE 6. Pre-amplifier Stage with Low Pass Filter

#### Supply Bypassing

Correct supply bypassing has two important goals. The first is to ensure that noise on the supply lines does not enter the circuit and become audible in the output. The second is to help stabilize an unregulated power supply and provide current under heavy current conditions. Because of the two different goals multiple capacitors of various types and values are recommended for supply bypassing. For noise de-coupling, generally small ceramic capacitors (.001 $\mu$ F to .1 $\mu$ F) along with slightly larger tantalum or electrolytic capacitors (1 $\mu$ F to 10 $\mu$ F) in parallel will do an adequate job of removing most noise from the supply rails. These capacitors should be placed as close as possible to each IC's supply

pin(s) using leads as short as possible. For supply stabilizing, large electrolytic capacitors  $(3,300\mu F)$  to  $15,000\mu F$ ) are needed. The value used is design and cost dependent.

#### **High Frequency PCB Design**

A double-sided PCB is recommended when designing a class D amplifier system. One side should contain a ground plane with the power traces on the other side directly over the ground plane. The advantage is the parasitic capacitance created between the ground plane and the power planes. This parasitic capacitance is very small (pF) but is the value needed for coupling high frequency noise to ground. At high frequencies, capacitors begin to act more like inductors because of lead and parasitic inductance in the capacitor. For this reason, bypassing capacitors should be surface mount because of their low parasitic inductance. Equation (8) shows how to determine the amount of power to ground plane capacitance.

$$C = \epsilon o \epsilon r A/d$$

(Farads) (8) where  $\epsilon o = 0.22479 p F/in$  and  $\epsilon r = 4.1$

A is the common PCB area and d is the distance between the planes. The designer should target a value of 100pF or greater for both the positive supply to ground capacitance and negative supply to ground capacitance. Signal traces that cross over each other should be laid out at 90° to minimized any coupling.

#### **Output Offset Voltage Minimization**

The amount of DC offset voltage seen at the output with no input signal present is already quite good with the LM4651/ 52. With no input signal present the system should be at 50% duty cycle. Any deviation from 50% duty cycle creates a DC offset voltage seen by the load. To completely eliminate the DC offset, a DC voltage divider can be used at the input to set the DC offset to near zero. This is accomplished by a simple resistor divider that applies a small DC voltage to the input. This forces the duty cycle to 50% when there is no input signal. The result is a LM4651 and LM4652 system with near zero DC offset. The divider should be a  $1.8 M\Omega$ from the +6V output (pin 6) to the input (other side of 25k, R<sub>1</sub>). R<sub>1</sub> acts like the second resistor in the divider. Also use a 1µF input capacitor before R<sub>1</sub> to block the DC voltage from the source. R<sub>1</sub> and the 1µF capacitor create a high pass filter with a 3dB point at 6.35Hz. The value of R<sub>OFFSET</sub> is set according to the application. Variations in switching frequency and supply voltage will change the amount of offset voltage requiring a different value than stated above. The value above (1.8M $\Omega$ ) is for ±20V and a switching frequency of 125kHz.

#### **Output Stage Filtering**

As common with Class D amplifier design, there are many trade-offs associated with different circuit values. The output stage is not an exception. National has found good results with a 50µF inductor and a 5µF Mylar capacitor (see Figure 1, **Typical Audio Application Circuit**) used as the output LC filter. The two-pole filter contains three components; L<sub>1</sub> and C<sub>BYP</sub> because the LM4651 and LM4652 have a bridged output. The design formula for a bridge output filter is  $f_C = 1/[2\pi(L_12C_{BYP})]/2$ .

A common mistake is to connect a large capacitor between ground and each output. This applies only to single-ended

applications. In bridge operation, each output sees  $C_{\text{BYP}}.$  This causes the extra factor of 2 in the formula. The alternative to  $C_{\text{BYP}}$  is a capacitor connected between each output,  $V_{\text{O}},$  and  $V_{\text{O}_2},$  and ground. This alternative is, however, not size or cost efficient because each capacitor must be twice  $C_{\text{BYP}}$ 's value to achieve the same filter cutoff frequency. The additional small value capacitors connected between each output and ground  $(C_1)$  help filter the high frequency from the output to ground . The recommended value for  $C_1$  is 0.1µF to 1µF or 2% to 20% of  $C_{\text{BYP}}.$ '

#### **Modulation Frequency Optimization**

Setting the modulation frequency depends largely on the application requirements. To maximize efficiency and output power a lower modulation frequency should be used. The lower modulation frequency will lower the amount of loss caused by switching the output MOSFETs increasing the efficiency a few percent. A lower switching frequency will also increase the peak output power before clipping because the over modulation protection time is a smaller percentage of the total period. Unfortunately, the lower modulation frequency has worse THD+N performance when the output power is below 10 watts. The recommended switching frequency to balance the THD+N performance, efficiency and output power is 125kHz to 145kHz.

#### THD+N Measurements and Out of Audio Band Noise

THD+N (Total Harmonic Distortion plus Noise) is a very important parameter by which all audio amplifiers are measured. Often it is shown as a graph where either the output power or frequency is changed over the operating range. A very important variable in the measurement of THD+N is the bandwidth limiting filter at the input of the test equipment.

Class D amplifiers, by design, switch their output power devices at a much higher frequency than the accepted audio range (20Hz - 20kHz). Switching the outputs makes the amplifier much more efficient than a traditional Class A/B amplifier. Switching the outputs at high frequency also increases the out-of-band noise. Under normal circumstances this out-of-band noise is significantly reduced by the output low pass filter. If the low pass filter is not optimized for a given switching frequency, there can be significant increase in out-of-band noise.

THD+N measurements can be significantly affected by out-of-band noise, resulting in a higher than expected THD+N measurement. To achieve a more accurate measurement of THD, the bandwidth at the input of the test equipment must be limited. Some common upper filter points are 22kHz, 30kHz, and 80kHz. The input filter limits the noise component of the THD+N measurement to a smaller bandwidth resulting in a more real-world THD+N value.

The output low pass filter does not remove all of the switching fundamental and harmonics. If the switching frequency fundamental is in the measurement range of the test equipment, the THD+N measurement will include switching frequency energy not removed by the output filter. Whereas the switching frequency energy is not audible, it's presence degrades the THD+N measurement. Reducing the bandwidth to 30kHz and 22kHz reveals the true THD performance of

the Class D amplifier. Increasing the switching frequency or reducing the cutoff frequency of the output filter will also reduce the level of the switching frequency fundamental and it's harmonics present at the output. This is caused by a switching frequency that is higher than the output filter cutoff frequency and, therefore, more attenuation of the switching frequency.

In-band noise is higher in switching amplifiers than in linear amplifiers because of increased noise from the switching waveform. The majority of noise is out of band (as discussed above), but there is also an increase of audible noise. The output filter design (order and location of poles) has a large effect on the audible noise level. Power supply voltage also has an effect on noise level. The output filter removes a certain amount of the switching noise. As the supply increases, the attenuation by the output fiter is constant. However, the switching waveform is now much larger resulting in higher noise levels.

# THERMAL CONSIDERATIONS Heat Sinking

The choice of a heat sink for the output FETs in a Class D audio amplifier is made such that the die temperature does not exceed  $T_{\rm JMAX}$  and activate the thermal protection circuitry under normal operating conditions. The heat sink should be chosen to dissipate the maximum IC power which occurs at maximum output power for a given load. Knowing the maximum output power, the ambient temperature surrounding the device, the load and the switching frequency, the maximum power dissipation can be calculated. The additional parameters needed are the maximum junction temperature and the thermal resistance of the IC package  $(\theta_{\rm JC},$  junction to case), both of which are provided in the **Absolute Maximum Ratings** and **Operating Ratings** sections above.

It should be noted that the idea behind dissipating the power within the IC is to provide the device with a low resistance to convection heat transfer such as a heat sink. Convection cooling heat sinks are available commercially and their manufacturers should be consulted for ratings. It is always safer to be conservative in thermal design.

Proper IC mounting is required to minimize the thermal drop between the package and the heat sink. The heat sink must also have enough metal under the package to conduct heat from the center of the package bottom to the fins without excessive temperature drop. A thermal grease such as Wakefield type 120 or Thermalloy Thermacote should be used when mounting the package to the heat sink. Without some thermal grease, the thermal resistance  $\theta_{CS}$  (case to sink) will be no better than 0.5°C/W, and probably much worse. With the thermal grease, the thermal resistance will be 0.2°C/W or less. It is important to properly torque the mounting screw. Over tightening the mounting screw will cause the package to warp and reduce the contact area with the heat sink. It can also crack the die and cause failure of the IC. The recommended maximum torque applied to the mounting screw is 40 inch-lbs. or 3.3 foot-lbs.

#### **Determining Maximum Power Dissipation**

Power dissipation within the integrated circuit package is a very important parameter. An incorrect maximum power dissipation ( $P_D$ ) calculation may result in inadequate heat sinking, causing thermal shutdown circuitry to operate intermittently. There are two components of power dissipation in a class D amplifier. One component of power dissipation in the

LM4652 is the  $R_{DS(ON)}$  of the FET times the RMS output current when operating at maximum output power. The other component of power dissipation in the LM4652 is the switching loss. If the output power is high enough and the DC resistance of the filter coils is not minimized then significant loss can occur in the output filter. This will not affect the power dissipation in the LM4652 but should be checked to be sure that the filter coils with not over heat.

The first step in determining the maximum power dissipation is finding the maximum output power with a given voltage and load. Refer to the graph **Output Power verses Supply Voltage** to determine the output power for the given load and supply voltage. From this power, the RMS output current can be calculated as  $I_{\rm OUTRMS} = {\rm SQRT}(P_{\rm OUT}/R_{\rm L})$ . The power dissipation caused by the output current is  $P_{\rm DOUT} = (I_{\rm OUTRMS})^2 * (2 * R_{\rm DS_{(ON)}})$ . The value for  $R_{\rm DS_{(ON)}}$  can be found from the **Electrical Characteristics for the LM4652** table above. The percentage of loss due to the switching is calculated by Equation (9):

$$%LOSS_{SWITCH} = (t_r + t_f + T_{OVERMOD}) * f_{SW}$$

(9)

$t_r$ ,  $t_f$  and  $T_{OVERMOD}$  can be found in the Electrical Characteristic for the LM4651 and Electrical Characteristic for the LM4652 sections above. The system designer determines the value for  $f_{SW}$  (switching frequency). Power dissipation caused by switching loss is found by Equation (10).  $P_{OUTMAX}$  is the 1% output power for the given supply voltage and the load impedance being used in the application.  $P_{OUTMAX}$  can be determined from the graph Output Power vs. Supply Voltage in the Typical Performance Characteristics section above.

$$P_{DSWITCH} = (\%LOSS_{SWITCH} * P_{OUTMAX}) / (1-\%LOSS_{SWITCH}) (Watts) (10)$$

$P_{DMAX}$  for the LM4652 is found by adding the two components ( $P_{DSWITCH} + P_{DOUT}$ ) of power dissipation together.

#### **Determining the Correct Heat Sink**

Once the LM4652's power dissipation known, the maximum thermal resistance (in °C/W) of a heat sink can be calculated. This calculation is made using Equation (11) and is based on the fact that thermal heat flow parameters are analogous to electrical current flow properties.

$$P_{DMAX} = (T_{JMAX} - T_{AMBIENTMAX}) / \theta_{JA} \quad (Watts) \quad (11)$$

$$Where \theta_{JA} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

Since we know  $\theta_{JC}$ ,  $\theta_{CS}$ , and  $T_{JMAX}$  from the **Absolute Maximum Ratings** and **Operating Ratings** sections above (taking care to use the correct  $\theta_{JC}$  for the LM4652 depending on which package type is being used in the application) and have calculated  $P_{DMAX}$  and  $T_{AMBIENTMAX}$ , we only need  $\theta_{SA}$ , the heat sink's thermal resistance. The following equation is derived from Equation (11):

$$\theta_{SA} = [(T_{JMAX} - T_{AMBIENTMAX}) / P_{DMAX}] - \theta_{JC} - \theta_{CS}$$

Again, it must be noted that the value of  $\theta_{SA}$  is dependent upon the system designer's application and its corresponding parameters as described previously. If the ambient temperature surrounding the audio amplifier is higher than  $T_{\mathsf{AMBIENTMAX}}$ , then the thermal resistance for the heat sink, given all other parameters are equal, will need to be lower.

#### Example Design of a Class D Amplifier

The following is an example of how to design a class D amplifier system for a power subwoofer application utilizing the LM4651 and LM4652 to meet the design requirements listed below:

| • | Output Power, 1% THD   | 125W         |

|---|------------------------|--------------|

| • | Load Impedance         | $4\Omega$    |

| • | Input Signal level     | 3V RMS (max) |

| • | Input Signal Bandwidth | 10Hz – 150Hz |

| • | Ambient Temperature    | 50°C (max)   |

|   |                        |              |

#### **Determine the Supply Voltage**

From the graph **Output Power verses Supply voltage at 1% THD** the supply voltage needed for a 125 watt,  $4\Omega$  application is found to be  $\pm 20$ V.

#### Determine the Value for Rosc (Modulation Frequency)

The oscillation frequency is chosen to obtain a satisfactory efficiency level while also maintaining a reasonable THD performance. The modulation frequency can be chosen using the Clipping Power Point and Efficiency verses Switching Frequency graph. A modulation frequency of 125kHz is found to be a good middle ground for THD performance and efficiency. The value of the resistor for  $R_{\rm OSC}$  is found from Equation (6) to be 3.9 k $\Omega$ .

#### Determine the Value for R<sub>SCKT</sub> (Circuit Limit)

The current limit is internally set as a failsafe to 10 amps. The inductor ripple current and the peak output current must be lower than 10 amps or current limit protection will turn on. A typical  $4\Omega$  load driven by a filter using  $50\mu H$  inductors does not require more than 10A. The current limit will have to be increased when loads less than  $4\Omega$  are used to acheive higher output power. With  $R_{SCKT}$  equal to  $100k\Omega$ , the current limit is 10A

#### Determine the Value for R<sub>DLY</sub> (Dead Time Control)

The delay time or dead time is set to the recommended value so  $R_{\rm DLY}$  equals  $5 k \Omega.$  If a higher bandwidth of operation is desired,  $R_{\rm DLY}$  should be a lower value resistor. If a zero value for  $R_{\rm DLY}$  is desired, connect the LM4651's pin 17 to GND.

# Determine the Value of $L_1$ , $C_{BYP}$ , $C_1$ , $R_{fl1}$ $R_{fl2}$ , $C_{fl1}$ $C_{fl2}$ , $R_f$ , $C_f$ (the Output and Feedback Filters)

All component values show in *Figure 1* **Typical Audio Application Circuit**, are optimized for a subwoofer application. Use the following guidelines when changing any component values from those shown. The frequency response of the output filter is controlled by  $L_1$  and  $C_{\rm BYP}$ . Refer to the **Application Information** section titled **Output Stage Filtering** for a detailed explanation on calculating the correct values for  $L_1$  and  $C_{\rm BYP}$ .

$C_1$  should be in the range of 0.1 $\mu$ F to 1 $\mu$ F or 2 - 20% of  $C_{BYP}$ .  $R_{fl1}$  and  $R_{fl2}$  are found by the ratio  $R_{fl1}$  = 10 $R_{fl2}$ .

A lower ratio can be used if the application is for lower output voltages than the 125Watt,  $4\Omega$  solution show here.

The feedback RC filter's pole location should be higher than the output filter pole. The reason for two capacitors in parallel instead of one larger capacitor is to reduce the possible EMI from the feedback traces.  $C_{\rm fl1}$  is placed close as possible to the output of the LM4652 so that an audio signal is present on the feedback trace instead of a high frequency square wave.  $C_{\rm fl2}$  is then placed as close as possible to the feedback inputs (pins 14, 19) of the LM4651 to filter off any noise picked up by the feedback traces. The combination lowers EMI and provides a cleaner audio feedback signal to the LM4651.  $R_{\rm f}$  should be in range of  $100{\rm k}\Omega$  to  $1{\rm M}\Omega$ .  $C_{\rm f}$  controls the bandwidth of the error signal and should be in the range of  $100{\rm pF}$  to  $470{\rm pF}$ .

#### Determine the Value for $C_{START}$ (Start Up Delay)

The start-up delay is chosen to be 1 second to ensure minimum pops or clicks when the amplifier is powered up. Using Equation (2), the value of  $C_{START}$  is 11.7 $\mu$ F. A standard value of  $10\mu$ F is used.

#### Determine the Value of Gain, R<sub>1</sub>, and R<sub>2</sub>

The gain is set to produce a 125W output at no more than 1% distortion with a  $3V_{RMS}$  input. A dissipation of 125W in a  $4\Omega$  load requires a 22.4V $_{RMS}$  signal. To produce this output signal, the LM4651/LM4652 amplifier needs an overall closed-loop gain of 22.4V $_{RMS}/3V_{RMS}$ , or 7.5V/V (17.5db). Equation (12) shows all the variables that affect the system gain.

Gain =

$$[(R_2/R_1) \times ((R_{fl1} + R_{fl2})/R_{fl2}) - (R_2/R_1) + .5].(3)$$

The values for  $R_{\rm fl1},\,R_{\rm fl2},\,{\rm and}\,R_{\rm f}$  were found in the <code>Determine</code> the <code>Value</code> of the <code>Filters</code> section above. Therefore,  $R_{\rm fl1}=620k\Omega,\,R_{\rm fl2}=62k\Omega$  and  $R_{\rm f}=390k\Omega.$  The value of  $V_{\rm CC}$  was also found as the first step in this example to be  $\pm 20V.$  Inserting these values into equation (12) and reducing gives the equation below:

$$R_2 = .7R_1 \tag{4}$$

The input resistance is desired to be  $20k\Omega$  so  $R_1$  is set to  $20k\Omega$ .  $R_2$  is then found to be  $14k\Omega$ .

Lowering  $R_2$  directy affects the noise of the system. Changing  $R_1$  to increase gain with the lower value for  $R_2$  has very little affect on the noise level. The percent change in noise is about what whould be expected with a higher gain. The drawback to a lower  $R_1$  value is a larger  $C_{\text{IN}}$  value, necessary to properly couple the lowest desired signal frequencies. If a  $20k\Omega$  input impedance is not required, then the recommended values shown in Figure 1, Typical Audio Application Circuit should be used: with  $R_1$ 's value set to  $4.7k\Omega$  and  $R_2$ 's value set to  $3.5k\Omega$  for a gain 7.5V/V.

#### **Determine the Needed Heat Sink**

The only remaining design requirement is a thermal design that prevents activating the thermal protection circuitry. Use Equations (9) - (11) to calculate the amount of power dissipation for the LM4652. The appropriate heat sink size, or thermal resistance in °C/W, will then be determined.

Equation (9) determines the percentage of loss caused by the switching. Use the typical values given in the **Electrical Characteristics for the LM4651** and **Electrical Characteristics for the LM4652** tables for the rise time, fall time and over modulation time:

This switching loss causes a maximum power dissipation, using Equation (10), of:

$$P_{DSWITCH} = (5.0\% * 125W) / (1-5.0\%)$$

$P_{DSWITCH} = 6.6W$

Next the power dissipation caused by the  $R_{\mathrm{DS}(\mathrm{ON})}$  of the output FETs is found by multiplying the output current times the  $R_{\mathrm{DS}(\mathrm{ON})}.$  Again, the value for  $R_{\mathrm{DS}(\mathrm{ON})}$  is found from the **Electrical Characteristics for the LM4652** table above. The value for  $R_{\mathrm{DS}(\mathrm{ON})}$  at  $100^{\circ}\text{C}$  is used since we are calculating the maximum power dissipation.

$$I_{OUTRMS} = SQRT(125watts/4\Omega) = 5.59 \text{ amps}$$

$$P_{RDS(ON)} = (5.59A)^2 * (0.230\Omega^*2)$$

$$P_{RDS(ON)} = 14.4W$$

The total power dissipation in the LM4652 is the sum of these two power losses giving:

$$P_{DTOTAL} = 6.6W + 14.4W = 21W$$

The value for Maximum Power Dissipation given in the **System Electrical Characteristics for the LM4651 and LM4652** is 22 watts. The difference is due to approximately 1 watt of power loss in the LM4651. The above calculations are for the power loss in the LM4652.

Lastly, use Equation (11) to determine the thermal resistance of the LM4652's heat sink. The values for  $\theta_{JC}$  and  $T_{JMAX}$  are found in the **Operating Ratings** and the **Absolute Maximum Ratings** section above for the LM4652. The value of  $\theta_{JC}$  is 2°C/W for the isolated (TF) package or 1°C/W for the non-isolated (T) package. The value for  $T_{JMAX}$  is 150°C. The value for  $\theta_{CS}$  is set to 0.2°C/W since this is a reasonable value when thermal grease is used. The maximum ambient temperature from the design requirements is 50°. The value of  $\theta_{SA}$  for the isolated (TF) package is:

$$\theta_{SA} = [(150^{\circ}C - 50^{\circ}C)/21W] - 2^{\circ}C/W - 0.2^{\circ}C/W$$

$\theta_{SA} = 2.5^{\circ}C/W$

and for the non-isolated (T) package without a mica washer to isolate the heat sink from the package:

$$\theta_{SA} = [(150^{\circ}C - 50^{\circ}C)/21W] - 1^{\circ}C/W - 0.2^{\circ}C/W$$

$$\theta_{SA} = 3.5^{\circ}C/W$$

To account for the use of a mica washer simply subtract the thermal resistance of the mica washer from  $\theta_{\text{SA}}$  calculated above

# **Recommendations for Critical External Components**

| Circuit<br>Symbol                 | Suggested<br>Value | Suggested Type                                             | Supplier/Contact Information                                                      | Supplier Part<br>#       |

|-----------------------------------|--------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|

| C <sub>fl1</sub>                  | 330pF              | Ceramic Disc                                               |                                                                                   |                          |

| C <sub>fl2</sub>                  | 100pF              | Ceramic Disc                                               |                                                                                   |                          |

| C <sub>f</sub>                    | 470pF              | Ceramic Disc                                               |                                                                                   |                          |

| C <sub>B2</sub>                   | 1µF                | Resin Dipped Solid Tantalum                                |                                                                                   |                          |

| C <sub>B1</sub> & C <sub>BT</sub> | 0.1µF              | Monolithic Ceramic                                         |                                                                                   |                          |

| C <sub>B3</sub>                   | 0.001µF            | Monolithic Ceramic                                         |                                                                                   |                          |

| C <sub>1</sub> & C <sub>BYP</sub> | 5μF - 10μF         | Metalized Polypropylene or<br>Polyester Film               | Bishop Electronics Corp.<br>(562) 695 - 0446<br>http://www.bishopelectronics.com/ | BEC-9950<br>A11A-50V     |

| C <sub>1</sub> & C <sub>BYP</sub> | 5μF - 10μF         | Metalized Polypropylene or<br>Polyester Film               | Nichicon Corp.<br>(847) 843-7500<br>http://www.nichicon-us.com/                   | QAF2Exx<br>or<br>QAS2Exx |

| D <sub>1</sub>                    | 3A, 50V            | Fast Schottky Diode                                        |                                                                                   |                          |

| L <sub>1</sub>                    | 47μH, 5A           | High Saturation Open Core<br>(Vertical Mount Power Chokes) | CoilCraft<br>(847) 639-6400<br>http://www.coilcraft.com/                          | PCV-0-<br>473-05         |

| L <sub>1</sub>                    | 50μH, 5.6A         | High Saturation Flux Density<br>Ferrite Rod                | J.W. Miller<br>(310) 515-1720<br>http://www.jwmiller.com/                         | 5504                     |

| L <sub>1</sub>                    | 68μH, 7.3A         | High Saturation Flux Density<br>Ferrite Rod                | J.W. Miller<br>(310) 515-1720<br>http://www.jwmiller.com/                         | 5512                     |

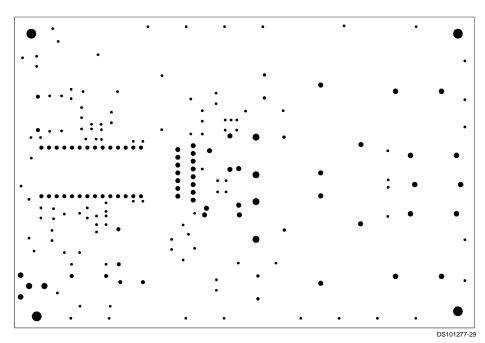

FIGURE 7. Reference PCB silkscreen layer

FIGURE 8. Reference PCB top layer

FIGURE 9. Reference PCB bottom layer

FIGURE 10. Reference PCB top layer solder mask

FIGURE 11. Reference PCB bottom layer solder mask

# Physical Dimensions inches (millimeters) unless otherwise noted

#### Order Number LM4651N NS Package Number N28B

Order Number LM4652TF NS Package Number TF15B

#### **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Americas Tel: 1-800-272-9959 Fax: 1-800-737-7018

Email: support@nsc.com www.national.com

**National Semiconductor**

Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

Email: ap.support@nsc.com

National Semiconductor Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.