SEMICONDUCTOR

# DM74ALS374 Octal 3-STATE D-Type Edge-Triggered Flip-Flop

### **General Description**

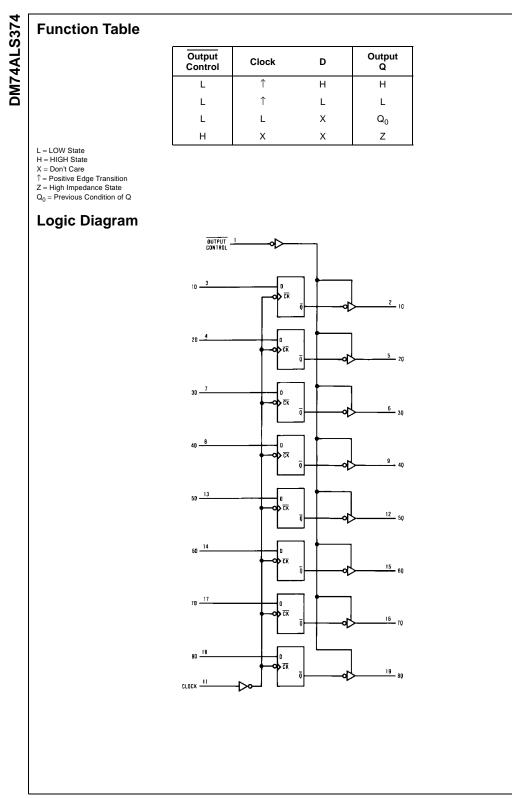

This 8-bit register features totem-pole 3-STATE outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. The high-impedance state and increased high-logic-level drive provides this register with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for interface or pull-up components. It is particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

The eight flip-flops of the DM74ALS374 are edge-triggered D-type flip-flops. On the positive transition of the clock, the Q outputs will be set to the logic states that were set up at the D inputs.

A buffered output control input can be used to place the eight outputs in either a normal logic state (HIGH or LOW logic levels) or a high-impedance state. In the high-impedance state the outputs neither load nor drive the bus lines significantly.

The output control does not affect the internal operation of the flip-flops. That is, the old data can be retained or new data can be entered even while the outputs are OFF.

#### Features

Switching specifications at 50 pF

Package Description

- Switching specifications guaranteed over full temperature and V<sub>CC</sub> range

- Advanced oxide-isolated, ion-implanted Schottky TTL process

September 1986

Revised February 2000

- Functionally and pin-for-pin compatible with LS TTL counterpart

- Improved AC performance over DM74LS374 at approximately half the power

- 3-STATE buffer-type outputs drive bus lines directly

| Order Number  | Package Number |            |

|---------------|----------------|------------|

| DM74AI S374WM | M20B           | 20-Lead Sn |

| Device also available is | Trans and Dard Onesited |                                                                           |

|--------------------------|-------------------------|---------------------------------------------------------------------------|

| DM74ALS374N              | N20A                    | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |

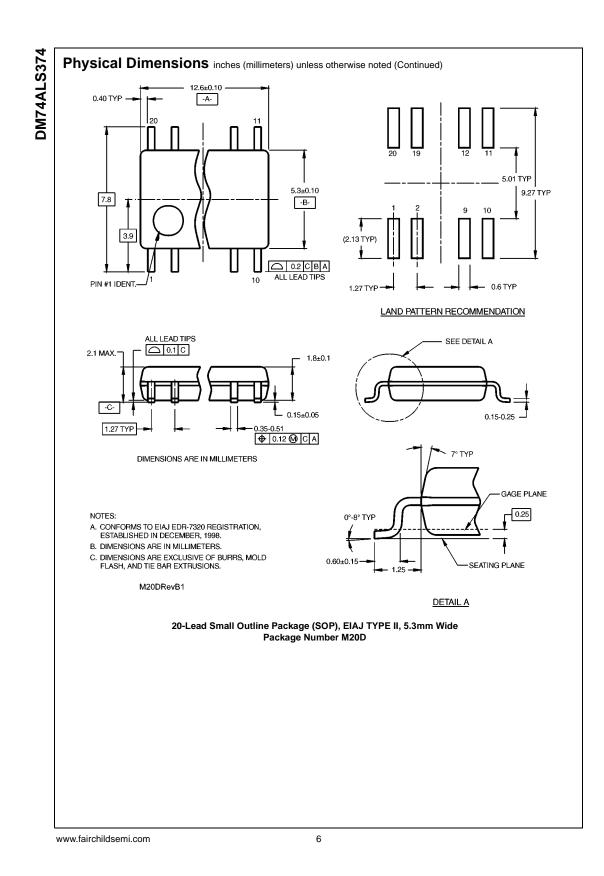

| DM74ALS374SJ             | M20D                    | 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide             |

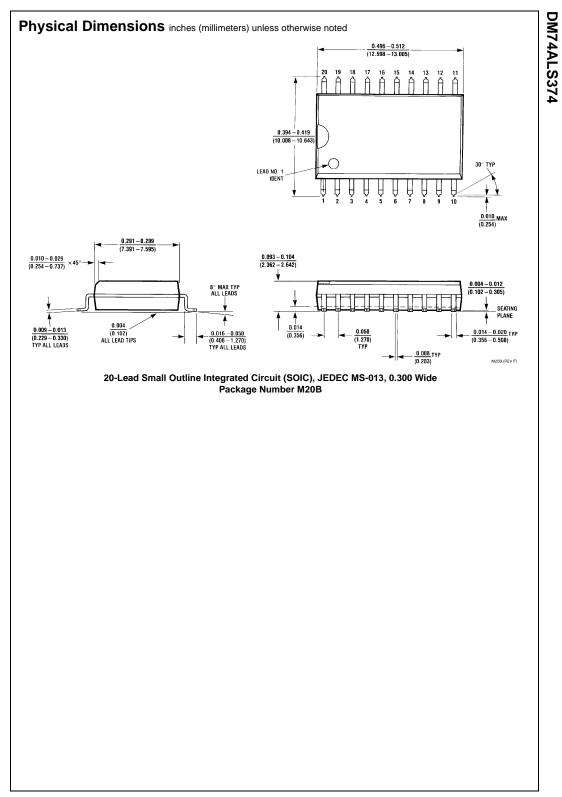

| DM74ALS374WM             | M20B                    | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|                          |                         |                                                                           |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

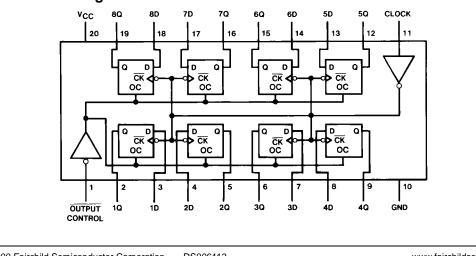

#### **Connection Diagram**

**Ordering Code:**

www.fairchildsemi.com

www.fairchildsemi.com

2

#### Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Voltage Applied to Disabled Output   | 5.5V                              |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature Range (Note 2)   | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Typical θ <sub>JA</sub>              |                                   |

| N Package                            | 60.0°C/W                          |

| M Package                            | 79.0°C/W                          |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 2: This product meets application requirements of 500 temperature cycles from -65°C to +150°C.

#### **Recommended Operating Conditions**

| Symbol          | Parameter                                                                |       | Min | Nom | Max              | Units           |

|-----------------|--------------------------------------------------------------------------|-------|-----|-----|------------------|-----------------|

| V <sub>CC</sub> | Supply Voltage                                                           | Itage |     | 5   | 5.5              | V               |

| VIH             | HIGH Level Input Voltage                                                 |       | 2   |     |                  | V               |

| V <sub>IL</sub> | LOW Level Input Voltage                                                  |       |     |     | 0.8              | V               |

| он              | HIGH Level Output Current<br>LOW Level Output Current<br>Clock Frequency |       |     |     | -2.6<br>24<br>35 | mA<br>mA<br>MHz |

| OL              |                                                                          |       |     |     |                  |                 |

| fclock          |                                                                          |       | 0   |     |                  |                 |

| tw              | Width of Clock Pulse                                                     | HIGH  | 14  |     |                  | ns              |

|                 |                                                                          | LOW   | 14  |     |                  | ns              |

| ้รบ             | Data Setup Time (Note 3)                                                 |       | 10↑ |     |                  | ns              |

| н               | Data Hold Time (Note 3)                                                  |       | 0↑  |     |                  | ns              |

| T <sub>A</sub>  | Free Air Operating Temperature                                           |       | 0   |     | 70               | °C              |

## **DC Electrical Characteristics**

| Symbol           | Parameter                  | Conditions                            |                                       | Min                 | Тур  | <b>Max</b><br>-1.5 | Units<br>V |

|------------------|----------------------------|---------------------------------------|---------------------------------------|---------------------|------|--------------------|------------|

| V <sub>IK</sub>  | Input Clamp Voltage        | $V_{CC} = 4.5V, I_I = -18 \text{ mA}$ | $V_{CC} = 4.5V, I_I = -18 \text{ mA}$ |                     |      |                    |            |

| V <sub>OH</sub>  | HIGH Level Output          | $V_{CC} = 4.5V$                       | I <sub>OH</sub> = Max                 | 2.4                 | 3.2  |                    | V          |

|                  | Voltage                    | $V_{CC} = 4.5V$ to 5.5V               | I <sub>OH</sub> = -400 μA             | V <sub>CC</sub> – 2 |      |                    | V          |

| V <sub>OL</sub>  | LOW Level Output           | $V_{CC} = 4.5V$                       | I <sub>OL</sub> = 12 mA               |                     | 0.25 | 0.4                | V          |

|                  | Voltage                    |                                       | I <sub>OL</sub> = 24 mA               |                     | 0.35 | 0.5                | V          |

| l                | Input Current @ Max.       | $V_{CC} = 5.5V, V_{IH} = 7V$          | 1                                     |                     |      |                    |            |

|                  | Input Voltage              |                                       |                                       |                     |      | 0.1                | mA         |

| Ін               | HIGH Level Input Current   | $V_{CC} = 5.5V, V_{IH} = 2.7V$        |                                       |                     |      | 20                 | μΑ         |

| IIL              | LOW Level Input Current    | $V_{CC} = 5.5V, V_{IL} = 0.4V$        |                                       |                     |      | -0.2               | mA         |

| I <sub>O</sub>   | Output Drive Current       | $V_{CC} = 5.5V$                       | V <sub>O</sub> = 2.25V                | -30                 |      | -112               | mA         |

| I <sub>OZH</sub> | OFF-State Output Current,  | $V_{CC} = 5.5V, V_{O} = 2.7V$         | 1                                     |                     |      | 20                 |            |

|                  | HIGH Level Voltage Applied |                                       |                                       |                     |      | 20                 | μA         |

| I <sub>OZL</sub> | OFF-State Output Current,  | $V_{CC} = 5.5V, V_{O} = 0.4V$         |                                       |                     |      | 00                 |            |

|                  | LOW Level Voltage Applied  |                                       |                                       |                     |      | -20                | μA         |

| I <sub>CC</sub>  | Supply Current             | $V_{CC} = 5.5V$                       | Outputs HIGH                          |                     | 11   | 19                 | mA         |

|                  |                            | Outputs Open                          | Outputs LOW                           |                     | 19   | 28                 | mA         |

|                  |                            |                                       | Outputs Disabled                      |                     | 20   | 31                 | mA         |

www.fairchildsemi.com

# DM74ALS374

| Symbol           | Parameter                | Conditions                     | From    | То     | Min | Max | Units |

|------------------|--------------------------|--------------------------------|---------|--------|-----|-----|-------|

| f <sub>MAX</sub> | Maximum Clock Frequency  | V <sub>CC</sub> = 4.5V to 5.5V |         |        | 35  |     | MHz   |

| t <sub>PLH</sub> | Propagation Delay Time   | $R_L = 500\Omega$              | Clock   | Any O  | 3   | 12  | ns    |

|                  | LOW-to-HIGH Level Output | $C_L = 50 \text{ pF}$          | CIUCK   | Any Q  | 3   | 12  | 115   |

| t <sub>PHL</sub> | Propagation Delay Time   |                                | Clock   | Any Q  | 5   | 16  | ns    |

|                  | HIGH-to-LOW Level Output |                                | CIUCK   | Ally Q | 5   | 10  | 115   |

| . 2.1            | Output Enable Time       |                                | Output  | Any Q  | 5   | 17  | ns    |

|                  | to HIGH Level Output     |                                | Control | Ally Q | 5   | 17  | 115   |

| t <sub>PZL</sub> | Output Enable Time       |                                | Output  | Any Q  | 7   | 18  | ns    |

|                  | to LOW Level Output      |                                | Control | Ally Q | '   | 10  | 115   |

| 1112             | Output Disable Time      |                                | Output  | Any Q  | 2   | 10  | ns    |

|                  | from HIGH Level Output   |                                | Control |        | 2   | 10  | 115   |

| t <sub>PLZ</sub> | Output Disable Time      |                                | Output  | Anv    | 3   | 18  |       |

|                  | from LOW Level Output    |                                | Control | Any Q  | 3   | 18  | ns    |

www.fairchildsemi.com

www.fairchildsemi.com

5