# FX803 Audio Signalling Processor

# **FX803 Audio Signalling Processor**

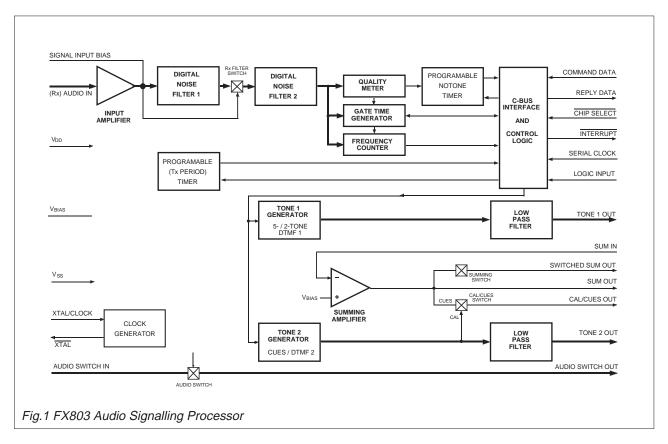

As part of the DBS 800 System, this audio signalling processor will provide an inband tone signalling facility for PMR radio systems. Signalling systems supported include Selcall (CCIR, ZVEI I, II and III, EEA), 2-Tone Selcall and Dual Tone Multi-Frequency (DTMF) encode.

Using a non-predictive tone decoder and versatile encoders gives the FX803 the capability to work in any standard or non-standard tone system.

This is a full-duplex device consisting of:

- Two individual tone generators and a programmable (Tx) period timer.

- A tone decoder with programmable Notone Timer.

- An on-chip summing amplifier.

For use with Single Tone or Selective Call systems.

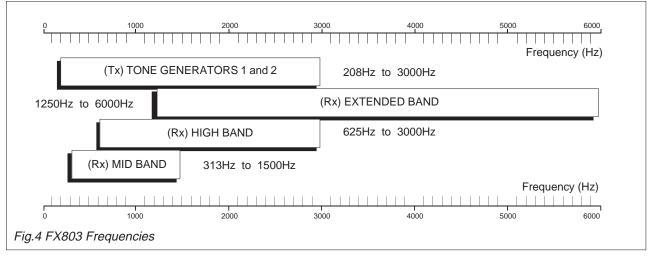

Under the control of the  $\mu$ Controller, via "C-BUS," the FX803 will encode and transmit a single or pair of audio tones, in the frequency range 208Hz to 3kHz, simultaneously, and detect, decode and indicate the frequency of non-predicted input tones in the frequency range 313Hz to 6kHz.

Both tone generators can be individually placed into a power economical "Powersave" mode.

A general purpose logic input, interfacing directly with the Status Register, is provided. This could be used as an auxiliary method of routeing digital information to the  $\mu$ Controller via the "C-BUS."

The output frequencies are produced from data loaded to the device, with a programmable, general purpose, on-chip timer available to indicate the tone transmit periods.

A Dual Tone Multi-Frequency (DTMF) output is obtained by combining the 2 independent output frequencies in the integral summing amplifier. This Summing Amplifier output is also available for level adjustment.

Tones produced by the FX803 can also be used in the DBS 800 system as modulation calibration inputs and for "CUE" audio indications for the operator.

Received tones are measured and their frequency indicated to the  $\mu$ Controller in the form of a received data word. A poor-quality or incoherent tone will, after a programmed period, indicate Notone.

The FX803 is a low-power, 5-volt CMOS integrated circuit and is available in 24-pin DIL cerdip and 24-pin/lead plastic SMD packages.

Publication D/803/6 April 1998

# **Pin Number Function**

| J/LG/LS | DW |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

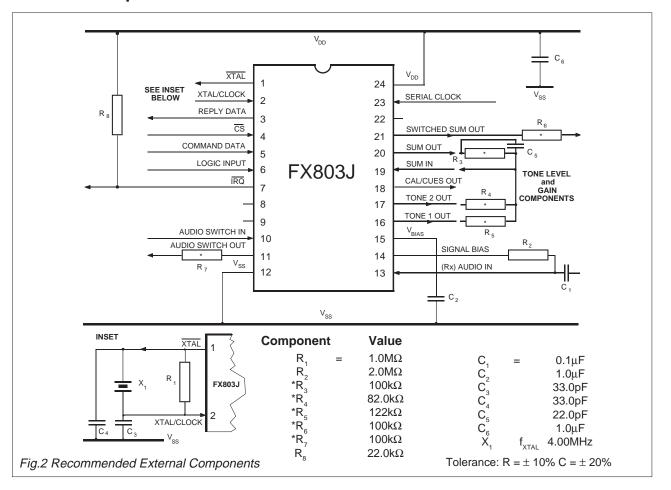

| 1       | 1  | Xtal: The output of the on-chip clock oscillator. External components are required at this input when a Xtal input is used. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | 2  | <b>Xtal/Clock:</b> The input to the on-chip clock oscillator inverter. A Xtal or externally derived clock (f <sub>XTAL</sub> ) should be connected here. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                               |

| 3       | 3  | Reply Data: The "C-BUS" serial data output to the $\mu$ Controller. The transmission of Reply Data bytes is synchronized to the Serial Clock under the control of the Chip Select input. This 3-state output is held at high-impedance when not sending data to the $\mu$ Controller. See Timing Diagrams.                                                                                                                                                                                                                                           |

| 4       | 5  | Chip Select (CS): The "C-BUS" data loading control function. This input is provided by the μController. Data transfer sequences are initiated, completed or aborted by the CS signal. See Timing Diagram.                                                                                                                                                                                                                                                                                                                                            |

| 5       | 6  | Command Data: The "C-BUS" serial data input from the μController. Data is loaded to this device in 8-bit bytes, MSB (B7) first, and LSB (B0) last, synchronized to the Serial Clock. See Timing Diagrams.                                                                                                                                                                                                                                                                                                                                            |

| 6       | 7  | <b>Logic Input:</b> This 'real-time' input is available as a general purpose logic input port which can be read from the Status Register. See Table 3.                                                                                                                                                                                                                                                                                                                                                                                               |

| 7       | 8  | Interrupt Request (IRQ): The output of this pin indicates an interrupt condition to the $\mu$ Controller, by going to a logic "0." This is a "wire-or able" output, allowing the connection of up to 8 peripherals to 1 interrupt port on the $\mu$ Controller. This pin has a low-impedance pulldown to logic "0" when active and a high-impedance when inactive. The System $\overline{\mbox{IRQ}}$ line requires one pullup resistor to $V_{DD}$ . The conditions that cause interrupts are indicated in the Status Register and are shown below: |

|         |    | G/Purpose Timer Period Expired  Rx Tone Measurement Complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |    | These interrupts are inactive during relevant Powersave conditions and can be disabled by Bits 5 and 6 in the Control Register.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8       | 4  | No internal connection, connect to V <sub>ss</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9       | 9  | No internal connection, connect to V <sub>ss</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

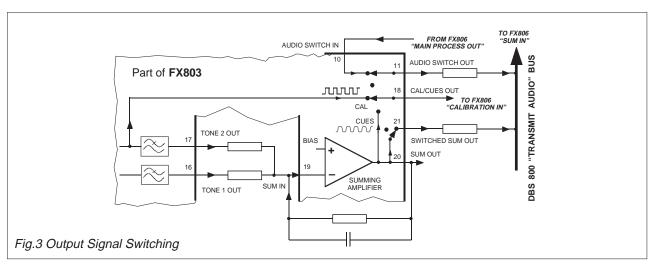

| 10      | 10 | Audio Switch In: The input to the stand-alone, on-chip Audio Switch. This switching function (Control Register Bit 7) may be used to break the system transmitter modulation path when it is required to provide a CUE (beep) from Tone Generator 2 to the loudspeaker via the FX806 PLMR Audio Processor.                                                                                                                                                                                                                                           |

| 11      | 11 | Audio Switch Out: The output of the stand-alone, on-chip Audio Switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12      | 12 | V <sub>ss</sub> : Negative Supply (Signal Ground).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# **Pin Number Function**

| J/LG/LS | DW |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | 13 | (Rx) Audio In: The received audio tone signalling input to the Input Amplifier. This input requires to be a.c. coupled and connected, using external components, to the Signal Input Bias pin. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14      | 14 | <b>Signal Input Bias:</b> External components are required between this input and the (Rx) Audio In pin See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15      | 15 | $V_{\scriptsize BIAS}$ : The internal circuitry bias line, held at $V_{\scriptsize DD}/2$ this pin must be decoupled to $V_{\scriptsize SS}$ by capacitor $C_2$ See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16      | 16 | <b>Tone 1 Out:</b> Tone 1 Generator (2-/5- tone Selcall or DTMF 1) output. External gain and coupling components will be required at this output when operating in a complete DBS 800 audio installation. The frequency of this output is determined by writing to Tx Tone Generator 1 Register (Table 4). See Figure 2.                                                                                                                                                                                                                                                                                          |

| 17      | 17 | <b>Tone 2 Out:</b> Tone 2 Generator (2-/5- tone Selcall, CUES or DTMF 2) output. External gain and coupling components will be required at this output when operating in a complete DBS 800 audio installation. The frequency of this output is determined by writing to Tx Tone Generator 2 Register (Table 5). See Figure 2.                                                                                                                                                                                                                                                                                    |

| 18      | 18 | CAL/CUES Out: An auxiliary, selectable tone frequency output, providing a square wave CALibration signal from Tone 2 Generator or a sine wave CUES (beep) signal from the Summing Amplifier. The output mode (CAL or CUES) is selected by Bit 14 in the Tx Tone Generator 2 Register (Table 5). In a DBS 800 audio installation, this output should be connected to the Calibration Input of the FX806 PLMR Audio Processor. When Tone Generator 2 is set to V <sub>BIAS</sub> (NOTONE), the CAL output is pulled to V <sub>BIAS</sub> and during a powersave of Tone Generator 2 it is held at V <sub>SS</sub> . |

| 19      | 19 | <b>Sum In:</b> The input to the on-chip Summing Amplifier. This amplifier is available for combining Tone 1 and Tone 2 outputs (DTMF). Gain and coupling components should be used at this input to provide the required system gains. See Figures 2 and 3.                                                                                                                                                                                                                                                                                                                                                       |

| 20      | 20 | <b>Sum Out:</b> The output of the on-chip Summing Amplifier. Combined tones (1 and 2) are available at this output. See Figures 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21      | 21 | <b>Switched Sum Out:</b> The combined tone output available for transmitter modulation. The switch allows control of the FX803 final output to the FX806. Control of this switch is by Bit 4 of the Control Register. See Figures 2 and 3.                                                                                                                                                                                                                                                                                                                                                                        |

| 22      | 22 | No internal connection, connect to $V_{\rm ss}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23      | 23 | <b>Serial Clock:</b> The "C-BUS" serial clock input. This clock, produced by the μController, is used for transfer timing of commands and data to and from the Audio Signalling Processor. See Timing Diagrams.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 24      | 24 | V <sub>DD</sub> : Positive supply rail. A single +5-volt power supply is required. Levels and voltages within the Audio Signalling Processor are dependent upon this supply.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |    | NOTE: (i) Further information on external components and DBS 800 system integration of this microcircuit are contained in the System Support Document.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |    | "C-BUS" is CML's proprietary standard for the transmission of commands and data between a μController and DBS 800 microcircuits. It may be used with any μController, and can, if desired, take advantage of the hardware serial I/O functions embodied into many types of μController. The "C-BUS" data rate is determined solely by the μController.                                                                                                                                                                                                                                                            |

# **External Components**

#### Notes

- Xtal/clock circuitry components shown INSET are recommended in accordance with CML Application Note D/XT/1 April 1986. The DBS 800 System Support Document contains additional notes on the use of Xtal/ clock frequencies (f<sub>XTAL</sub>).

- 2. It is recommended that, to improve screening and reduce noise levels around the FX803, Pins 8, 9 and 22 are connected to  $V_{\rm sc}$ .

- 3. Resistors marked with an asterisk (\*) are System Components, calculated to operate in a system with other DBS 800 microcircuits. Figure 3 shows in detail, these components used in the System signal paths.

R<sub>3</sub>, R<sub>4</sub>, R<sub>5</sub>, C<sub>5</sub> Tone mixing components to provide a 3dB tone-differential (twist) when used in a DTMF configuration. Single tone output levels are set independently or by the FX806 Modulator Drivers.

R<sub>7</sub> Modulation level and matching for inputs to the FX806.

# **Controlling Protocol**

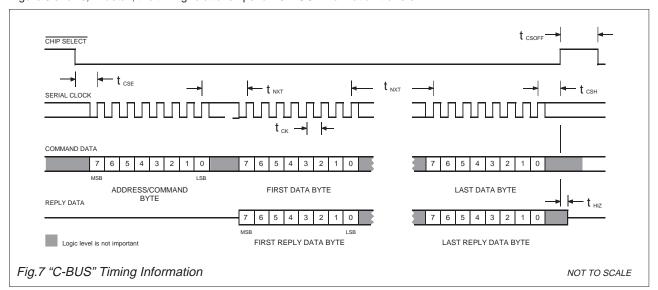

Control of the FX803 Audio Signalling Processor's operation is by communication between the µController and the FX803 internal registers on the "C-BUS," using Address/Commands (A/Cs) and appended instructions or data (see Figure 7). The use and content of these instructions is detailed in the following paragraphs and tables.

### **FX803 Internal Registers**

FX803 internal registers are detailed below:

Control Register (30<sub>H</sub>) – Write Only, control and configuration of the FX803.

Status Register (31<sub>H</sub>) - Read Only, reporting of device functions.

**Rx Tone Frequency** Register (32<sub>H</sub>) — Read Only, indicates frequency of the last received input.

**Rx Notone Timer** Register  $(33_{\rm H})$  — Write Only, setting of the Rx Notone period.

**Tx Tone Generator 1** Register (34<sub>H</sub>) — Write Only, setting the required output frequency from Tx Tone Generator 1.

**Tx Tone Generator 2** Register (35<sub>H</sub>) — Write Only, setting required output frequency from Tx Tone Generator 2.

**General Purpose Timer** Register (36<sub>H</sub>) – Write Only, setting of a general purpose, sequential time period.

#### Address/Commands

The first byte of a loaded data sequence is always recognized by the "C-BUS" as an Address/Command (A/C) byte. Instruction and data transactions to and from this device consist of an Address/Command byte followed by either:

- (i) further instructions or data or,

- (ii) a Status or data Reply.

Instructions and data are loaded and transferred, via "C-BUS," in accordance with the timing information given in Figures 7 and 8.

Table 1 shows the list of A/C bytes relevant to the FX803. A complete list of DBS 800 "C-BUS" Address allocations is published in the System Support Document.

| Command<br>Assignment     | Address/Command (A/C) Byte Hex. Binary |     |   |   |   |   |   |   | te  | + | Data<br>Byte/s                         |  |  |

|---------------------------|----------------------------------------|-----|---|---|---|---|---|---|-----|---|----------------------------------------|--|--|

|                           |                                        | MSE | 3 |   |   |   |   |   | LSB |   | _ <b>,</b>                             |  |  |

| General Reset             | 01                                     | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 1   |   |                                        |  |  |

| Write to Control Register | 30                                     | 0   | 0 | 1 | 1 | 0 | 0 | 0 | 0   | + | 1 byte Instruction to Control Register |  |  |

| Read Status Register      | 31                                     | 0   | 0 | 1 | 1 | 0 | 0 | 0 | 1   | + | 1 byte Reply from Status Register      |  |  |

| Read Rx Tone Frequency    | 32                                     | 0   | 0 | 1 | 1 | 0 | 0 | 1 | 0   | + | 2 byte Reply from Rx Tone Register     |  |  |

| Write to NOTONE Timer     | 33                                     | 0   | 0 | 1 | 1 | 0 | 0 | 1 | 1   | + | 1 byte Instruction to Notone Register  |  |  |

| Write to Tx Tone Gen. 1   | 34                                     | 0   | 0 | 1 | 1 | 0 | 1 | 0 | 0   | + | 2 byte Instruction to Tx Tone Gen. 1   |  |  |

| Write to Tx Tone Gen. 2   | 35                                     | 0   | 0 | 1 | 1 | 0 | 1 | 0 | 1   | + | 2 byte Instruction to Tx Tone Gen. 2   |  |  |

| Write to G/Purpose Timer  | 36                                     | 0   | 0 | 1 | 1 | 0 | 1 | 1 | 0   | + | 1 byte Instruction to G/Purpose Timer  |  |  |

"Write to Control Register" - A/C 30,, followed by 1 byte of Command Data.

#### **Audio Switch**

See the Signal Switching diagram (Figure 3) and DBS 800 Document for application examples.

#### **General Purpose Timer**

Should be set up before interrupts are enabled, as a General Reset command will set the timer period to 00 \_ - 0ms (permanent interrupt).

#### **Interrupt Enable Instructions**

Status Bits 0, 1 and 2 are produced regardless of the state of these settings.

#### **Band Selection**

Bits 2 and 3 set the required frequency range (see Figure 4, FX803 Frequencies).

#### **Summing Switch**

To break the FX803 drive to the FX806 PLMR Audio Processor (see Figure 3, Signal Switching).

#### Interrupt Designation

**Decoder Interrupts:**

No Tone Timer and Rx Tone Measurement.

Transmitter Interrupt:

G/Purpose Timer Interrupt.

| S             | etting               | Control Bits                                          |

|---------------|----------------------|-------------------------------------------------------|

|               | <b>ISB Bit 7</b> 1 0 | Transmitted First Audio Switch Enable Disable         |

|               | <b>6</b><br>1<br>0   | <b>G/Purpose Timer Interrupt</b><br>Enable<br>Disable |

|               | <b>5</b><br>1<br>0   | <b>Decoder Interrupts</b><br>Enable<br>Disable        |

|               | <b>4</b><br>1<br>0   | <b>Summing Switch</b><br>Enable<br>Disable            |

| <b>3</b><br>0 | <b>2</b><br>0        | <b>Band Selection</b><br>High Band                    |

| 0             | 1                    | Mid Band                                              |

| 1             | 0                    | Extended Band                                         |

| 1             | 1                    | Do Not use this setting                               |

|               | <b>1</b><br>0        | Set to "0"                                            |

|               | <b>0</b><br>0        | Set to "0"                                            |

| Table 2       | Control Real         | ister                                                 |

Table 2 Control Register

### "Read Status Register" - A/C 31,, followed by 1 byte of Reply Data.

| Reading                         | Status Bits                                                                  |

|---------------------------------|------------------------------------------------------------------------------|

| <b>MSB</b><br><b>Bit 7</b><br>0 | Received First<br>Set to<br>"0"                                              |

| <b>6</b><br>0                   | Set to "0"                                                                   |

| <b>5</b><br>0                   | Set to "0"                                                                   |

| <b>4</b><br>0                   | Set to "0"                                                                   |

| <b>3</b><br>1<br>0              | Logic Input Status<br>"1"<br>"0"                                             |

| <b>2</b><br>1                   | G/Purpose Timer Period<br>Expired<br>(IRQ generated if enabled)<br>(Table 2) |

| <b>1</b><br>1                   | Notone Timer Period<br>Expired<br>(IRQ generated if enabled)<br>(Table 2)    |

| <b>0</b><br>1                   | Rx Tone Measurement<br>Complete<br>(Interrupt Generated)                     |

|                                 |                                                                              |

### Interrupt Requests (IRQ)

Interrupts on this device are available to draw the attention of the  $\mu$ Controller to a change in the condition of the bit in the Status Register. However Bits are set in the Status Register irrespective of the setting of interrupt enable bits (Table 2) and these changes may be recognized by 'polling' the register.

#### **General Purpose Timer Period**

Set to a logic "1" when the timer period has expired. Cleared to a logic "0,"

- By a read of the Status Register or,

- New G/Purpose Timer information or,

- General Reset Command

#### **Notone Timer Period**

Set to a logic "1" when the timer period has expired. Cleared to a logic "0,"

- By a read of the Status Register or,

- New Notone Timer information or,

- General Reset Command

#### **Rx Tone Measurement**

Set to a logic "1" when the Rx Tone measurement is complete.

#### Cleared to a logic "0,"

- By a read of the Status Register or,

- General Reset Command

Table 3 Status Register

# Tx Tone Generator Registers 1 and 2

Each Tx Tone Generator is controlled individually by writing a two-byte command to the relevant Tx Tone Generator Register. The format of this command word, which is different for each tone generator, is shown below with the calculations required for tone frequency  $(f_{TONE})$  generation described in the following text.

"Write to Tx Tone Generator 1 Register" – A/C 34, followed by 2 bytes of Command Data.

| MSB<br>(loaded fi | ret)      |                               |         | Bit Numbers |                                |   |   |          |           |                    |   |   |        | , | LSB<br>(loaded last) |  |  |

|-------------------|-----------|-------------------------------|---------|-------------|--------------------------------|---|---|----------|-----------|--------------------|---|---|--------|---|----------------------|--|--|

| 15                | 14        | 13                            | 12      | 11          | 10                             | 9 | 8 | 7        | 6         | 5                  | 4 | 2 | 1 0    |   |                      |  |  |

| "0"               | "0"       | V <sub>BIAS</sub> /<br>Enable |         |             | ese 13 l<br>' <b>A</b> " is us |   |   |          |           |                    |   |   |        |   |                      |  |  |

| The bina          | •         | ber produced                  | by bits | 0 to 12     | (MSB) is                       | 3 | E | Bit 13 a | t logic " | 1" = To<br>0" = To |   |   | 0., 10 |   | IE).                 |  |  |

| 0                 | all logic | "0" then Tx T                 | one Ge  | nerator     | 1 is                           |   | E | Bits 14  | and 15    |                    |   | • |        |   |                      |  |  |

| Table 4           | Settin    | g Tx Tone G                   | Generat | or 1        |                                |   |   |          |           |                    |   |   |        |   |                      |  |  |

"Write to Tx Tone Generator 2 Register" - A/C 35, followed by 2 bytes of Command Data.

|        | SB<br>d first)            |                               |         | Bit Numbers                                                                                                                                                       |          |   |                                              |           |           |                      |          |     |      | LSB<br>(loaded last) |          |  |

|--------|---------------------------|-------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|----------------------------------------------|-----------|-----------|----------------------|----------|-----|------|----------------------|----------|--|

| 15     | 14                        | 13                            | 12      | 11                                                                                                                                                                | 10       | 9 | 8                                            | 7         | 6         | 5                    | 4        | 3   | 2    | 1                    | <b>0</b> |  |

| "0"    | CAL/<br>CUES              | V <sub>BIAS</sub> /<br>Enable |         | These 13 bits (0 to 12) are used to produce a binary number, designated " $\bf B$ " is used in the formulas below to set the Tx Tone 2 frequency ( $f_{TONE}$ 2). |          |   |                                              |           |           |                      |          |     |      |                      |          |  |

|        | oinary num<br>gnated "B." | ber produced                  | by bits | 0 to 12                                                                                                                                                           | (MSB) is | 8 | I                                            | Bit 13 a  | t logic " | '1" = To<br>'0" = To |          |     | DIAC |                      | ≣).      |  |

| If "B" | = all logic               | "0" then Tx To                | one Ger | nerator                                                                                                                                                           | 2 is     |   | Bit 14 at logic "1" = Squarewave CAL Output. |           |           |                      |          |     |      |                      |          |  |

| Pow    | ersaved.                  |                               |         |                                                                                                                                                                   |          |   | "0" = Sinewave CUES Output.                  |           |           |                      |          |     |      |                      |          |  |

|        |                           |                               |         |                                                                                                                                                                   |          |   | I                                            | Bit 15 (N | иsв) mu   | st be a              | logic "C | )." |      |                      |          |  |

| Table  | e 5 Setting               | g Tx Tone Ge                  | enerato | or 2                                                                                                                                                              |          |   |                                              |           |           |                      |          |     |      |                      |          |  |

#### Notes

- (1) Programming Tone Generator 2 to  $V_{BIAS}$  (NOTONE) (Bit 13) will place the CAL/CUES Output at  $V_{BIAS}$  via a  $40k\Omega$  internal resistor.

- (2) Programming Tone Generator 2 to Powersave will place the CAL/CUES Output at  $V_{ss}$ .

- (3) If both Tone Generators (1 and 2) are Powersaved, the Summing Amplifier is also Powersaved.

#### **Calculations**

As can be seen from Tables 4 and 5 (above), a binary number ("A" or "B" – Bits 0 to 12) is loaded to the respective Tx Tone Generator. The formulas shown below are used to calculate the required output frequency.

Required Tx Tone output frequency =  $f_{TONE} 1$  or 2 XTAL/clock frequency =  $f_{XTAL}$ Input Data Word (Bits 0 to 12) = "A" or "B"

Formula

$$\mathbf{f}_{\mathsf{TONE}\,^{(Hz)}} = \underbrace{\frac{f_{\mathsf{XTAL}\,^{(Hz)}}}{4\,\mathsf{x}\,^{\mathsf{*}}\!\mathsf{A}^{\mathsf{*}}\,(\mathsf{or}\,^{\mathsf{*}}\!\mathsf{B}^{\mathsf{*}})}}_{\mathsf{4}\,\mathsf{x}\,^{\mathsf{*}}\!\mathsf{A}^{\mathsf{*}}\,(\mathsf{or}\,^{\mathsf{*}}\!\mathsf{B}^{\mathsf{*}})} \qquad \qquad \mathsf{or} \qquad \mathsf{Input}\,^{\mathsf{*}}\!\mathsf{A}^{\mathsf{*}}\,\,(\mathsf{or}\,^{\mathsf{*}}\!\mathsf{B}^{\mathsf{*}}) = \underbrace{\frac{f_{\mathsf{XTAL}\,^{(Hz)}}}{4\,\mathsf{x}\,f_{\mathsf{TONE}\,^{(Hz)}}}}_{\mathsf{4}\,\mathsf{x}\,f_{\mathsf{TONE}\,^{(Hz)}}}$$

### **Tx Tone Frequencies**

With reference to Tables 4 and 5 (above), whilst Input Data Words "A" or "B" can be programmed for frequencies outside the stated limits of 208Hz and 3000Hz, any output frequencies obtained may not be within specified parameters (see "Specification" page).

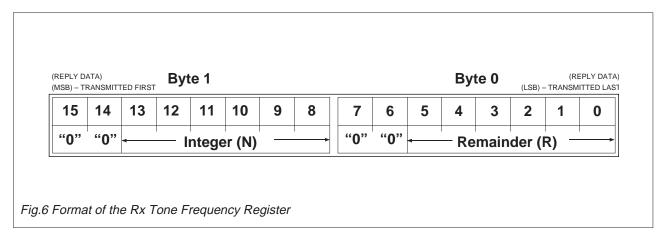

"Read Rx Tone Frequency Register" - A/C 32,, followed by 2 bytes of Reply Data.

# Measurement of Rx Signal Frequency (S<sub>INPUT</sub>)

The measurement details given on Pages 10 and 11 are for a Xtal/clock frequency ( $f_{xTAL}$ ) of 4.032MHz, a scaling formula for other values of  $f_{xTAL}$  is given at the bottom of this page.

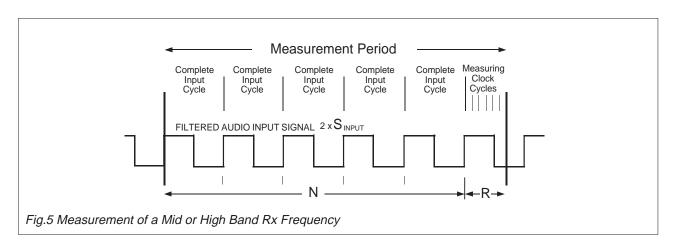

The input audio signal (S<sub>INPUT</sub>) is filtered and measured in the Frequency Counter over a specified "measurement period" (9.125 ms or 18.250 ms).

The measuring function counts the number of complete input cycles occurring within the measurement period and then the number of measuring-clock cycles necessary to make up the period.

When the count period of a successful decode is complete, the Rx Tone Measurement bit in the Status Register, and the Interrupt bit (if enabled) are set.

The Rx Tone Frequency Register will now indicate the signal frequency ( $S_{\text{INPUT}}$ ) in the form of 2 bytes (1 and 0) as illustrated in Figure 6 below.

#### The Integer (N) - Byte 1

A binary number representing 'twice the number of complete input audio cycle periods' counted during the specified measurement period, which is:

High Band Decode

=

9.125 ms

=

"t"

Mid Band Decode

=

18.250 ms

=

"t"

Extended Band Decode

=

9.125 ms

=

"t"

See the bottom of this page for "t" and "f" scaling factors

#### The Remainder (R) - Byte 0

A binary number representing the remainder part, R, of 2 x Input Signal Frequency ( $S_{INPUT,I}$  'R = number of specified measuring-clock cycles' required to complete the specified measurement period (See N).

The clock-cycle frequencies are:

High Band Decode

=

56.00 kHz

=

"f"

Mid Band Decode

=

28.00 kHz

=

"f"

Extended Band Decode

=

56.00 kHz

=

"f"

# **f**<sub>XTAL</sub> Scaling Factors

The calculations above are for an  $f_{x_{TAL}}$  of 4.032MHz. The following formulas enable the calculation of these values using any Xtal value. Note:  $f_{x_{TAL}}$  values are stated in MHz.

"t" scaled = "t"

$$\times \left[ \frac{4.032}{f_{XTAL}} \right]$$

"f"  $\times \left[ \frac{f_{XTAL}}{4.032} \right]$

# Frequency Measurement Formulæ

To assist in the production of 'look-up' tables and limit-values in the  $\mu$ Controller and provide guidance upon the determination of N and R from a measured frequency, the following formulæ show the derivation of the Rx frequency,  $S_{\text{INPUT}}$ , from the measured data bytes (N and R), Figure 6.

# **High Band Measurement**

### S<sub>INPUT</sub> – High Band

In the measurement period of 9.125ms, there are Nh cycles at  $2S_{_{\rm INPUT}}$  and Rh clock cycles at 56.000kHz.

so

$$\frac{Nh}{2 \times S_{\text{INPLIT}}} + \frac{Rh}{56000} = 9.125 \text{ms}$$

From which

$$S_{INPUT} = \frac{28000 \times Nh}{(511 - Rh)}$$

Hz [1]

#### Nh and Rh - High Band

The measurement period = 9.125msClock Frequency = 56.000kHzThe measured frequency =  $2 \times S_{INPUT}$  c/s In the measurement period there are:

Nh is the lower integer value of this decimal number:

Nh = INT

$$(9.125 \times 10^{-3} \times 2 \times S_{INPLIT})$$

[4]

Rh is rounded to the nearest integer of this decimal number:

Rh =

$$(9.125 \times 10^{-3} - \frac{Nh}{2 \times S_{INPUT}}) \times 56000$$

[5]

# **Mid Band Measurements**

# S<sub>INPUT</sub> – Mid Band

In the measurement period of 18.250ms, there are Nm cycles at  $2S_{\text{INPLIT}}$  and Rm clock cycles at 28.000kHz.

so

$$\frac{Nm}{2 \times S_{\text{IMPLIT}}} + \frac{Rm}{28000} = 18.250 \text{ms}$$

From which

$$S_{INPUT} = \frac{14000 \times Nm}{(511 - Rm)}$$

Hz [2]

#### Nm and Rm - Mid Band

Nm is the lower integer value of this decimal number:

Nm = INT

$$(18.250 \times 10^{-3} \times 2 \times S_{INPLIT})$$

[6]

Rm is rounded to the nearest integer of this decimal number:

Rm =

$$(18.250 \times 10^{-3} - Nm) \times 28000$$

[7]

$\frac{1}{2} \times S_{INPUT}$

#### **Extended Band Measurements**

# S<sub>INPUT</sub> – Extended Band

In the measurement period of 9.125ms, there are Ne cycles at  $S_{\text{INPLIT}}$  and Re clock cycles at 56.000kHz.

so

$$\frac{\text{Ne}}{\text{S}_{\text{INPUT}}}$$

+  $\frac{\text{Re}}{56000}$  = 9.125ms

From which

$$S_{INPUT} = \frac{56000 \times Ne}{(511 - Re)}$$

Hz [3]

#### Ne and Re - Extended Band

In the measurement period there are:

Ne is the lower integer value of this decimal number:

Ne = INT

$$(9.125 \times 10^{-3} \times S_{INPLIT})$$

[8]

Re is rounded to the nearest integer of this decimal number:

Re =

$$(9.125 \times 10^{-3} - \frac{\text{Ne}}{\text{S}_{\text{INPUT}}}) \times 56000$$

[9]

"Write to the Rx Notone Timer Register" - A/C 33 of followed by 1 byte of Command Data.

|                             | Se         | tting    | 1              | Function/Perio                                 | Function/Period |  |  |  |  |  |  |  |  |

|-----------------------------|------------|----------|----------------|------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

| <b>MSB</b><br><b>7</b><br>0 | <b>6</b> 0 | <b>5</b> | <b>4</b><br>0  | Transmitted Bit 7 First These 4 bits must be " | •               |  |  |  |  |  |  |  |  |

| 3                           | 2          | 1        | 0              | High/Extended<br>Band                          | Mid<br>Band     |  |  |  |  |  |  |  |  |

| 0                           | 0          | 0        | 0              | period (ms) 0                                  | 0               |  |  |  |  |  |  |  |  |

| 0                           | 0          | 0        | 1              | " 20 ±1%                                       | 40 ±1%          |  |  |  |  |  |  |  |  |

| 0                           | 0          | 1        | 0              | 40 "                                           | 80 "            |  |  |  |  |  |  |  |  |

| 0                           | 0          | 1        | 1              | 60 "                                           | 120 "           |  |  |  |  |  |  |  |  |

| 0                           | 1          | 0        | 0              | 80 "                                           | 160 "           |  |  |  |  |  |  |  |  |

| 0                           | 1          | 0        | 1              | 100 "                                          | 200 "           |  |  |  |  |  |  |  |  |

| 0                           | 1          | 1        | 0              | 120 "                                          | 240 "           |  |  |  |  |  |  |  |  |

| 0                           | 1          | 1        | 1              | 140 "                                          | 280 "           |  |  |  |  |  |  |  |  |

| 1                           | 0          | 0        | 0              | 160 "                                          | 320 "           |  |  |  |  |  |  |  |  |

| 1                           | 0          | 0        | 1              | 180 "                                          | 360 "           |  |  |  |  |  |  |  |  |

| 1                           | 0          | 1        | 0              | 200 "                                          | 400 "           |  |  |  |  |  |  |  |  |

| 1                           | 0          | 1        | 1              | 220 "                                          | 440 "           |  |  |  |  |  |  |  |  |

| 1                           | 1          | 0        | 0              | 240 "                                          | 480 "           |  |  |  |  |  |  |  |  |

| 1                           | 1          | 0        | 1              | 260 "                                          | 520 "           |  |  |  |  |  |  |  |  |

| 1                           | 1          | 1        | 0              | 280 "                                          | 560 "           |  |  |  |  |  |  |  |  |

| 1                           | 1          | 1        | 1              | 300 "                                          | 600 "           |  |  |  |  |  |  |  |  |

| Tab                         | le 6       | Rx N     | <b>I</b> OTONE | <br>Timer Settings                             |                 |  |  |  |  |  |  |  |  |

# Operation of the Rx Notone Timer

An Rx Notone period is that period when no signal or a consistently bad-quality signal is received.

The Rx Notone Timer can be employed to indicate to the  $\mu$ Controller that a Notone situation has existed for a predetermined period.

This timer register can be written-to and set in any mode of the FX803.

The Notone Timer period is 'primed' by writing to the Notone Timer Register (33 $_{\rm H}$ ) using the settings given in Table 6.

"Priming" sets the timing period; this period can only start directly after a frequency (tone) measurement has been successfully completed.

The NOTONE Timer is a one-shot timer being reset only by successful tone measurements.

If the quality of the received signal drops to an unusable level the NOTONE Timer will start its run-down.

On completion of the preset period, the NOTONE Timer Period Expired bit in the Status Register and the Interrupt (when enabled, *Table 2*) are set.

Upon detection of the Interrupt, the Status Register should be read by the  $\mu$ Controller to ascertain the source of the Interrupt.

The Notone Timer Period Expired bit is cleared:

- i By a read of the Status Register or,

- ii New Notone Timer information or,

- iii General Reset command

This timer is set to  $00_{H}$  (0ms) by a General Reset command.

The following situations may be encountered by the Notone Timer circuitry:

#### No Signal

The NOTONE Timer can only start its run down on completion of a valid frequency measurement.

#### No Signal after a Valid Tone Measurement

The timer will start to run down when the last Rx Tone Measurement complete bit is set. At the end of the "primed" period the Notone Timer Period Expired bit in the Status Register and the Interrupt will be set.

#### Signal Fades after a Valid Tone Measurement

The timer will start to run down when the signal becomes unreadable to the device. At the end of the "primed" period the Notone Timer Period Expired bit in the Status Register and the Interrupt will be set.

#### Signal Appears after the Timer has Started

If the frequency measurement is more than 75% complete when the timer period expires, neither the NOTONE bit nor the Interrupt will be set unless that frequency measurement is subsequently aborted.

"Write to General Purpose Timer Register" - A/C 36, followed by 1 byte of Command Data.

|              | Se            | etting   | 1             | Function/Period                                  |  |  |  |  |  |  |  |

|--------------|---------------|----------|---------------|--------------------------------------------------|--|--|--|--|--|--|--|

| <b>MSB</b> 7 | <b>6</b><br>0 | <b>5</b> | <b>4</b><br>0 | Transmitted Bit 7 First These 4 bits must be "0" |  |  |  |  |  |  |  |

| 3            | 2             | 1        | 0             | High/Extended Mid<br>Band Band                   |  |  |  |  |  |  |  |

| 0            | 0             | 0        | 0             | Reset Timer and Start Timing Period of 0 0       |  |  |  |  |  |  |  |

| 0            | 0             | 0        | 1             | " 10 ms ±1% 20 ms ±1%                            |  |  |  |  |  |  |  |

| 0            | 0             | 1        | 0             | 20 " 40 "                                        |  |  |  |  |  |  |  |

| 0            | 0             | 1        | 1             | 30 " 60 "                                        |  |  |  |  |  |  |  |

| 0            | 1             | 0        | 0             | 40 " 80 "                                        |  |  |  |  |  |  |  |

| 0            | 1             | 0        | 1             | 50 " 100 "                                       |  |  |  |  |  |  |  |

| 0            | 1             | 1        | 0             | 60 " 120 "                                       |  |  |  |  |  |  |  |

| 0            | 1             | 1        | 1             | 70 " 140 "                                       |  |  |  |  |  |  |  |

| 1            | 0             | 0        | 0             | 80 " 160 "                                       |  |  |  |  |  |  |  |

| 1            | 0             | 0        | 1             | 90 " 180 "                                       |  |  |  |  |  |  |  |

| 1            | 0             | 1        | 0             | 100 " 200 "                                      |  |  |  |  |  |  |  |

| 1            | 0             | 1        | 1             | 110 " 220 "                                      |  |  |  |  |  |  |  |

| 1            | 1             | 0        | 0             | 120 " 240 "                                      |  |  |  |  |  |  |  |

| 1            | 1             | 0        | 1             | 130 " 260 "                                      |  |  |  |  |  |  |  |

| 1            | 1             | 1        | 0             | 140 " 280 "                                      |  |  |  |  |  |  |  |

| 1            | 1             | 1        | 1             | 150 " 300 "                                      |  |  |  |  |  |  |  |

Table 7 General Purpose Timer Settings

# Operation of the General Purpose Timer

This timer, which is not dedicated to any specific function within the FX803, can be employed within the DBS 800 system to indicate time-elapsed periods of between 10ms and 150ms in the High/Extended Band, 20ms and 300ms in the Mid Band, to the  $\mu$ Controller.

Setting of the timer is by loading a single-byte data word via the "C-BUS," as indicated in Table 7 (left), to the FX803 via the Command Data line.

The timer will be reset and the run-down started on completion of Timer Data Word loading.

When the programmed time period has expired, the General Purpose Timer Expired bit (Bit 2) in the Status Register and the Interrupt (if enabled) are set.

The General Purpose Timer Expired bit is cleared:

- i By a read of the Status Register, or

- ii New G/P Timer information, or

- iii General Reset command.

When the programmed time period has expired, this timer will reset, restart and continue sequencing until;

- i New G/P Timer information is written, or

- ii A General Reset command.

The General Purpose Timer Expired bit and the Interrupt will remain set until cleared.

This timer is set to  $00_{H}$  (0ms) by a General Reset command.

### **Powersave**

Various sections of the FX803 can be placed independently into a power economical condition. Table 8 (below) gives a brief summary of the inactive, power-economical states available to the FX803.

| Powersaved Section                | Instruction Sour                            | Table                       |              |

|-----------------------------------|---------------------------------------------|-----------------------------|--------------|

| Tone Encoder 1                    | Tx Tone Gen.1 Reg. (34,)                    | All bits = "0"              | 4            |

| Tone Encoder 2                    | Tx Tone Gen.2 Reg. (35 <sub>H</sub> )       | All bits = "0"              | 5            |

| Summing Amplifier                 | This action is automatic when bo condition. | th Tone Encoders are in the | ne powersave |

| Table 8 FX803 Powersave Functions |                                             |                             |              |

#### **Powersave Conditions**

**Xtal/Clock and "C-BUS"**: This circuitry is always active, on all DBS 800 microcircuits, under any powered/powersaved conditions.

#### **Interrupt Requests**

An Interrupt ( $\overline{|RQ}$ ), when enabled, is provided by the FX803 to indicate the following conditions to the  $\mu$ Controller.

# NOTONE Timer Period Expired

**Enabled:** By Control Register Bit 5. **Set:** When the preset Notone Flag is

set

**Identified:** By Status Register Bit 1. **Cleared:** By reading the Status

Register.

#### G/Purpose Timer Period Expired

**Enabled:** By Control Register Bit 6. **Set:** When the General Purpose Timer

has timed out.

Identified: By Status Register Bit 2.

Cleared: By reading the Status

Register.

# Rx Tone Measurement Complete

Enabled: By Control Register Bit 5.

**Set:** When an Rx Frequency Measurement has been successfully

completed.

Identified: By Status Register Bit 0.

Cleared: By reading the Status

Register.

On recognition of the "Read Status" Command byte, the interrupt output is cleared, the Status Bits are transferred to the  $\mu$ Controller via the "C-BUS" Reply Data line and the internal Status Bits are cleared.

# **Operational Recommendations**

It is recommended that, following initial System power-up a General Reset command is sent to the FX803.

#### Receive Sequence

- Send Control Command for Rx: Select Midband/Highband and Digital Filter length.

- **2.** Disable transmitters, if desired by writing to Tone Frequency registers.

- Prime the NOTONE Timer by sending the required period byte.

- 4. Enable Decoder interrupts as desired.

- 5. When a valid tone has been detected by a successfully completed measurement the Status Register is set to "Tone Measurement Complete" and an interrupt sent to the  $\mu C$ .

- 6. The μC examines the Status Register, if tone measurement is complete, reads in the Rx Tone Frequency in the form N + R (Figure 6).

- 7. Rx Tone Measurement Complete interrupts are periodically sent to the  $\mu C$  unless Notone is detected, in which case a Notone Interrupt is sent.

#### **Transmit Control Sequence**

- Set Tone Frequency Generators to V<sub>BIAS</sub> (setting both tone generators (Bit 13 = "1")) during the transmitter initialization period.

- Send Control Command for Tx: Select Sum/Switched Sum o/p and Audio Switch states.

- Send General Purpose (GP) Timer information for the V<sub>BIAS</sub> (NOTONE) transmitter initialization period (Step 1). This will initiate the timer.

- 4. Enable the General Purpose Timer interrupt.

- μC waits for "GP Timer Expired;" Reads the Status Register to check interrupt due to timer; Resets the Status Bit.

- If required, the  $\mu$ C sends the next timer period followed by the next tone(s) frequency information. A new timer period sent will reset the timer, otherwise the timer is self-sequencing.

- 6. The  $\mu$ C monitors the interrupts and repeats 5 & 6 as required.

- After last loaded tone the μC turns off the Tone Generator(s) by setting tone outputs to V<sub>BIAS</sub> (NOTONE) (Tables 4 and 5).

#### **General Reset**

Upon Power-Up the "bits" in the FX803 registers will be random (either "0" or "1"). A General Reset Command (01 $_{\rm H}$ ) will be required to "reset" all microcircuits on the "C-BUS," and has the following effect upon the FX803.

Sets the FX803 to:

Encoder High Band (625Hz to 3000Hz)  $\,-\,$  with interrupts disabled, both timers set to 00  $_{\rm H}.$

It is recommended that both timers are set-up before interrupts are enabled, to prevent initial, undesired interrupts.

#### Glossary of Abbreviations

Below is a list of abbreviations used within this Data Sheet.

$\begin{array}{ll} {\rm f_{_{XTAL}}} & {\rm Xtal/clock \, frequency} \\ {\rm S_{_{INPUT}}} & {\rm Audio \, input \, signal} \\ {\rm f_{_{TONE}}} & {\rm Tone \, frequency} \\ \end{array}$

# **Timing Information**

### **Timing Diagrams**

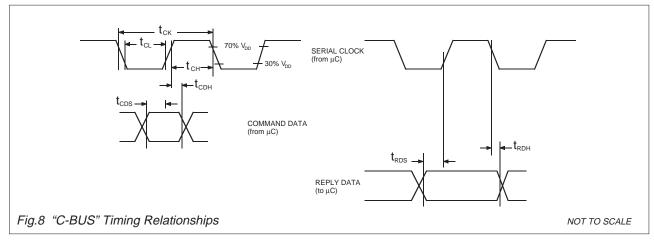

Figure 7 shows the timing parameters for two-way communication between the  $\mu$ Controller and the FX803 on the "C-BUS." Figure 8 shows, in detail, the timing relationships for "C-BUS" information transfer.

| Parameter          | Min. | Тур. | Max. | Unit |

|--------------------|------|------|------|------|

| t <sub>cse</sub>   | 2.0  | _    | _    | μs   |

| t <sub>CSH</sub>   | 4.0  | _    | _    | μs   |

| t <sub>CSOFF</sub> | 2.0  | _    | _    | μs   |

| t <sub>NXT</sub>   | 4.0  | _    | _    | μs   |

| t <sub>CK</sub>    | 2.0  | _    | _    | μs   |

| t <sub>CH</sub>    | 500  | _    | _    | ns   |

| t <sub>CL</sub>    | 500  | _    | _    | ns   |

| t <sub>CDS</sub>   | 250  | _    | _    | ns   |

| t <sub>CDH</sub>   | 0    | _    | _    | ns   |

| t <sub>RDS</sub>   | 250  | _    | _    | ns   |

| t <sub>RDH</sub>   | 50.0 | _    | _    | ns   |

| t <sub>HIZ</sub>   | _    | -    | 2.0  | μs   |

#### **Notes**

- (1) Command Data is transmitted to the peripheral MSB (Bit 7) first, LSB (Bit 0) last. Reply Data is read from the FX803 MSB (Bit 7) first, LSB (Bit 0) last.

- (2) Data is clocked into the FX803 and into the  $\mu$ Controller on the rising Serial Clock edge.

- (3) Loaded data instructions are acted upon at the end of each individual, loaded byte.

- (4) To allow for differing μController serial interface formats, the FX803 will work with either polarity Serial Clock pulses.

# **Specification**

# **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

Operating temperature range: FX803J -40°C to +85°C (cerdip)

FX803DW/LG/LS -40°C to +85°C (plastic)

Storage temperature range: FX803J -55°C to +125°C (cerdip)

FX803DW/LG/LS -40°C to +85°C (plastic)

### **Operating Limits**

All device characteristics are measured under the following conditions unless otherwise specified:

$V_{DD} = 5.0 \text{V}$ .  $T_{AMB} = 25 ^{\circ}\text{C}$ . Xtal/Clock ( $f_{XTAL}$ ) = 4.032MHz. Audio Level 0dB ref: = 308mVrms @ 1kHz (60% deviation, FM).

Noise Bandwidth = 5.0kHz Band-Limited Gaussian.

| Characteristics                                                  | See Note | Min. | Тур.       | Max. | Unit      |

|------------------------------------------------------------------|----------|------|------------|------|-----------|

|                                                                  |          |      |            |      |           |

| Static Values                                                    |          | 4.5  | <b>5</b> 0 |      |           |

| Supply Voltage                                                   |          | 4.5  | 5.0        | 5.5  | V         |

| Supply Current                                                   |          |      | 2.0        |      | m /\      |

| (Decoder + Both Timers)<br>(Decoder + Both Timers + One Tx only) |          | _    | 2.0<br>4.0 | _    | mA<br>mA  |

| (All Functions Enabled)                                          |          | _    | 5.0        | _    | mA        |

| Analogue Impedances                                              |          | _    | 5.0        | _    | ША        |

| (Rx) Audio Input                                                 |          | _    | 20.0       | _    | $M\Omega$ |

| Summing Amp Input                                                |          | _    | 20.0       | _    | MΩ        |

| Switch                                                           |          | _    | 1.0        | _    | kΩ        |

| Tones 1 and 2 Outputs                                            |          | _    | 10.0       | _    | kΩ        |

| CAL/CUES Output                                                  |          | _    | 5.0        | _    | kΩ        |

| Summing Outputs                                                  |          | _    | 10.0       | _    | kΩ        |

| Curining Outputs                                                 |          |      | 10.0       |      | K22       |

| Dynamic Values                                                   |          |      |            |      |           |

| Digital Interface                                                |          |      |            |      |           |

| Input Logic "1"                                                  | 1        | 3.5  | _          | _    | V         |

| Input Logic "0"                                                  | 1        | _    | _          | 1.5  | V         |

| Output Logic "1" (IOH = $-120\mu$ A)                             | 2        | 4.6  | _          | _    | V         |

| Output Logic "0" (IOL = $360\mu$ A)                              | 3        | _    | _          | 0.4  | V         |

| I <sub>OUT</sub> Tristate (Logic "1" or "0")                     | 3        | _    | _          | 4.0  | μΑ        |

| Input Capacitance                                                | 1        | _    | _          | 7.5  | pF        |

| $IOX \qquad (V_{OUT} = 5.0V)$                                    | 4        | _    | -          | 4.0  | μΑ        |

| Overall Performance Rx - Decoding                                |          |      |            |      |           |

| 5                                                                |          |      |            |      |           |

| High-Band<br>Sensitivity                                         |          | _    | -20.0      | _    | dB        |

| Tone Response Time                                               | _        |      |            | 00.0 |           |

| Good Signal                                                      | 5        | _    | _          | 30.0 | ms        |

| Tone-to-Noise Ratio = 0dB                                        | 5, 6     | _    | _          | 40.0 | ms        |

| Frequency                                                        |          | 005  |            | 0000 |           |

| Band                                                             |          | 625  |            | 3000 | Hz        |

| Measurement Resolution                                           | 0        | _    | 0.2        | _    | %         |

| Measurement Accuracy                                             | 9        | _    | 0.5        | _    | %         |

# Specification .....

| Characteristics                                       | See Note | Min. | Тур.         | Max. | Unit   |

|-------------------------------------------------------|----------|------|--------------|------|--------|

|                                                       |          |      |              |      |        |

| Rx - Decoding                                         |          |      |              |      |        |

| Mid-Band                                              |          |      |              |      |        |

| Sensitivity                                           |          | _    | -20.0        | _    | dB     |

| Tone Response Time                                    |          |      |              |      |        |

| Good Signal                                           | 7        | _    | _            | 60.0 | ms     |

| Tone-to-Noise Ratio = 0dB                             | 6, 7     | _    | _            | 80.0 | ms     |

| Frequency                                             |          | 040  |              | 4500 | 1.1-   |

| Band                                                  |          | 313  | 0.0          | 1500 | Hz     |

| Measurement Resolution Measurement Accuracy           | 9        | _    | 0.2<br>0.5   | _    | %<br>% |

| Measurement Accuracy                                  | 9        | _    | 0.5          | _    | 70     |

| Extended-Band                                         |          |      |              |      |        |

| Sensitivity                                           |          | _    | -20.0        | _    | dB     |

| Tone Response Time                                    |          |      |              |      |        |

| Good Signal                                           | 5        | _    | _            | 20.0 | ms     |

| Frequency                                             |          |      |              |      |        |

| Band                                                  |          | 1250 |              | 6000 | Hz     |

| Measurement Resolution                                |          | _    | 0.2          | _    | %      |

| Measurement Accuracy                                  | 9        | _    | 0.5          | _    | %      |

| Tx - Encoders 1 and 2                                 |          |      |              |      |        |

| Tone Frequency                                        |          | 208  |              | 3000 | Hz     |

|                                                       |          | _    | _            | 1.0  | μs     |

| Period (1/f <sub>TONE</sub> ) Error<br>Tone Amplitude |          | -1.0 | _            | 1.0  | dB     |

| Total Harmonic Distortion                             |          | _    | _            | 5.0  | %      |

| Rise Time to 90%                                      |          | _    | $3/f_{TONE}$ | _    | secs   |

| Fall Time to 10%                                      | 8        | _    | _            | 5.0  | ms     |

| Frequency Change Time                                 |          | _    | $3/f_{TONE}$ | _    | secs   |

| Timers                                                |          |      |              |      |        |

| General Purpose                                       |          |      |              |      |        |

| Timing Period Range                                   |          |      |              |      |        |

| High-Band                                             |          | 10.0 |              | 150  | ms     |

| Mid-Band                                              |          | 20.0 |              | 300  | ms     |

| Rx Notone                                             |          |      |              |      |        |

| Timing Period Range                                   |          | 00.0 |              | 000  |        |

| High-Band                                             |          | 20.0 |              | 300  | ms     |

| Mid-Band                                              |          | 40.0 |              | 600  | ms     |

| Xtal/Clock Frequency (f <sub>XTAI</sub> )             |          | 3.9  | _            | 6.0  | MHz    |

| · XTAL                                                |          |      |              |      |        |

|                                                       |          |      |              |      |        |

#### Notes

- 1. Device control pins; Serial Clock, Command Data, and CS.

- 2. Reply Data output.

- 3. 4.

- Reply Data and  $\overline{\text{IRQ}}$  outputs. Leakage current into the "Off"  $\overline{\text{IRQ}}$  output.

- 5. Measurement Period = 9.125ms.

- 6. Decode Probability = 0.993.

- 7. Measurement Period = 18.250ms.

- 8. When set to Powersave.

- 9. For a good input signal.

- The use of the FX803 at Xtal/clock frequencies above 4.0MHz will cause a shift in the overall performance parameters.

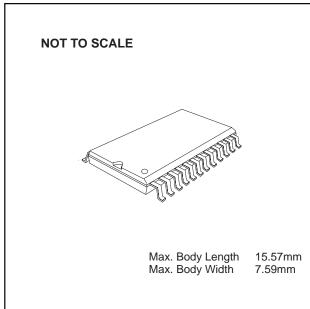

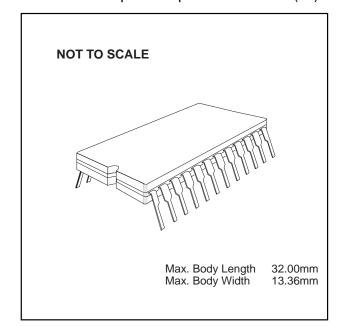

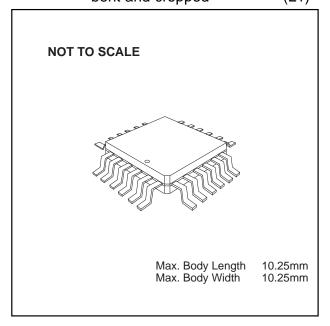

# **Package Outlines**

The FX803 is available in the package styles outlined below. Mechanical package diagrams and specifications are detailed in Section 10 of this document. Pin 1 identification marking is shown on the relevant diagram and pins on all package styles number anti-clockwise when viewed from the top.

**FX803DW** 24-pin plastic S.O.I.C.

The FX803 is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

(D2)

**FX803J**

24-pin cerdip DIL

(J4)

**FX803LG** 24-pin quad plastic encapsulated bent and cropped (L1)

**FX803LS** 24-lead plastic leaded chip carrier (L2)

**Ordering Information**

**FX803DW** 24 pin plastic S.O.I.C. (D2) **FX803J** 24-pin cerdip DIL (J4) Max. Body Length Max. Body Width 10.40mm

**FX803LG** 24-pin encapsulated bent and cropped (L1)

**FX803LS** 24-lead plastic leaded chip carrier (L2)

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.

#### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (Consumer Microcircuits Limited (UK), MX-COM, Inc. (USA) and CML Microcircuits (Singapore) Pte Ltd) have undergone name changes and, whilst maintaining their separate new names (CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

COMMUNICATION SEMICONDUCTORS

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

4800 Bethania Station Road. Winston-Salem, NC 27105, USA Tel: +1 336 744 5050,

0800 638 5577 Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307

Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com

D/CML (D)/1 February 2002