No.3802A,

LC7233

# Single-chip PLL and Microcontroller with LCD Driver

## **OVERVIEW**

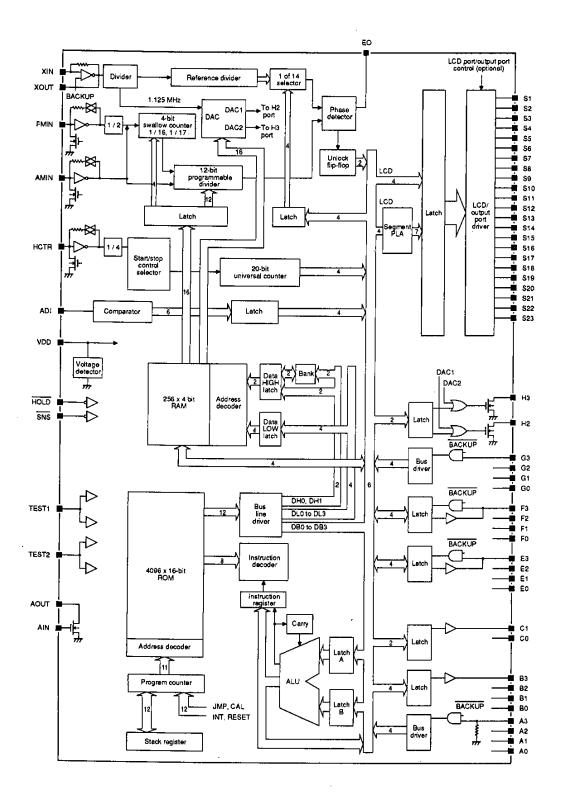

The LC7233 is a single-chip microcontroller that incorporates a phase-locked loop (PLL), which can operate up to 150 MHz, and a liquid-crystal display (LCD) driver, making it ideal for digital tuners. It has a large number of input/output ports and a frequency measurement circuit.

The LC7233 features on-chip RAM and ROM, a programmable high-speed divider, a 6-bit analog-to-digital converter and a low-voltage detection reset circuit.

The LC7233 operates from a single 5 V supply and is available in 64-pin QIPs.

## **FEATURES**

- · 150 MHz phase-locked loop

- LCD driver

- 6-bit analog-to-digital converter

- Two 8-bit PWM digital-to-analog converters

- Two 4-bit input ports

- Two 4-bit input/output ports

- · 6-bit keypad matrix scan output

- 2-bit open-drain high-voltage output

- 23 mask-selectable output drivers

- 20-bit universal counter

- 4096 × 16-bit program ROM (000H to FFEH user-addressable memory)

- $256 \times 4$ -bit data RAM

- · Low-voltage detection reset circuit

- Programmable high-speed divider

- Single-word instructions

- Four-level stack

- PLL-unlocked flip-flop

- Timer flip-flop

- · Programmable watchdog interrupt address

- Standby mode

- CPU operates down to 3.5 V, with data retention down to 1.3 V.

- Single 5 V supply

- 64-pin QIP

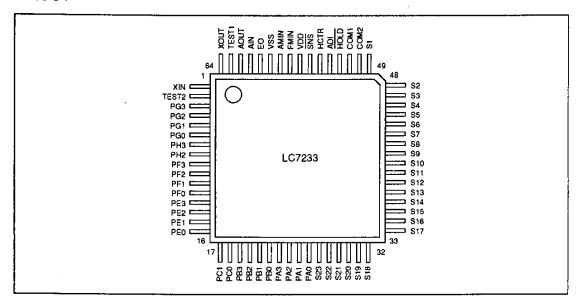

#### **PINOUT**

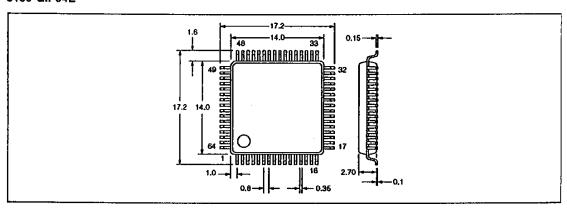

#### **PACKAGE DIMENSIONS**

Unit: mm

#### 3159-QIP64E

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall;

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

# **BLOCK DIAGRAM**

# PIN DESCRIPTION

| Number   | Name       | Equivalent circuit | Description                    |

|----------|------------|--------------------|--------------------------------|

| 1        | XIN        | XIN =              | Crystal oscillator connections |

| 64       | XOUT       | XOUT               |                                |

| 2        | TEST2      |                    |                                |

| 63       | TEST1      |                    | Test pins                      |

| 3 to 6   | PG3 to PG0 | BACKUP             | Input port G                   |

| 7, 8     | PH1, PH0   | BACKUP<br>         | Output port H                  |

| 9 to 12  | PF3 to PF0 | BACKUP             | Input/output port F            |

| 13 to 16 | PE3 to PE0 |                    | Input/output port E            |

| 17, 18   | PC1, PC0   |                    | Output port C                  |

| 19 to 22 | PB3 to PB0 | BACKUP             | Output port B                  |

| 23 to 26 | PA3 to PA0 | BACKUP             | Input port A                   |

| Number   | Name        | Equivalent circuit          | Description               |

|----------|-------------|-----------------------------|---------------------------|

| 27 to 49 | \$23 to \$1 | BACKUP                      | LCD segment outputs       |

| 50, 51   | COM2, COM1  | BACKUP                      | LCD common driver outputs |

| 52       | HOLD        |                             | Hold-mode control input   |

| 55       | SNS         |                             | Power-fail detect         |

| 53       | ADI         | ref HOLD PLISTOP controlled | A/D converter input       |

| 54       | HCTR        | HOLD. PLISTOP controlled    | Universal counter input   |

| 56       | VDD         |                             | 5 V supply                |

| 57       | FMIN        |                             | FM VCO input              |

| 58       | AMIN        | HOLO, PLLSTOP controlled    | AM VCO input              |

| 59       | VSS         |                             | Ground                    |

| Number | Name | Equivalent circuit | Description             |

|--------|------|--------------------|-------------------------|

| 60     | EO   | J                  | Phase comparator output |

| 61     | AIN  | AIN .              | Analog input            |

| 62     | AOUT | AOUT HE THE        | Analog output           |

# **SPECIFICATIONS**

# **Absolute Maximum Ratings**

| Parameter                                     | Symbol              | Rating                   | Unit   |

|-----------------------------------------------|---------------------|--------------------------|--------|

| Supply voltage range                          | V <sub>DD</sub> max | -0.3 to 6.5              | V      |

| Port G, HOLD, ADI and SNS input voltage range | V <sub>IN1</sub>    | -0.3 to 13               | V      |

| Input voltage range (other inputs)            | V <sub>IN2</sub>    | $-0.3$ to $V_{DD} + 0.3$ | ٧      |

| Port H and AOUT output voltage range          | V <sub>out1</sub>   | →0.3 to 15               | V      |

| Output voltage range (all other outputs)      | V <sub>OUT2</sub>   | $-0.3$ to $V_{DD} + 0.3$ | V      |

| Port H output current range                   | I <sub>OUT1</sub>   | 0 to 5                   | mA     |

| Ports E and F output current range            | I <sub>OUT2</sub>   | 0 to 3                   | mA     |

| Ports B and C output current range            | Гоитз               | 0 to 1                   | mA     |

| AOUT output current range                     | lour4               | 0 to 2                   | mA     |

| Power dissipation                             | Po                  | 400                      | mW     |

| Operating temperature range                   | Topr                | -40 to 85                | deg. C |

| Storage temperature range                     | T <sub>stg</sub>    | -45 to 125               | deg. C |

# **Recommended Operating Conditions**

$T_a = 25 \text{ deg. C}$

| Parameter                               | Symbol           | Rating     | Unit |

|-----------------------------------------|------------------|------------|------|

| Supply voltage                          | V <sub>DO</sub>  | 5          | V    |

| Supply voltage range (PLL and CPU)      | V <sub>DD1</sub> | 4.5 to 5.5 | V    |

| Supply voltage range (CPU)              | V <sub>DD2</sub> | 3.5 to 5.5 | V    |

| Supply voltage range for data retention | V <sub>DD3</sub> | 1.3 to 5.5 | V    |

# **Electrical Characteristics**

$V_{\text{DD}} = 3.5$  to 5.5 V,  $T_{\text{a}} = -40$  to 85 deg. C unless otherwise noted

| Parameter                                             | Comba!           | Candition                                                                                           |                    | Rating |                    | Unit  |

|-------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-------|

| rarallister                                           | Symbol           | Condition                                                                                           | min                | typ    | max                | Ollik |

| Port G HIGH-level input voltage                       | V <sub>IH1</sub> |                                                                                                     | 0.7V <sub>DD</sub> | _      | 8.0                | ٧     |

| SNS HIGH-level input voltage                          | V <sub>IH2</sub> |                                                                                                     | 2.5                | -      | 8.0                | ٧     |

| Port A HIGH-level input voltage                       | V <sub>IH3</sub> |                                                                                                     | 0.6V <sub>DD</sub> | -      | V <sub>DD</sub>    | ٧     |

| Ports E and F HIGH-level input voltage                | V <sub>IH4</sub> |                                                                                                     | 0.7V <sub>DD</sub> | _      | V <sub>DD</sub>    | ٧     |

| HOLD HIGH-level input voltage                         | V <sub>IH5</sub> |                                                                                                     | 0.8V <sub>DD</sub> | _      | 8.0                | ٧     |

| Port G LOW-level input voltage                        | V <sub>IL1</sub> |                                                                                                     | 0                  | -      | 0.3V <sub>DD</sub> | ٧     |

| HOLD LOW-level input voltage                          | VIL2             |                                                                                                     | 0                  | -      | 0.4V <sub>DD</sub> | ٧     |

| SNS LOW-level input voltage                           | V <sub>IL3</sub> |                                                                                                     | 0                  | -      | 1.3                | ٧     |

| Port A LOW-level input voltage                        | V <sub>IL4</sub> |                                                                                                     | 0                  | -      | 0.2V <sub>DD</sub> | ٧     |

| Ports E and F LOW-level input voltage                 | V <sub>IL5</sub> |                                                                                                     | 0                  | _      | 0.3V <sub>DD</sub> | ٧     |

| XIN input frequency                                   | f <sub>IN1</sub> | V <sub>IN</sub> = 0.5 to 1.5 V                                                                      | 4.0                | 4.5    | 5.0                | MHz   |

| FMIN input frequency                                  |                  | V <sub>IN</sub> = 0.1 to 1.5 V,<br>V <sub>DD</sub> = 4.5 to 5.5 V                                   | 10                 | -      | 130                | MHz   |

| willy input nequelicy                                 | fin2             | $V_{IN} = 0.15 \text{ to } 1.5 \text{ V},$<br>$V_{DD} = 4.5 \text{ to } 5.5 \text{ V}$              | 10                 | _      | 150                | ₩IΠZ  |

| AMIN input frequency<br>(low range)                   | fins             | V <sub>IN</sub> = 0.1 to 1.5 V,<br>V <sub>DD</sub> = 4.5 to 5.5 V                                   | 0.5                | -      | 10                 | MHz   |

| AMIN input frequency<br>(high range)                  | fin4             | $V_{IN} = 0.1$ to 1.5 V,<br>$V_{DD} = 4.5$ to 5.5 V                                                 | 2.0                | _      | 40                 | MHz   |

| HCTR input frequency                                  | fins             | V <sub>IN</sub> = 0.1 to 1.5 V,<br>V <sub>DD</sub> = 4.5 to 5.5 V                                   | 0.4                | -      | 12                 | MHz   |

| XIN rms input amplitude                               | V <sub>IN1</sub> |                                                                                                     | 0.5                |        | 1.5                | ٧     |

| FMIN rms input amplitude                              | V <sub>IN2</sub> |                                                                                                     | 0.1                | -      | 1.5                | ٧     |

| AMIN rms input amplitude                              | V <sub>IN3</sub> |                                                                                                     | 0.1                |        | 1.5                | ٧     |

| HCTR rms input amplitude                              | V <sub>IN4</sub> |                                                                                                     | 0.1                | _      | 1.5                | ٧     |

| ADI input voltage range                               | V <sub>IN5</sub> |                                                                                                     | 0                  | _      | V <sub>DD</sub>    | ٧     |

| SNS reject pulsewidth                                 | P <sub>rej</sub> |                                                                                                     | , <u> </u>         | -      | 50                 | μ\$   |

| Standby threshold voltage                             | V <sub>DET</sub> |                                                                                                     | 2.7                | 3.0    | 3.3                | ٧     |

| HOLD, ADI, SNS and port G<br>HIGH-level input current | liH1             | V <sub>IN</sub> = 5.5 V                                                                             | _                  | -      | 3.0                | μА    |

| Ports A, E and F HIGH-level<br>input current          | l <sub>IH2</sub> | Ports E and F are high impedance, port A has no R <sub>PD</sub> , V <sub>IN</sub> = V <sub>DD</sub> | _                  | -      | 3.0                | μΑ    |

| XIN HIGH-level input current                          | l <sub>IH3</sub> | $V_{IN} = V_{DD} = 5.0 \text{ V}$                                                                   | 2                  | 5      | 15                 | μΑ    |

| FMIN, AMIN and HCTR<br>HIGH-level input current       | 11114            | V <sub>IN</sub> = V <sub>DD</sub> = 5.0 V                                                           | 4                  | 10     | 30                 | μА    |

| Port A HIGH-level input current                       | I <sub>IH5</sub> | $V_{IN} = V_{OD} = 5.0 \text{ V},$<br>port A has $R_{PD}$                                           | -                  | 50     | _                  | μΑ    |

| AIN HIGH-level input current                          | I <sub>tH6</sub> | VIN = VDD                                                                                           |                    | 0.01   | 10.00              | nA    |

| Downston                                             | A                  |                                                                                         | T                      | Rating                |                       | 0-4  |

|------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------|------|

| Parameter                                            | Symbol             | Condition                                                                               | min                    | typ                   | max                   | Unit |

| HOLD, ADI, SNS and port G<br>LOW-level input current | l <sub>IL1</sub>   | VIN = VSS                                                                               | -                      | -                     | 3.0                   | μА   |

| Ports A, E and F LOW-level input current             | l <sub>IL2</sub>   | Ports E and F are high impedance, port A has no R <sub>PD</sub> , V <sub>IN</sub> = Vss | _                      | -                     | 3.0                   | μА   |

| XIN LOW-level input current                          | I <sub>(L3</sub>   | V <sub>IN</sub> = V <sub>SS</sub>                                                       | 2                      | 5                     | 15                    | μΑ   |

| FMIN, AMIN and HCTR<br>LOW-level input current       | I <sub>IL4</sub>   | Vin = Vss                                                                               | 4                      | 10                    | 30                    | μА   |

| AIN LOW-level input current                          | I <sub>IL5</sub>   | V <sub>IN</sub> = V <sub>SS</sub>                                                       | -                      | 0,01                  | 10.0                  | nA   |

| Port A input voltage                                 | V <sub>IF</sub>    | Port A is high impedance                                                                | _                      | -                     | 0.05V <sub>DO</sub>   | ٧    |

| Port A pull-down resistance                          | R <sub>PD</sub>    | V <sub>DD</sub> = 5 V                                                                   | 75                     | 100                   | 200                   | kΩ   |

| EO output leakage current                            | l <sub>OFFH1</sub> | Vo = VDD                                                                                | _                      | 0.01                  | 10.0                  | nA   |

| Ports B, C, E and F output<br>leakage current        | l <sub>OFFH2</sub> | $V_0 = V_{DD}$                                                                          | -                      | -                     | 3.0                   | μΑ   |

| Port H output leakage current                        | Тоггнз             | V <sub>0</sub> = 13 V                                                                   | -                      | -                     | 5.0                   | μА   |

| AOUT output leakage current                          | loffh4             | V <sub>0</sub> = 13 V                                                                   | -                      | -                     | 1.0                   | μА   |

| EO output leakage current                            | I <sub>OFFL1</sub> | V <sub>0</sub> = V <sub>SS</sub>                                                        | _                      | 0.01                  | 10.0                  | nA   |

| Ports B, C, E and F output<br>leakage current        | loffL2             | Vo = Vss                                                                                | -                      | ı                     | 3.0                   | μΑ   |

| Ports B and C HIGH-level output voltage              | V <sub>OH1</sub>   | I <sub>0</sub> = 1 mA                                                                   | V <sub>DD</sub> - 2.0  | V <sub>DD</sub> - 1.0 | V <sub>DD</sub> - 0.5 | V    |

| Ports E and F HIGH-level output voltage              | V <sub>OH2</sub>   | I <sub>0</sub> = 1 mA                                                                   | V <sub>DD</sub> 1.0    | -                     | -                     | ٧    |

| EO HIGH-level output voltage                         | V <sub>OH3</sub>   | l <sub>0</sub> = 500 μA                                                                 | V <sub>DD</sub> - 1.0  | _                     | -                     | ٧    |

| XOUT HIGH-level output voltage                       | V <sub>OH4</sub>   | l <sub>0</sub> = 200 μA                                                                 | V <sub>DD</sub> - 1.0  | -                     | -                     | ٧    |

| S1 to S23 HIGH-level output voltage                  | V <sub>OH5</sub>   | 1 <sub>0</sub> = -0.1 mA                                                                | V <sub>DD</sub> - 1.0  | -                     | -                     | ٧    |

| COM1 and COM2 HIGH-level output voltage              | V <sub>0H6</sub>   | l <sub>0</sub> = 25 μA                                                                  | V <sub>DO</sub> - 0.75 | -                     | -                     | ٧    |

| Ports B and C LOW-level output voltage               | V <sub>0L1</sub>   | lo = 50 μA                                                                              | 0.5                    | 1.0                   | 2.0                   | V    |

| Ports E and F LOW-level output voltage               | V <sub>OL2</sub>   | I <sub>0</sub> = 1 mA                                                                   | -                      | _                     | 1.0                   | ٧    |

| EO LOW-level output voltage                          | V <sub>OL3</sub>   | I <sub>0</sub> = 500 μA                                                                 | _                      | -                     | 1.0                   | ٧    |

| XOUT LOW-level output voltage                        | V <sub>OL4</sub>   | Ι <sub>0</sub> = 200 μΑ                                                                 | _                      | _                     | 1.0                   | ٧    |

| S1 to S23 LOW-level output voltage                   | V <sub>OL5</sub>   | l <sub>0</sub> = 0.1 mA                                                                 | -                      | -                     | 1.0                   | ٧    |

| AOUT LOW-level output voltage                        | V <sub>OL6</sub>   | i <sub>0</sub> = 5 mA,<br>AIN = 1.3 V                                                   |                        |                       | 0.5                   | ٧    |

| COM1 and COM2 LOW-level output voltage               | V <sub>OL7</sub>   | Ιο = 25 μΑ                                                                              | 0.3                    | 0.5                   | 0.75                  | ٧    |

| Port H LOW-level output voltage                      | Vola               | l <sub>0</sub> = 5 mA                                                                   | 0.75                   | -                     | 2.0                   | ٧    |

| COM1 and COM2 mid-level output voltage               | V <sub>M1</sub>    | V <sub>DD</sub> = 5 V, I <sub>0</sub> = 20 μA                                           | 2.0                    | 2.5                   | 3.0                   | ٧    |

| Parameter                   | Sumbal           | Condition                                                                     |       | Rating |     | Unit |

|-----------------------------|------------------|-------------------------------------------------------------------------------|-------|--------|-----|------|

| r al allictor               | Symbol           | Condition                                                                     | min   | typ    | max | Unii |

| A/D converter error         | ε                | V <sub>DD</sub> = 4.5 to 5.5 V                                                | - 1/2 | -      | 1/2 | lsb  |

| Supply current              | I <sub>DD1</sub> | f <sub>in</sub> = 130 MHz,<br>V <sub>DD</sub> = 4.5 to 5.5 V                  | _     | 15     | 20  | mA   |

|                             |                  | PLL halted,<br>t <sub>cyc</sub> = 2.67 μs                                     | -     | 1.5    | _   |      |

| Hold-mode supply current    | I <sub>DD2</sub> | PLL halted,<br>t <sub>cyc</sub> = 13.33 μs,<br>V <sub>DD</sub> = 3.5 to 5.5 V | -     | 1.0    | _   | mA   |

|                             |                  | PLL halted, $t_{cyc} = 40.00 \ \mu s$ , $V_{DD} = 3.5 \ to \ 5.5 \ V$         | -     | 0.7    |     |      |

| Standby-mode supply current |                  | $V_{DD}$ = 5.5 V, oscillator halted, $T_a$ = 25 deg. C                        | -     | _      | 5   |      |

| ошниму-тнойе заррту ситтепт | I <sub>DD3</sub> | $V_{DO} = 2.5 \text{ V, oscillator}$<br>halted, $T_a = 25 \text{ deg. C}$     | _     | -      | 1   | μА   |

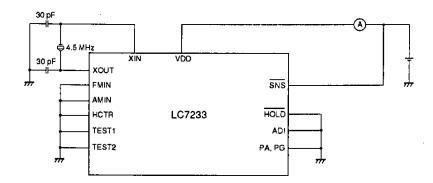

# **Measurement Circuits**

## Hold mode

# Notes

- 1. Ports E and F are selected as output ports.

- 2. Ports A to H, S1 to S23, COM1 and COM2 are open.

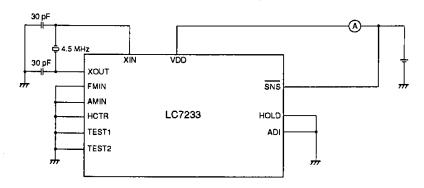

# Standby mode

# Note Ports A to H, S1 to S23, COM1 and COM2 are open.

# **FUNCTIONAL DESCRIPTION**

#### **LCD** Driver

The LC7233 can drive LCD segments. The LCP and LCD instructions transfer data to the LCD outputs. The LCD instruction transfers data directly to the LCD outputs. The LCP instruction converts data to 7-segment format before transfer to the outputs.

S1 to S23 are the driver outputs. The LCD frame rate is 100 Hz with a 50% duty cycle. After reset or power-up, a blank signal is present on all outputs. In standby mode, all outputs are LOW. They can be used as general-purpose outputs if the appropriate mask option is selected.

COM1 and COM2 are the LCD common driver outputs. Output drive is 50% duty with 50% bias. Upon reset or after power-up, the normal drive signals are present on these outputs. In standby mode, all outputs are LOW.

## Frequency Counter

Frequency measurement is performed at the HCTR input by the 20-bit universal counter. The input frequency range is 0.4 to 12 MHz, which is used for measuring AM and FM IF frequencies. Capacitive coupling should be used.

## Phase-locked Loop

The FMIN or AMIN input signal is divided down by a programmable divider, and then compared with the crystal frequency, which is also divided down using 14 selectable ratios. The phase difference between the two signals is measured using a phase detector and output on EO.

FMIN is the input pin for the FM VCO input signal. The input frequency range is 10 to 130 MHz. Capacitive coupling should be used.

AMIN is the AM VCO input. The bandwidth is adjustable in two ranges by using the PLL instruction—HIGH (2 to 40 MHz) for the SW band, and LOW (0.5 to 10 MHz), for the LW and MW bands. Capacitive coupling should be used.

#### Input/Output Ports

# Port A

This input port has a low switching threshold, which is used for keypad matrix inputs. Pull-down resistors for all pins are available as a mask option. Note that either all or none of the pins should have pull-down resistors. In standby mode, inputs are ignored.

#### Ports B and C

These output ports have unbalanced CMOS outputs which are used as keypad matrix scan outputs. Upon reset, outputs are set LOW, and in standby mode, outputs are high impedance. The outputs can be short-circuited.

#### Port E

The transfer direction of this input/output port is selected automatically under software control. When an input instruction (IN, TPT, or TPF) is executed, port E is configured for input operation, and an output instruction (OUT, SPB or RPB), for output operation. Upon reset, all pins become inputs. In standby mode, the output drivers are high impedance and the input signals are ignored. All bits should either be inputs or outputs.

#### Port F

The transfer direction of this input/output port is selected by the FPC instruction. Each pin of this port can be set independently to be an input or output. Upon reset, all pins become inputs. In standby mode, the output drivers are high impedance and the input signals are ignored.

#### Port G

This is an input port only. In standby mode, inputs are ignored.

#### Port H

These output ports are high-voltage, n-channel open-drain drivers, which are used for switching power supplies. Upon reset and in standby mode, outputs are high impedance. Port H can also be configured as the output of DACI and DAC2.

#### A/D Converter

The A/D converter is a 6-bit successive approximation type. The conversion cycle time is 1.28 ms. Full-scale output data is 3FH for an input of  $V_{DD} \times (63/96)$ .

#### Power-fail Detection

When connected to the supply,  $\overline{SNS}$  is used as a power-fail detector.  $\overline{SNS}$  can also be used as a standard input port.

#### Crystal Oscillator

The master crystal oscillator, which has a feedback resistor on-chip, requires only the connection of a 4.5 MHz crystal.

## **Low-power Modes**

#### Hold mode

When the hold-mode control pin, HOLD, is driven LOW and the HOLDEN (hold enable) flip-flop has previously been set by an SS instruction, the LC7233 enters hold mode.

$\overline{HOLD}$  has a high-voltage input (V<sub>IH</sub>(max) = 8.0 V) which can be connected directly to the power supply.

#### Standby mode

When the LC7233 is in hold mode and HOLD is LOW, standby mode can be set by the CKSTP instruction.

#### Test Pins

Two device test pins are provided—TEST1 and TEST2. These should either be tied to Vss or left open.

# INSTRUCTION SET

| ADDR | Program memory address [12 bits]                             |

|------|--------------------------------------------------------------|

| b    | Borrow                                                       |

| В    | Bank number [2 bits]                                         |

| С    | Carry                                                        |

| DH   | Data memory address high-order bits (row address) [2 bits]   |

| DL   | Data memory address low-order bits (column address) [4 bits] |

| I    | Immediate data [4 bits]                                      |

| M    | Data memory address                                          |

| N    | Bit position [4 bits]                                        |

| Pn   | Port number [4 bits]                                         |

| T    | General register (Bank 00H to 0FH)                           |

| Rn   | Register number [4 bits]                                     |

| ()   | Contents of register or memory                               |

| ( )n | Contents of bit N of register or memory                      |

| Operand                                                                        |                                                              | Oreration                  |                        |                    | 1 1            |            |         |   |          | Instruction format | n format |           |                       |          |    |   | i i                                               | Parentalists                                                                                                              |                |

|--------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------|------------------------|--------------------|----------------|------------|---------|---|----------|--------------------|----------|-----------|-----------------------|----------|----|---|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|

| 1st 2nd 015 014 013 012 011 010 09 08                                          | D15 D14 D13 D12 D11 D10 D9                                   | D15 D14 D13 D12 D11 D10 D9 | D14 D13 D12 D11 D10 D9 | D13 D12 D11 D10 D9 | D12 D11 D10 D9 | D11 D10 D9 | D110 D9 | 8 | Н        |                    | D7 D6    | 8         | 5 04                  | 8        | 8  | 8 | MUZUON                                            | Versingbook                                                                                                               | Skip condition |

|                                                                                |                                                              |                            | :                      |                    | :              |            |         |   |          | . 1                |          | Addin     | Add instructions      |          |    |   |                                                   |                                                                                                                           |                |

| r M Add M to r 0 1 0 0 0 0 DH                                                  | Add N to 7 0 1 0 0 0 0                                       | . 0 1 0 0 0 0              | 1 0 0 0 0              | 0 0 0 0            | 0 0            | 0          | 0       |   | 吾        |                    |          | ᄓ         |                       |          | Æ  |   | (v) + (v) + (v)                                   | Adds the contents of M to the contents of r and stores the result in r                                                    |                |

| r M Add M to r and 0 1 0 0 1 DH skip if carry                                  | Add M to r and 0 1 0 0 1 skp if carry                        | Mitorand 0 1 0 0 1         | 1 0 0 0 1              | 0 0 0 1            | 0 0 1          | 0 1        | -       |   | ¥ .      |                    |          | ٦.        |                       |          | 뜐  |   | $r \leftarrow (r) + (M)$ , skip if carry          | Adds the contents of M to the contents of r and stores the result in r. Skips if a carry is generated                     | Carry          |

| r Mr Add M to r 0 1 0 0 1 0 DH                                                 | Add M to r 0 1 0 0 1 0 With carry                            | r 0 1 0 0 1 0              | 1 0 0 1 0              | 0 0 1 0            | 0 1 0          | 1 0        |         |   | 핆        |                    |          | ಕ         | . ]                   |          | R. |   | 2 + (M) + C                                       | Adds the contents of M to the contents of r and C and stores the result in r                                              |                |

| r M with carry and 0 1 0 0 1 1 DH skip if carry                                | Add M lo r with carry and 0 1 0 0 1 1 skip if carry          | 0 1 0 0 1 1                | 1 0 0 1                | 0 0 1 1            | 1 1            | 1          | -       |   | 舌        |                    |          | ח         |                       |          | Rn |   | $\Gamma \leftarrow (I) + (M) + C$ , skip if carry | Adds the content of M to the contents of r and C and stores the result in r. Skips if a carry is generated                | Camy           |

| M 1 Add 10 M 0 1 0 1 0 0 DH                                                    | Add 1 0 1 0 0 0                                              | M 0 1 0 1 0 0              | 1 0 1 0 0              | 0 1 0 0            | 1 0 0          | 0 0        | 0       |   | HO       |                    |          | DL        |                       |          | -  |   | M ← (M) + I                                       | Adds the immediate data to the contents of M and stores the result in M                                                   |                |

| M I Add to M and 0 1 0 1 0 1 DH                                                | Add I to M and 0 1 0 1 0 1                                   | and 0 1 0 1 0 1            | 1 0 1 0 1              | 0 1 0 1            | 1 0 1          | 0 1        | -       | - | 폽        |                    |          | <b>т</b>  |                       |          | -  |   | $M \leftarrow (M) + I, \ skip \ \text{if}$ carry  | Adds the inninediate data to the contents of M and stores the result in M. Skips if a carry is generated                  | Camy           |

| M I Add to M 0 1 0 1 1 0 DH with carry                                         | Add to M 0 1 0 1 1 0                                         | 0 1 0 1 0                  | 1 0 1 1 0              | 0 1 1 0            | 1 1 0          | 0 1        |         |   | 품        |                    |          | ด         |                       |          | -  |   | M ← (M) + 1 + C                                   | Adds the immediate data to the contents of M and C and stores the result in M                                             |                |

| M i with carry and 0 1 0 1 1 1 DH skip if carry                                | Add I to M with carry and 0 1 0 1 1 1 skip if carry          | 0 1 0 1 1                  | 1 0 1                  | 1 1                | -              | -          |         |   | 퓹        |                    |          | ٥٦        |                       |          | 1  |   | $M \leftarrow (M) + I + C$ , skip if carry        | Adds the immediate data to the contents of M and C and stores the result in M. Skips if a carry is generated              | Csm            |

|                                                                                |                                                              |                            |                        |                    |                |            |         |   |          |                    | S        | offract i | Subtract instructions | <b>1</b> |    |   |                                                   |                                                                                                                           |                |

| r M Subtract M 0 1 1 0 0 0 DH from r                                           | Subtract M 0 1 1 0 0 0                                       | 0 1 1 0 0 0                | 1 1 0 0 0              | 1 0 0 0            | 0 0 0          | 0 0        | D       |   | 품        |                    |          | Dr.       |                       |          | 뜐  |   | $r \leftarrow (r) - (M)$ skip if carry            | Subtracts the contents of M from the contents of r and stores the result in r                                             |                |

| r M from r and skip 0 1 1 0 0 1 DH if borrow                                   | Subtract M trom r and Skip 0 1 1 0 0 1                       | skip 0 1 1 0 0 1           | 1 0 0 1                | 0 0 1              | 1              | 1          |         |   | <b>å</b> |                    |          | 10        |                       |          | Ŗ  |   | r <- (r) - (M), skip if<br>borrow                 | Subtracts the contents of M from the contents of r and stores the result in r. Skips if a borrow is generated             | Ватгож         |

| r M from r with 0 1 1 0 1 0 DH borrow                                          | Subtract M 0 1 1 0 1 0 borrow                                | 0 1 1 0 1                  | - 0                    | 0 0                | - 0            | 0          |         |   | 푬        |                    |          | ы         |                       |          | 몺  | , | r ← (r) – (M) – b                                 | Subtracts the contents of M from the contents of r<br>with borrow and stores the result in r                              | ·              |

| Subtract M from r with 0 1 1 0 1 1 DH borrow and skip 0 1 1 0 1 1 DH if borrow | Subtract M from r with 0 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 | skip 0 1 1 0 1 1           | 0                      | -                  |                | -          |         |   | 퓹        | _                  |          | DF.       |                       |          | R. |   | r ← (r) – (M) – b, sköp<br>ří borrow              | Subtracts the contents of M from the contents of r with borrow and stores the result in r. Skips if a borrow is generated | Borrow         |

| M i Subtract I from 0 1 1 1 0 0 DH                                             | Subtract I from 0 1 1 1 0 0                                  | 0 1 1 1 0                  | 1 1 0 0                | 1 1 0 0            | 1 0 0          | 0 0        | 0       |   | 5        | 7                  |          | טר        |                       |          | 1  |   | M ← (M) - I                                       | Subtracts the immediate data from the contents of M and stores the result in M                                            |                |

| M i Subtract i from 6 1 1 1 0 1 E                                              | Subtract I from M and skip if 0 1 1 1 0 1 borrow             | 1 1 0 5                    | 1 1 0 0                | 1 1 0 1            | 1 0 1          | 1          | -       |   | _        | 吾                  |          | ם         |                       |          | -  |   | M ← (M) – l, skip if<br>borrow                    | Subtracts the immediate data from the contents of M and stores the result in M. Skips if a borrow is generated            | Вогтож         |

| M Subtract 1 from 0 1 1 1 1 0 D                                                | Subtract I from 0 1 1 1 1 0 Meth borrow                      | 0 1 1 1 0                  | 1 1 1 0                | 1 1 0              | 1 1 0          | 0 1        |         |   |          | 품                  |          | 占         |                       |          | -  | ŀ | $M \leftarrow (M) - 1 - b$                        | Subtracts the immediate data from the contents of M with borrow and stores the result in M                                |                |

|       |          | Operand      | j                                                |      |    |     | İ   | ;   |              | Instructi | Instruction format            |                      |             | 1                                    |                                                                                                                            |                    |

|-------|----------|--------------|--------------------------------------------------|------|----|-----|-----|-----|--------------|-----------|-------------------------------|----------------------|-------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------|

| 9012  | 181      | 2md          | Operation                                        | 9115 | 94 | D13 | 210 | 110 | DIG          | 20        | D7 D6 D5                      | 104                  | 03 02 01 00 | Notabbn                              | UCECTIFICON                                                                                                                | Serie contribution |

| Sibs  | ×        | <del>-</del> | Subtract I from M with borrow and skip if borrow | 0    | -  | -   | -   | -   | <del>-</del> | на        | 70                            |                      | -           | M ← (M) · I ·· b, skip<br>ř borrow   | Subtracts the immediate data from the contents of M with borrow and stores the result in M. Skips if a borrow is generated | Barrow             |

|       | 1        |              |                                                  |      |    |     |     |     |              |           | Compare                       | Compare instructions |             |                                      |                                                                                                                            |                    |

| SEO   | _        | ≥            | Skip if r equals<br>M                            | 0    | 0  | 0   | 0   | 0   | -            | 吾         | 70                            |                      | Rn          | (r) - (M), skip if zero              | Compares the contents of r and M and skips if they are equal                                                               | (yy) = (1)         |

| SGE   | _        | ₹            | Skip if r is<br>greater than or<br>equal to M    | 0    | 0  |     | 0   | -   | -            | 품         | מר                            |                      | 뜐           | (r) – (M), skip ri<br>(r) ≥ (M)      | Compares the contents of r and M and skips if r is greater than or equal to M                                              | (N) < (J)          |

| SEOI  |          | _            | Skip if M<br>equals I                            | •    | -  | -   | -   | -   | -            | H         | 10                            |                      | -           | (M) - 1, skip if zero                | Compares the immediate data to the contents of M and skips if they are equal                                               | 0 = 1 - (M)        |

| EE 98 | Σ        | _            | Skip if M is<br>greater than or<br>equal to 1    |      | 0  | -   | -   | -   | -            | 푬         | ಕ                             |                      | _           | (M) - 1, skip if (M) ≥ l             | Compares the contents of M with the inmediate data and skips if M is greater than or equal to I                            | - ^:<br>(N)        |

|       |          |              |                                                  |      |    | 1   | 1   | 1   |              |           | Logic arithmetic instructions | tic instructi        | OUS         |                                      |                                                                                                                            |                    |

| AND   |          | _            | AND I with M                                     | 0    | 0  | -   | -   | 0   |              | 푬         | ಕ                             |                      | _           | M ← (M) · 1                          | Calculates the logic-AND of the immediate data and the contents of M and stores the result in M                            |                    |

| HO.   | ₽        | _            | OR I with M                                      | 0    | 0  | -   |     | -   | 0            | HO        | ю                             |                      | -           | M <- (M) + 1                         | Calcustres the logic-OR of the immediate data and the contents of M and stores the result in M                             |                    |

| EXI   | -        | æ            | Exclusive-OR M<br>with r                         | 0    | 0  | -   | 0   | b   | 0            | 吾         | 70                            |                      | 뜐           | $r \leftarrow (r) \text{ oplus (M)}$ | Calculates the logic-XOR of the contents of r and M, and stores the result in r                                            |                    |

|       |          |              |                                                  |      |    |     |     |     |              |           | Load and ston                 | stare instructions   | Oms         |                                      |                                                                                                                            |                    |

| ОП    | <u>.</u> | ≥            | Lozd M into r                                    | -    | •  | •   | -   |     | 0            | 품         | ъ                             |                      | 器           | r ← (M)                              | Moves the contents of M to r                                                                                               |                    |

| ST    | 2        | -            | Store r in M                                     | -    | 0  | ė,  | 0   | 0   | -            | H         | טר                            |                      | Rn          | M ← (f)                              | Moves the contents of r to M                                                                                               |                    |

| MVRD  | _        | W            | Move M to M<br>addressed by<br>Rn                | -    | 0  | 0   | 0   | -   | 0            | . B       | Dr.                           |                      | 뜐           | [DH, Rn] ← (M)                       | Moves the contents of M to the address referenced by DH and Rn                                                             |                    |

| MVRS  | Σ        | I            | Move M<br>addressed by<br>Rn to M                | -    | 0  | 0   | 0   | -   |              | H         | 70                            |                      | Æ           | M ← [OH, Rn]                         | Moves the contents of the memory location referenced by DK and Rn to M                                                     |                    |

| MVSR  | ₩.       | W            | Move M to M                                      | -    | 0  | 0   | -   | 0   |              | 苦         | 0.1                           |                      | DL2         | [DH.DL1] ← [DH.DL2 ]                 | Moves the contents of memory location 2 to memory location 1                                                               |                    |

| WW    | 2        | _            | Move I to M                                      | -    | -  | 0   | -   | -   | 1            | HO        | TO DE                         |                      | -           | M ← 1                                | Moves the immediate data to M                                                                                              |                    |

| ∏     | 2        | _            | Load M to PLL<br>registers                       | -    |    | 0   | -   | -   | 0            | 舌         | 10                            |                      | Rn          | PLLr ← (M)                           | Moves the contents of M to the PLL registers                                                                               |                    |

|        | ľ    |         | <u> </u>                                          |     |          |     |        |   |     |          | 1                  |           |                |                                  |              |              |        |   |                                          |                                                                                                 |                           |

|--------|------|---------|---------------------------------------------------|-----|----------|-----|--------|---|-----|----------|--------------------|-----------|----------------|----------------------------------|--------------|--------------|--------|---|------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------|

| Manage | ad n | Uperand | Operation                                         |     | [        |     |        |   |     | <u>=</u> | Instruction formal | E L       | _              |                                  |              |              |        |   | -                                        |                                                                                                 |                           |

|        | ħ    | 2nd     |                                                   | ms. | 914      | D13 | д<br>П | 듈 | 910 | 25       | 2                  | 70        | 8              | 22                               | ă            | 8            | 10 20  | 8 | NOCEOU I                                 | uond u 20041                                                                                    | Stip condition            |

|        |      |         |                                                   |     |          |     |        |   |     |          |                    |           | 2              | test instructions                | uctions      |              |        |   |                                          |                                                                                                 |                           |

| TMT    | ≥    | 2       | Test bits of M<br>and skip if true                | 1   | 0        | 1   | 0      | 0 | -   | HO       | -                  |           | Ы              |                                  |              |              | z      |   | Skôp if M(N) = all 1                     | Tests the bits of memory location M specified by N. Skips if all bits are logic 1               | All bits<br>specified = 1 |

| TMF    | 2    | 2       | Test bits of M<br>and skip if false               | -   | 0        | -   | 0      | 1 | 1   | на       | <del></del>        |           | Ы              |                                  |              |              | æ      |   | Skip if M(N) = all 0                     | Tests the bits of memory location M specified by N. Skips if all bits are logic 0               | All tits<br>specified = 0 |

|        |      |         |                                                   |     |          |     |        |   |     |          |                    | denn      | amd s          | Jump and subroutine instructions | e instru     | ertions      |        |   |                                          |                                                                                                 |                           |

| JMP    | ADI  | ADOR    | Jump to<br>address                                | -   | 0        | -   | _      |   |     |          |                    | Aſ        | ADDR (12 bits) | 2 bits)                          |              |              |        |   | PC ← ADDR                                | Jumps to the address specified by ADDR                                                          |                           |

| CAL    | ADDR |         | Call subroutine                                   | -   | -        | 0   | 0      |   |     |          |                    | A.        | ADDR (12 bits) | 2 bits)                          |              |              |        |   | Stack ← (PC) + 1,<br>PC ← ADDR           | Jumps to the subroutine specified by ADDR                                                       |                           |

| RT     |      |         | Return from<br>subroutine                         |     | -        | 0   | _      | 0 | -   | •        | 0                  | -         | -              | -                                |              | -            | 0      | - | PC ← stack                               | Returns from a subroutine                                                                       |                           |

|        |      |         |                                                   |     |          |     |        |   |     |          |                    | 1         | Fag            | test instr                       | instructions | -            | -      | } |                                          |                                                                                                 |                           |

| MIT    | Z    |         | Test timer<br>flip-flop                           | -   | 1        | 0   | 1      | - | -   | -        |                    | -         | -              | -                                |              |              | z      |   | Skip if timer F/F = 0                    | Tests the timer flip-flop and skips if zero                                                     | Timer F/F = 0             |

| 旭      | Z    |         | Test PLL<br>flip-flop                             | -   | -        | 0   | -      | 0 | -   | -        | -                  |           |                |                                  | 0            |              | 2      |   | Skip if PLL F/F = 0                      | Tests the PLL-unlocked flip-flop and skips if zero                                              | PLL F/F = 0               |

|        |      |         |                                                   |     |          |     |        |   |     | 1        | "                  | Status re | register t     | test and                         | 펉            | instructions | и      |   |                                          |                                                                                                 |                           |

| - ss   | N    |         | Set status<br>register bits                       | 1   | 1        | 0   | 1      | - | -   | 0        | 0                  | 0         | 0              | 0                                |              |              | 2      |   | (Status register 1)<br>N ← 1             | Sets the bits of the status register specified by N                                             |                           |

| RS     | N    |         | Reset status<br>register bits                     | -   | -        | 0   | -      | - | -   | •        | -                  | 0         | •              | -                                |              |              | z      |   | (Status register 1)<br>N ← 0             | Resets the bits of the status register specified by N                                           |                           |

| TST    | N    |         | Test status<br>register bits and<br>skip if true  | -   | -        | 0   | -      | - | -   | -        | •                  | -         | -              | -                                |              |              | z      |   | Skip if (status register 2)<br>N = all 1 | Tests the bits of status register 2 specified by N.<br>Skips if all bits are 1                  | All bits specified = 1    |

| TSF    | N    |         | Test status<br>register bits and<br>skip if false | -   | <b>,</b> | 0   | -      | - | -   | -        | -                  | 0         | 0              |                                  | 0            |              | æ      |   | Skip if (status register 2)<br>N = all 0 | Tests the bits of status register 2 specified by N.<br>Skips if all bits are 0                  | All bits<br>specified = 0 |

|        |      |         |                                                   |     |          |     |        |   |     |          | ĺ                  |           | Bank           | select instruction               | chuction     |              |        |   |                                          |                                                                                                 |                           |

| BANK   | -    |         | Select bank                                       | -   | -        | 0   | -      | 0 | 0   | В        |                    | 0         | 0              | 0                                | 0            | -            | 0      | 0 | BANK ← B                                 | Selects one of four memory banks                                                                |                           |

|        |      |         |                                                   |     |          |     |        |   |     |          |                    | _         | nput/on        | Input/output instructions        | truction     | 'n           | !<br>! |   |                                          |                                                                                                 |                           |

| CC)    | Σ    | -       | Move data to<br>LCD segments                      | -   | 1        | 1   | 0      | 0 | 0   | 8        |                    |           | 占              |                                  |              |              | DIGIT  |   | LCD (DIGIT) ← 1                          | Loads the immediate data directly to the LCD driver                                             |                           |

| වු     | 2    | -       | Move 7-segment<br>data to LCD                     | -   | -        | -   | 0      | 0 | -   | М        |                    |           | ᆸ              |                                  |              |              | DIGIT  |   | CD (DIGIT) ← PLA ←                       | Converts the immediate data to 7-segment format using a PLA then transfers it to the LCD driver |                           |

| Z.     | ₹    | Pn      | Move port data<br>to M                            | -   | +        | 1   | 0      | - | 0   | 품        | _                  |           | 늄              |                                  |              |              | ۔ ا    |   | M ← (part (Pn))                          | Moves the data from input port Pn to M                                                          |                           |

|        |      |         |                                                   | 1   |          |     |        |   |     | I        | 1                  |           | l              |                                  | 1            |              |        |   |                                          |                                                                                                 |                           |

| ļ     | at 0 | Operand | Omeration                                 |    |     |     |          |     |     |              | Instruction format | format |           |                                |           |     |     |   | a distribution                   | Perceittion                                                                                                                                                     | Gir<br>Seedilise          |

|-------|------|---------|-------------------------------------------|----|-----|-----|----------|-----|-----|--------------|--------------------|--------|-----------|--------------------------------|-----------|-----|-----|---|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|       | 181  | 2md     | operations                                | МS | 110 | D13 | 2112     | 110 | 910 | 2            | 2                  | D7     | 18        | 8                              | 75        | 8   | 20  | 8 |                                  | unndunen                                                                                                                                                        |                           |

| OUT   | ×    | P.      | Move data to<br>port                      | -  | _   | -   | 0        | -   | -   | 품            |                    |        | ᆸ         |                                |           |     | ۵   |   | (Port (Pn)) ← M                  | Moves the contents of memory location M to port Pn                                                                                                              |                           |

| 885   | Æ    | z       | Set port bits                             | -  | -   | _   | -        | 0   | 0   | 0            | -                  |        | م         | 1                              | <u> </u>  |     | z   |   | (Port (Pn)) N ← 1                | Sets the bits of port Pn, specified by N. to logic 1                                                                                                            |                           |

| RP8   | Æ    | z       | Reset port bits                           | -  | _   | -   | -        | 0   | -   | -            | -                  |        | Δ.        |                                |           |     | z   |   | (Port (Pn)) N ← 0                | Sets the bits of port Pn, specified by N, to logic 0                                                                                                            |                           |

| ТРТ   | ų    | æ       | Test bits of<br>port and skip if<br>frue  | +  | -   | -   | -        | _   | 0   | -            |                    |        | ۵         |                                |           |     | Z   |   | Skip if (port (Pn))<br>N = all 1 | Tests the bits of port Pn specified by N. Skips if all bits are logic 1                                                                                         | All bits<br>specified = 1 |

| TPF.  | Pn   | z       | Test bits of<br>port and skip if<br>false | -  | - ' | -   | -        | -   | -   | -            | -                  |        | ۵         |                                |           |     | *   |   | Skip if (port (Pn)<br>N = all 0  | Tests the bits of port Pn specified by N. Skips if all bits are logic 0                                                                                         | All bits<br>specified = 0 |

|       |      |         |                                           |    |     |     | ]        |     |     |              |                    | ş      | resal     | Universal counter instructions | nstruct   | , i |     |   |                                  |                                                                                                                                                                 |                           |

| SON   | _    |         | Set UCCW1                                 | 6  | 0   | 0   | 0        | 0   | 0   | 0            | -                  | 0      |           | 0                              |           |     | _   |   | UCCW1 ← 1                        | Sets the universal counter flag 1                                                                                                                               |                           |

| ဆဂ    | -    |         | Set LOCKY2                                | ۰  | 0   | 0   | 0        | 0   | 0   | -            | -                  | 0      | 0         | 0                              |           |     | -   |   | UCCW2 ← 1                        | Sets the universal counter flag 2                                                                                                                               |                           |

|       |      |         |                                           |    |     |     |          |     |     |              |                    | E      | liscellan | Miscellaneous instructions     | rtruction | 2   |     |   |                                  |                                                                                                                                                                 |                           |

| SĘ.   | Z    |         | Port F direction<br>control               | 0  | 0   | 0   | <b>,</b> | 0   | 0   | 0            |                    | •      |           |                                |           |     | z   |   | FPC latch $\leftarrow$ N         | Defines the direction of individual pins of port F. If a but in the port F direction register is set by FPC, the corresponding pin of port F becomes an output. |                           |

| CKSTP |      |         | Stop clock                                | 0  | 0   | 0   | -        | 0   | 0   | 0            | -                  | 0      | 0         | 0                              |           | 0   | 0 0 | 0 | Stop clock if HOLD = 0           | Stops the processor clock if $\overline{HOLD} = 0$                                                                                                              |                           |

| DAC   | _    |         | Move data to<br>DAC registers             | 0  | 0   | 0   | 0        | 0   | 0   | <del>-</del> | 0                  | 0      | 0         | 0                              | 0         |     | _   |   | DAC <sub>r</sub> ← I             | Loads the immediate data to the DAC registers                                                                                                                   |                           |

| NOP   |      |         | No operation                              | 0  | 0   | 0   | 0        | 0   | 0   | 0            | 0                  | 0      | 0         | 0                              | 0         |     |     |   |                                  | No operation                                                                                                                                                    | !                         |

# MASK OPTIONS

| . Parameter                                                  | Options                     |

|--------------------------------------------------------------|-----------------------------|

| Watchdog timer (WDT)                                         | Yes                         |

| **************************************                       | No                          |

| Pull-down resistors on port A (the keypad matrix input port) | Yes                         |

| Tull-down resistors on port A (the keypad matrix input port) | No                          |

|                                                              | 2.67 μs                     |

| Instruction cycle time                                       | 13.33 μs                    |

|                                                              | 40.00 μs                    |

| S1 to S23 configuration                                      | LCD driver output port      |

| S1 to S23 configuration                                      | General-purpose output port |

# **DEVELOPMENT SYSTEM**

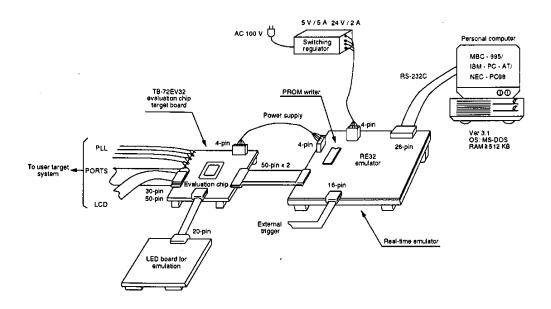

The LC7233 development environment is shown in figure 1. It uses an LC72EV32 evaluation chip mounted on a TB-72EV32 target board and a multifunctional emulator (RE32), which is controlled by a personal computer, to provide full debugging facilities.

Figure 1. Development system