## 1Kx4 Static RAM

#### **Features**

- · Memory reset function

- 1024 x 4 static RAM for control store in high-speed computers

- CMOS for optimum speed/power

- · High speed

- 10 ns (commercial)

- -12 ns (military)

- Low power

- -495 mW (commercial)

- -550 mW (military)

- · Separate inputs and outputs

- 5-volt power supply ±10% tolerance in both commercial and military

- Capable of withstanding greater than 2001V static discharge

- TTL-compatible inputs and outputs

#### **Functional Description**

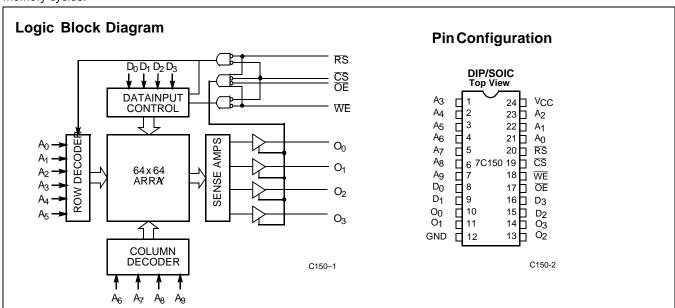

The CY7C150 is a high-performance CMOS static RAM designed for use in cache memory, high-speed graphics, and data-acquisition applications. The CY7C150 has a memory reset feature that allows the entire memory to be reset in two memory cycles.

Separate I/O paths eliminates the need to multiplex data in and data out, providing for simpler board layout and faster system performance. Outputs are three-stated during write, reset, deselect, or when output enable (OE) is held HIGH, allowing for easy memory expansion.

Reset is initiated by selecting the device ( $\overline{CS} = LOW$ ) and taking the reset (RS) input LOW. Within two memory cycles all bits are internally cleared to zero. Since chip select must be LOW for the device to be reset, a global reset signal can be employed, with only selected devices being cleared at any given time.

Writing to the device is accomplished when the chip select (CS) and write enable (WE) inputs are both LOW. Data on the four data inputs (D<sub>0</sub>-D<sub>3</sub>) is written into the memory location specified on the address pins ( $A_0$  through  $A_9$ ).

Reading the device is accomplished by taking chip select (CS) and output enable (OE) LOW while write enable (WE) remains HIGH. Under these conditions, the contents of the memory location specified on the address pins will appear on the four output pins ( $O_0$  through  $O_3$ ).

The output pins remain in high-impedance state when chip enable (CE) or output enable (OE) is HIGH, or write enable (WE) or reset (RS) is LOW.

A die coat is used to insure alpha immunity.

#### **Selection Guide**

|                                |            | 7C150-10 | 7C150-12 | 7C150-15 | 7C150-25 | 7C150-35 |

|--------------------------------|------------|----------|----------|----------|----------|----------|

| Maximum Access Time (ns)       | Commercial | 10       | 12       | 15       | 25       |          |

|                                | Military   |          | 12       | 15       | 25       | 35       |

| Maximum Operating Current (mA) | Commercial | 90       | 90       | 90       | 90       | 90       |

|                                | Military   |          | 100      | 100      | 100      | 100      |

Cypress Semiconductor Corporation • Document #: 38-05024 Rev. \*A

3901 North First Street

San Jose

CA 95134 • 408-943-2600

Revised January 18, 2003

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature ......-65°C to+150°C Ambient Temperature with Power Applied......-55°C to+125°C Supply Voltage to Ground Potential (Pin 24 to Pin 12).....-0.5V to+7.0V DC Voltage Applied to Outputs in High Z State ......-0.5V to+7.0V DC Input Voltage ......-3.0V to +7.0V

| Static Discharge Voltage       | . >2001V |

|--------------------------------|----------|

| (per MIL-STD-883, Method 3015) |          |

| Latch-Up Current               | >200 mA  |

### **Operating Range**

| Range                   | Ambient<br>Temperature | V <sub>CC</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ± 10%        |

| Military <sup>[1]</sup> | −55°C to +125°C        | 5V ± 10%        |

#### Note:

#### Electrical Characteristics Over the Operating Range<sup>[2]</sup>

Output Current into Outputs (LOW) ......20 mA

|                 |                                          |                                                   |                                           | 7C   | 150             |      |

|-----------------|------------------------------------------|---------------------------------------------------|-------------------------------------------|------|-----------------|------|

| Parameter       | Description                              | Test Con                                          | ditions                                   | Min. | Max.            | Unit |

| V <sub>OH</sub> | Output HIGH Voltage                      | $V_{CC} = Min., I_{OH} = -0.4$                    | $V_{CC} = Min., I_{OH} = -0.4 \text{ mA}$ |      |                 | V    |

| V <sub>OL</sub> | Output LOW Current                       | V <sub>CC</sub> = Min., I <sub>OL</sub> = 12 m    | A                                         |      | 0.4             | V    |

| V <sub>IH</sub> | Input HIGH Level                         |                                                   |                                           | 2.0  | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Input LOW Level                          |                                                   |                                           | -3.0 | 0.8             | V    |

| I <sub>IX</sub> | Input Load Current                       | $GND \le V_1 \le V_{CC}$                          |                                           | -10  | +10             | μΑ   |

| l <sub>OZ</sub> | Output Current (High Z)                  | $V_{OL} \le V_{OUT} \le V_{OH}$ , Output Disabled |                                           | -50  | +50             | μА   |

| I <sub>OS</sub> | Output Short Circuit Current[3]          | V <sub>CC</sub> = Max., V <sub>OUT</sub> = GND    |                                           |      | -300            | mA   |

| I <sub>CC</sub> | V <sub>CC</sub> Operating Supply Current | V <sub>CC</sub> = Max.,                           | Commercial                                |      | 90              | mA   |

|                 |                                          | I <sub>OUT</sub> = 0 mA                           | Military                                  |      | 100             | mA   |

#### Notes:

- See the last page of this specification for Group A subgroup testing information.

Not more than 1 output should be shorted at a time. Duration of the short circuit should not exceed 30 seconds.

#### Capacitance<sup>[4]</sup>

| Parameter        | Description        | tion Test Conditions                        |    | Unit |

|------------------|--------------------|---------------------------------------------|----|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C$ , $f = 1 \text{ MHz}$ , | 10 | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                             | 10 | pF   |

#### Note:

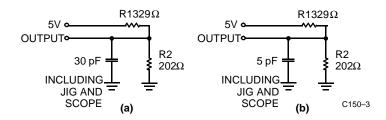

#### **AC Test Loads and Waveforms**

Equivalent to: THÉVENIN EQUIVALENT

> OUTPUT • 1.9V **م**ــ

<sup>1.</sup> TA is the "instant on" case temperature.

Tested initially and after any design or process changes that may affect these parameters.

### Switching Characteristics Over the Operating Range<sup>[2,5]</sup>

|                   |                                                | 7C15 | 50–10 | 7C15 | 50–12 | 7C150-15 |      | 7C150-25 |      | 7C150-35 |      |      |

|-------------------|------------------------------------------------|------|-------|------|-------|----------|------|----------|------|----------|------|------|

| Parameter         | r Description                                  |      | Max.  | Min. | Max.  | Min.     | Max. | Min.     | Max. | Min.     | Max. | Unit |

| READ CYC          | CLE                                            | 1    | ı     | ı    |       | ı        | ı    | 1        | 1    | 1        | ı    | 1    |

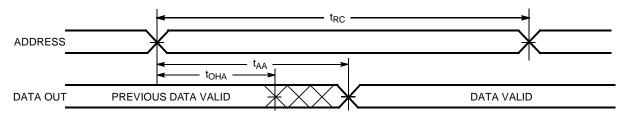

| t <sub>RC</sub>   | Read Cycle Time                                | 10   |       | 12   |       | 15       |      | 25       |      | 35       |      | ns   |

| t <sub>AA</sub>   | Address to Data Valid                          |      | 10    |      | 12    |          | 15   |          | 25   |          | 35   | ns   |

| t <sub>OHA</sub>  | Output Hold from Address<br>Change             | 2    |       | 2    |       | 2        |      | 2        |      | 2        |      | ns   |

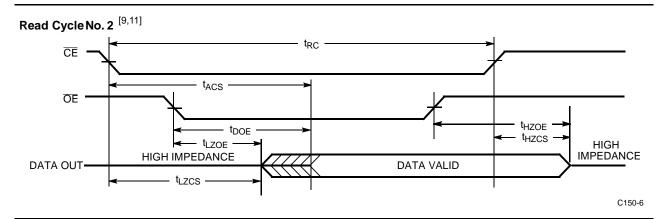

| t <sub>ACS</sub>  | CS LOW to Data Valid                           |      | 8     |      | 10    |          | 12   |          | 15   |          | 20   | ns   |

| t <sub>LZCS</sub> | CS LOW to Low Z <sup>[6]</sup>                 | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>HZCS</sub> | CS HIGH to High Z <sup>[6,7]</sup>             |      | 6     |      | 8     |          | 11   |          | 20   |          | 25   | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid                           |      | 6     |      | 8     |          | 10   |          | 15   |          | 20   | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z <sup>[6]</sup>                 | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>HZOE</sub> | OE HIGH to High Z <sup>[6,7]</sup>             |      | 6     |      | 8     |          | 9    |          | 20   |          | 25   | ns   |

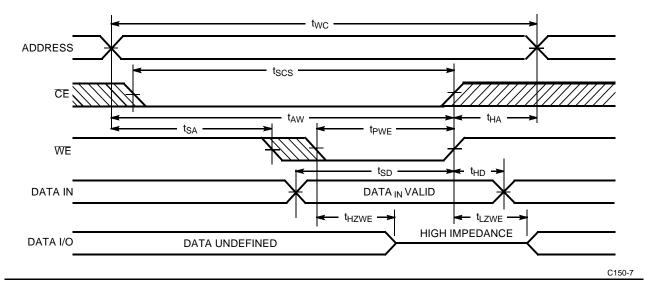

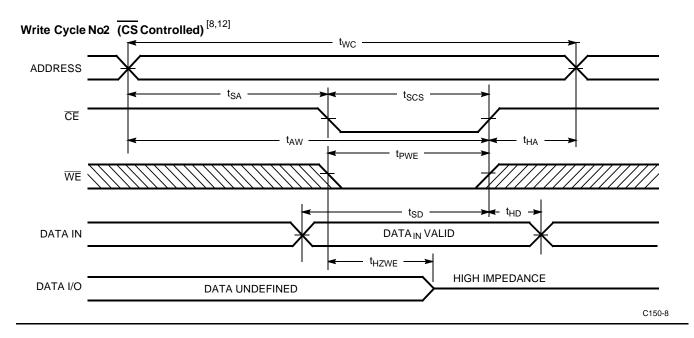

| WRITE CY          | CLE <sup>[8]</sup>                             | 1    |       | ı    |       | ı        |      |          | 1    | 1        |      | 1    |

| t <sub>WC</sub>   | Write Cycle Time                               | 10   |       | 12   |       | 15       |      | 25       |      | 35       |      | ns   |

| t <sub>SCS</sub>  | CS LOW to Write End                            | 6    |       | 8    |       | 11       |      | 15       |      | 20       |      | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End                    | 8    |       | 10   |       | 13       |      | 20       |      | 30       |      | ns   |

| t <sub>HA</sub>   | Address Hold from Write End                    | 2    |       | 2    |       | 2        |      | 5        |      | 5        |      | ns   |

| t <sub>SA</sub>   | Address Set-Up to Write Start                  | 2    |       | 2    |       | 2        |      | 5        |      | 5        |      | ns   |

| t <sub>PWE</sub>  | WE Pulse Width                                 | 6    |       | 8    |       | 11       |      | 15       |      | 20       |      | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End                       | 6    |       | 8    |       | 11       |      | 15       |      | 20       |      | ns   |

| t <sub>HD</sub>   | Data Hold from Write End                       | 2    |       | 2    |       | 2        |      | 5        |      | 5        |      | ns   |

| t <sub>LZWE</sub> | WE HIGH to Low Z <sup>[6]</sup>                | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[6,7]</sup>              |      | 6     |      | 8     |          | 12   |          | 20   |          | 25   | ns   |

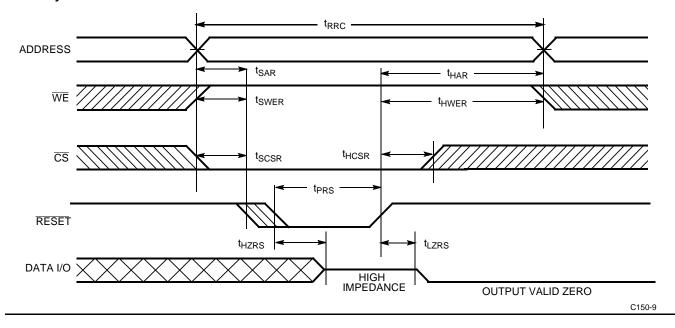

| RESET CY          | CLE                                            | 1    | 1     | ı    |       | ı        | 1    |          | 1    | 1        | 1    | 1    |

| t <sub>RRC</sub>  | Reset Cycle Time                               | 20   |       | 24   |       | 30       |      | 50       |      | 70       |      | ns   |

| t <sub>SAR</sub>  | Address Valid to Beginning of Reset            | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>SWER</sub> | Write Enable HIGH to Beginning of Reset        | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>SCSR</sub> | Chip Select LOW to Beginning of Reset          | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>PRS</sub>  | Reset Pulse Width                              | 10   |       | 12   |       | 15       |      | 20       |      | 30       |      | ns   |

| t <sub>HCSR</sub> | Chip Select Hold After End of Reset            | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>HWER</sub> | Write Enable Hold After End of Reset           | 8    |       | 12   |       | 15       |      | 30       |      | 40       |      | ns   |

| t <sub>HAR</sub>  | Address Hold After End of Reset                | 10   |       | 12   |       | 15       |      | 30       |      | 40       |      | ns   |

| t <sub>LZRS</sub> | Reset HIGH to Output in Low Z <sup>[6]</sup>   | 0    |       | 0    |       | 0        |      | 0        |      | 0        |      | ns   |

| t <sub>HZRS</sub> | Reset LOW to Output in High Z <sup>[6,7]</sup> |      | 6     |      | 8     |          | 12   |          | 20   |          | 25   | ns   |

#### Notes:

Document #: 38-05024 Rev. \*A

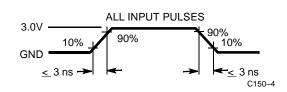

Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified  $l_{OL}/l_{OH}$  and 30-pF load capacitance.

At any given temperature and voltage condition,  $t_{HZ}$  is less than  $t_{LZ}$  for any given device.  $t_{HZCS}$ ,  $t_{HZOS}$ ,  $t_{HZOS}$ ,  $t_{HZDS}$ ,  $t_{HZDS}$ ,  $t_{HZDS}$ ,  $t_{HZOS}$ ,  $t_{H$

### **Switching Waveforms**

#### Read Cycle No.1 [9,10]

C150-5

# Write CycleNo.1 ( $\overline{\text{WE}}$ Controlled) [8]

#### Notes:

- WE is HIGH for read cycle.

Device is continuously selected, CS and OE = V<sub>IL</sub>.

Address prior to or coincident with CS transition LOW.

[+] Feedback

### Switching Waveforms (continued)

# Reset Cycle [13]

[+] Feedback

If CS goes HIGH with WE HIGH, the output <u>remains in a high-impedance state</u>.

Reset cycle is defined by the overlap of RS and CS for the minimum reset pulse width.

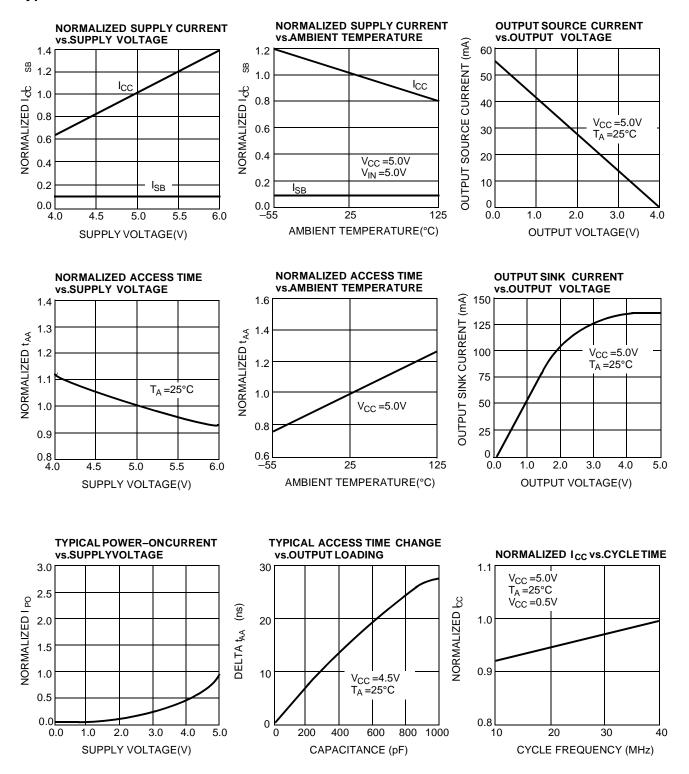

#### Typical DC and AC Characteristics

Document #: 38-05024 Rev. \*A Page 6 of 11

### **Truth Table**

| Inputs |    |    |    |                                |                |

|--------|----|----|----|--------------------------------|----------------|

| CS     | WE | OE | RS | Outputs                        | Mode           |

| Н      | Χ  | Χ  | Х  | High Z                         | Not Selected   |

| L      | Н  | Х  | L  | High Z                         | Reset          |

| L      | L  | Χ  | Н  | High Z                         | Write          |

| L      | Н  | L  | Н  | O <sub>0</sub> -O <sub>3</sub> | Read           |

| L      | Χ  | Н  | Н  | High Z                         | Output Disable |

### **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                 | Operating<br>Range |

|---------------|---------------|-----------------|------------------------------|--------------------|

| 10            | CY7C150-10PC  | P13A            | 24-Lead (300-Mil) Molded DIP | Commercial         |

|               | CY7C150-10SC  | S13             | 24-Lead Molded SOIC          |                    |

| 12            | CY7C150-12PC  | P13A            | 24-Lead (300-Mil) Molded DIP | Commercial         |

|               | CY7C150-12SC  | S13             | 24-Lead Molded SOIC          |                    |

|               | CY7C150-12DMB | D14             | 24-Lead (300-Mil) CerDIP     | Military           |

| 15            | CY7C150-15PC  | P13A            | 24-Lead (300-Mil) Molded DIP | Commercial         |

|               | CY7C150-15SC  | S13             | 24-Lead Molded SOIC          |                    |

|               | CY7C150-15DMB | D14             | 24-Lead (300-Mil) CerDIP     | Military           |

| 25            | CY7C150-25PC  | P13A            | 24-Lead (300-Mil) Molded DIP | Commercial         |

|               | CY7C150-25SC  | S13             | 24-Lead Molded SOIC          |                    |

|               | CY7C150-25DMB | D14             | 24-Lead (300-Mil) CerDIP     | Military           |

| 35            | CY7C150-35DMB | D14             | 24-Lead (300-Mil) CerDIP     | Military           |

Document #: 38-05024 Rev. \*A Page 7 of 11

### MILITARY SPECIFICATIONS Group A Subgroup Testing

### **DC Characteristics**

| Parameter            | Subgroups |

|----------------------|-----------|

| V <sub>OH</sub>      | 1, 2, 3   |

| V <sub>OL</sub>      | 1, 2, 3   |

| V <sub>IH</sub>      | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| I <sub>IX</sub>      | 1, 2, 3   |

| I <sub>OZ</sub>      | 1, 2, 3   |

| I <sub>CC</sub>      | 1, 2, 3   |

### **Switching Characteristics**

| Parameter         | Subgroups       |

|-------------------|-----------------|

| READ CYCLE        |                 |

| t <sub>RC</sub>   | 7, 8, 9, 10, 11 |

| t <sub>AA</sub>   | 7, 8, 9, 10, 11 |

| t <sub>OHA</sub>  | 7, 8, 9, 10, 11 |

| t <sub>ACS</sub>  | 7, 8, 9, 10, 11 |

| WRITE CYCLE       |                 |

| t <sub>WC</sub>   | 7, 8, 9, 10, 11 |

| t <sub>SCS</sub>  | 7, 8, 9, 10, 11 |

| t <sub>AW</sub>   | 7, 8, 9, 10, 11 |

| t <sub>HA</sub>   | 7, 8, 9, 10, 11 |

| t <sub>SA</sub>   | 7, 8, 9, 10, 11 |

| t <sub>PWE</sub>  | 7, 8, 9, 10, 11 |

| t <sub>SD</sub>   | 7, 8, 9, 10, 11 |

| t <sub>HD</sub>   | 7, 8, 9, 10, 11 |

| RESET CYCLE       |                 |

| t <sub>RRC</sub>  | 7, 8, 9, 10, 11 |

| t <sub>SAR</sub>  | 7, 8, 9, 10, 11 |

| t <sub>SWER</sub> | 7, 8, 9, 10, 11 |

| t <sub>SCSR</sub> | 7, 8, 9, 10, 11 |

| t <sub>PRS</sub>  | 7, 8, 9, 10, 11 |

| t <sub>HCSR</sub> | 7, 8, 9, 10, 11 |

| t <sub>HWER</sub> | 7, 8, 9, 10, 11 |

| t <sub>HAR</sub>  | 7, 8, 9, 10, 11 |

Document #: 38-05024 Rev. \*A

Page 8 of 11

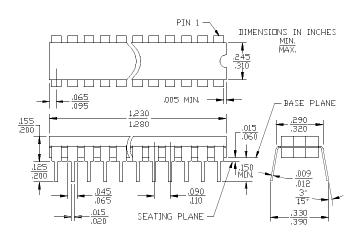

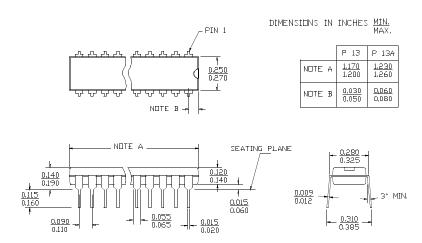

### **Package Diagrams**

# **24-Lead (300-Mil) CerDIP D14**MIL-STD-1835 D- 9Config.A

#### 24-Lead (300-Mil) Molded DIP P13/P13A

Document #: 38-05024 Rev. \*A

[+] Feedback

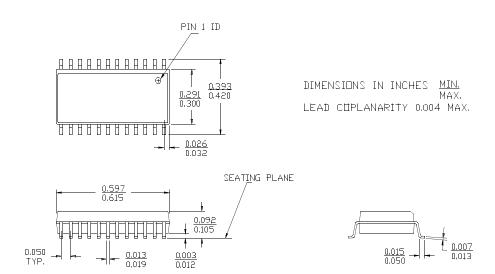

### Package Diagrams (continued)

#### 24-Lead Molded SOIC S13

| Document Title: Cy7C150 1K x4 Static RAM Document Number: 38-05024 |         |               |                 |                                                                                                                                                                                                           |  |  |

|--------------------------------------------------------------------|---------|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REV.                                                               | ECN NO. | Issue<br>Date | Orig. of Change | Description of Change                                                                                                                                                                                     |  |  |

| **                                                                 | 106810  | 09/10/01      | SZV             | Change from Spec number: 38-00028 to 38-05024                                                                                                                                                             |  |  |

| *A                                                                 | 122462  | 01/18/03      | RBI             | This ECN/Spec will serve as the master signature approval document for all ECN's referenced to it. ECN's to datasheets adding power up requirements are covered for signatures when referenced to 122462. |  |  |

Document #: 38-05024 Rev. \*A