# INTEGRATED CIRCUITS

Product specification Replaces data sheet PLC18V8Z35/PLC18V8ZI of Dec 19 1995, and data sheet PLC18V8Z25/PLC18V8ZI of Dec 19, 1995

# PLC18V8Z

#### DESCRIPTION

The PLC18V8Z is a universal PAL® device featuring high performance and virtually zero-standby power for power sensitive applications. They are reliable, user-configurable substitutes for discrete TTL/CMOS logic. While compatible with TTL and HCT logic, the PLC18V8Z can also replace HC logic over the V<sub>CC</sub> range of 4.5 to 5.5V.

The PLC18V8Z is a two-level logic element comprised of 10 inputs, 74 AND gates (product terms) and 8 output Macro cells.

Each output features an "Output Macro Cell" which can be individually configured as a dedicated input, a combinatorial output, or a registered output with internal feedback. As a result, the PLC18V8Z is capable of emulating all common 20-pin PAL devices to reduce documentation, inventory, and manufacturing costs.

A power-up reset function and a Register Preload function have been incorporated in the PLC18V8Z architecture to facilitate state machine design and testing.

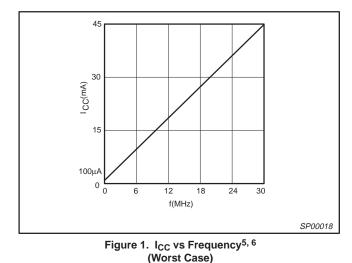

With a standby current of less than  $100\mu$ A and active power consumption of 1.5mA/MHz, the PLC18V8Z is ideally suited for power sensitive applications in battery operated/backed portable instruments and computers.

The PLC18V8Z is also processed to industrial requirements for operation over an extended temperature range of -40°C to +85°C and supply voltage of 4.5V to 5.5V.

Ordering information can be found on the following page.

#### FEATURES

- 20-pin Universal Programmable Array Logic

- Virtually Zero-Standby-power

- 20µA (typical)

- Available in DIP, PLCC, SOL (Small Outline), SSOP (Shrink Small Outline), and TSSOP (Thin Shrink Small Outline) packages

- Functional replacement for Series 20 PAL devices

- $I_{OL} = 24mA$

- Up to 18 inputs and 8 input/output macro cells

- Programmable output polarity

- Power-up reset on all registers

- Register Preload capability

- Synchronous Preset/Asynchronous Reset

- Security fuse to prevent duplication of proprietary designs

- Also available in 3V operation—the P3C18V8Z

#### APPLICATIONS

- Battery powered instruments

- Laptop and pocket computers

- Industrial control

- Medical Instruments

- Portable communications equipment

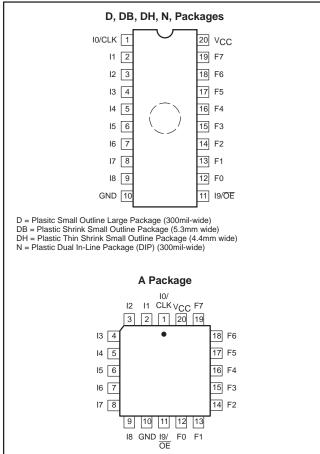

#### **PIN CONFIGURATIONS**

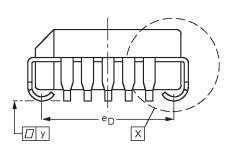

A = Plastic Leaded Chip Carrier

#### **PIN DESCRIPTIONS**

| I               | Dedicated Input                      |

|-----------------|--------------------------------------|

| В               | Bidirectional input/output           |

| 0               | Dedicated output                     |

| D               | Registered output (D-type flip-flop) |

| F               | Output/Input Macrocell               |

| CLK             | Clock Input                          |

| ŌE              | Output Enable                        |

| V <sub>CC</sub> | Supply Voltage                       |

| GND             | Ground                               |

SP00544

PAL is a registered trademark of Advanced Micro Devices, Inc.

PLC18V8Z

#### **ORDERING INFORMATION**

| DESCRIPTION                                                             | TEMPERATURE<br>RANGE                                           | ORDER CODE   | DRAWING<br>NUMBER |

|-------------------------------------------------------------------------|----------------------------------------------------------------|--------------|-------------------|

| 20-Pin (300mil-wide) Plastic Dual In-Line Package, 25ns t <sub>PD</sub> |                                                                | PLC18V8Z25N  | SOT146-1          |

| 20-Pin (350mil square) Plastic Leaded Chip Carrier Package              | ]                                                              | PLC18V8Z25A  | SOT380-1          |

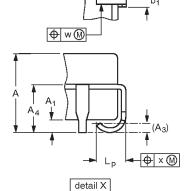

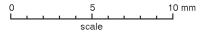

| 20-Pin (300mil-wide) Plastic Small Outline Large Package                | ]                                                              | PLC18V8Z25D  | SOT163-1          |

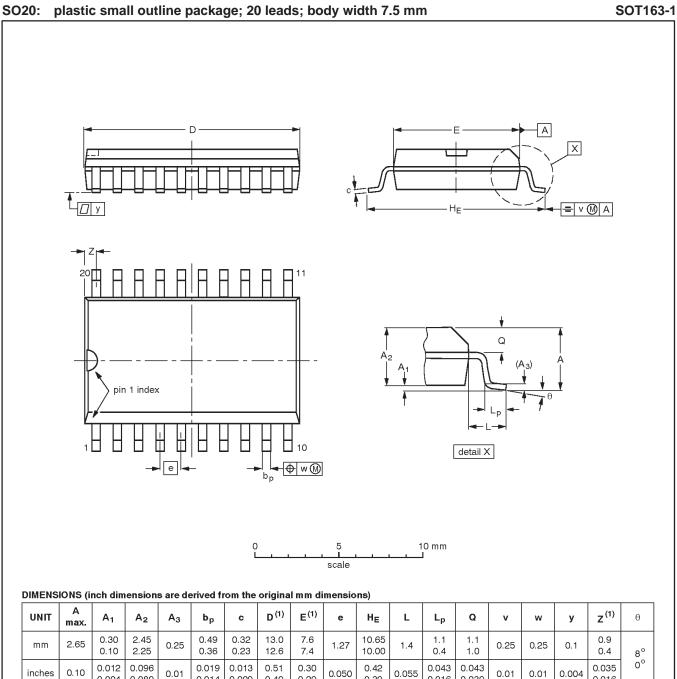

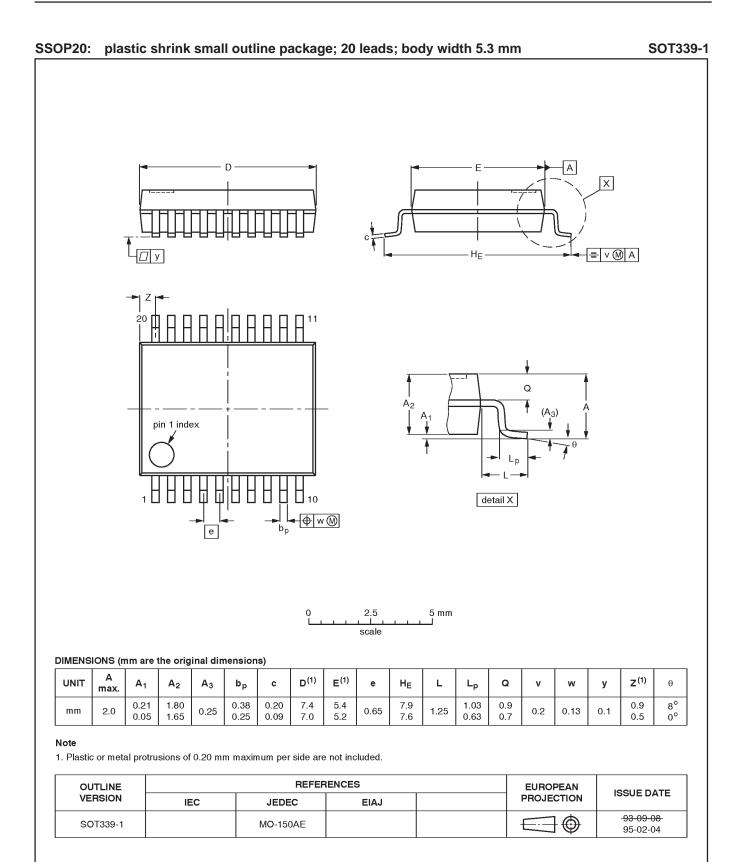

| 20-Pin (5.3mm-wide) Plastic Shrink Small Outline Package                | ]                                                              | PLC18V8Z25DB | SOT339-1          |

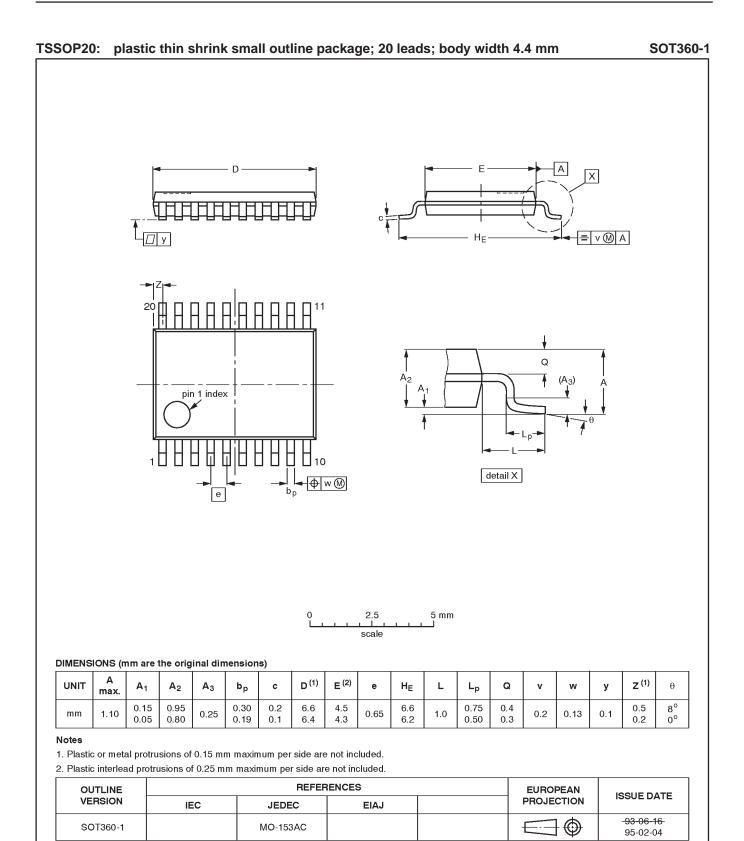

| 20-Pin (4.4mm-wide) Plastic Thin Shrink Small Outline Package           | Commercial                                                     | PLC18V8Z25DH | SOT360-1          |

| 20–Pin (300mil–wide) Plastic Dual In–Line Package. 35ns t <sub>PD</sub> | <ul> <li>Temperature Range<br/>± 5% Power Supplies</li> </ul>  | PLC18V8Z35N  | SOT146-1          |

| 20–Pin (350mil square) Plastic Leaded Chip Carrier Package              | ]                                                              | PLC18V8Z35A  | SOT380-1          |

| 20–Pin (300mil square) Plastic Small Outline Large Package Package      | 1                                                              | PLC18V8Z35D  | SOT163-1          |

| 20–Pin (5.3mm–wide) Plastic Shrink Small Outline Package                | ]                                                              | PLC18V8Z35DB | SOT339-1          |

| 20–Pin (4.4mm–wide) Plastic Thin shrink Small Outline Package           | 1                                                              | PLC18V8Z35DH | SOT260-1          |

| 20-Pin (300mil-wide) Plastic Dual In-Line Package 25ns t <sub>PD</sub>  |                                                                | PLC18V8ZIAN  | SOT146-1          |

| 20-Pin (350mil square) Plastic Leaded Chip Carrier Package              | ]                                                              | PLC18V8ZIAA  | SOT380-1          |

| 20-Pin (300mil-wide) Plastic Small Outline Large Package                | ]                                                              | PLC18V8ZIAD  | SOT163-1          |

| 20-Pin (5.3mm-wide) Plastic Shrink Small Outline Package                |                                                                | PLC18V8ZIADB | SOT339-1          |

| 20-Pin (4.4mm-wide) Plastic Thin Shrink Small Outline Package           | Industrial                                                     | PLC18V8ZIADH | SOT360-1          |

| 20–Pin (300mil–wide) Plastic Dual In–Line Package, 40ns t <sub>PD</sub> | <ul> <li>Temperature Range<br/>± 10% Power Supplies</li> </ul> | PLC18V8ZIN   | SOT146-1          |

| 20–Pin (350mil square) Plastic Leaded chip Carrier Package              | ]                                                              | PLC18V8ZIA   | SOT380-1          |

| 20–Pin (300mil square) Plastic Small Outline Large Package              | ]                                                              | PLC18V8ZZID  | SOT163-1          |

| 20–Pin (5.3mm–wide) Plastic Shrink Small Outline Package                | ]                                                              | PLC18V8ZIDB  | SOT339-1          |

| 20-Pin (4.4mm-wide) Plastic Thin Shrink Small Outline Package           |                                                                | PLC18V8ZIDH  | SOT360-1          |

# PLC18V8Z

| PIN<br>NO. | PLC<br>18V8Z        | 16L8<br>16H8<br>16P8<br>16P8 | 16R4<br>16RP4 | 16R6<br>16RP6 | 16R8<br>16RP8 | 16L2<br>16H2<br>16P2 | 14L4<br>14H4<br>14P4 | 12L6<br>12H6<br>12P6 | 10L8<br>10H8<br>10P8 |

|------------|---------------------|------------------------------|---------------|---------------|---------------|----------------------|----------------------|----------------------|----------------------|

| 1          | I <sub>0</sub> /CLK | I                            | CLK           | CLK           | CLK           | I                    | I                    | I                    | I                    |

| 19         | F7                  | В                            | В             | В             | D             | I                    | I                    | I                    | 0                    |

| 18         | F6                  | В                            | В             | D             | D             | I                    | I                    | 0                    | 0                    |

| 17         | F5                  | В                            | D             | D             | D             | I                    | 0                    | 0                    | 0                    |

| 16         | F4                  | В                            | D             | D             | D             | 0                    | 0                    | 0                    | 0                    |

| 15         | F3                  | В                            | D             | D             | D             | 0                    | 0                    | 0                    | 0                    |

| 14         | F2                  | В                            | D             | D             | D             | I                    | 0                    | 0                    | 0                    |

| 13         | F1                  | В                            | В             | D             | D             | I                    | I                    | 0                    | 0                    |

| 12         | F0                  | В                            | В             | В             | D             | I                    | I                    | I                    | 0                    |

| 11         | I <sub>9</sub> /OE  |                              | ŌĒ            | ŌĒ            | ŌĒ            |                      | I                    | I                    | I                    |

#### PAL DEVICE TO PLC18V8Z OUTPUT PIN CONFIGURATION CROSS REFERENCE

The Philips Semiconductors' state-of-the-art Floating-Gate CMOS EPROM process yields bipolar equivalent performance at less than one-quarter the power consumption. The erasable nature of the EPROM process enables Philips Semiconductors to functionally test the devices prior to shipment to the customer. Additionally, this allows Philips Semiconductors to extensively stress test, as well as ensure the threshold voltage of each individual EPROM cell. 100% programming yield is subsequently guaranteed.

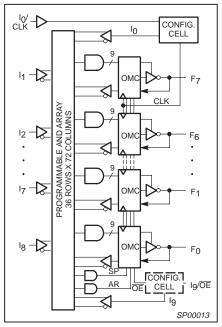

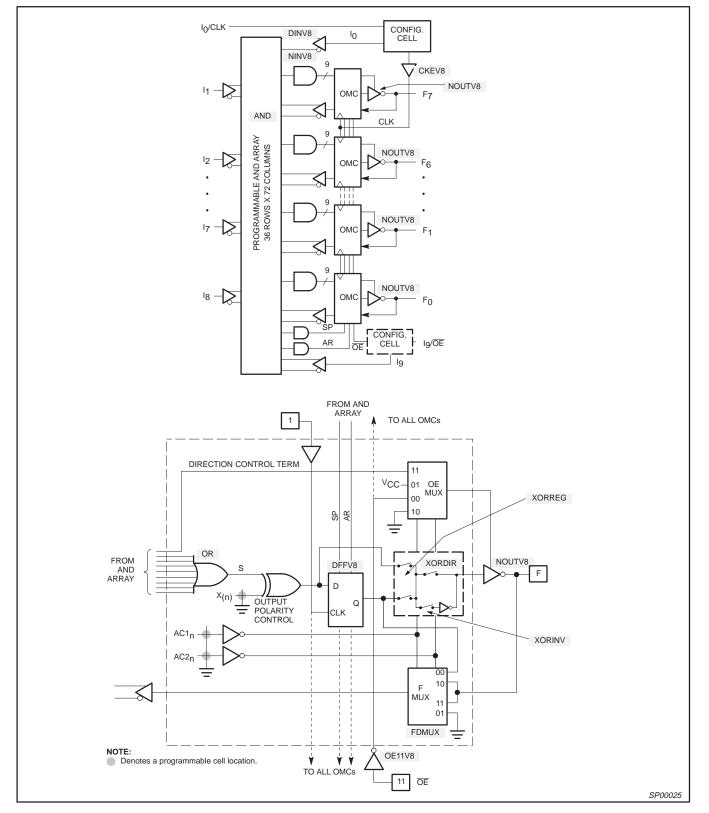

#### **FUNCTIONAL DIAGRAM**

# PLC18V8Z

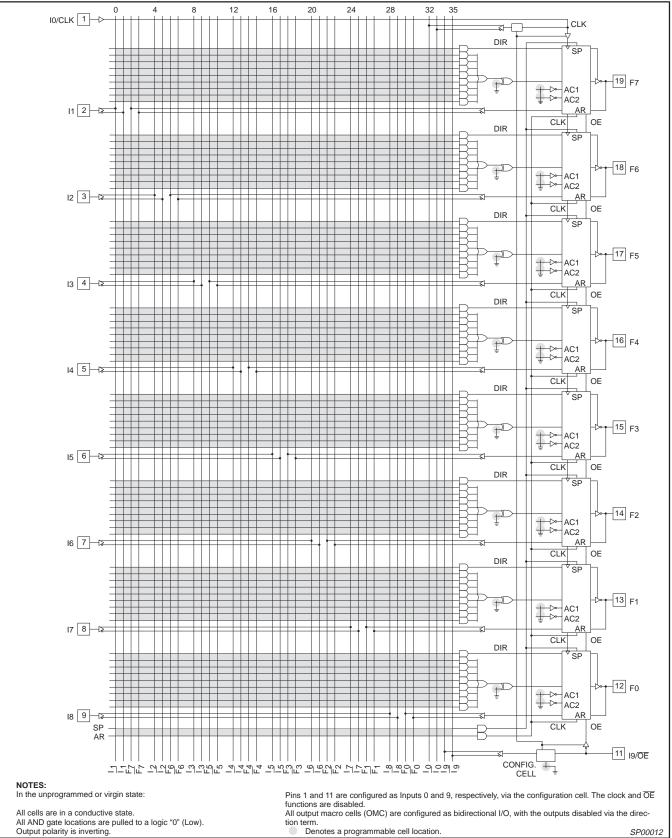

#### LOGIC DIAGRAM

# PLC18V8Z

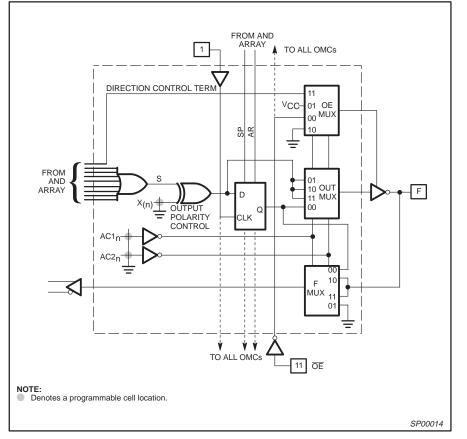

#### **OUTPUT MACRO CELL (OMC)**

#### THE OUTPUT MACRO CELL (OMC)

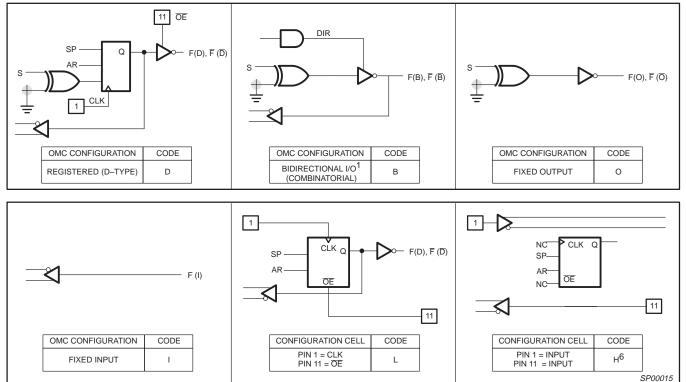

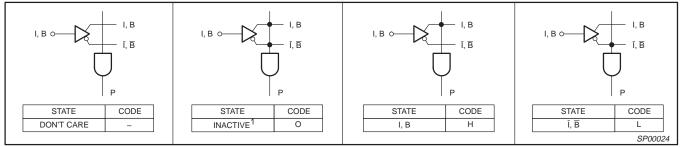

The PLC18V8Z series devices have 8 individually programmable Output Macro Cells. The 72 AND inputs (or product terms) from the programmable AND array are connected to the 8 OMCs in groups of 9. Eight of the AND terms are dedicated to logic functions; the ninth is for asynchronous direction control, which enables/disables the respective bidirectional I/O pin. Two product terms are dedicated for the Synchronous Preset and Asynchronous Reset functions.

Each OMC can be independently programmed via 16 architecture control bits,  $AC1_n$  and  $AC2_n$  (one pair per macro cell). Similarly, each OMC has a programmable output polarity control bit (Xn). By configuring the pair of architecture control bits according to the configuration cell table, 4 different configurations may be implemented. Note that the configuration cell is automatically programmed based on the OMC configuration.

#### **DESIGN SECURITY**

The PLC18V8Z series devices have a programmable security fuse that controls the access to the data programmed in the device. By using this programmable feature, proprietary designs implemented in the device cannot be copied or retrieved.

# PLC18V8Z

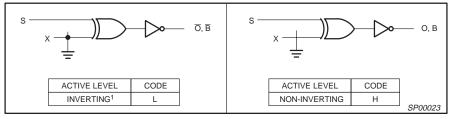

#### **CONFIGURATION CELL**

A single configuration cell controls the functions of Pins 1 and 11. Refer to Functional Diagram. When the configuration cell is programmed, Pin 1 is a dedicated clock and Pin 11 is dedicated for output enable. When the configuration cell is unprogrammed, Pins 1 and 11 are both dedicated inputs. Note that the output enable for all registered OMCs is common—from Pin 11 only. Output enable control of the bidirectional I/O OMCs is provided from the AND array via the direction product term. If any one OMC is configured as registered, the configuration cell will be automatically configured (via the design software) to ensure that the clock and output enable functions are enabled on Pins 1 and 11, respectively. If none of the OMCs are registered, the configuration cell will be programmed such that Pins 1 and 11 are dedicated inputs. The programming codes are as follows:

| Pin 1 = CLK, Pin 11 = $\overline{OE}$ | L |

|---------------------------------------|---|

| Pin 1 and Pin 11 = Input              | Н |

|                                                  | CONTR            | OL CELL CONFIGUR | TIONS        |                                                                                            |

|--------------------------------------------------|------------------|------------------|--------------|--------------------------------------------------------------------------------------------|

| FUNCTION                                         | AC1 <sub>1</sub> | AC2 <sub>N</sub> | CONFIG. CELL | COMMENTS                                                                                   |

| Registered mode                                  | Programmed       | Programmed       | Programmed   | Dedicated clock from Pin 1. OE Control for all registerd OMCs from Pin 11 only.            |

| Bidirectional I/O mode <sup>1</sup> Unprogrammed |                  | Unprogrammed     | Unprogrammed | Pins 1 and 11 are dedicated inputs.<br>3-State control from AND array only.                |

| Fixed input mode                                 | Unprogrammed     | Programmed       | Unprogrammed | Pins 1 and 11 are dedicated inputs.                                                        |

| Fixed output mode                                | Programmed       | Unprogrammed     | Unprogrammed | Pins 1 and 11 are dedicated inputs. The feedback path (via F <sub>MUX</sub> ) is disabled. |

NOTE:

1. This is the virgin state as shipped from the factory.

#### **ARCHITECTURE CONTROL**—AC1 and AC2

#### NOTES:

A factory shipped unprogrammed device is configured such that:

- 1. This is the initial unprogrammed state. All cells are in a conductive state.

- 2. All AND gates are pulled to a logic "0" (Low).

- 3. Output polarity is inverting.

- 4. Pins 1 and 11 are configured as inputs 0 and 9. The clock and OE functions are disabled.

- 5. All Output Macro Cells (OMCs) are configured as bidirectional I/O, with the outputs disabled via the direction term.

- 6. This configuration cannot be used if any OMCs are configured as registered (Code = D).

PLC18V8Z

Product specification

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL              | PARAMETER                                        | RATINGS                                              | UNIT            |

|---------------------|--------------------------------------------------|------------------------------------------------------|-----------------|

| V <sub>CC</sub>     | Supply voltage                                   | -0.5 to +7                                           | V <sub>DC</sub> |

| V <sub>CC</sub>     | Operating supply voltage                         | 4.5 to 5.5 (Industrial)<br>4.75 to 5.25 (Commercial) | V <sub>DC</sub> |

| V <sub>IN</sub>     | Input voltage                                    | –0.5 to V <sub>CC</sub> + 0.5                        | V <sub>DC</sub> |

| V <sub>OUT</sub>    | Output voltage                                   | –0.5 to V <sub>CC</sub> + 0.5                        | V <sub>DC</sub> |

| $\Delta t/\Delta V$ | Input/clock transition rise or fall <sup>2</sup> | 250                                                  | ns/V maximum    |

| I <sub>IN</sub>     | Input currents                                   | -10 to +10                                           | mA              |

| I <sub>OUT</sub>    | Output currents                                  | +24                                                  | mA              |

| T <sub>amb</sub>    | Operating temperature range                      | –40 to +85 (Industrial)<br>0 to +75 (Commercial)     | °C              |

| T <sub>stg</sub>    | Storage temperature range                        | -65 to +150                                          | °C              |

NOTE:

1. Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification of the device is not implied.

All digital circuits can oscillate or trigger prematurely when input rise and fall times are very long. When the input signal to a device is at or near the switching threshold, noise on the line will be amplified and can cause oscillation which, if the frequency is low enough, can cause subsequent stages to switch and give erroneous results. For this reason, Schmitt-triggers are recommended if rise/fall times are likely to exceed 250ns at V<sub>CC</sub> = 4.5V.

#### THERMAL RATINGS

| TEMPERATURE                                |       |  |  |  |  |  |  |  |  |

|--------------------------------------------|-------|--|--|--|--|--|--|--|--|

| Maximum junction                           | 150°C |  |  |  |  |  |  |  |  |

| Maximum ambient                            | 75°C  |  |  |  |  |  |  |  |  |

| Allowable thermal rise ambient to junction | 75°C  |  |  |  |  |  |  |  |  |

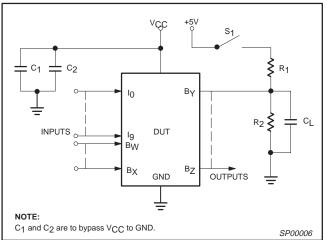

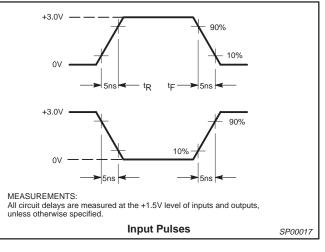

#### **AC TEST CONDITIONS**

#### **VOLTAGE WAVEFORMS**

Product specification

# PLC18V8Z

#### **DC ELECTRICAL CHARACTERISTICS**

| Industrial = $-40^{\circ}C \le T_a$ | mb ≤ +85°C, 4.5V ≤ \ | / <sub>CC</sub> ≤ 5.5V |

|-------------------------------------|----------------------|------------------------|

| SYMBOL              | PARAMETER                                            | TEST CONDITION                                                       | MIN                           | TYP <sup>1</sup> | MAX                   | UNIT     |

|---------------------|------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|------------------|-----------------------|----------|

| Input volt          | age                                                  |                                                                      |                               |                  |                       |          |

| V <sub>IL</sub>     | Low                                                  | $V_{CC} = MIN$                                                       | -0.3                          |                  | 0.8                   | V        |

| V <sub>IH</sub>     | High                                                 | $V_{CC} = MAX$                                                       | 2.0                           |                  | V <sub>CC</sub> + 0.3 | V        |

| Output vo           | oltage <sup>2</sup>                                  |                                                                      |                               |                  |                       |          |

| V <sub>OL</sub>     | Low                                                  | $V_{CC} = MIN, I_{OL} = 20\mu A$<br>$V_{CC} = MIN, I_{OL} = 24mA$    |                               |                  | 0.100<br>0.500        | V<br>V   |

| V <sub>OH</sub>     | High                                                 | $V_{CC} = MIN, I_{OH} = -3.2mA$<br>$V_{CC} = MIN, I_{OH} = -20\mu A$ | 2.4<br>V <sub>CC</sub> – 0.1V |                  |                       | V<br>V   |

| Input cur           | rent                                                 |                                                                      |                               |                  |                       | -        |

| IIL                 | Low <sup>7</sup>                                     | V <sub>IN</sub> = GND                                                |                               |                  | -10                   | μA       |

| I <sub>IH</sub>     | High                                                 | $V_{IN} = V_{CC}$                                                    |                               |                  | 10                    | μA       |

| Output cu           | urrent                                               |                                                                      |                               |                  |                       |          |

| I <sub>O(OFF)</sub> | Hi-Z state                                           | V <sub>OUT</sub> = V <sub>CC</sub><br>V <sub>OUT</sub> = GND         |                               |                  | 10<br>-10             | μΑ<br>μΑ |

| I <sub>OS</sub>     | Short-circuit <sup>3</sup>                           | V <sub>OUT</sub> = GND                                               |                               |                  | -130                  | mA       |

| I <sub>CC</sub>     | V <sub>CC</sub> supply current (Standby)             | $V_{CC} = MAX, V_{IN} = 0 \text{ or } V_{CC}^8$                      |                               | 20               | 100                   | μΑ       |

| I <sub>CC</sub> /f  | V <sub>CC</sub> supply current (Active) <sup>4</sup> | V <sub>CC</sub> = MAX (CMOS inputs) <sup>5, 6</sup>                  |                               |                  | 1.5                   | mA/MHz   |

| Capacitar           | nce                                                  |                                                                      |                               |                  |                       |          |

| Cl                  | Input                                                | $V_{CC} = 5V, V_{IN} = 2.0V$                                         |                               | 12               |                       | pF       |

| CB                  | I/O                                                  | $V_{B} = 2.0V$                                                       |                               | 15               |                       | pF       |

#### NOTES:

- 1. All typical values are at  $V_{CC} = 5V$ ,  $T_{amb} = +25^{\circ}C$ . 2. All voltage values are with respect to network ground terminal.

- 3. Duration of short-circuit should not exceed one second. Test one at a time.

- 4. Tested with TTL input levels:  $V_{IL} = 0.45V$ ,  $V_{IH} = 2.4V$ . Measured with all outputs switching.

- 5.  $\Delta I_{CC}/TTL$  input = 2mA.

- 6.  $\Delta I_{CC}$  vs frequency (registered configuration) = 2mA/MHz. 7.  $I_{IL}$  for Pin 1 ( $I_0$ /CLK) is ± 10µA with V<sub>IN</sub> = 0.4V. 8. V<sub>IN</sub> includes CLK and  $\overline{OE}$  if applicable.

# $\begin{array}{l} \textbf{AC ELECTRICAL CHARACTERISTICS^4} \\ \textbf{Commercial} = \ 0^\circ \textbf{C} \leq \textbf{T}_{amb} \leq +75^\circ \textbf{C}, \ 4.75 \textbf{V} \leq \textbf{V}_{CC} \leq 5.25 \textbf{V}; \\ \textbf{Industrial} = -40^\circ \textbf{C} \leq \textbf{T}_{amb} \leq +85^\circ \textbf{C}, \ 4.5 \textbf{V} \leq \textbf{V}_{CC} \leq 5.5 \textbf{V}; \ \textbf{R}_2 = 390 \Omega \end{array}$

|                               |                                                               |                      |                                 | TEST CONDITIO                                     | N <sup>1</sup>         |     | 8V8Z25<br>nercial) | PLC18V8ZIA<br>(Industrial) |     |      |

|-------------------------------|---------------------------------------------------------------|----------------------|---------------------------------|---------------------------------------------------|------------------------|-----|--------------------|----------------------------|-----|------|

| SYMBOL                        | PARAMETER                                                     | FROM                 | то                              | R <sub>1</sub> (Ω)                                | C <sub>L</sub><br>(pF) | MIN | МАХ                | MIN                        | MAX | דואט |

| Pulse wi                      | dth                                                           |                      |                                 |                                                   |                        |     |                    |                            |     |      |

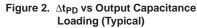

| t <sub>CKP</sub>              | Clock period<br>(Minimum t <sub>IS</sub> + t <sub>CKO</sub> ) | CLK +                | CLK +                           | 200                                               | 50                     | 33  |                    | 33                         |     | ns   |

| t <sub>CKH</sub>              | Clock width High                                              | CLK +                | CLK –                           | 200                                               | 50                     | 15  |                    | 15                         |     | ns   |

| t <sub>CKL</sub>              | Clock width Low                                               | CLK –                | CLK +                           | 200                                               | 50                     | 15  |                    | 15                         |     | ns   |

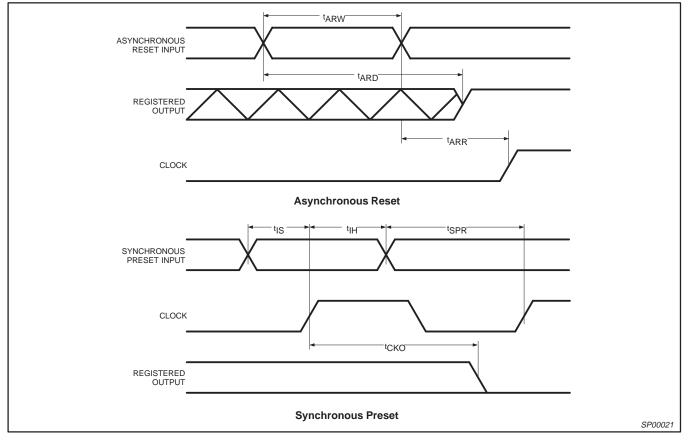

| t <sub>ARW</sub>              | Async reset pulse width                                       | I±, F±               | I <del>∓</del> , F <del>∓</del> |                                                   |                        | 25  |                    | 25                         |     | ns   |

| Hold time                     | e                                                             |                      |                                 |                                                   |                        |     |                    |                            |     |      |

| t <sub>IH</sub>               | Input or feedback<br>data hold time                           | CLK +                | Input ±                         | 200                                               | 50                     | 0   |                    | 0                          |     | ns   |

| Setup tin                     | ne                                                            |                      |                                 |                                                   |                        |     |                    |                            |     |      |

| t <sub>IS</sub>               | Input or feedback<br>data setup time                          | I±, F±               | CLK +                           | 200                                               | 50                     | 18  |                    | 18                         |     | ns   |

| Propaga                       | tion delay                                                    |                      |                                 | •                                                 |                        |     |                    |                            |     |      |

| t <sub>PD</sub>               | Delay from input<br>to active output                          | I ±, F±              | F±                              | 200                                               | 50                     |     | 25                 |                            | 25  | ns   |

| t <sub>СКО</sub>              | Clock High to output valid access Time                        | CLK +                | F±                              | 200                                               | 50                     |     | 15                 |                            | 15  | ns   |

| t <sub>OE1</sub> <sup>3</sup> | Product term enable to<br>outputs off                         | I ±, F±              | F±                              | Active-High R = 1.5k<br>Active-Low R = 550        | 50                     |     | 25                 |                            | 25  | ns   |

| t <sub>OD1</sub> <sup>2</sup> | Product term disable to<br>outputs off                        | I ±, F±              | F±                              | From $V_{OH} R = \infty$<br>From $V_{OL} R = 200$ | 5                      |     | 25                 |                            | 25  | ns   |

| t <sub>OD2</sub> <sup>2</sup> | Pin 11 output disable High to outputs off                     | OE –                 | F±                              | From $V_{OH} R = \infty$<br>From $V_{OL} R = 200$ | 5                      |     | 20                 |                            | 20  | ns   |

| $t_{OE2}^3$                   | Pin 11 output enable to active output                         | OE +                 | F±                              | Active-High R = 1.5k<br>Active-Low R = 550        | 50                     |     | 20                 |                            | 20  | ns   |

| t <sub>ARD</sub>              | Async reset delay                                             | I±, F±               | F+                              |                                                   |                        |     | 30                 |                            | 30  | ns   |

| t <sub>ARR</sub>              | Async reset recovery time                                     | I±, F±               | CLK +                           |                                                   |                        | 20  |                    | 20                         |     | ns   |

| t <sub>SPR</sub>              | Sync preset recovery time                                     | I±, F±               | CLK +                           |                                                   |                        | 20  |                    | 20                         |     | ns   |

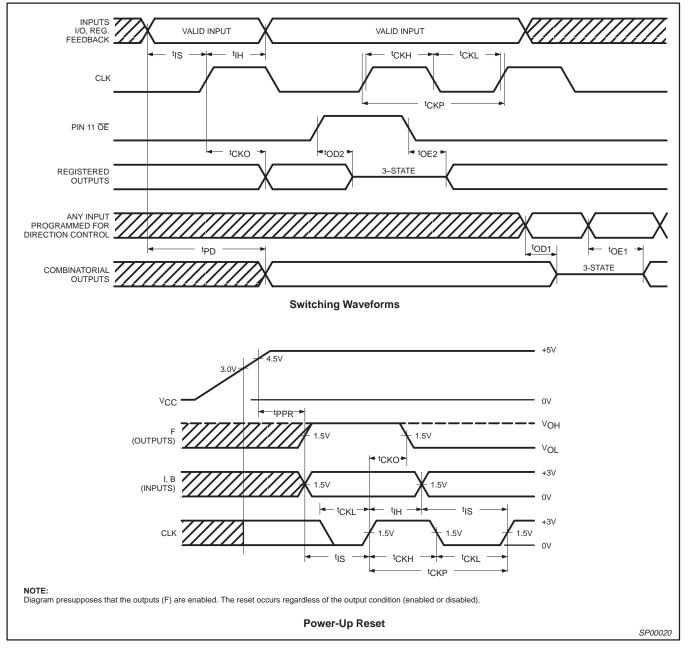

| t <sub>PPR</sub>              | Power-up reset                                                | V <sub>CC</sub> +    | F+                              |                                                   |                        |     | 25                 |                            | 25  | ns   |

| Frequen                       | cy of operation                                               |                      | -                               |                                                   | -                      | -   | -                  | -                          | -   | -    |

| MAX                           | Maximum frequency                                             | l/(t <sub>IS</sub> + | t <sub>CKO</sub> )              | 200                                               | 50                     |     | 30                 |                            | 30  | MHz  |

NOTES:

1. Refer also to AC Test Conditions. (Test Load Circuit)

2. For 3-State output; output enable times are tested with  $C_L = 50$ pF to the 1.5V level, and  $S_1$  is open for high-impedance to High tests and closed for high-impedance to Low tests. Output disable times are tested with  $C_L = 5$ pF. High-to-High impedance tests are made to an output voltage of  $V_T = (V_{OH} - 0.5V)$  with S<sub>1</sub> open, and Low-to-High impedance tests are made to the  $V_T = (V_{OL} + 0.5V)$  level with S<sub>1</sub> closed. 3. Resistor values of 1.5k and 550 $\Omega$  provide 3-State levels of 1.0V and 2.0V, respectively. Output timing measurements are to 1.5V level. 4. Leave all the cells on unused product terms intact (unprogrammed) for all patterns.

# $\begin{array}{l} \textbf{AC ELECTRICAL CHARACTERISTICS^4} \\ \textbf{Commercial} = ~~0^\circ\text{C} \leq \textbf{T}_{amb} \leq +75^\circ\text{C},~4.75\text{V} \leq \textbf{V}_{CC} \leq 5.25\text{V}; \\ \textbf{Industrial} = -40^\circ\text{C} \leq \textbf{T}_{amb} \leq +85^\circ\text{C},~4.5\text{V} \leq \textbf{V}_{CC} \leq 5.5\text{V};~\textbf{R}_2 = 390\Omega \end{array}$

|                               |                                                               |                      |                                 | TEST CONDITIO                                     | N <sup>1</sup>         |     | 8V8Z35<br>nercial) | PLC18V8ZI<br>(Industrial) |     |      |

|-------------------------------|---------------------------------------------------------------|----------------------|---------------------------------|---------------------------------------------------|------------------------|-----|--------------------|---------------------------|-----|------|

| SYMBOL                        | PARAMETER                                                     | FROM                 | то                              | R <sub>1</sub> (Ω)                                | C <sub>L</sub><br>(pF) | MIN | МАХ                | MIN                       | MAX | דואט |

| Pulse wi                      | dth                                                           |                      |                                 |                                                   |                        |     |                    |                           |     |      |

| t <sub>CKP</sub>              | Clock period<br>(Minimum t <sub>IS</sub> + t <sub>CKO</sub> ) | CLK +                | CLK +                           | 200                                               | 50                     | 47  |                    | 57                        |     | ns   |

| t <sub>CKH</sub>              | Clock width High                                              | CLK +                | CLK –                           | 200                                               | 50                     | 20  |                    | 25                        |     | ns   |

| t <sub>CKL</sub>              | Clock width Low                                               | CLK –                | CLK +                           | 200                                               | 50                     | 20  |                    | 25                        |     | ns   |

| t <sub>ARW</sub>              | Async reset pulse width                                       | Ι±, F±               | l <del>-</del> , F <del>-</del> |                                                   |                        | 35  |                    | 40                        |     | ns   |

| Hold time                     | e                                                             |                      |                                 | -                                                 |                        |     |                    |                           |     |      |

| t <sub>IH</sub>               | Input or feedback data hold time                              | CLK +                | Input ±                         | 200                                               | 50                     | 0   |                    | 0                         |     | ns   |

| Setup tin                     | ne                                                            |                      |                                 |                                                   |                        |     |                    |                           |     |      |

| t <sub>IS</sub>               | Input or feedback data setup time                             | I ±, F±              | CLK +                           | 200                                               | 50                     | 25  |                    | 30                        |     | ns   |

| Propaga                       | tion delay                                                    |                      |                                 | •                                                 |                        |     |                    |                           |     |      |

| t <sub>PD</sub>               | Delay from input<br>to active output                          | I ±, F±              | F±                              | 200                                               | 50                     |     | 35                 |                           | 40  | ns   |

| t <sub>СКО</sub>              | Clock High to output valid access Time                        | CLK +                | F±                              | 200                                               | 50                     |     | 22                 |                           | 27  | ns   |

| t <sub>OE1</sub> <sup>3</sup> | Product term enable to<br>outputs off                         | I ±, F±              | F±                              | Active-High R = 1.5k<br>Active-Low R = 550        | 50                     |     | 35                 |                           | 40  | ns   |

| t <sub>OD1</sub> <sup>2</sup> | Product term disable to outputs off                           | I ±, F±              | F±                              | From $V_{OH} R = \infty$<br>From $V_{OL} R = 200$ | 5                      |     | 35                 |                           | 40  | ns   |

| t <sub>OD2</sub> <sup>2</sup> | Pin 11 output disable High to outputs off                     | OE –                 | F±                              | From $V_{OH} R = \infty$<br>From $V_{OL} R = 200$ | 5                      |     | 25                 |                           | 40  | ns   |

| $t_{OE2}^{3}$                 | Pin 11 output enable to active output                         | OE +                 | F±                              | Active-High R = 1.5k<br>Active-Low R = 550        | 50                     |     | 25                 |                           | 30  | ns   |

| t <sub>ARD</sub>              | Async reset delay                                             | Ι±, F±               | F+                              |                                                   |                        |     | 35                 |                           | 40  | ns   |

| t <sub>ARR</sub>              | Async reset recovery time                                     | I±, F±               | CLK +                           |                                                   |                        | 25  |                    | 30                        |     | ns   |

| t <sub>SPR</sub>              | Sync preset recovery time                                     | I±, F±               | CLK +                           |                                                   |                        | 25  |                    | 30                        |     | ns   |

| t <sub>PPR</sub>              | Power-up reset                                                | V <sub>CC</sub> +    | F+                              |                                                   |                        |     | 35                 |                           | 40  | ns   |

| Frequen                       | cy of operation                                               |                      | -                               |                                                   | -                      | -   | -                  | -                         | -   | -    |

| МАХ                           | Maximum frequency                                             | l/(t <sub>IS</sub> + | t <sub>CKO</sub> )              | 200                                               | 50                     |     | 21                 |                           | 18  | MHz  |

NOTES:

1. Refer also to AC Test Conditions. (Test Load Circuit)

2. For 3-State output; output enable times are tested with  $C_L = 50$ pF to the 1.5V level, and  $S_1$  is open for high-impedance to High tests and closed for high-impedance to Low tests. Output disable times are tested with  $C_L = 5$ pF. High-to-High impedance tests are made to an output voltage of  $V_T = (V_{OH} - 0.5V)$  with S<sub>1</sub> open, and Low-to-High impedance tests are made to the  $V_T = (V_{OL} + 0.5V)$  level with S<sub>1</sub> closed. 3. Resistor values of 1.5k and 550 $\Omega$  provide 3-State levels of 1.0V and 2.0V, respectively. Output timing measurements are to 1.5V level. 4. Leave all the cells on unused product terms intact (unprogrammed) for all patterns.

# PLC18V8Z

#### **POWER-UP RESET**

In order to facilitate state machine design and testing, a power-up reset function has been incorporated in the PLC18V8Z. All internal registers will reset to Active-Low (logical "0") after a specified period of time ( $t_{PPR}$ ). Therefore, any OMC that has been configured as a registered output will always produce an Active-High on the associated output pin because of the inverted output buffer. The internal feedback (Q) of a registered OMC will also be set Low. The programmed polarity of OMC will not affect the Active-High output condition during a system power-up condition.

#### **TIMING DIAGRAMS**

# PLC18V8Z

#### TIMING DIAGRAMS (Continued)

# PLC18V8Z

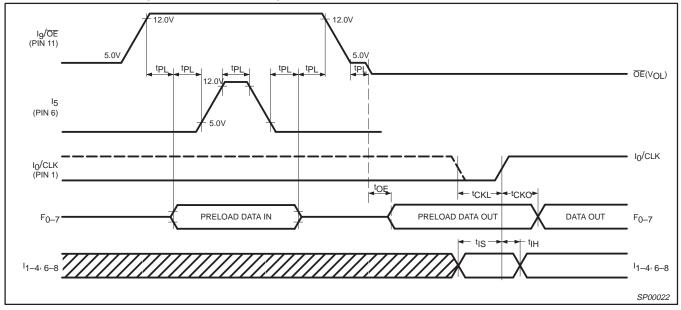

#### REGISTER PRELOAD FUNCTION (DIAGNOSTIC MODE ONLY)

In order to facilitate the testing of state machine/controller designs, a diagnostic mode register preload feature has been incorporated into the PLC18V8Z series device. This feature enables the user to load the registers with predetermined states while a super voltage is applied to Pins 11 and 6 (I9/OE and I5). (See diagram for timing and sequence.)

To read the data out, Pins 11 and 6 must be returned to normal TTL levels. The outputs, F0 - F7, must be enabled in order to read data out. The Q outputs of the registers will reflect data in as input via F0 - F7 during preload. Subsequently, the register Q output via the feedback path will reflect the data in as input via F0 - F7.

Refer to the voltage waveform for timing and voltage references.  $t_{PL}=10\mu\text{sec.}$

#### **REGISTER PRELOAD (DIAGNOSTIC MODE)**

Product specification

# PLC18V8Z

#### LOGIC PROGRAMMING

The PLC18V8Z series is fully supported by industry standard (JEDEC compatible) PLD CAD tools, including Philips Semiconductors' SNAP design software package. ABEL™ and CUPL™ design software packages also support the PLC18V8Z architecture.

All packages allow Boolean and state equation entry formats. SNAP, ABEL and CUPL also accept, as input, schematic capture format.

PLC18V8Z logic designs can also be generated using the program table entry format, which is detailed on the following pages. This program table entry format is supported by SNAP only.

With Logic programming, the AND/OR/EX-OR gate input connections necessary to implement the desired logic function are coded directly from logic equations using the Program Table. Similarly, various OMC configurations are implemented by programming the Architecture Control bits AC1 and AC2. Note that the configuration cell is automatically programmed based on the OMC configuration.

In this table, the logic state of variables I, P and B associated with each Sum Term S is assigned a symbol which results in the proper fusing pattern of corresponding link pairs, defined as follows:

#### **OUTPUT POLARITY - (O, B)**

#### "AND" ARRAY – (I, B)

#### NOTE:

1. A factory shipped unprogrammed device is configured such that all cells are in a conductive state.

ABEL is a trademark of Data I/O Corp.

CUPL is a trademark of Logical Devices, Inc.

Philips Semiconductors

# PLC18V8Z

**PROGRAM TABLE** NOTES: CUSTOMER NAME \_\_\_\_ In the unprogrammed or virgin state: PURCHASE ORDER # \_\_\_ • All AND gate locations are pulled to a logic "0" (Low). • Output polarity is inverting. \_\_\_\_\_ CF(XXXX) PHILIPS DEVICE # • Pins 1 and 11 are configured as inputs 0 and 9, respectively, via CUSTOMER SYMBOLIZED PART #\_\_\_\_ the configuration cell. The clock and  $\overline{OE}$  functions are disabled. • All output macro cells (OMC) are configured as combinatorial I/O, TOTAL NUMBER OF PARTS. with the outputs disabled via the direction control term. REV. DATE PROGRAM TABLE # INACTIVE I, F (I, B) I, F (I, B) \*\*DONT CARE 0 3 7 1 -AND ARRAY -ဖ œ ٥ 7 1 -ΞO 6 5 FIXED OUTPUT BIDIRECTIONAL I/O REGISTERED (D-TYPE) FIXED INPUT 4 3 OMC ARCH. 2 0 7 6 8 O D AND CONTROL 19 18 PIN 1 = CLK; PIN 11 = <del>oe</del> PIN 1, PIN 11 = INPUT NON-INVERTING INVERTING 5 4 1 CONFIGURATION CELL (CLK/OE CONTROL) ARCH. CONTROL BITS OUTPUT POLARITY OUTPUT POLARITY CONFIG. CELL' 16 Т F(I) 3 2 과 4 - 0 <u></u> -± ⊏ г Н OR ARRAY (FIXED) DATA CANNOT BE ENTERED INTO THE OR ARRAY FIELD DUE TO THE FIXED NATURE OF THE DEVICE ARCHITEC-TURE. 10 ACTIVE OUTPUT NOT USED DIRECTION CONTROL D 6 5 18 1 OR (FIXED) F (B, O, D) 5 4 3 2 16 귱 14 \_\_\_\_\_\_\_\_\_\_ -3 Þ

SP00029

PLC18V8Z

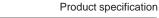

SOT146-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | c              | D <sup>(1)</sup> | E <sup>(1)</sup> | e    | e <sub>1</sub> | L            | M <sub>E</sub> | M <sub>H</sub> | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.30   | 0.53<br>0.38   | 0.36<br>0.23   | 26.92<br>26.54   | 6.40<br>6.22     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80   | 10.0<br>8.3    | 0.254 | 2.0                      |

| inches | 0.17      | 0.020                  | 0.13                   | 0.068<br>0.051 | 0.021<br>0.015 | 0.014<br>0.009 | 1.060<br>1.045   | 0.25<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31   | 0.39<br>0.33   | 0.01  | 0.078                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE | ΓLINE |     | REFER | RENCES | EUROPEAN   | ISSUE DATE                       |  |

|---------|-------|-----|-------|--------|------------|----------------------------------|--|

| VER     | RSION | IEC | JEDEC | EIAJ   | PROJECTION | 1550E DATE                       |  |

| SOT     | 146-1 |     |       | SC603  | $\bigcirc$ | <del>-92-11-17</del><br>95-05-24 |  |

# PLC18V8Z

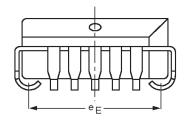

#### DIMENSIONS (millimetre dimensions are derived from the original inch dimensions)

| UNIT   | А              | A <sub>1</sub><br>min. | Α3   | A <sub>4</sub><br>max. | bp           | b <sub>1</sub> | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | е <sub>D</sub> | еE           | Н <sub>D</sub> | HE            | k              | Lp           | v     | w     | У     | Z <sub>D</sub> <sup>(1)</sup><br>max. | Z <sub>E</sub> <sup>(1)</sup><br>max. | β               |

|--------|----------------|------------------------|------|------------------------|--------------|----------------|------------------|------------------|------|----------------|--------------|----------------|---------------|----------------|--------------|-------|-------|-------|---------------------------------------|---------------------------------------|-----------------|

| mm     | 4.57<br>4.19   | 0.51                   | 0.25 | 3.05                   | 0.53<br>0.33 | 0.81<br>0.66   | 9.04<br>8.89     | 9.04<br>8.89     | 1.27 | 8.38<br>7.37   | 8.38<br>7.37 | 10.03<br>9.78  | 10.03<br>9.78 | 1.22<br>1.07   | 1.44<br>1.02 | 0.18  | 0.18  | 0.10  | 2.16                                  | 2.16                                  | 45 <sup>0</sup> |

| inches | 0.180<br>0.165 | 0.020                  | 0.01 | 0.12                   |              | 0.032<br>0.026 |                  | 0.356<br>0.350   | 0.05 | 0.330<br>0.290 | 1            | 0.395<br>0.385 |               | 0.048<br>0.042 |              | 0.007 | 0.007 | 0.004 | 0.085                                 | 0.085                                 |                 |

#### Note

1. Plastic or metal protrusions of 0.01 inches maximum per side are not included.

| OUTLINE  |     | REFER    | RENCES | EUROPEAN   | ISSUE DATE                       |  |

|----------|-----|----------|--------|------------|----------------------------------|--|

| VERSION  | IEC | JEDEC    | EIAJ   | PROJECTION |                                  |  |

| SOT380-1 |     | MO-047AA |        |            | <del>-92-11-17</del><br>95-02-25 |  |

SOT380-1

PLC18V8Z

#### Note

1997 Aug 08

inches

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

0.014

0.009

0.49

0.29

0.01

0.004

0.089

| OUTLINE  |        | REFER    | EUROPEAN | ISSUE DATE |            |                                  |  |

|----------|--------|----------|----------|------------|------------|----------------------------------|--|

| VERSION  | IEC    | JEDEC    | EIAJ     |            | PROJECTION | 1550E DATE                       |  |

| SOT163-1 | 075E04 | MS-013AC |          |            |            | <del>-92-11-17</del><br>95-01-24 |  |

0.39

0.016

0.039

0.01

0.01

0.004

0.016

Product specification

# PLC18V8Z

| DEFINITIONS               |                        |                                                                                                                                                                                                                                                            |  |  |  |  |  |

|---------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Sheet Identification | Product Status         | Definition                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Objective Specification   | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                         |  |  |  |  |  |

| Preliminary Specification | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |  |  |

| Product Specification     | Full Production        | This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |  |  |  |  |  |

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1997 All rights reserved. Printed in U.S.A.

Let's make things better.