# CA3086

# General Purpose NPN Transistor Array

November 1996

## Applications

- Three Isolated Transistors and One Differentially Connected Transistor Pair For Low-Power Applications from DC to 120MHz

- General-Purpose Use in Signal Processing Systems Operating in the DC to 190MHz Range

- Temperature Compensated Amplifiers

- See Application Note, AN5296 "Application of the CA3018 Integrated-Circuit Transistor Array" for Suggested Applications

## **Ordering Information**

| PART NUMBER<br>(BRAND) | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE                     | PKG.<br>NO. |

|------------------------|----------------------------------|-----------------------------|-------------|

| CA3086                 | -55 to 125                       | 14 Ld PDIP                  | E14.3       |

| CA3086M<br>(3086)      | -55 to 125                       | 14 Ld SOIC                  | M14.15      |

| CA3086M96<br>(3086)    | -55 to 125                       | 14 Ld SOIC Tape<br>and Reel | M14.15      |

| CA3086F                | -55 to 125                       | 14 Ld CERDIP                | F14.3       |

## Description

The CA3086 consists of five general-purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially connected pair.

The transistors of the CA3086 are well suited to a wide variety of applications in low-power systems at frequencies from DC to 120MHz. They may be used as discrete transistors in conventional circuits. However, they also provide the very significant inherent advantages unique to integrated circuits, such as compactness, ease of physical handling and thermal matching

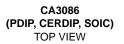

#### Pinout

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

#### **Absolute Maximum Ratings**

| The following ratings apply for each transistor in the device: |       |

|----------------------------------------------------------------|-------|

| Collector-to-Emitter Voltage, V <sub>CEO</sub>                 | . 15V |

| Collector-to-Base Voltage, V <sub>CBO</sub>                    | . 20V |

| Collector-to-Substrate Voltage, V <sub>CIO</sub> (Note 1)      |       |

| Emitter-to-Base Voltage, V <sub>EBO</sub>                      | 5V    |

| Collector Current, I <sub>C</sub>                              | 50mA  |

|                                                                |       |

### **Operating Conditions**

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2)     | $\theta_{JA}$ ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)    |

|------------------------------------------|-----------------------------------|----------------------------------------|

| CERDIP Package                           | 150                               | 75                                     |

| PDIP Package                             | 180                               | N/A                                    |

| SOIC Package                             | 220                               | N/A                                    |

| Maximum Power Dissipation (Any one tran  | nsistor)                          | 300mW                                  |

| Maximum Junction Temperature (Hermetic I | Packages)                         | 175 <sup>0</sup> C                     |

| Maximum Junction Temperature (Plastic F  | Package)                          | 150 <sup>0</sup> C                     |

| Maximum Storage Temperature Range        |                                   | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 1)   | 0s)                               | 300 <sup>0</sup> C                     |

| (SOIC - Lead Tips Only)                  |                                   |                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- The collector of each transistor in the CA3086 is isolated from the substrate by an integral diode. The substrate (Terminal 13) must be connected to the most negative point in the external circuit to maintain isolation between transistors and to provide for normal transistor action. To avoid undesirable coupling between transistors, the substrate (Terminal 13) should be maintained at either DC or signal (AC) ground. A suitable bypass capacitor can be used to establish a signal ground.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications** T<sub>A</sub> = 25<sup>o</sup>C, For Equipment Design

| PARAMETER                                    | SYMBOL               | TEST CONDITIONS                          | MIN | ТҮР        | МАХ | UNITS |

|----------------------------------------------|----------------------|------------------------------------------|-----|------------|-----|-------|

| Collector-to-Base Breakdown Voltage          | V <sub>(BR)CBO</sub> | $I_{C} = 10 \mu A, I_{E} = 0$            | 20  | 60         | -   | V     |

| Collector-to-Emitter Breakdown Voltage       | V <sub>(BR)CEO</sub> | I <sub>C</sub> = 1mA, I <sub>B</sub> = 0 | 15  | 24         | -   | V     |

| Collector-to-Substrate Breakdown Voltage     | V <sub>(BR)CIO</sub> | $I_{C} = 10 \mu A, I_{CI} = 0$           | 20  | 60         | -   | V     |

| Emitter-to-Base Breakdown Voltage            | V <sub>(BR)EBO</sub> | $I_{E} = 10 \mu A, I_{C} = 0$            | 5   | 7          | -   | V     |

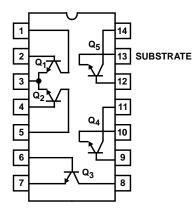

| Collector-Cutoff Current (Figure 1)          | I <sub>CBO</sub>     | $V_{CB} = 10V, I_E = 0,$                 | -   | 0.002      | 100 | nA    |

| Collector-Cutoff Current (Figure 2)          | ICEO                 | $V_{CE} = 10V, I_B = 0,$                 | -   | (Figure 2) | 5   | μΑ    |

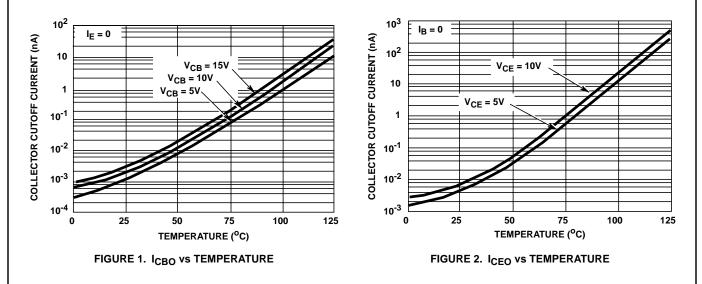

| DC Forward-Current Transfer Ratio (Figure 3) | h <sub>FE</sub>      | $V_{CE} = 3V$ , $I_C = 1mA$              | 40  | 100        | -   |       |

#### **Electrical Specifications** T<sub>A</sub> = 25<sup>o</sup>C, Typical Values Intended Only for Design Guidance

| PARAMETER                                          | SYMBOL                     | TEST CONDITIONS                                                    |                       | TYPICAL<br>VALUES | UNITS              |

|----------------------------------------------------|----------------------------|--------------------------------------------------------------------|-----------------------|-------------------|--------------------|

| DC Forward-Current Transfer Ratio                  | h <sub>FE</sub>            | $V_{CE} = 3V$                                                      | I <sub>C</sub> = 10mA | 100               |                    |

| (Figure 3)                                         |                            |                                                                    | I <sub>C</sub> = 10μΑ | 54                |                    |

| Base-to-Emitter Voltage (Figure 4)                 | V <sub>BE</sub>            | V <sub>CE</sub> = 3V                                               | I <sub>E</sub> = 1 mA | 0.715             | V                  |

|                                                    |                            |                                                                    | I <sub>E</sub> = 10mA | 0.800             | V                  |

| V <sub>BE</sub> Temperature Coefficient (Figure 5) | $\Delta V_{BE} / \Delta T$ | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                        |                       | -1.9              | mV/ <sup>o</sup> C |

| Collector-to-Emitter<br>Saturation Voltage         | V <sub>CE SAT</sub>        | I <sub>B</sub> = 1mA, I <sub>C</sub> = 10mA                        |                       | 0.23              | V                  |

| Noise Figure (Low Frequency)                       | NF                         | $  f = 1 kHz, V_{CE} = 3 V, I_C = 100 \mu A, \\ R_S = 1 k \Omega $ |                       | 3.25              | dB                 |

| PARAMETER                                                           | SYMBOL           | TEST CONDITIONS                                     | TYPICAL<br>VALUES      | UNITS |

|---------------------------------------------------------------------|------------------|-----------------------------------------------------|------------------------|-------|

| Low-Frequency, Small-Signal Equivalent-<br>Circuit Characteristics: |                  | $f = 1kHz, V_{CE} = 3V, I_C = 1mA$                  |                        |       |

| Forward Current-Transfer Ratio<br>(Figure 6)                        | h <sub>FE</sub>  |                                                     | 100                    | -     |

| Short-Circuit Input Impedance<br>(Figure 6)                         | h <sub>IE</sub>  |                                                     | 3.5                    | kΩ    |

| Open-Circuit Output Impedance<br>(Figure 6)                         | h <sub>OE</sub>  |                                                     | 15.6                   | μS    |

| Open-Circuit Reverse-Voltage<br>Transfer Ratio (Figure 6)           | h <sub>RE</sub>  |                                                     | 1.8 X 10 <sup>-4</sup> | -     |

| Admittance Characteristics:                                         |                  | f = 1MHz,V <sub>CE</sub> = 3V, I <sub>C</sub> = 1mA |                        |       |

| Forward Transfer Admittance<br>(Figure 7)                           | УFE              |                                                     | 31 - j1.5              | mS    |

| Input Admittance (Figure 8)                                         | УІЕ              |                                                     | 0.3 + j0.04            | mS    |

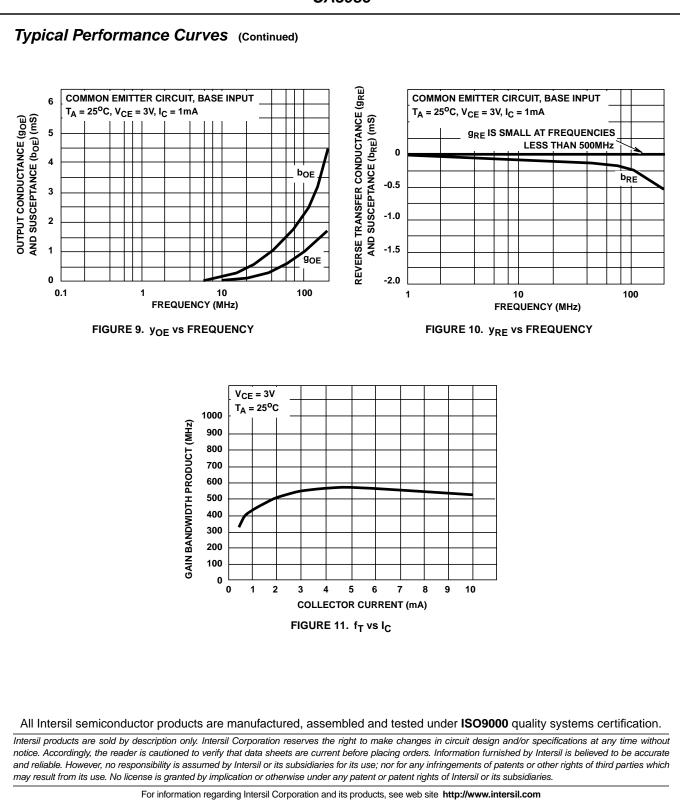

| Output Admittance (Figure 9)                                        | УОЕ              |                                                     | 0.001 + j0.03          | mS    |

| Reverse Transfer Admittance<br>(Figure 10)                          | УRE              |                                                     | See Figure 10          | -     |

| Gain-Bandwidth Product (Figure 11)                                  | f <sub>T</sub>   | $V_{CE} = 3V$ , $I_C = 3mA$                         | 550                    | MHz   |

| Emitter-to-Base Capacitance                                         | C <sub>EBO</sub> | $V_{EB} = 3V, I_E = 0$                              | 0.6                    | pF    |

| Collector-to-Base Capacitance                                       | C <sub>CBO</sub> | $V_{CB} = 3V, I_{C} = 0$                            | 0.58                   | pF    |

| Collector-to-Substrate Capacitance                                  | C <sub>CIO</sub> | $V_{C I} = 3V, I_{C} = 0$                           | 2.8                    | pF    |

# **Electrical Specifications** $T_A = 25^{\circ}C$ , Typical Values Intended Only for Design Guidance (Continued)

# **Typical Performance Curves**

## Sales Office Headquarters

#### NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 724-7000 FAX: (321) 724-7240

#### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029