# Am186<sup>™</sup>ER and Am188<sup>™</sup>ER

# High-Performance, 80C186- and 80C188-Compatible, 16-Bit Embedded Microcontrollers with RAM

## DISTINCTIVE CHARACTERISTICS

- E86<sup>TM</sup> family 80C186- and 80C188-compatible microcontrollers with enhanced bus interface

- Lower system cost with high performance

- 3.3-V  $\pm$  0.3-V operation with 5-V tolerant I/O

#### Memory integration

- 32 Kbyte of internal SRAM

- Internal SRAM provides same performance as zero-wait-state external memory

- High performance

- 25-, 33-, 40- and 50-MHz operating frequencies

- Supports zero-wait-state operation at 50 MHz with 55-ns external memory

- 1-Mbyte memory address space

- 64-Kbyte I/O space

- Enhanced features provide faster access to memory and various clock input modes

- Nonmultiplexed address bus provides glueless interface to external RAM and ROM

- Phase-locked loop (PLL) enables processor to operate at up to four times clock input frequency

- Enhanced integrated peripherals

- Thirty-two programmable I/O (PIO) pins

- Asynchronous serial port allows full-duplex, 7-bit or 8-bit data transfers

- DMA to and from asynchronous serial port

- Synchronous serial interface allows half-duplex, bidirectional data transfer to and from ASICs

- Reset configuration register

- Additional external interrupts

- Hardware watchdog timer can generate NMI or system reset

- Pseudo static RAM (PSRAM) controller includes auto refresh capability

- Familiar 80C186 peripherals with enhanced functionality

- Two independent DMA channels

- Programmable interrupt controller with six external interrupts

- Three programmable 16-bit timers

- Programmable memory and peripheral chip-select logic

- Programmable wait state generator

- Power-save clock mode

- Software-compatible with the 80C186 and 80C188 microcontrollers

- Widely available native development tools, applications, and system software

- Available in the following packages:

100-pin, thin quad flat pack (TQFP)

- 100-pin, plastic quad flat pack (PQFP)

## **GENERAL DESCRIPTION**

The Am186<sup>™</sup>ER and Am188<sup>™</sup>ER microcontrollers are part of the AMD E86<sup>™</sup> family of embedded microcontrollers and microprocessors based on the x86 architecture. The Am186ER and Am188ER microcontrollers are the ideal upgrade for designs requiring 80C186/80C188 microcontroller compatibility, increased performance, serial communications, a direct bus interface, and integrated memory.

The Am186ER and Am188ER microcontrollers integrate memory and the functions of the CPU, nonmultiplexed address bus, timers, chip selects, interrupt controller, DMA controller, PSRAM controller, watchdog timer, asynchronous serial port, synchronous serial interface, and programmable I/O (PIO) pins on one chip. Compared to the 80C186/ 80C188 microcontrollers, the Am186ER and Am188ER microcontrollers enable designers to reduce the size, power consumption, and cost of embedded systems, while increasing functionality and performance.

The Am186ER and Am188ER microcontrollers have been designed to meet the most common requirements of embedded products developed for the communications, office automation, mass storage, and general embedded markets. Specific applications include feature phones, cellular phones, PBXs, multiplexers, modems, disk drives, hand-held terminals and desktop terminals, fax machines, printers, photocopiers, and industrial controls.

<sup>©</sup> Copyright 2000 Advanced Micro Devices, Inc. All rights reserved.

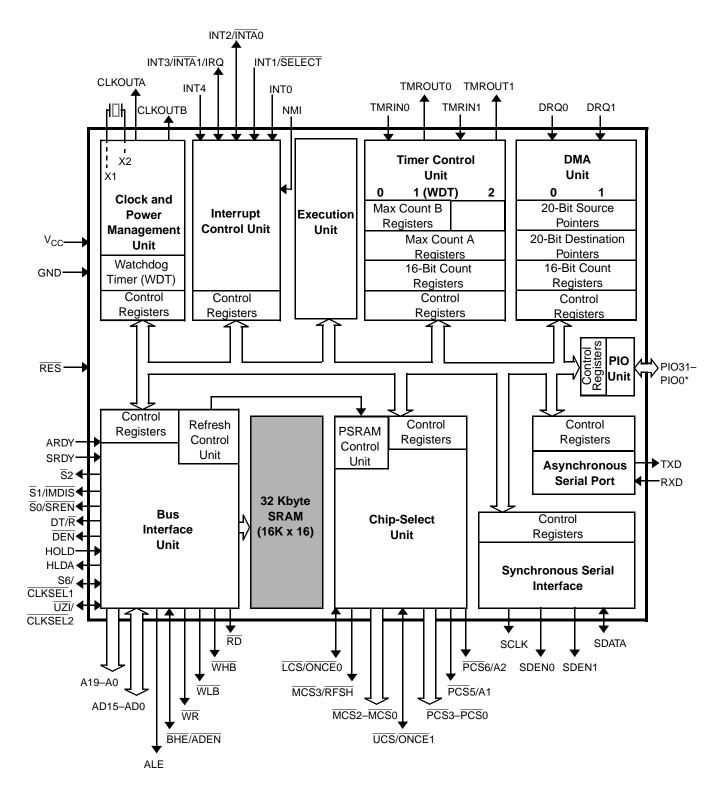

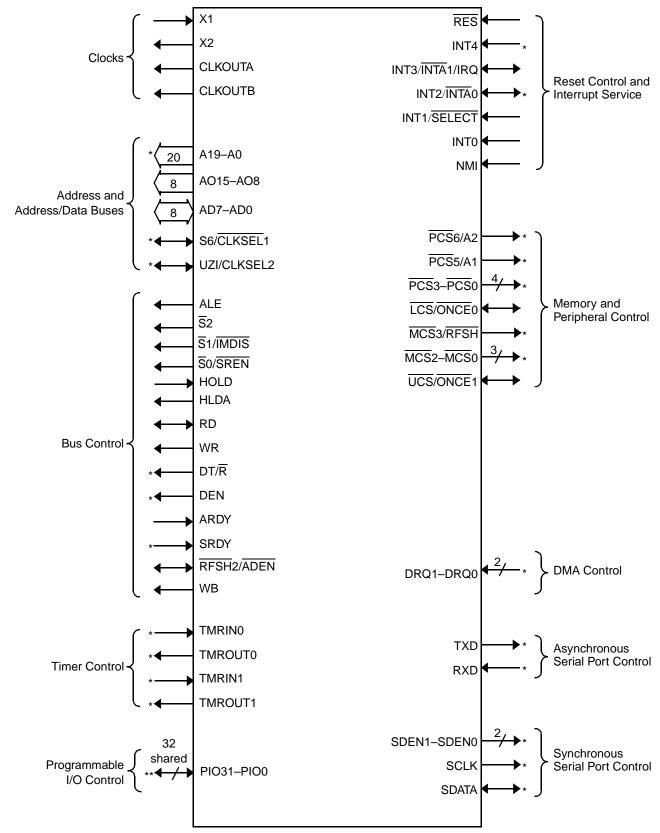

## Am186™ER MICROCONTROLLER BLOCK DIAGRAM

#### Note:

\* All PIO signals are shared with other physical pins. See the pin descriptions beginning on page 30 and Table 3 on page 36 for information on shared functions.

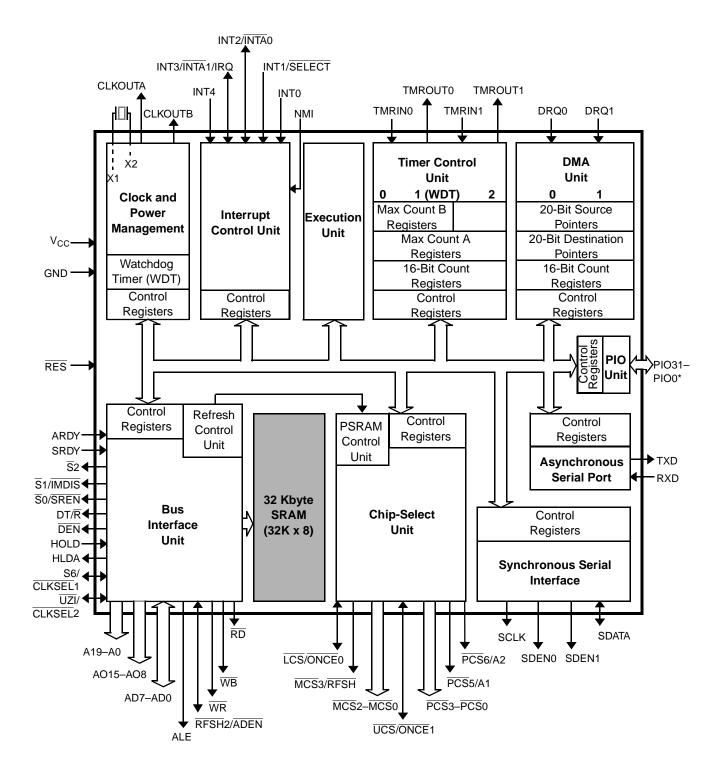

### Am188™ER MICROCONTROLLER BLOCK DIAGRAM

#### Notes:

\* All PIO signals are shared with other physical pins. See the pin descriptions beginning on page 30 and Table 3 on page 36 for information on shared functions.

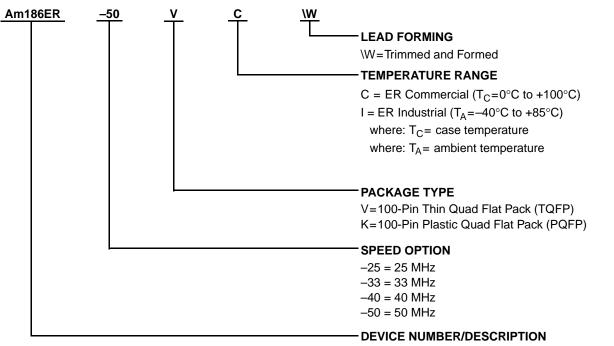

## **ORDERING INFORMATION**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order numbers (valid combinations) are formed by a combination of the elements below.

Am186ER = High-Performance, 80C186-Compatible, 16-Bit Embedded Microcontroller with RAM

Am188ER = High-Performance, 80C188-Compatible, 16-Bit Embedded Microcontroller with RAM

#### Valid Combinations

Valid combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| Valid Combinations |         |  |  |

|--------------------|---------|--|--|

| Am186ER-25         |         |  |  |

| Am186ER-33         | VC\W or |  |  |

| Am186ER-40         | KC\W    |  |  |

| Am186ER-50         |         |  |  |

| Am188ER-25         |         |  |  |

| Am188ER-33         | VC\W or |  |  |

| Am188ER-40         | KC\W    |  |  |

| Am188ER-50         |         |  |  |

| Am186ER-25         |         |  |  |

| Am186ER-33         | KI\W or |  |  |

| Am186ER-40         | VI\W    |  |  |

| Am186ER-50         |         |  |  |

| Am188ER-25         |         |  |  |

| Am188ER-33         | KI\W or |  |  |

| Am188ER-40         | VI\W    |  |  |

| Am188ER-50         |         |  |  |

## TABLE OF CONTENTS

| Distinctive Characteristics                                              | . 1 |

|--------------------------------------------------------------------------|-----|

| General Description                                                      | . 1 |

| Am186™ER Microcontroller Block Diagram                                   | . 2 |

| Am188™ER Microcontroller Block Diagram                                   | . 3 |

| Ordering Information                                                     | . 4 |

| List of Figures                                                          |     |

| List of Tables                                                           |     |

| Revision History                                                         |     |

| E86 <sup>™</sup> Family of Embedded Microprocessors and Microcontrollers |     |

| Related Documents                                                        |     |

| Demonstration Board Products                                             |     |

| Third-Party Development Support Products                                 | .13 |

| Customer Service                                                         |     |

| Key Features and Benefits                                                |     |

| Application Considerations                                               |     |

| Comparison of the Am186 <sup>™</sup> ER and 80C186 Microcontrollers      |     |

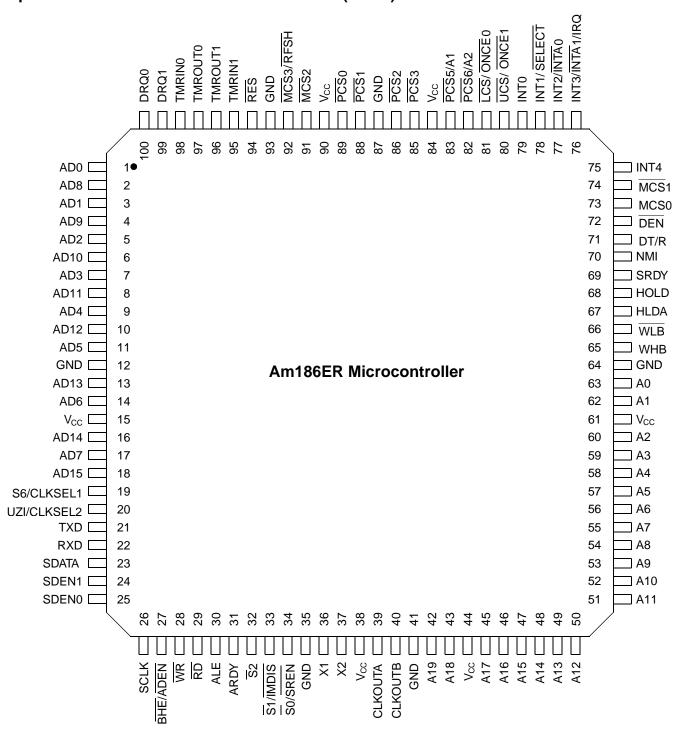

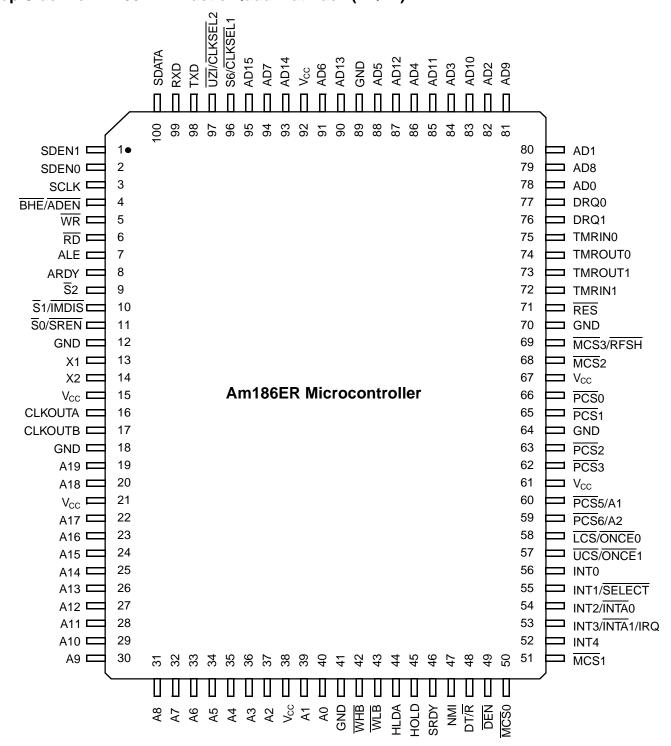

| TQFP Connection Diagram and Pinouts—Am186™ER Microcontroller             |     |

| TQFP Pin Assignments—Am186™ER Microcontroller (Sorted by Pin Number)     |     |

| TQFP Pin Assignments—Am186™ER Microcontroller (Sorted by Pin Name)       |     |

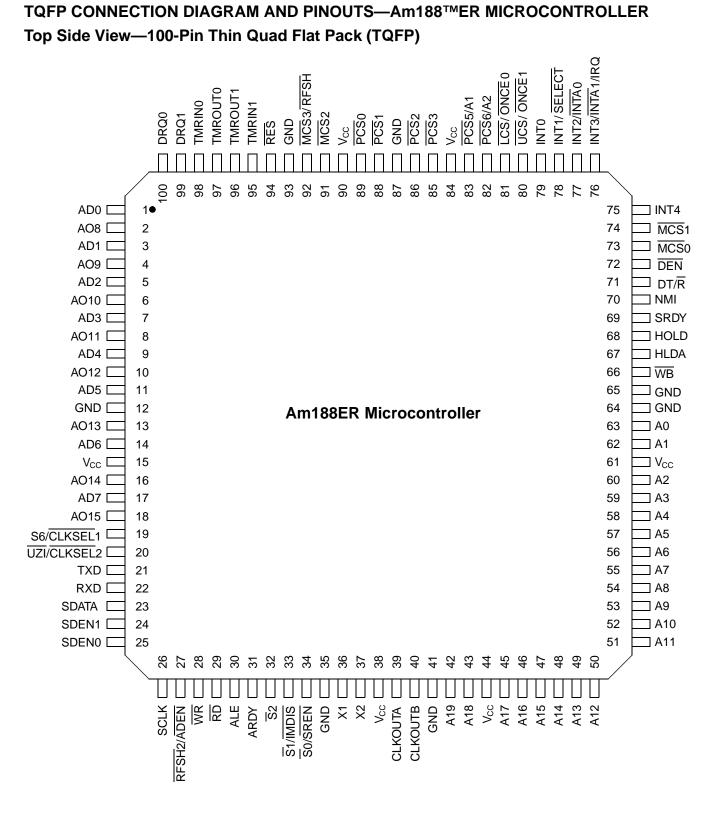

| TQFP Connection Diagram and Pinouts—Am188™ER Microcontroller             |     |

| TQFP Pin Assignments—Am188™ER Microcontroller (Sorted by Pin Number)     |     |

| TQFP Pin Assignments—Am188™ER Microcontroller (Sorted by Pin Name)       |     |

| PQFP Connection Diagram and Pinouts—Am186™ER Microcontroller             |     |

| PQFP Pin Assignments—Am186™ER Microcontroller (Sorted by Pin Number)     |     |

| PQFP Pin Assignments—Am186™ER Microcontroller (Sorted by Pin Name)       |     |

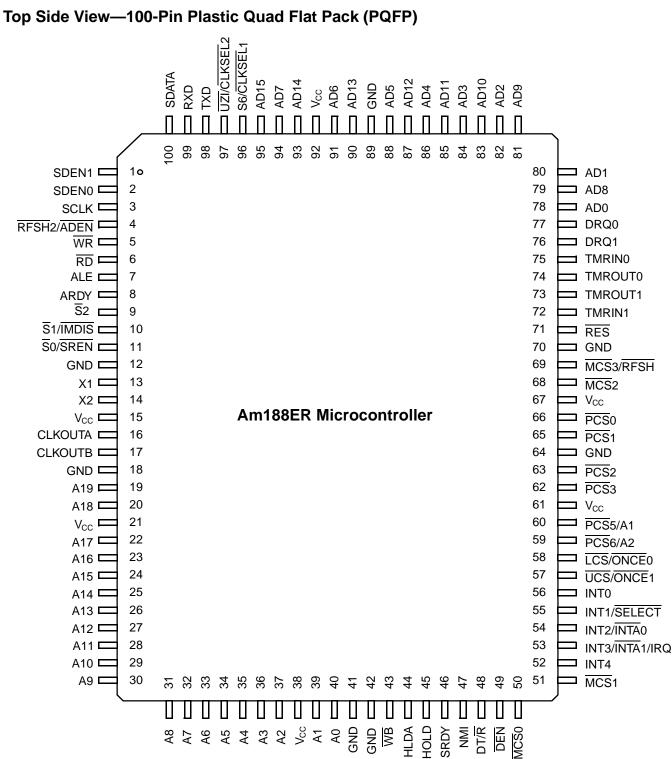

| PQFP Connection Diagram and Pinouts—Am188™ER Microcontroller             |     |

| PQFP Pin Assignments—Am188™ER Microcontroller (Sorted by Pin Number)     |     |

| PQFP Pin Assignments—Am188™ER Microcontroller (Sorted by Pin Name)       |     |

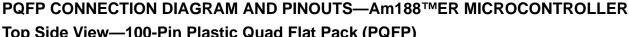

| Logic Symbol—Am186™ER Microcontroller                                    |     |

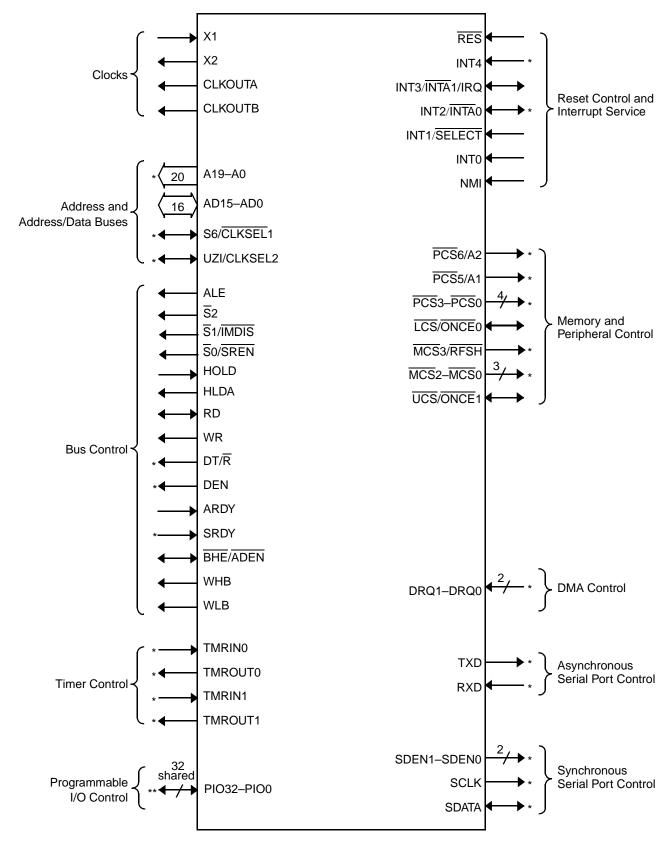

| Logic Symbol—Am188™ER Microcontroller                                    |     |

| Pin Descriptions                                                         |     |

| Pins Used by Emulators                                                   |     |

| A19–A0 (A19/PIO9, A18/PIO8, A17/PIO7)                                    |     |

| AD7–AD0 (AT9/PIO9, AT8/PIO8, AT7/PIO7)                                   |     |

|                                                                          |     |

|                                                                          | 30  |

| AO15–AO8 (Am188™ER Microcontroller)                                      |     |

|                                                                          |     |

|                                                                          |     |

| BHE/ADEN (Am186™ER Microcontroller Only)                                 |     |

|                                                                          |     |

|                                                                          |     |

|                                                                          |     |

| DRQ1–DRQ0 (DRQ1/PIO13, DRQ0/PIO12)                                       |     |

| DT/R/PIO4                                                                |     |

| GND                                                                      |     |

| HLDA                                                                     |     |

| HOLD                                                                     |     |

| INTO                                                                     |     |

| INT1/SELECT                                                              |     |

| INT2/INTA0/PIO31                                                         |     |

| INT3/INTA1/IRQ                                                           |     |

| INT4/PIO30                                                               | 33  |

| LCS/ONCE0                                                  | 33 |

|------------------------------------------------------------|----|

| MCS3/RFSH/PIO25                                            | 33 |

| MCS2-MCS0 (MCS2/PIO24, MCS1/PIO15, MCS0/PIO14)             |    |

| NMI                                                        |    |

| PCS3–PCS0 (PCS3/PIO19, PCS2/PIO18, PCS1/PIO17, PCS0/PIO16) | 34 |

| PCS5/A1/PIO3                                               |    |

| PCS6/A2/PIO2                                               |    |

| PIO31–PIO0 (Shared)                                        |    |

| RD                                                         |    |

| RES                                                        |    |

| RFSH2/ADEN (Am188™ER Microcontroller Only)                 |    |

| RXD/PIO28                                                  |    |

| <u>K</u> AD/F1028<br>S2                                    |    |

|                                                            |    |

|                                                            |    |

| S0/SREN                                                    |    |

| S6/CLKSEL1/PIO29                                           |    |

| SCLK/PIO20                                                 |    |

| SDATA/PIO21                                                |    |

| SDEN1/PIO23, SDEN0/PIO22                                   |    |

| SRDY/PIO6                                                  |    |

| TMRIN0/PIO11                                               |    |

| TMRIN1/PIO0                                                |    |

| TMROUT0/PIO10                                              | 38 |

| TMROUT1/PIO1                                               | 38 |

| TXD/PIO27                                                  | 38 |

| UCS/ONCE1                                                  | 38 |

| UZI/CLKSEL2/PIO26                                          | 38 |

| V <sub>CC</sub>                                            | 39 |

| WHB (Am186™ER Microcontroller Only)                        |    |

| WLB (Am186™ER Microcontroller Only)                        |    |

| WB (Am188™ER Microcontroller Only)                         |    |

| WR                                                         |    |

| X1                                                         |    |

| X1                                                         |    |

| Functional Description                                     |    |

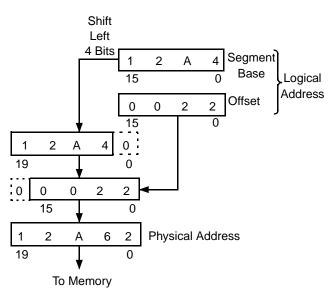

| Memory Organization                                        | 40 |

|                                                            |    |

| I/O Space                                                  |    |

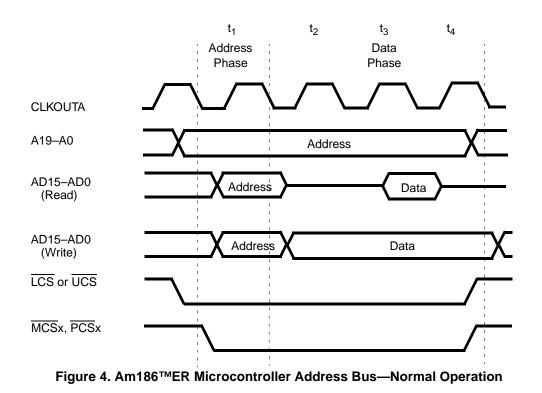

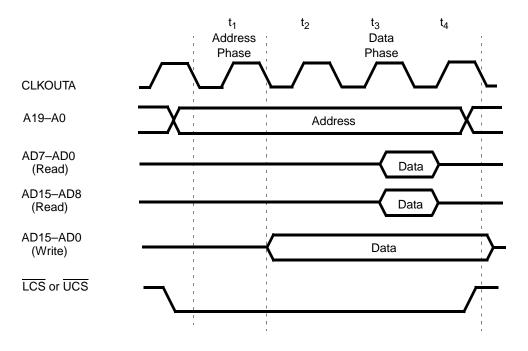

| Bus Operation                                              |    |

| Bus Interface Unit                                         |    |

| Nonmultiplexed Address Bus                                 |    |

| Byte Write Enables                                         |    |

| Output Enable                                              |    |

| Pseudo Static RAM (PSRAM) Support                          |    |

| Peripheral Control Block (PCB)                             | 44 |

| Reading and Writing the PCB                                | 44 |

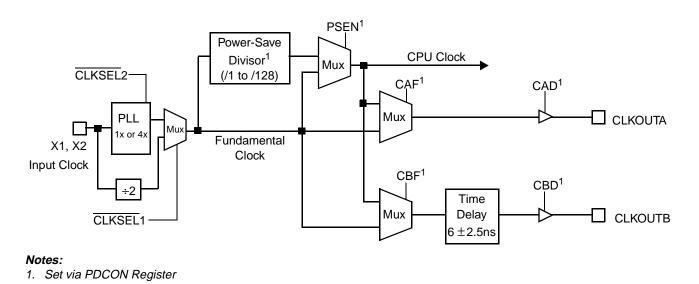

| Clock and Power Management                                 |    |

| Phase-Locked Loop (PLL)                                    |    |

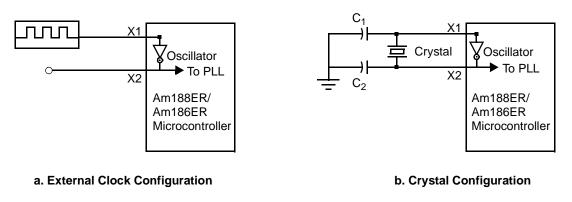

| Crystal-Driven Clock Source                                |    |

| External Source Clock                                      |    |

| System Clocks                                              |    |

| Power-Save Operation                                       |    |

| Initialization and Processor Reset                         |    |

| Reset Configuration Register                               |    |

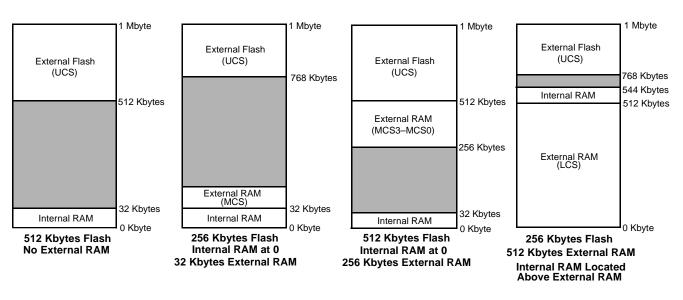

| Chip-Select Unit                                                                                    | . 49 |

|-----------------------------------------------------------------------------------------------------|------|

| Chip-Select Timing                                                                                  | . 49 |

| Ready and Wait-State Programming                                                                    | . 49 |

| Memory Maps                                                                                         |      |

| Chip-Select Overlap                                                                                 |      |

| Upper Memory Chip Select                                                                            |      |

| Low Memory Chip Select                                                                              |      |

| Midrange Memory Chip Selects                                                                        |      |

| Peripheral Chip Selects                                                                             |      |

| Internal Memory                                                                                     |      |

| Interaction with External RAM                                                                       |      |

| Emulator and Debug Modes                                                                            |      |

| Refresh Control Unit                                                                                |      |

| Interrupt Control Unit                                                                              |      |

| Programming the Interrupt Control Unit                                                              |      |

| Timer Control Unit                                                                                  |      |

|                                                                                                     |      |

| Watchdog Timer                                                                                      |      |

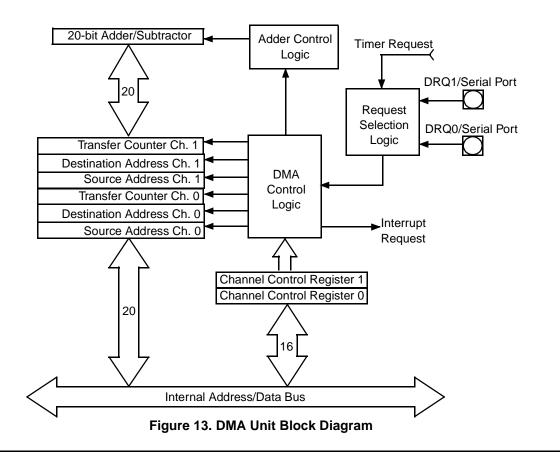

| Direct Memory Access                                                                                |      |

| DMA Operation                                                                                       |      |

| Asynchronous Serial Port/DMA Transfers                                                              |      |

| DMA Channel Control Registers                                                                       |      |

| DMA Priority                                                                                        |      |

| Asynchronous Serial Port                                                                            |      |

| DMA Transfers through the Serial Port                                                               |      |

| Synchronous Serial Interface                                                                        |      |

| Four-Pin Interface                                                                                  |      |

| Programmable I/O (PIO) Pins                                                                         |      |

| Low-Voltage Operation                                                                               | . 59 |

| Low-Voltage Standard                                                                                | . 59 |

| Power Savings                                                                                       | . 59 |

| Input/Output Circuitry                                                                              | . 59 |

| Absolute Maximum Ratings                                                                            | . 60 |

| Operating Ranges                                                                                    | . 60 |

| DC Characteristics Over Commercial and Industrial Operating Ranges                                  |      |

| Thermal Characteristics                                                                             |      |

| TQFP Package                                                                                        |      |

| Typical Ambient Temperatures                                                                        |      |

| Commercial and Industrial Switching Characteristics and Waveforms                                   |      |

| Key to Switching Waveforms                                                                          |      |

| Alphabetical Key to Switching Parameter Symbols                                                     |      |

| Numerical Key to Switching Parameter Symbols                                                        |      |

| Switching Characteristics over Commercial and Industrial Operating Ranges,                          |      |

| Read Cycle (25 MHz and 33 MHz)                                                                      | 70   |

| Switching Characteristics over Commercial and Industrial Operating Ranges,                          |      |

| Read Cycle (40 MHz and 50 MHz)                                                                      | 71   |

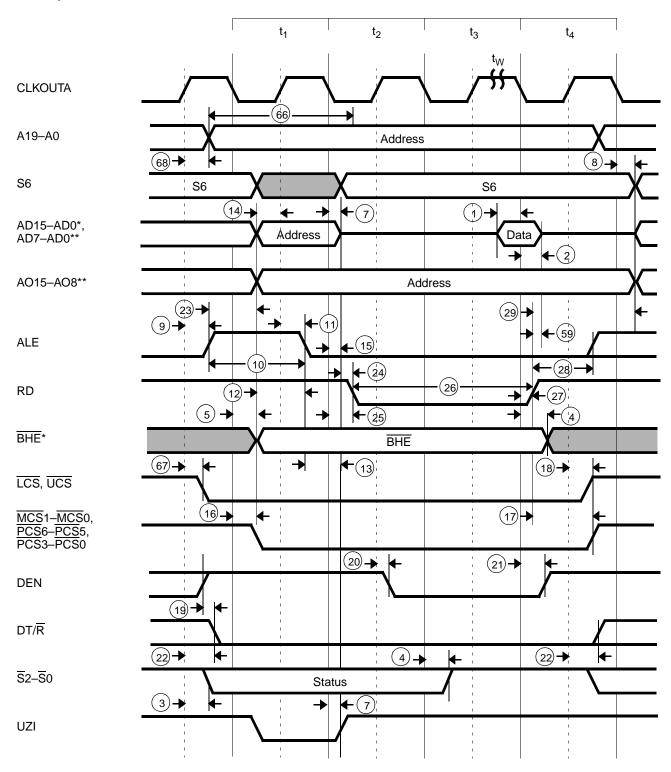

| Read Cycle Waveforms                                                                                |      |

| Switching Characteristics over Commercial and Industrial Operating Ranges,                          | 2    |

| Write Cycle (25 MHz and 33 MHz)                                                                     | 73   |

| Switching Characteristics over Commercial and Industrial Operating Ranges,                          | . 13 |

| Write Cycle (40 MHz and 50 MHz)                                                                     | 71   |

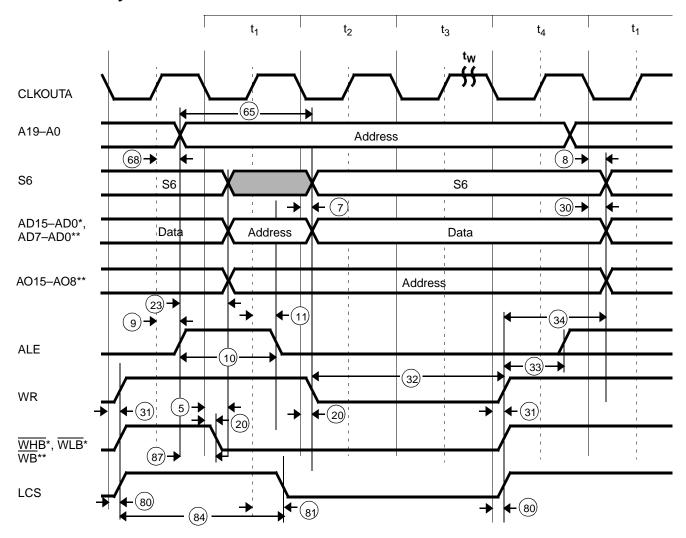

|                                                                                                     |      |

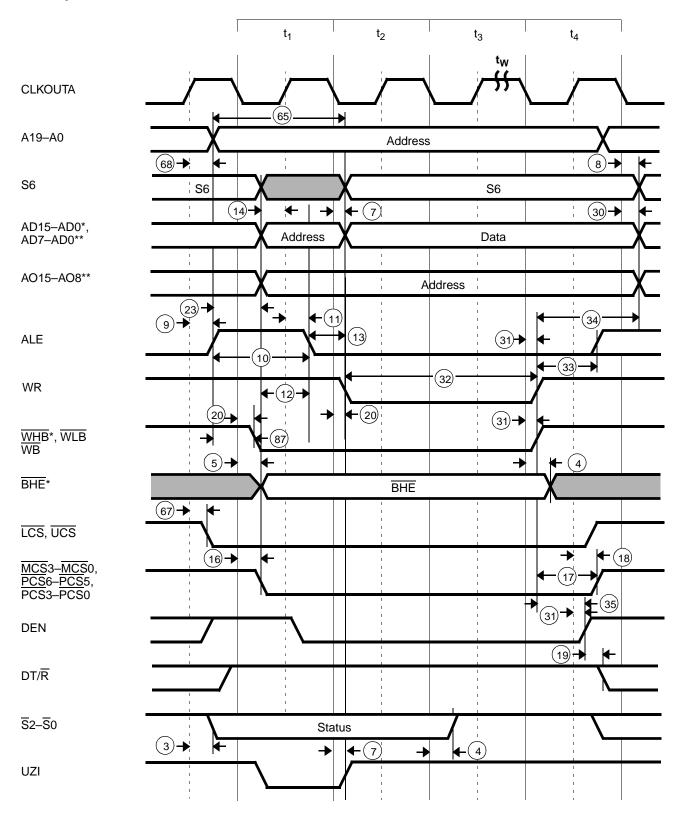

| Write Cycle Waveforms<br>Switching Characteristics over Commercial and Industrial Operating Ranges, | . 73 |

|                                                                                                     | 70   |

| Internal RAM Show Read Cycle (25 MHz and 33 MHz)                                                    | . 10 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

|----------------------------------------------------------------------------|------|

| Internal RAM Show Read Cycle (40 MHz and 50 MHz)                           | . 76 |

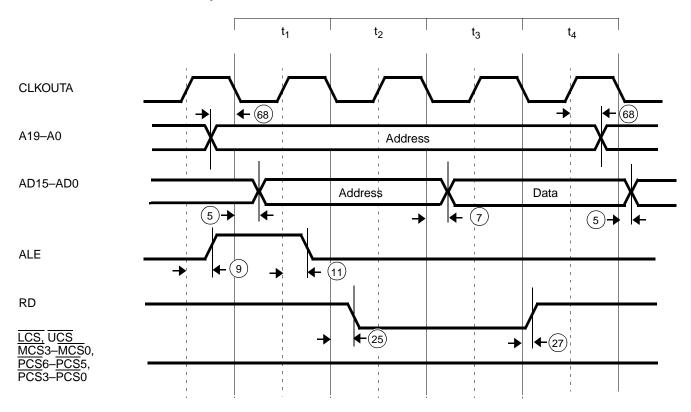

| Internal RAM Show Read Cycle Waveform                                      | . 77 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| PSRAM Read Cycle (25 MHz and 33 MHz)                                       | . 78 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| PSRAM Read Cycle (40 MHz and 50 MHz)                                       | . 79 |

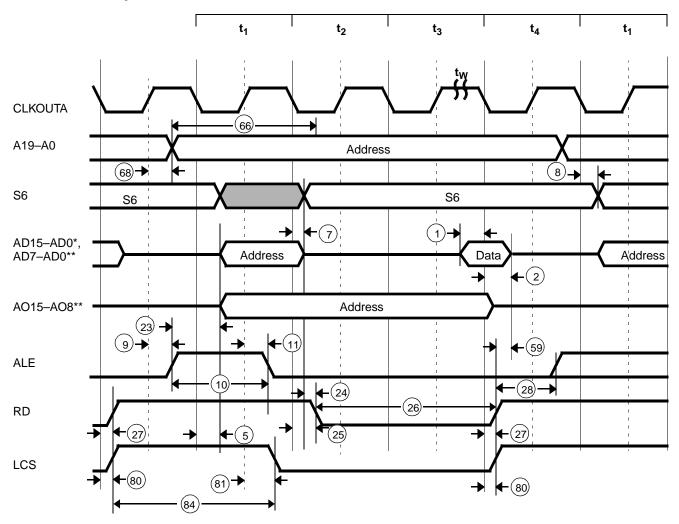

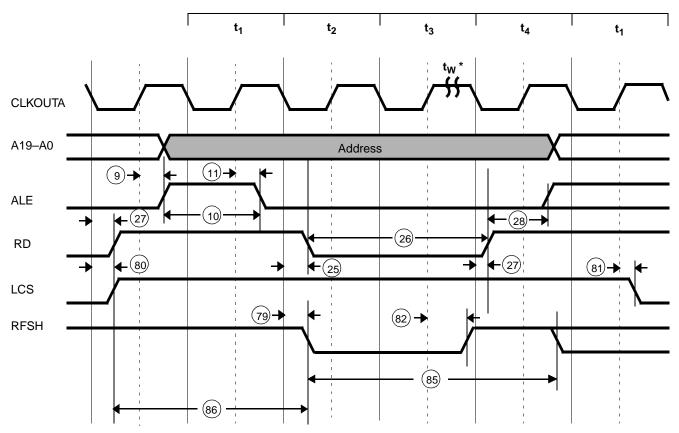

| PSRAM Read Cycle Waveforms                                                 |      |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| PSRAM Write Cycle (25 MHz and 33 MHz)                                      | . 81 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| PSRAM Write Cycle (40 MHz and 50 MHz)                                      | 82   |

| PSRAM Write Cycle Waveforms                                                |      |

| Switching Characteristics over Commercial and Industrial Operating Ranges, | . 00 |

| PSRAM Refresh Cycle (25 MHz and 33 MHz)                                    | 84   |

| Switching Characteristics over Commercial and Industrial Operating Ranges, | . 04 |

| PSRAM Refresh Cycle (40 MHz and 50 MHz)                                    | 95   |

|                                                                            |      |

| PSRAM Refresh Cycle Waveforms                                              | . 00 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, | 07   |

| Interrupt Acknowledge Cycle (25 MHz and 33 MHz)                            | . 07 |

| Switching Characteristics over Commercial Operating Ranges,                | 00   |

| Interrupt Acknowledge Cycle (40 MHz and 50 MHz)                            |      |

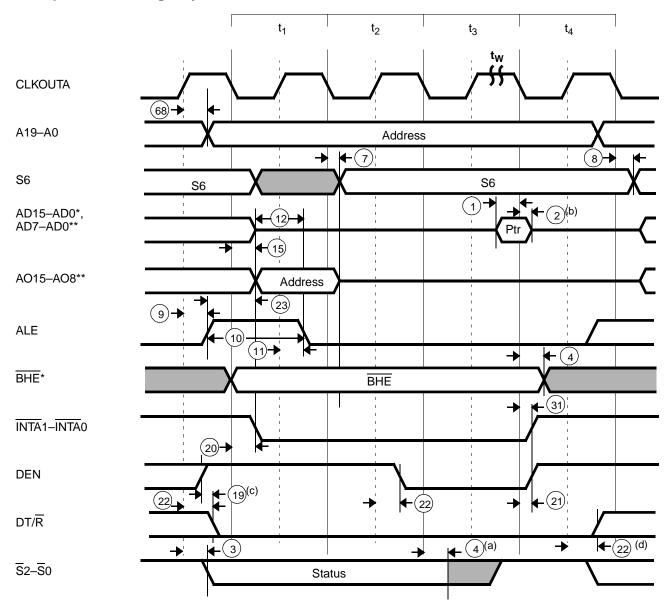

| Interrupt Acknowledge Cycle Waveforms                                      | . 89 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, | ~~   |

| Software Halt Cycle (25 MHz and 33 MHz)                                    | . 90 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Software Halt Cycle (40 MHz and 50 MHz)                                    |      |

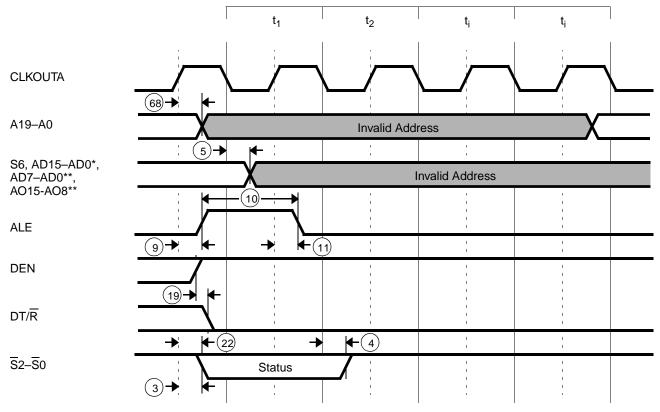

| Software Halt Cycle Waveforms                                              | . 91 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Clock (25 MHz)                                                             | . 92 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Clock (33 MHz)                                                             | . 93 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Clock (40 MHz and 50 MHz)                                                  | . 94 |

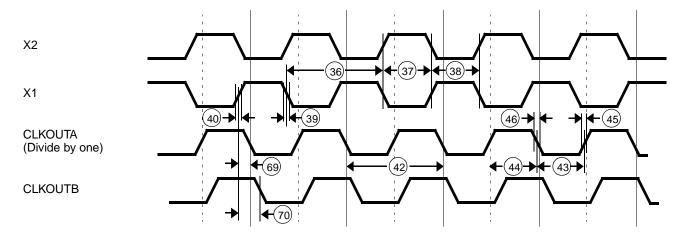

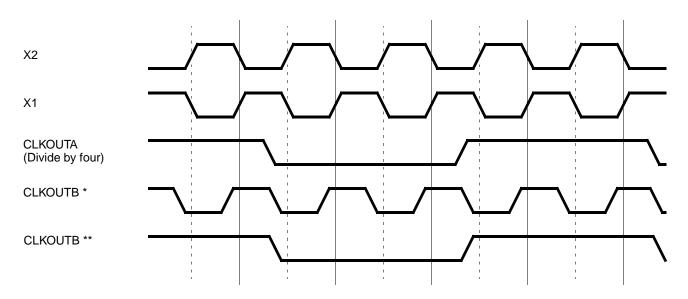

| Clock Waveforms—Active Mode                                                | . 95 |

| Clock Waveforms—Power-Save Mode                                            | . 95 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Ready and Peripheral Timing (25 MHz and 33 MHz)                            | . 96 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Ready and Peripheral Timing (40 MHz and 50 MHz)                            | . 96 |

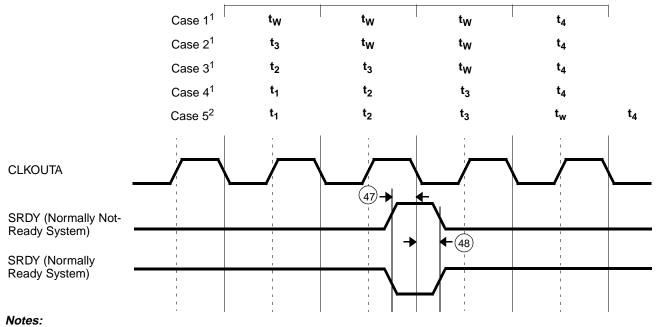

| Synchronous Ready Waveforms                                                | . 97 |

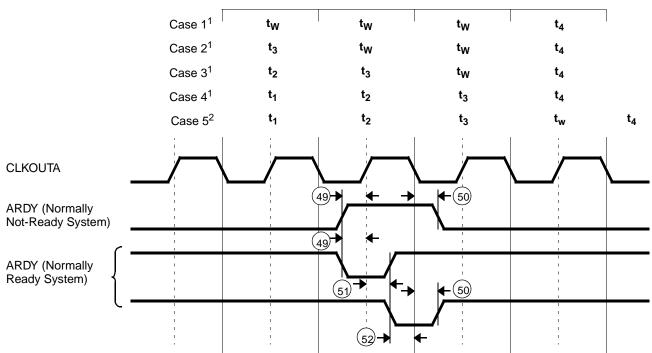

| Asynchronous Ready Waveforms                                               | . 97 |

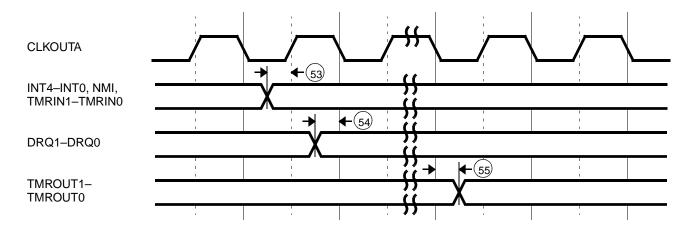

| Peripheral Waveforms                                                       | . 98 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Reset and Bus Hold (25 MHz and 33 MHz)                                     | . 99 |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Reset and Bus Hold (40 MHz and 50 MHz)                                     | . 99 |

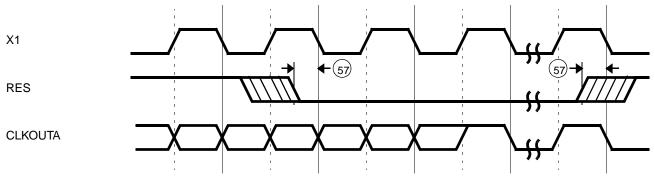

| Reset Waveforms                                                            |      |

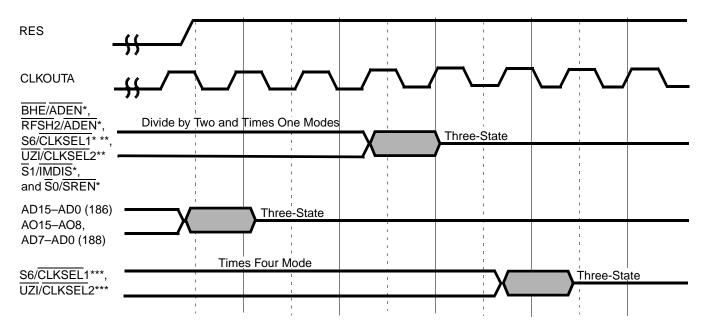

| Signals Related to Reset Waveforms                                         |      |

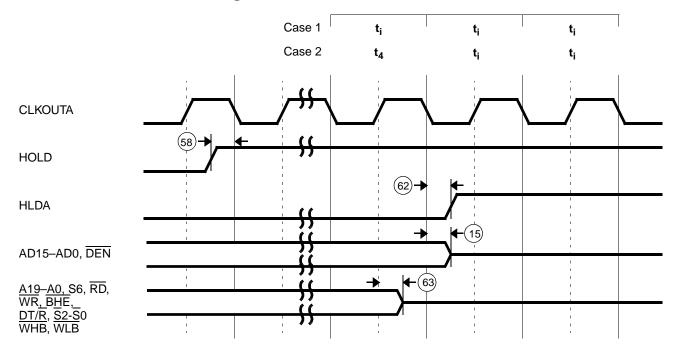

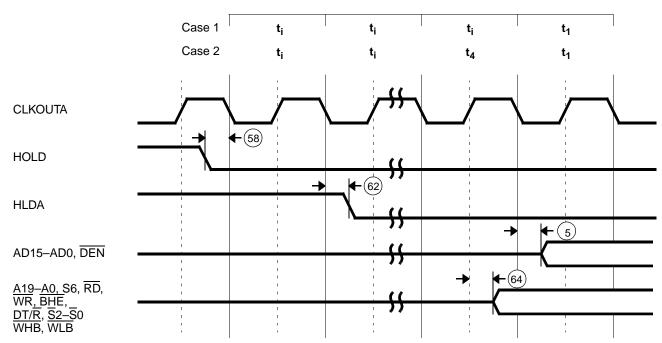

| Bus Hold Waveforms—Entering                                                |      |

| Bus Hold Waveforms—Leaving                                                 |      |

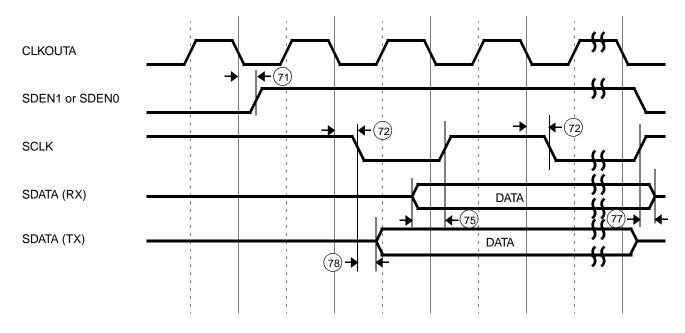

| Switching Characteristics over Commercial and Industrial Operating Ranges, |      |

| Synchronous Serial Interface (SSI) (25 MHz and 33 MHz)                     | 102  |

|                                                                            |      |

| Switching Characteristics over Commercial and Industrial Operating Ranges, |     |

|----------------------------------------------------------------------------|-----|

| Synchronous Serial Interface (SSI) (40 MHz and 50 MHz)                     | 102 |

| Synchronous Serial Interface (SSI) Waveforms                               | 103 |

| TQFP Physical Dimensions                                                   | 104 |

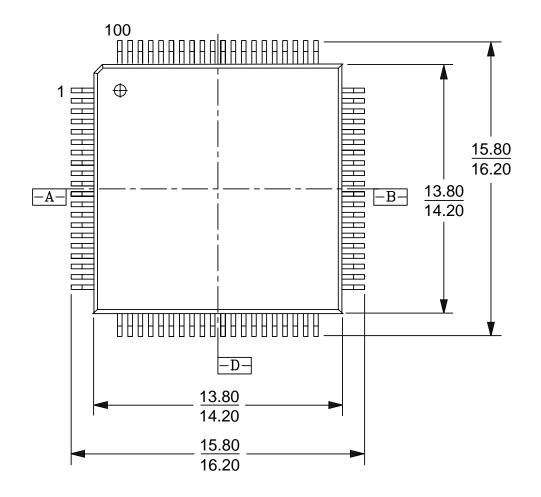

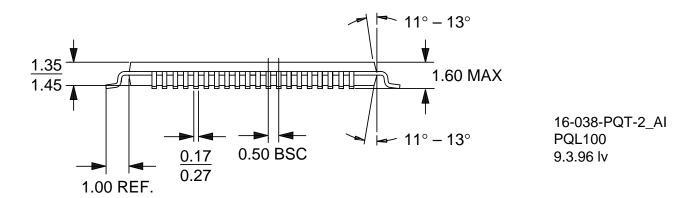

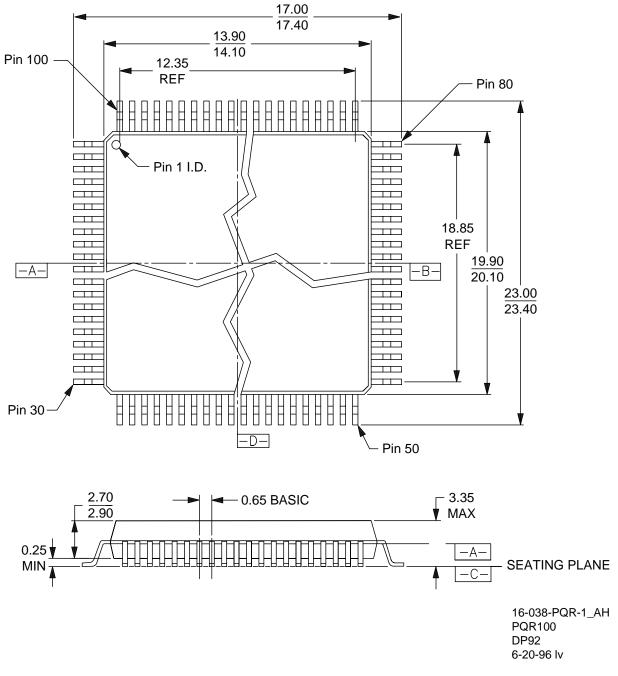

| PQFP Physical Dimensions                                                   | 105 |

| Index                                                                      |     |

## LIST OF FIGURES

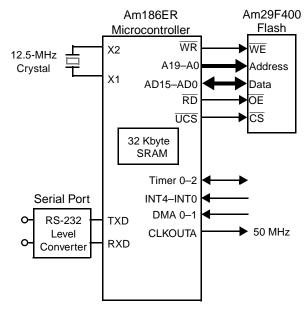

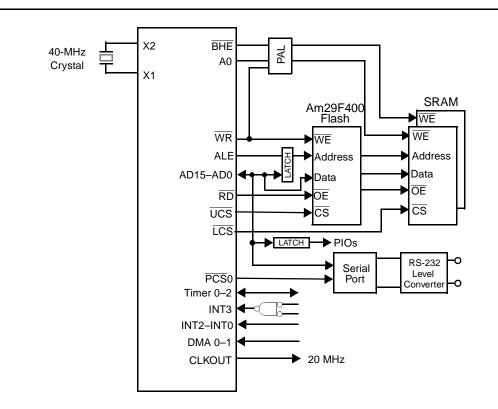

| Figure 1.  | Am186ER 50-MHz Example System Design                                                       | . 15 |

|------------|--------------------------------------------------------------------------------------------|------|

| Figure 2.  | Typical 80C186 System Design                                                               | . 15 |

| Figure 3.  | Two-Component Address Example                                                              | . 40 |

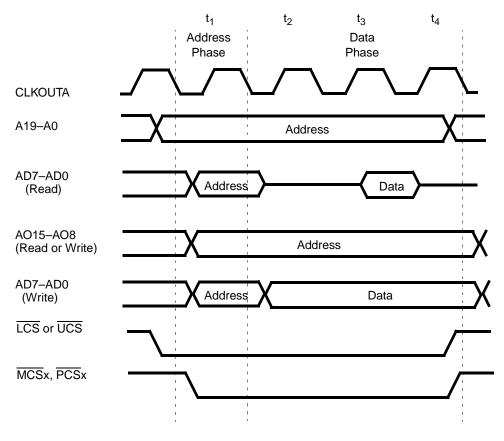

| Figure 4.  | Am186 <sup>™</sup> ER Microcontroller Address Bus—Normal Operation                         | . 42 |

| Figure 5.  | Am186™ER Microcontroller—Address Bus Disable in Effect                                     | . 42 |

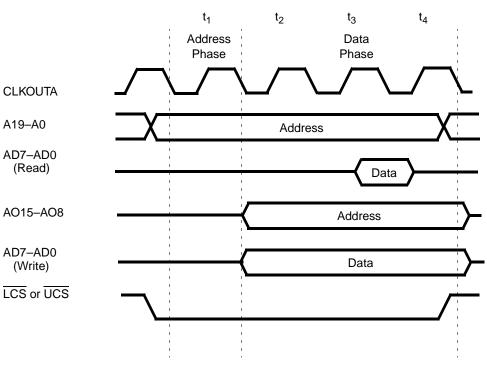

| Figure 6.  | Am188™ER Microcontroller Address Bus—Normal Operation                                      | . 43 |

| Figure 7.  | Am188™ER Microcontroller—Address Bus Disable in Effect                                     |      |

| Figure 8.  | Am186 <sup>™</sup> ER and Am188 <sup>™</sup> ER Microcontrollers Oscillator Configurations | . 45 |

| Figure 9.  | Peripheral Control Block Register Map                                                      | . 46 |

| Figure 10. | Clock Organization                                                                         | . 48 |

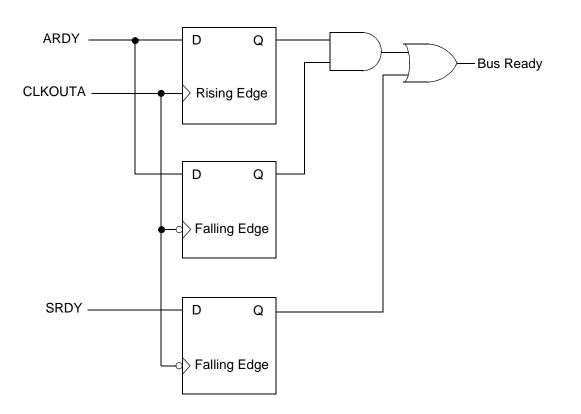

| Figure 11. | ARDY and SRDY Synchronization Logic Diagram                                                | . 49 |

| Figure 12. | Example Memory Maps                                                                        |      |

| Figure 13. | DMA Unit Block Diagram                                                                     |      |

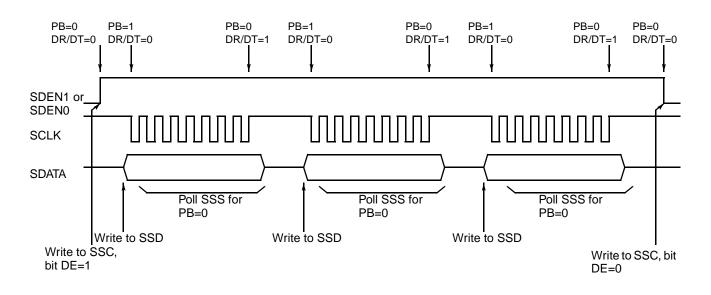

| Figure 14. | Synchronous Serial Interface Multiple Write                                                | . 58 |

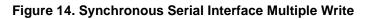

| Figure 15. | Synchronous Serial Interface Multiple Read                                                 | . 58 |

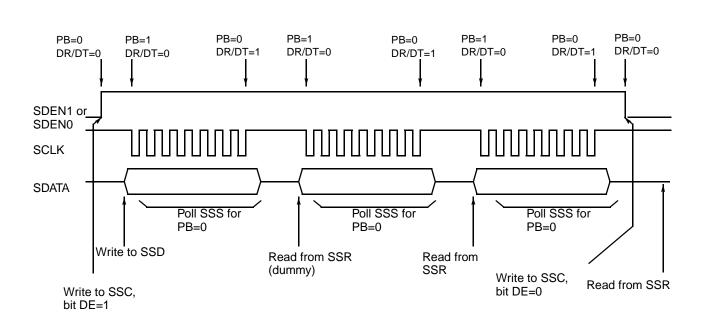

| Figure 16. | Thermal Resistance (°C/Watt)                                                               | . 61 |

| Figure 17. | Thermal Characteristics Equations                                                          |      |

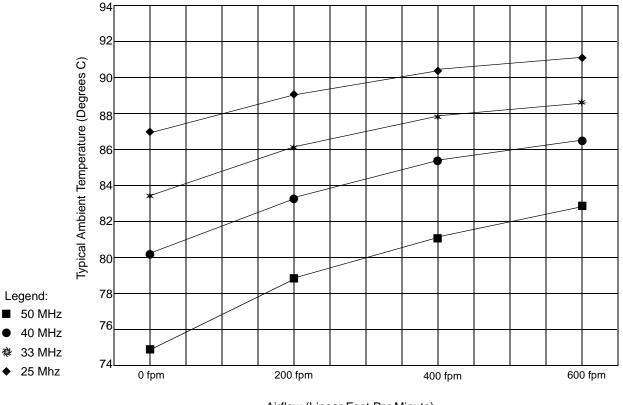

| Figure 18. | Typical Ambient Temperatures for PQFP with Two-Layer Board                                 | . 63 |

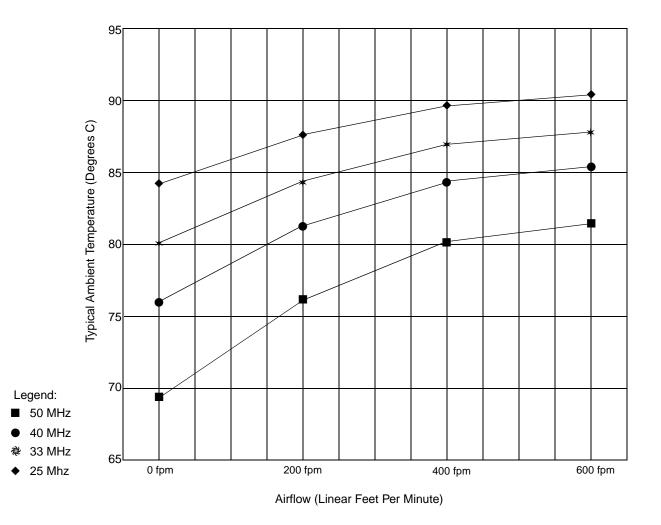

| Figure 19. | Typical Ambient Temperatures for TQFP with Two-Layer Board                                 |      |

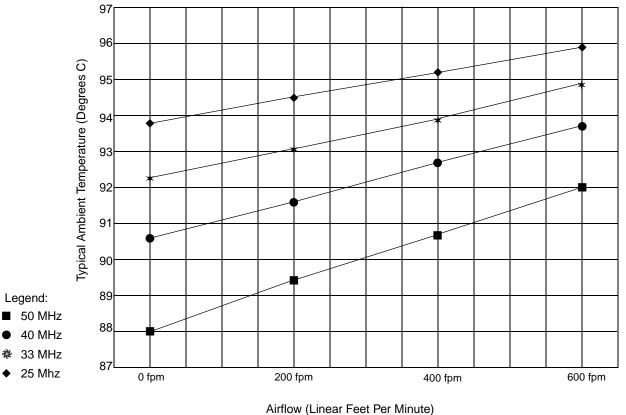

| Figure 20. | Typical Ambient Temperatures for PQFP with Four-Layer to Six-Layer Board                   | . 65 |

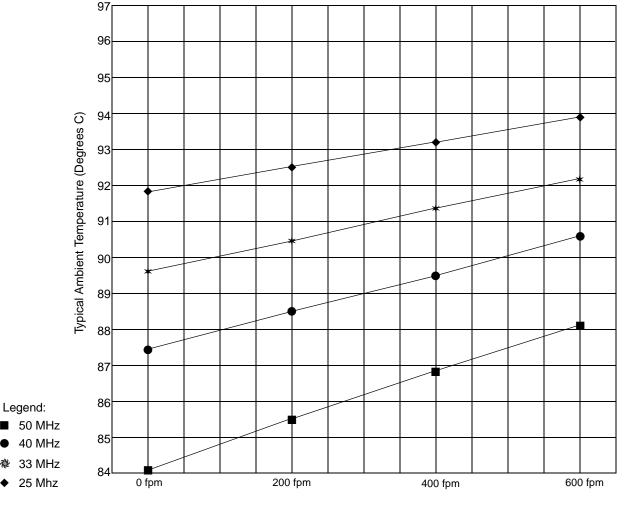

| Figure 21. | Typical Ambient Temperatures for TQFP with Four-Layer to Six-Layer Board                   | . 66 |

## LIST OF TABLES

| Table 1.  | Related AMD Products—E86 <sup>™</sup> Family Devices                     | . 12 |

|-----------|--------------------------------------------------------------------------|------|

| Table 2.  | Data Byte Encoding                                                       |      |

| Table 3.  | Numeric PIO Pin Assignments                                              | . 36 |

| Table 4.  | Alphabetic PIO Pin Assignments                                           | . 36 |

| Table 5.  | Bus Cycle Encoding                                                       | . 37 |

| Table 6.  | Clocking Modes                                                           |      |

| Table 7.  | Segment Register Selection Rules                                         | . 40 |

| Table 8.  | Maximum and Minimum Clock Frequencies                                    | . 44 |

| Table 9.  | Am186ER Microcontroller Maximum DMA Transfer Rates                       | . 55 |

| Table 10. | Thermal Characteristics (°C/Watt)                                        | . 61 |

| Table 11. | Typical Power Consumption Calculation                                    |      |

| Table 12. | Junction Temperature Calculation                                         | . 62 |

| Table 13. | Typical Ambient Temperatures for PQFP with Two-Layer Board               |      |

| Table 14. | Typical Ambient Temperatures for TQFP with Two-Layer Board               | . 64 |

| Table 15. | Typical Ambient Temperatures for PQFP with Four-Layer to Six-Layer Board | . 65 |

| Table 16. | Typical Ambient Temperatures for TQFP with Four-Layer to Six-Layer Board | . 66 |

|           |                                                                          |      |

## **REVISION HISTORY**

| Date                                                                                                                                             | Rev | Description                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feb. 2000                                                                                                                                        | D   | Replaced block diagrams on page 2 and page 3 with updated diagrams showing that the internal data bus interfaces via the BIU and not RAM.                                              |

| Feb. 2000         D         Added new industrial parts for "Ordering Information" on page 4.                                                     |     |                                                                                                                                                                                        |

| Feb. 2000                                                                                                                                        | D   | Updated product listings and customer service matter on page 12 and page 13.                                                                                                           |

| Feb. 2000                                                                                                                                        | D   | Replaced Figure 8 on page 45 (microcontroller oscillator configurations) with updated figure.                                                                                          |

| Feb. 2000                                                                                                                                        | D   | Updated several references to watchdog timer on page 54 to reflect that the WDT is inactive after reset, not active).                                                                  |

| Feb. 2000                                                                                                                                        | D   | Provided a value for the TBD in the table entitled, "DC Characteristics Over Commercial and Industrial Operating Ranges" on page 60.                                                   |

| Feb. 2000                                                                                                                                        | D   | Updated table title and "Min" values for No. 66 in the switching characteristics table, "Read Cycle (40 MHz and 50 MHz)" on page 71.                                                   |

| Feb. 2000                                                                                                                                        | D   | Updated table title and "Max" values for No. 87 in the switching characteristics table, "Write Cycle (40 MHz and 50 MHz)" on page 74.                                                  |

| Feb. 2000                                                                                                                                        | D   | Updated table title and "Min" value for No. 9 (50 MHz) in the switching characteristics table, "Internal RAM Show Read Cycle (40 MHz and 50 MHz)" on page 76.                          |

| Feb. 2000                                                                                                                                        | D   | Updated table title and "Min" values for No. 66 in the switching characteristics table, "PSRAM Read Cycle (40 MHz and 50 MHz)" on page 79.                                             |

| Feb. 2000                                                                                                                                        | D   | Updated table title and "Max" value for No. 68 (40 MHz) in the switching characteristics table,<br>"PSRAM Write Cycle (40 MHz and 50 MHz)" on page 82.                                 |

| Feb. 2000                                                                                                                                        | D   | Updated table title in the switching characteristics table, "PSRAM Refresh Cycle (40 MHz and 50 MHz)" on page 85.                                                                      |

| Feb. 2000                                                                                                                                        | D   | Updated table title in the switching characteristics table, "Software Halt Cycle (40 MHz and 50 MHz)" on page 90.                                                                      |

| Feb. 2000                                                                                                                                        | D   | Updated "Min" and "Max" values in the switching characteristics table, "Clock (33 MHz)" on page 93.                                                                                    |

| Feb. 2000                                                                                                                                        | D   | Updated table title in the switching characteristics table, "Clock (40 MHz and 50 MHz)" on page 94.                                                                                    |

| Feb. 2000       D       Updated table title in the switching characteristics table, "Ready and Peripheral Timing (40 MHz an 50 MHz)" on page 96. |     |                                                                                                                                                                                        |

| Feb. 2000       D       Updated table title in the switching characteristics table, "Reset and Bus Hold (40 MHz and 50 MHz on page 99.           |     | Updated table title in the switching characteristics table, "Reset and Bus Hold (40 MHz and 50 MHz)" on page 99.                                                                       |

| Feb. 2000                                                                                                                                        | D   | Updated table title in the switching characteristics table, "Synchronous Serial Interface (SSI) (40 MHz and 50 MHz)" on page 102.                                                      |

| Feb. 2000                                                                                                                                        | D   | In the table "Switching Characteristics over Commercial and Industrial Operating Ranges Read Cycle (40 MHz and 50 MHz)", row 9, column "50 MHz" - "Min", the "0" is deleted.           |

| Feb. 2000                                                                                                                                        | D   | In the table "Switching Characteristics over Commercial and Industrial Operating Ranges Read Cycle (40 MHz and 50 MHz)", row 66, column "40 MHz" - "Min", the value is changed.        |

| Feb. 2000                                                                                                                                        | D   | In the table "Switching Characteristics over Commercial and Industrial Operating Ranges Read Cycle (40 MHz and 50 MHz)", row 66, column "50 MHz" - "Min", the value is changed.        |

| Feb. 2000                                                                                                                                        | D   | In the table "Switching Characteristics over Commercial and Industrial Operating Ranges PSRAM Write Cycle (40 MHz and 50 MHz)", row 68, column "40 MHz" - "Max", the value is changed. |

| May 2000                                                                                                                                         | D   | Under "Key Features and Benefits" on page 14, in the third bullet "Enhanced functionality," the feature, "a PSRAM controller" was added.                                               |

| May 2000                                                                                                                                         | D   | Under "HOLD" on page 32, the sentence, "A HOLD request is second only to DRAM or PSRAM refresh requests in priority of activity requests received by the processor." is changed.       |

| Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Rev | Description                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | Under "SRDY/PIO6" on page 38, the following sentence was added: "When SRDY is configured as P106, the internal SRDY signal is driven Low."                                                                     |

| May 2000       D       cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Z1/X2 Min" and in the cell of row "Z1/X2 |     | In Table 8, "Maximum and Minimum Clock Frequencies," on page 44, the values are changed in the cell of row "Divide by 2" and column "X1/X2 Min" and in the cell of row "Divide by 2" and column "CLKOUTA Min". |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | In "Switching Characteristics over Commercial and Industrial Operating Ranges" on page 93, Max value in the number "36" row was changed to "33."                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | In "Switching Characteristics over Commercial and Industrial Operating Ranges" on page 94, the value in "40 MHz Max" for row number 36 was changed to "33."                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | In "Synchronous Ready Waveforms" on page 97, the diagram was changed.                                                                                                                                          |

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | In "Asynchronous Ready Waveforms" on page 97, the diagram was changed.                                                                                                                                         |

| May 2000 D In "BHE/ADEN", on page 31, the second paragraph under ADEN was changed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | In "BHE/ADEN", on page 31, the second paragraph under ADEN was changed.                                                                                                                                        |

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | In " $\overline{\text{UZI}}/\overline{\text{CLKSEL}}$ 2/PIO26", on page 38, the paragraph description of $\overline{\text{UZI}}$ was changed.                                                                  |

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | In "Read Cycle Waveforms" on page 72, the UZI line in the diagram was changed.                                                                                                                                 |

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | In "Write Cycle Waveforms" on page 75, the UZI line in the diagram was changed.                                                                                                                                |

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | Added the diagram, Table 11, "ARDY and SRDY Synchronization Logic Diagram," on page 49.                                                                                                                        |

| May 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D   | Added an index.                                                                                                                                                                                                |

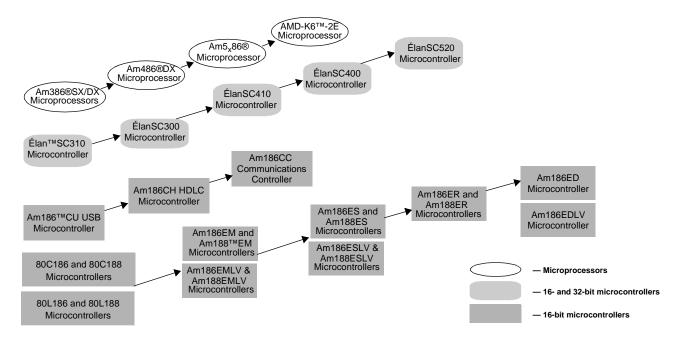

E86<sup>™</sup> FAMILY OF EMBEDDED MICROPROCESSORS AND MICROCONTROLLERS

E86<sup>™</sup> Family of Embedded Microprocessors and Microcontrollers

Table 1. Related AMD Products—E86<sup>™</sup> Family Devices

| Device <sup>1</sup>  | Description                                                                                   |

|----------------------|-----------------------------------------------------------------------------------------------|

| 80C186/80C188        | 16-bit microcontroller                                                                        |

| 80L186/80L188        | Low-voltage, 16-bit microcontroller                                                           |

| Am186™EM/Am188™EM    | High-performance, 16-bit embedded microcontroller                                             |

| Am186EMLV/Am188EMLV  | High-performance, 16-bit embedded microcontroller                                             |

| Am186ES/Am188ES      | High-performance, 16-bit embedded microcontroller                                             |

| Am186ESLV/Am188ESLV  | High-performance, 16-bit embedded microcontroller                                             |

| Am186ED              | High-performance, 80C186- and 80C188-compatible, 16-bit embedded microcontroller with 8- or   |

|                      | 16-bit external data bus                                                                      |

| Am186EDLV            | High-performance, 80C186- and 80C188-compatible, low-voltage, 16-bit embedded                 |

|                      | microcontroller with 8- or 16-bit external data bus                                           |

| Am186ER/Am188ER      | High-performance, low-voltage, 16-bit embedded microcontroller with 32 Kbyte of internal SRAM |

| Am186CC              | High-performance, 16-bit embedded communications controller                                   |

| Am186CH              | High-performance, 16-bit embedded HDLC microcontroller                                        |

| Am186CU              | High-performance, 16-bit embedded USB microcontroller                                         |

| ÉlanSC300            | High-performance, highly integrated, low-voltage, 32-bit embedded microcontroller             |

| ÉlanSC310            | High-performance, single-chip, 32-bit embedded PC/AT-compatible microcontroller               |

| ÉlanSC400            | High-performance, single-chip, low-power, PC/AT-compatible microcontroller                    |

| ÉlanSC410            | High-performance, single-chip, PC/AT-compatible microcontroller                               |

| ÉlanSC520            | High-performance, single-chip, 32-bit embedded microcontroller                                |

| Am386®SX             | High-performance, 32-bit embedded microprocessor with 16-bit external data bus                |

| Am386®DX             | High-performance, 32-bit embedded microprocessor with 32-bit external data bus                |

| Am486®DX             | High-performance, 32-bit embedded microprocessor with 32-bit external data bus                |

| Am5 <sub>x</sub> 86® | High-performance, 32-bit embedded microprocessor with 32-bit external data bus                |

| AMD-K6™-2E           | High-performance, 32-bit embedded microprocessor with 64-bit external data bus                |

|                      | and 3DNow!™ technology                                                                        |

|                      |                                                                                               |

#### Notes:

1. 186 = 16-bit microcontroller and 80C186-compatible (except where noted otherwise); 188 = 16-bit microcontroller with 8-bit external data bus and 80C188-compatible (except where noted otherwise); LV = low voltage

#### **Related Documents**

The following documents provide additional information regarding the Am186ER and Am188ER microcontrollers.

- Am186ER and Am188ER Microcontrollers User's Manual, order #21684

- FusionE86<sup>SM</sup> Catalog, order #19255

- Making the Most of the Am186<sup>™</sup>ER or Am188<sup>™</sup>ER Microcontroller Application Note, order #21046

- Using the 3.3-V Am186<sup>TM</sup>ER or Am188<sup>TM</sup>ER Microcontroller in a 5-V System Application Note, order #21045

- Comparing the Am186<sup>™</sup>EM and Am186ER Microcontrollers Technical Bulletin (Available only at www.amd.com/products/epd/techdocs.)

- The Advantages of Integrated RAM Technical Bulletin (Available only at www.amd.com/products/ epd/techdocs.)

A full description of the Am186ER and Am188ER microcontrollers' registers and instructions is included in the *Am186ER and Am188ER Microcontrollers User's Manual* listed above.

To order literature, contact the nearest AMD sales office or call the literature center at one of the numbers listed on the back cover of this manual. In addition, all these documents are available in PDF form on the AMD web site. To access the AMD home page, go to www.amd.com. Then follow the Embedded Processor link for information about E86 microcontrollers.

#### **Demonstration Board Products**

The SD186ER demonstration board product is a standalone, low-cost evaluation platform for the Am186ER microcontroller.

The SD186ER board demonstrates the basic processor functionality and features of the Am186ER microcontroller and the simplicity of its system design. The SD186ER demonstration board is designed with the Am186/Am188 expansion interface that provides access to the Am186ER microcontroller signals. The 104-pin expansion interface facilitates prototyping by enabling the demonstration board to be used as the minimal system core of a design. Contact your local AMD sales office for more information on demonstration board availability and pricing.

#### **Third-Party Development Support Products**

The FusionE86 Program of Partnerships for Application Solutions provides the customer with an array of products designed to meet critical time-to-market needs. Products and solutions available from the AMD FusionE86 partners include protocol stacks, emulators, hardware and software debuggers, board-level products, and software development tools, among others. In addition, mature development tools and applications for the x86 platform are widely available in the general marketplace.

#### **Customer Service**

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff to answer E86 and Comm86 family hardware and software development questions.

#### Hotline and World Wide Web Support

For answers to technical questions, AMD provides e-mail support as well as a toll-free number for direct access to our corporate applications hotline.

**Note:** The support telephone numbers listed below are subject to change. For current telephone numbers, refer to www.amd.com/support/literature.

The AMD World Wide Web home page provides the latest product information, including technical information and data on upcoming product releases. In addition, EPD CodeKit software on the Web site provides tested source code example applications.

#### **Corporate Applications Hotline**

| (800) 222-9323      | Toll-free for U.S. and Canada |

|---------------------|-------------------------------|

| 44-(0) 1276-803-299 | U.K. and Europe hotline       |

Additional contact information is listed on the back of this datasheet. For technical support questions on all E86 and Comm86 products, send e-mail to **epd.support@amd.com**.

#### World Wide Web Home Page

To access the AMD home page go to: **www.amd.com**. Then follow the **Embedded Processors** link for information about E86 family and Comm86<sup>™</sup> products.

Questions, requests, and input concerning AMD's WWW pages can be sent via e-mail to **webmas-ter@amd.com**.

#### **Documentation and Literature**