# HMS87C5216

# CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER FOR UR(Universal Remocon) & WIRELESS KEYBOARD

#### 1. OVERVIEW

# 1.1 Description

The HMS87C5216 is an advanced CMOS 8-bit microcontroller with 16K bytes of ROM. The device is one of GMS800 family. The MagnaChip Semicon HMS87C5216 is a powerful microcontroller which provides a highly flexible and cost effective solution to many UR & Keyboard applications. The HMS87C5216 provides the following standard features: 16K bytes of ROM, 320 bytes of RAM, 8-bit timer/counter, on-chip oscillator, clock circuitry and RC wake up function. 4 chanel ADC, In addition, the HMS87C5216 Series supports power saving modes to reduce power consumption

| Device name | ROM Size | EPROM Size | RAM Size | Operatind Voltage | Package                                |

|-------------|----------|------------|----------|-------------------|----------------------------------------|

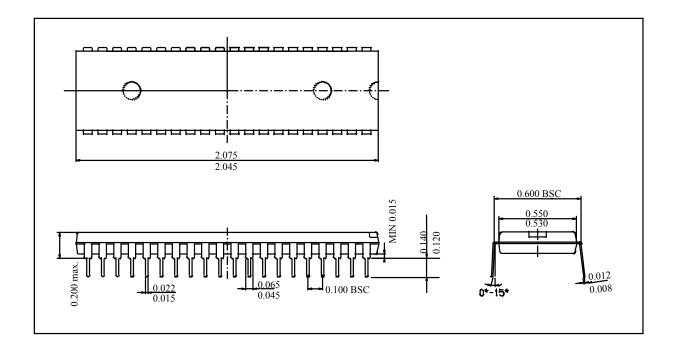

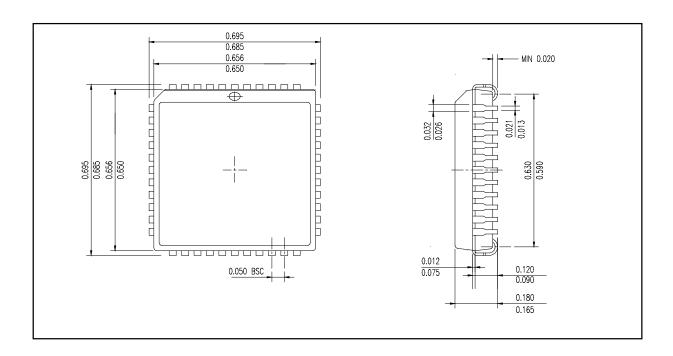

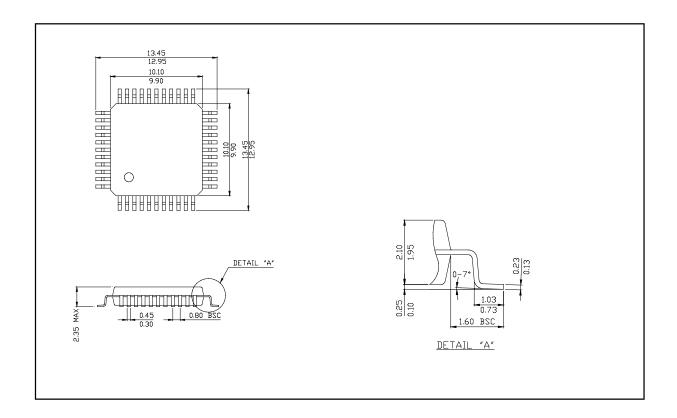

| HMS87C5216  | -        | 16K byte   | 320bytes | 2.0 ~ 5.5V        | 28 SOP<br>40 PDIP<br>44 PLCC<br>44 QFP |

# 1.2 Features

- Instruction Cycle Time:

- 1us at 4MHz

- Programmable I/O pins

|        | 28 PIN | 40 PIN | 44 PIN |

|--------|--------|--------|--------|

| INPUT  | 2      | 2      | 2      |

| OUTPUT | 2      | 2      | 2      |

| I/O    | 22     | 34     | 38     |

- Operating Voltage

- 2.0 ~ 5.5 V @ 4MHz

- Timer

- Timer / Counter ....... 16Bit \* 1ch ...... 16Bit \* 2ch

- Basic Interval Timer ..... 8Bit \* 1ch

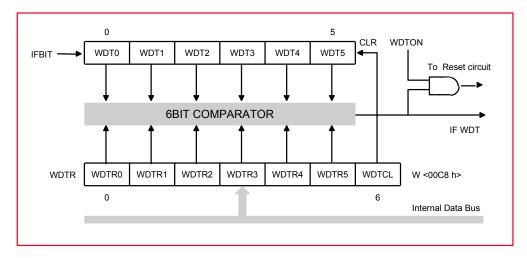

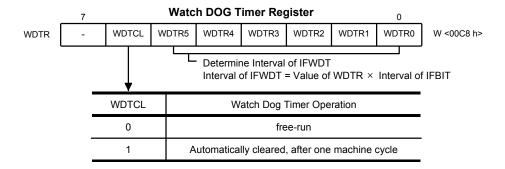

- Watch Dog Timer ...... 6Bit \* 1ch

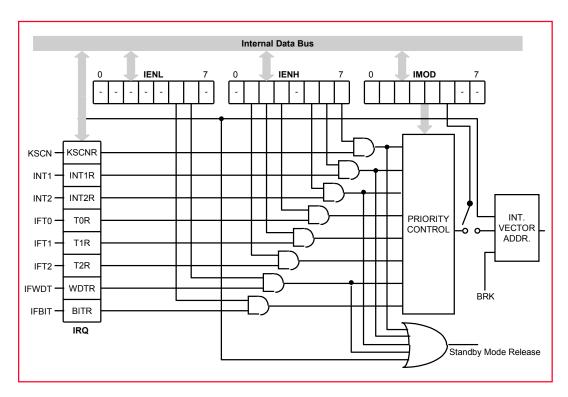

- 8 Interrupt sources

- \* Nested Interrupt control is available.

- External input: 2

- Keyscan input

- Basic Interval Timer

- Watchdog timer

- Timer: 3

- Power On Reset

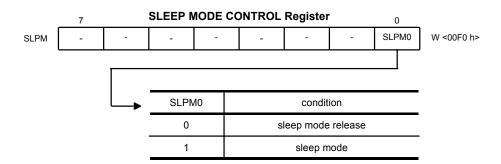

- Power saving Operation Modes

- STOP

- SLEEP

- Low Voltage Detection Circuit

- Watch Dog Timer Auto Start (During 1second after Power on Reset)

- 4 CHANEL ADC

- RC TIMER WAKE UP

# 1.3 Development Tools

The HMS87C5216 and HMS87C5216 are supported by a full-featured macro assembler, an in-circuit emulator CHOICE-  $Dr^{TM}$ .

| In Circuit Emulators | CHOICE-Dr.              |  |

|----------------------|-------------------------|--|

| Assembler            | HME Macro Assembler     |  |

| OTP Writer           | Single Writer : Sigma   |  |

| OTP Writer           | 4-Gang Writer : Dr.Gang |  |

| OTP Devices          | HMS87C5216              |  |

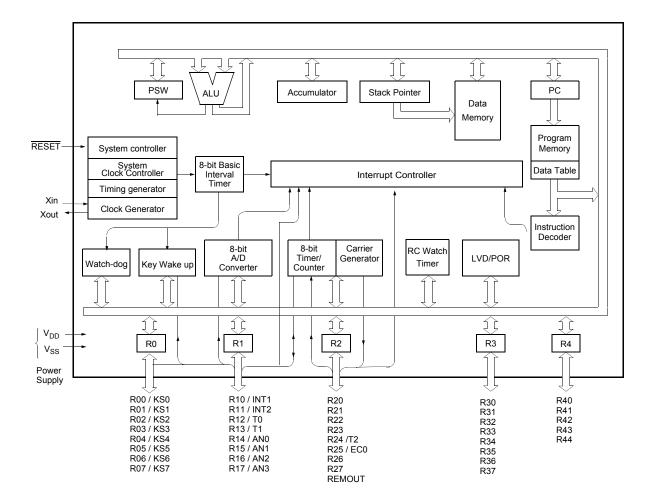

# 2. BLOCK DIAGRAM

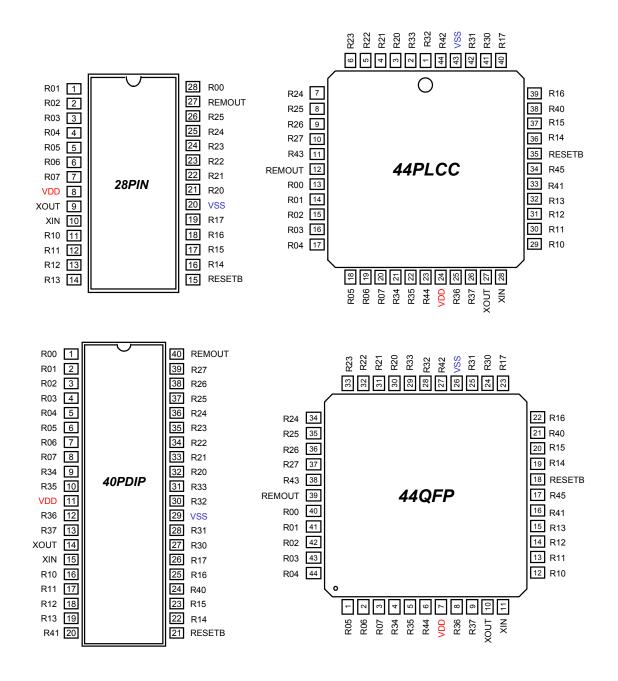

# 3. PIN ASSIGNMENT

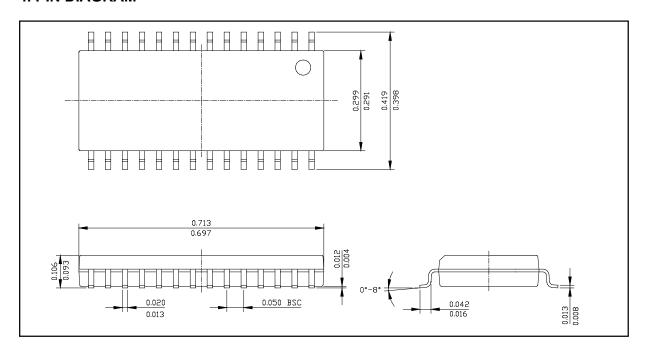

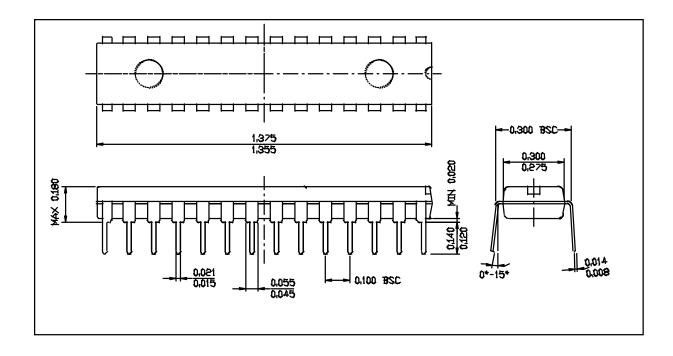

# 4. PIN DIAGRAM

# 5. PIN FUNCTION

V<sub>DD</sub>: Supply voltage.

V<sub>SS</sub>: Circuit ground.

**RESET**: Reset the MCU.

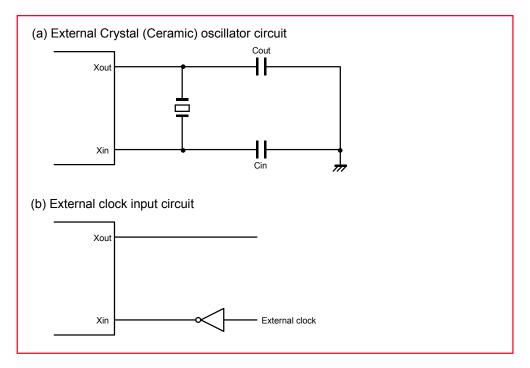

$X_{IN}$ : Input to the inverting oscillator amplifier and input to the internal main clock operating circuit.

**X**<sub>OUT</sub>: Output from the inverting oscillator amplifier.

**R00~R07**: R0 is an 8-bit CMOS bidirectional I/O port. R0 pins 1 or 0 written to the Port Direction Register can be used as outputs or inputs.

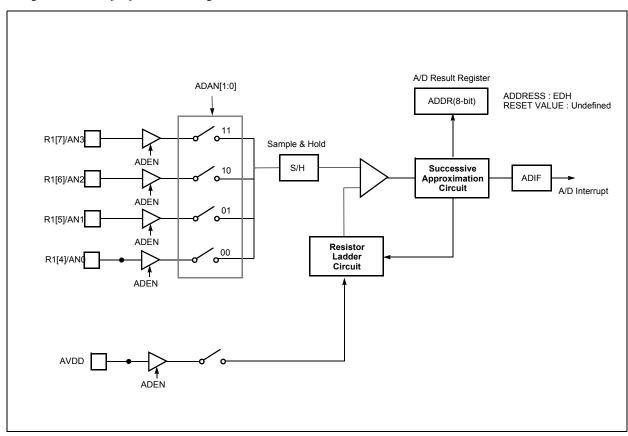

**R10~R17**: R1 is an 8-bit CMOS bidirectional I/O port. R1 pins 1 or 0 written to the Port Direction Register can be used as outputs or inputs.

In addition, R1 serves the functions of the various following special features.

| Port pin | Alternate function                |

|----------|-----------------------------------|

| R10      | INT1 (External Interrupt input 1) |

| R11      | INT2 (External Interrupt input 2) |

| R12      | T0 (Timer / Counter inpit 0)      |

| R13      | T1 (Timer / Counter inpit 1)      |

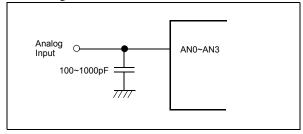

| R14      | AN0 (ADC input 0)                 |

| R15      | AN1 (ADC input 1)                 |

| R16      | AN2 (ADC input 2)                 |

| R17      | AN3 (ADC input 3)                 |

**R20~R22**, **R30~R37**: R2 & R3 is a 8-bit CMOS bidirectional I/O port. Each pins 1 or 0 written to the their Port Direction Register can be used as outputs or inputs.

In addition, R2 serves the functions of the various following special features.

| Port pin | Alternate function           |

|----------|------------------------------|

| R24      | T2 (Timer / Counter inpit 2) |

| R25      | /EC (Event Counter input )   |

**R40~R43**: R4 is 1-bit CMOS bidirectional I/O port. This pin 1 or 0 written to the its Port Direction Register can be used as outputs or inputs.

# 6.

| PIN Name                                                                                                                   | 1/0 | #  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | @Reset      | @STOP                      |

|----------------------------------------------------------------------------------------------------------------------------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------|

| XIN XOUT                                                                                                                   | 1,0 | 2  | Main Clock Input,Output                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Oscillation | L, L                       |

| R00/KS0<br>R01/KS1<br>R02/KS2<br>R03/KS3<br>R04/KS4<br>R05/KS5<br>R06/KS6<br>R07/KS7                                       | 1/0 | 8  | <ul> <li>► Each bit of the port can be individually configured as an input or an output by user software</li> <li>► Push-pull output</li> <li>► CMOS input with pull-up resistor (can be programmable)</li> <li>► Programmable Key Scan Input or Open drain output</li> <li>► Pull-ups are automatically disabled at output mode</li> </ul>                                                                                                                                    | Input       | State of<br>before<br>STOP |

| R10/KS8/INT1<br>R11/KS9/INT2<br>R12/KS10/T0<br>R13/KS11/T1<br>R14/KS12/AN0<br>R15/KS13/AN1<br>R16/KS14/AN2<br>R17/KS15/AN3 | 1/0 | 8  | <ul> <li>► Each bit of the port can be individually configured as an input or an output by user software</li> <li>► Push-pull output</li> <li>► CMOS input with pull-up resistor (can be programmable)</li> <li>► Programmable Key Scan Input or Open drain output</li> <li>► Direct Driving of LED (N-TR)</li> <li>► Pull-ups are automatically disabled at output mode</li> <li>► R1[7:4] is High Driving Capability</li> <li>► R1[7:4] is Schmitt Trigger Input.</li> </ul> | Input       | State of<br>before<br>STOP |

| R2[3:0]<br>R24/T2<br>R25/EC0<br>R2[7:6]<br>R3[7:0]<br>R4[5:0]                                                              | 1/0 | 22 | <ul> <li>► Each bit of the port can be individually configured as an input or an output by user software</li> <li>► Push-pull output</li> <li>► CMOS input with pull-up resistor (can be programmable)</li> <li>► Programmable Open drain output</li> <li>► Direct Driving of LED (N-TR)</li> <li>► Pull-ups are automatically disabled at output mode</li> </ul>                                                                                                              | Input       | State of<br>before<br>STOP |

| RESETB                                                                                                                     | 1   | 1  | Resetb Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | L           | Н                          |

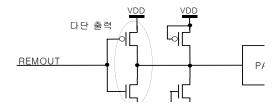

| REMOUT                                                                                                                     | 0   | 1  | Remocon Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | L           | L                          |

| VDD                                                                                                                        | _   | 1  | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDD         | VDD                        |

| VSS                                                                                                                        | -   | 1  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VSS         | VSS                        |

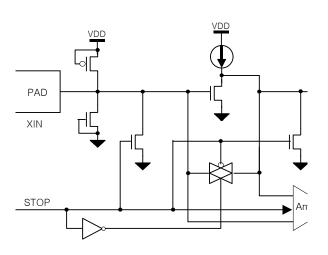

# 7. PORT STRUCTURES

# • RESET

• Xin, Xout

• RA0/EC0

# • RA1/AN1 ~ RA7/AN7

# 8. ELECTRICAL CHARACTERISTICS (HMS87C5216/GMS81C1408)

# 8.1 Absolute Maximum Ratings

| Supply voltage0.                                             | 3 to +7.0 V |

|--------------------------------------------------------------|-------------|

| Storage Temperature40                                        | to +125 ° C |

| aximum current out of V <sub>SS</sub> pin                    | TBD mA      |

| Maximum current into V <sub>DD</sub> pin                     | TBD mA      |

| Maximum current sunk by (I <sub>OL</sub> per I/O Pin)        | TBD mA      |

| Maximum output current sourced by (I <sub>OH</sub> per I/O P | in)         |

| 7 (0111                                                      | TBD mA      |

| Maximum current (ΣI <sub>OL</sub> )                          | TBDmA       |

| Maximum current (ΣI <sub>OH</sub> )                          | TBDmA       |

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 8.2 Recommended Operating Conditions

| Down works w          | Symbol Condition |                           | Specifications | 11:4 |      |

|-----------------------|------------------|---------------------------|----------------|------|------|

| Parameter             | Symbol           | Condition                 | Min.           | Max. | Unit |

| Supply Voltage        | $V_{DD}$         | f <sub>XIN</sub> =4MHz    | 2.0            | 5.5  | V    |

| Operating Frequency   | f <sub>XIN</sub> | V <sub>DD</sub> =2.0~5.5V | 1              | 4    | MHz  |

| Operating Temperature | T <sub>OPR</sub> | V <sub>DD</sub> =2.0~5.5V | -20            | 85   | °C   |

# 8.3 A/D Converter Characteristics

$(T_A=25^{\circ}C, V_{SS}=0V, V_{DD}=3.072V @f_{XIN}=4MHz)$

| Power-ster.                             | Cumbal            | Condition              | Sı                   | l lmi4 |                      |      |

|-----------------------------------------|-------------------|------------------------|----------------------|--------|----------------------|------|

| Parameter                               | Symbol            | Condition              | Min.                 | Тур.   | Max.                 | Unit |

| Analog Input Voltage Range              | V <sub>AIN</sub>  | -                      | V <sub>SS-</sub> 0.3 | -      | V <sub>DD</sub> +0.3 | ٧    |

| Current Following Between AVdd and AVss | IAVdd             | -                      | -                    | -      | 200                  | uA   |

| Overall Accuracy                        | N <sub>ACC</sub>  | -                      | -                    | ±1.0   | ±2.0                 | LSB  |

| Non-Linearity Error                     | N <sub>NLE</sub>  | -                      | -                    | ±1.0   | ±2.0                 | LSB  |

| Differential Non-Linearity Error        | N <sub>DNLE</sub> | -                      | -                    | ±1.0   | ±2.0                 | LSB  |

| Zero Offset Error                       | N <sub>ZOE</sub>  |                        | -                    | ±0.5   | ±1.5                 | LSB  |

| Full Scale Error                        | N <sub>FSE</sub>  |                        | -                    | ±0.25  | ±0.5                 | LSB  |

| Gain Error                              | N <sub>NLE</sub>  |                        | -                    | ±1.0   | ±1.5                 | LSB  |

| Conversion Time                         | T <sub>CONV</sub> | f <sub>XIN</sub> =4MHz | -                    | ı      | 30                   | uS   |

# 8.4 DC Electrical Characteristics

$(T_A = -20 \sim 85^{\circ} \text{C for HMS87C5216/1408 or } T_A = -40 \sim 85^{\circ} \text{C for HMS87C5216E/1408E}, V_{DD} = 2.2 \sim 5.5 \text{V}, V_{SS} = 0 \text{V}),$

| Doromotor          | Symbol Pin       |                         | Condition | Specifications      |      |          | l lmi4 |

|--------------------|------------------|-------------------------|-----------|---------------------|------|----------|--------|

| Parameter          | Symbol           | FIII                    | Condition | Min.                | Тур. | Max.     | Unit   |

| Input High Voltage | V <sub>IH1</sub> | X <sub>IN</sub> , RESET |           | 0.8 V <sub>DD</sub> | -    | $V_{DD}$ | V      |

| Damamatan                      | 0                  | Pin                                 | O a sa aliti a sa                             | Sp                 |      |                    |      |

|--------------------------------|--------------------|-------------------------------------|-----------------------------------------------|--------------------|------|--------------------|------|

| Parameter                      | Symbol Pin         |                                     | Condition                                     | Min.               | Тур. | Max.               | Unit |

| Input High Voltage             | V <sub>IH1</sub>   | RESET,XIN,INT1,IN<br>T2,EC0,R1<7:4> |                                               | 0.8V <sub>DD</sub> | -    | V <sub>DD</sub>    | V    |

| , , ,                          | V <sub>IH2</sub>   | R0,R1,R2,R3,R4                      |                                               | 0.7V <sub>DD</sub> | -    | V <sub>DD</sub>    | V    |

| Input Low Voltage              | V <sub>IL1</sub>   | RESET,XIN,INT1,IN<br>T2,EC0,R1<7:4> |                                               | 0                  | -    | 0.2V <sub>DD</sub> | ٧    |

| mpar = o managa                | V <sub>IL2</sub>   | R0,R1,R2,R3,R4                      |                                               | 0                  | -    | 0.3V <sub>DD</sub> | V    |

| Input High<br>Leakage Current  | I <sub>IH</sub>    | R0,R1,R2,R3,R4<br>RESETB            | V <sub>IH</sub> =VDD                          | -                  | -    | 1.0                | μА   |

| Input Low<br>Leakage Current   | I <sub>IL</sub>    | R0,R1,R2,R3,R4                      | V <sub>IL</sub> =0V                           | -                  | -    | -1.0               | μΑ   |

|                                | V <sub>OH1</sub>   | R0,R1<3:0>,R2,R3,<br>R4             | loh1=-0.8mA,VDD=3V                            | VDD-0.4            | -    | -                  | V    |

| Output High Voltage            | V <sub>OH2</sub>   | R1<7:0>,                            | loh2=-2.0mA,VDD=3V                            | VDD-0.4            | -    | -                  | V    |

|                                | V <sub>OH3</sub>   | XOUT                                | Ioh3=-50uA,VDD=3V                             | VDD-0.5            | -    | -                  | V    |

| Output Low Voltage             | V <sub>OL1</sub>   | R0,R1<3:0>,R2,R3,<br>R4             | I <sub>OL</sub> =5mA,V <sub>DD</sub> =3V      | -                  | -    | 0.8                | V    |

|                                | V <sub>OL2</sub>   | XOUT                                | I <sub>OL</sub> =50uA,V <sub>DD</sub> =3V     | -                  | -    | 0.5                | V    |

| Output High<br>Leakage Current | I <sub>IOHL</sub>  | R0,R1,R2,R3,R4                      | V <sub>OH</sub> =VDD                          | -                  | -    | 1.0                | μА   |

| Output Low<br>Leakage Current  | I <sub>IOLL</sub>  | R0,R1,R2,R3,R4                      | V <sub>OL</sub> =0V                           | -                  | -    | -1.0               | μА   |

| Output High Current            | I <sub>OH</sub>    | REMOUT                              | VDD=3V,VOH=2.0V                               | -20                | -    | -5                 | mA   |

| Output Low Current             | I <sub>OL</sub>    | REMOUT                              | VDD=3V,VOL=1.0V                               | -0.5               | -    | 3                  | mA   |

| Input Pull-up                  | I <sub>P</sub>     | R0,R1,R2,R3,R4<br>RESETB            | V <sub>DD</sub> =3V                           | 50                 | 100  | 200                | κ    |

| Hysteresis                     | V <sub>T</sub>     | Hysteresis Input <sup>1</sup>       | V <sub>DD</sub> =5V                           | 0.5                | -    | -                  | V    |

| Feed Back Resistor             | RF!                | Main OSC Feedback<br>Resistor       | V <sub>DD</sub> =3.0V, f <sub>XIN</sub> =4MHz | 0.2                | -    | 1.0                |      |

|                                | 1                  | Active Mede                         | V <sub>DD</sub> =4.0V                         | -                  | 4.0  | 10                 | mA   |

|                                | I <sub>DD</sub>    | Active Mode                         | V <sub>DD</sub> =2.0V                         | -                  | 2.4  | 6                  | mA   |

| Supply Currnet                 | I <sub>sleep</sub> | Sleep Mode                          | V <sub>DD</sub> =4.0V                         | -                  | 2.0  | 3.0                | mA   |

| Cuppiy Culliet                 | 'sieep             | Cicch Mode                          | V <sub>DD</sub> =2.0V                         | -                  | 1.0  | 2.0                | mA   |

|                                | I <sub>stop</sub>  | Stop Mode,Osc Stop                  | V <sub>DD</sub> =4.0V                         | -                  | 5.0  | 30                 | μΑ   |

|                                | Stop               | City mode, occ otop                 | V <sub>DD</sub> =2.0V                         | -                  | 3.0  | 25                 | μΑ   |

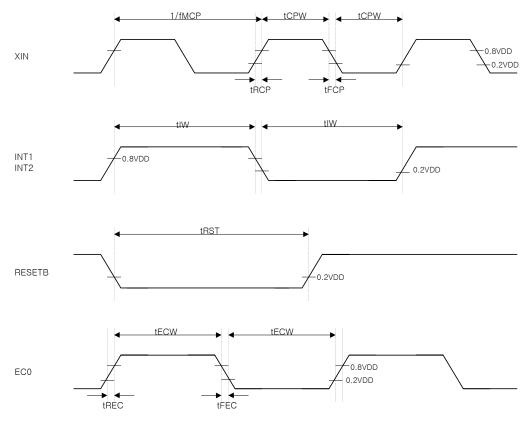

# 8.5 AC Characteristics

$(T_A = -20 \sim 85^{\circ} \text{ C for HMS87C5216/1408 or } T_A = -40 \sim 85^{\circ} \text{ C for HMS87C5216E/1408E}, V_{DD} = 5V \pm 10\%, V_{SS} = 0V)$

| D                                         | Obl                                | Di                                 | S    | 11:4 |      |                  |

|-------------------------------------------|------------------------------------|------------------------------------|------|------|------|------------------|

| Parameter                                 | Symbol                             | Pins                               | Min. | Тур. | Max. | Unit             |

| Operating Frequency                       | f <sub>MCP</sub>                   | X <sub>IN</sub>                    | 1    | -    | 4    | MHz              |

| Systemp Clock Cycle Time                  | t <sub>SYS</sub>                   | -                                  | 0.5  | -    | 2.0  | uS               |

| Oscillation Stabilizing<br>Time(4MHz)     | t <sub>MST!</sub>                  | X <sub>IN</sub> , X <sub>OUT</sub> | -    | -    | 20   | mS               |

| External Clock "H" or "L" Pulse Width     | t <sub>CPW</sub>                   | X <sub>IN</sub>                    | 80   |      |      | nS               |

| External Clock Transition Time            | t <sub>RCP</sub> ,t <sub>FCP</sub> | X <sub>IN</sub>                    | -    | -    | 20   | nS               |

| Interrupt Input Pulse Width               | t <sub>IVV</sub>                   | INT1,INT2                          | 2    | -    |      | t <sub>SYS</sub> |

| RESETB Input Pulse "L" Width              | t <sub>RST</sub>                   | RESETB                             | 8    | -    | -    | t <sub>SYS</sub> |

| Event Couter Input "H" or "L" Pulse Width | t <sub>TCW</sub>                   | ECo                                | 2    | -    | -    | t <sub>SYS</sub> |

| Event Couter Transition Time              | t <sub>REC</sub> ,t <sub>FEC</sub> | ECo                                | 0    | -    | 20   | nS               |

Figure 8-1 Timing Chart

#### 9. MEMORY ORGANIZATION

The HMS87C5216 have separate address spaces for Program memory and Data Memory. Program memory can only be read, not written to. It can be up to 16K bytes of Program memory.

Data memory can be read and written to up to 320 bytes including the stack area.

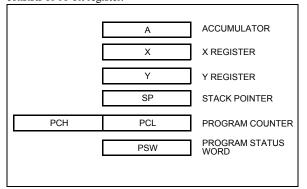

#### 9.1 Registers

This device has six registers that are the Program Counter (PC), a Accumulator (A), two index registers (X, Y), the Stack Pointer (SP), and the Program Status Word (PSW). The Program Counter consists of 16-bit register.

Figure 9-1 Configuration of Registers

**Accumulator:** The Accumulator is the 8-bit general purpose register, used for data operation such as transfer, temporary saving, and conditional judgement, etc.

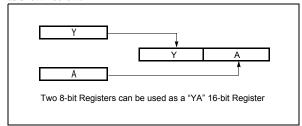

The Accumulator can be used as a 16-bit register with Y Register as shown below.

Figure 9-2 Configuration of YA 16-bit Register

X, Y Registers: In the addressing mode which uses these index registers, the register contents are added to the specified address, which becomes the actual address. These modes are extremely effective for referencing subroutine tables and memory tables. The index registers also have increment, decrement, comparison and data transfer functions, and they can be used as simple accumulators.

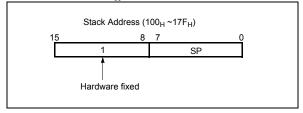

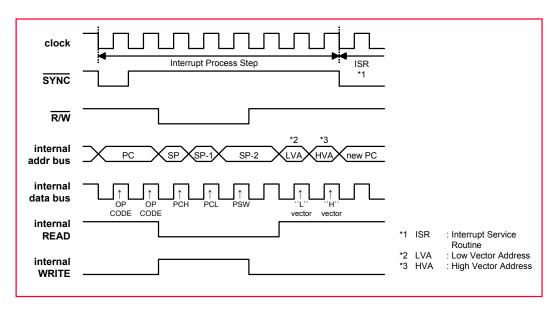

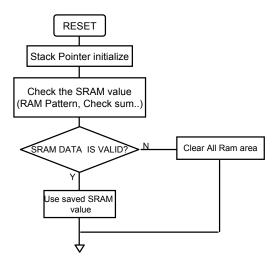

**Stack Pointer**: The Stack Pointer is an 8-bit register used for occurrence interrupts and calling out subroutines. Stack Pointer

identifies the location in the stack to be accessed (save or restore).

Generally, SP is automatically updated when a subroutine call is executed or an interrupt is accepted. However, if it is used in excess of the stack area permitted by the data memory allocating configuration, the user-processed data may be lost.

The stack can be located at any position within  $100_{\rm H}$  to  $17F_{\rm H}$  of the internal data memory. The SP is not initialized by hardware, requiring to write the initial value (the location with which the use of the stack starts) by using the initialization routine. Normally, the initial value of "17F $_{\rm H}$ " is used.

**Note:** The Stack Pointer must be initialized by software because its value is undefined after RESET.

Example: To initialize the SP LDX #07FH TXSP ; SP  $\leftarrow$ 7F<sub>H</sub>

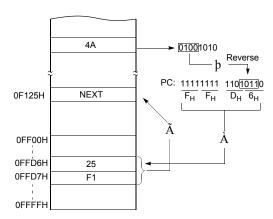

**Program Counter**: The Program Counter is a 16-bit wide which consists of two 8-bit registers, PCH and PCL. This counter indicates the address of the next instruction to be executed. In reset state, the program counter has reset routine address ( $PC_H:0FF_H$ ,  $PC_L:0FE_H$ ).

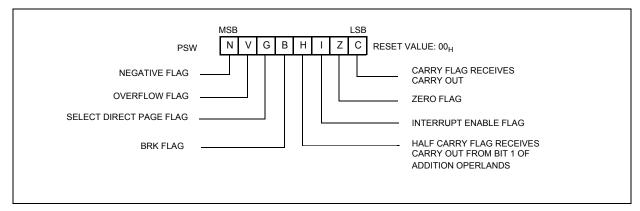

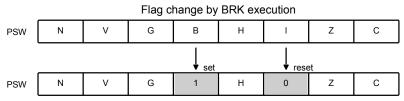

**Program Status Word**: The Program Status Word (PSW) contains several bits that reflect the current state of the CPU. The PSW is described in Figure 9-3. It contains the Negative flag, the Overflow flag, the Break flag the Half Carry (for BCD operation), the Interrupt enable flag, the Zero flag, and the Carry flag.

[Carry flag C]

This flag stores any carry or borrow from the ALU of CPU after an arithmetic operation and is also changed by the Shift Instruction or Rotate Instruction.

[Zero flag Z]

This flag is set when the result of an arithmetic operation or data transfer is "0" and is cleared by any other result.

Figure 9-3 PSW (Program Status Word) Register

#### [Interrupt disable flag I]

This flag enables/disables all interrupts except interrupt caused by Reset or software BRK instruction. All interrupts are disabled when cleared to "0". This flag immediately becomes "0" when an interrupt is served. It is set by the EI instruction and cleared by the DI instruction.

#### [Half carry flag H]

After operation, this is set when there is a carry from bit 3 of ALU or there is no borrow from bit 4 of ALU. This bit can not be set or cleared except CLRV instruction with Overflow flag (V).

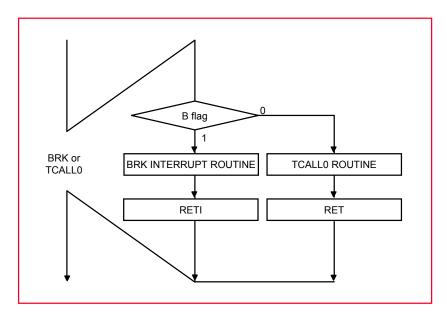

# [Break flag B]

This flag is set by software BRK instruction to distinguish BRK from TCALL instruction with the same vector address.

#### [Overflow flag V]

This flag is set to "1" when an overflow occurs as the result of an arithmetic operation involving signs. An overflow occurs when the result of an addition or subtraction exceeds  $\pm 127(7F_H)$  or  $\pm 128(80_H)$ . The CLRV instruction clears the overflow flag. There is no set instruction. When the BIT instruction is executed, bit 6 of memory is copied to this flag.

#### [Negative flag N]

This flag is set to match the sign bit (bit 7) status of the result of a data or arithmetic operation. When the BIT instruction is executed, bit 7 of memory is copied to this flag.

# [Direct page flag G]

This flag assigns RAM page for direct addressing mode. In the direct addressing mode, addressing area is from zero page 00 to FF when this flag is 0. If it is set to 1, addressing area is 1 page. It is set by instruction and cleared by CLRG.

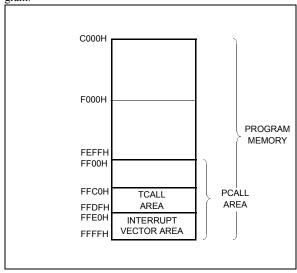

#### 9.2 Program Memory

A 16-bit program counter is capable of addressing up to 64K bytes, but these devices have 16K bytes program memory space only physically implemented. Accessing a location above  ${\rm FFFF}_{\rm H}$  will cause a wrap-around to  $0000_{\rm H}$ .

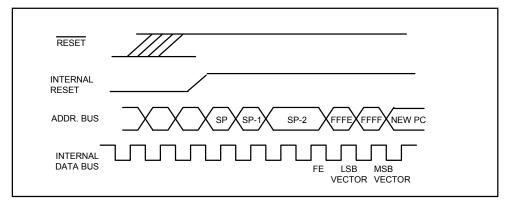

Figure 9-4, shows a map of Program Memory. After reset, the CPU begins execution from reset vector which is stored in address  $FFFE_H$  and  $FFFF_H$  as shown in Figure 9-5.

As shown in Figure 9-4, each area is assigned a fixed location in Program Memory. Program Memory area contains the user program

Figure 9-4 Program Memory Map

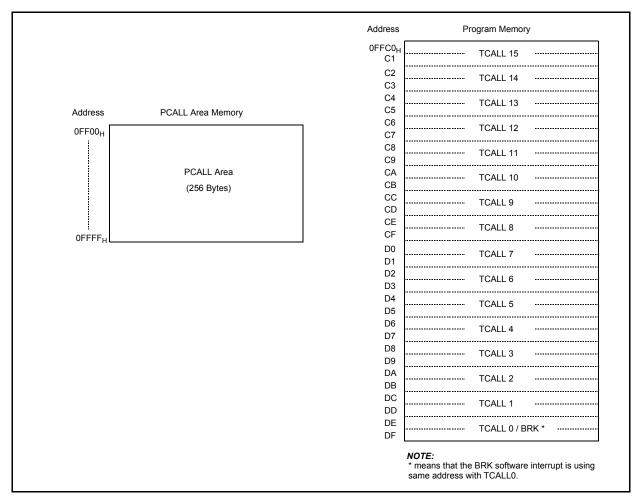

Page Call (PCALL) area contains subroutine program to reduce program byte length by using 2 bytes PCALL instead of 3 bytes CALL instruction. If it is frequently called, it is more useful to save program byte length.

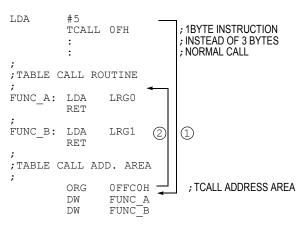

Table Call (TCALL) causes the CPU to jump to each TCALL address, where it commences the execution of the service routine. The Table Call service area spaces 2-byte for every TCALL:  $0 FFCO_H$  for TCALL15,  $0 FFCO_H$  for TCALL14, etc., as shown in Figure 9-6.

Example: Usage of TCALL

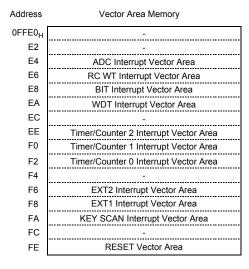

The interrupt causes the CPU to jump to specific location, where it commences the execution of the service routine. The External interrupt 0, for example, is assigned to location 0FFFA $_H$ . The interrupt service locations spaces 2-byte interval: 0FFF8 $_H$  and 0FFF9 $_H$  for External Interrupt 1, 0FFFA $_H$  and 0FFFB $_H$  for External Interrupt 0, etc.

As for the area from  $0 FF00_H$  to  $0 FFFF_H$ , if any area of them is not going to be used, its service location is available as general purpose Program Memory.

NOTE:

"-" means reserved area.

Figure 9-5 Interrupt Vector Area

Figure 9-6 PCALL and TCALL Memory Area

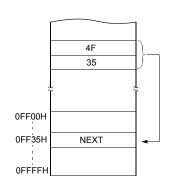

# **PCALL**→rel

4F35 PCALL 35H

#### $TCALL \rightarrow n$

4A TCALL 4

SEP. 2004 Ver 1.01

Example: The usage software example of Vector address and the initialize part.

```

ORG

OFFEOH

NOT_USED; (OFFEO)

NOT_USED; (OFFE2)

ADC_INT; (OFFE4) A/D Interface

DW

DW

DW

RC WT_INT; (OFFE6) RC WAKE UP Timer

DW

RC WT INT; (OFFE6) RC WAKE

BIT INT; (OFFE8) BIT TIMEY

WDT_INT; (OFFEA) WDT

NOT_USED; (OFFEC)

TMR2 INT; (OFFEE) TIMEY-2

TMR1_INT; (OFFF0) TIMEY-1

TMR0 INT; (OFFF2) TIMEY-0

NOT_USED; (OFFF4)

DW

DW

DW

DW

DW

DW

EXT2_INT; (0FFF6) External2

EXT1_INT; (0FFF8) External1

DW

DW

KEY_SCAN; (OFFFA) Key Scan

DW

NOT USED; (0FFFC)

RESET; (0FFFE) Reset

DW

DW

ORG OF000H

MAIN PROGRAM *

RESET: DI

;Disable All Interrupts

#0

LDX

RAM CLR: LDA

#0; RAM Clear(!0000H->!00BFH)

STA

{X}+

CMPX #0C0H

BNE

RAM CLR

#07FH;Stack Pointer Initialize

LDX

TXSP

CALL INITIAL;

LDM

R1, #0;Normal Port A

LDM

R1DD, #1000 0010B; Normal Port Direction

LDM

R2, #0; Normal Port B

R2DD, #1000_0010B; Normal Port Direction

LDM

```

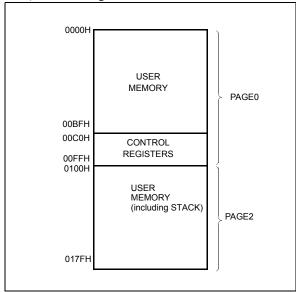

#### 9.3 Data Memory

Figure 9-7 shows the internal Data Memory space available. Data Memory is divided into two groups, a user RAM (including Stack) and control registers.

Figure 9-7 Data Memory Map

#### **User Memory**

The HMS87C5216 has  $330 \times 8$  bits for the user memory (RAM).

#### **Control Registers**

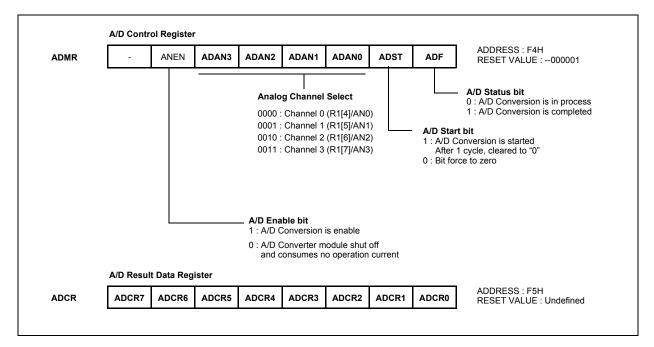

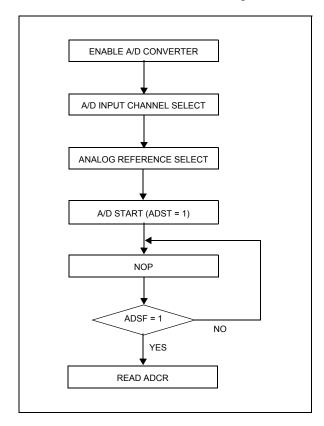

The control registers are used by the CPU and Peripheral function blocks for controlling the desired operation of the device. Therefore these registers contain control and status bits for the interrupt system, the timer/ counters, analog to digital converters and I/O ports. The control registers are in address range of  $0\text{CO}_H$  to  $0\text{FF}_H$ .

Note that unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

More detailed informations of each register are explained in each peripheral section.

**Note:** Write only registers can not be accessed by bit manipulation instruction. Do not use read-modify-write instruction. Use byte manipulation instruction.

Example; To write at CKCTLR

LDM CKCTLR, #09H; Divide ratio ÷16

Note: Several names are given at same address. Refer to-

| Address                                                                                              | Symbol                                                                 | R/W                                                                    | RESET<br>Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Addressing mode                                                                                          |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Address                                                                                              | Symbol                                                                 | R/W                                                                    | RESET<br>Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Addressing mode                                                                                          |

| 0C0H<br>0C1H<br>0C2H<br>0C3H<br>0C4H<br>0C5H<br>0C6H<br>0C7H<br>0C7H<br>0C8H<br>0C9H<br>0CAH<br>0CBH | R0 R0DR R1 R1DR R2 R2DR TMR1 CKCTLR BITR WDTR PSR RCWTR IESR IENL IRQL | R/W<br>W<br>R/W<br>W<br>W<br>W<br>W<br>W<br>W<br>W<br>W<br>W<br>W<br>W | Undefined 0000_0000 Undefined 0000_0000 Undefined 0000_000011_0111 0000_0000000_111100_0000000_000000_000000_000000_000000_000000_000000_000000_000000_000000_000000_000000_000000_000000_000000_0000000_0000000_0000000_0000000_0000000_0000000_0000000_0000000_0000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_0000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_000000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_000000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_000000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000 | byte, bit <sup>1</sup> byte <sup>2</sup> byte, bit byte byte, bit byte byte byte byte byte byte byte byt |

| 0CEH<br>0CFH<br>0D0H<br>0D1H                                                                         | IENH<br>IRQH<br>TM0<br>TM1                                             | R/W<br>R/W<br>R/W                                                      | 000000-<br>000000-<br>0000_0000<br>0000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | byte,bit<br>byte, bit<br>byte, bit                                                                       |

| 0D2H<br>0D3H<br>0D4H<br>0D5H<br>0D5H<br>0D6H<br>0D6H                                                 | TM2 T0HMD T0HLD T0MC T0LMD T0LC T0LLD                                  | R/W<br>W<br>R<br>W<br>R<br>W                                           | 0_0000<br>Undefined<br>Undefined<br>0000_0000<br>Undefined<br>0000_0000<br>Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | byte, bit byte byte byte byte byte byte byte byt                                                         |

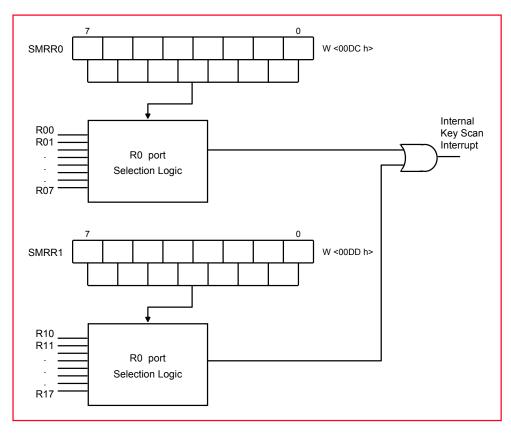

| OD7H OD8H OD8H OD9H OD9H ODAH ODCH ODDH ODEH ODFH                                                    | T1HD T1C T1LD T2C T2D TM01 KSR0 KSR1 R10D R2OD                         | W<br>R<br>W<br>R<br>W<br>W<br>W<br>W                                   | Undefined 0000_0000 Undefined 0000_0000 Undefined 0000_0000 0000_0000 0000_0000 0000_0000 0000_0000 0000_0000 0000 0000 0000 0000 0000 0000 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | byte byte byte byte byte byte byte byte                                                                  |

| 0E0H<br>0E1H<br>0E4H<br>0E5H<br>0E6H<br>0E7H<br>0E8H<br>0EEH                                         | R3OD<br>R4OD<br>R0OD<br>R3<br>R3DR<br>R4<br>R4DR<br>TMR2<br>LVDR       | W<br>W<br>R/W<br>W<br>R/W<br>R<br>R                                    | 0000_0000<br>00_0000<br>0000_0000<br>Undefined<br>0000_0000<br>Undefined<br>00_0000<br>0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | byte byte byte,bit byte,bit byte,bit byte,bit byte byte                                                  |

**Table 9-1 Control Registers**

|      | ·    |     |           |           |

|------|------|-----|-----------|-----------|

| 0F0H | SMR  | W   | 0         | byte      |

| 0F4H | ADMR | R/W | -000 0001 | byte, bit |

| 0F5H | ADDR | R   | Undefined | byte      |

| 0F6H | KRL0 | W   | 0000 0000 | byte      |

| 0F7H | KRL1 | W   | 0000 0000 | byte      |

| 0F8H | R0PU | W   | 0000 0000 | byte      |

| 0F9H | R1PU | W   | 0000 0000 | byte      |

| 0FAH | R2PU | W   | 0000 0000 | byte      |

| 0FBH | R3PU | W   | 0000 0000 | byte      |

| 0FCH | R4PU | W   | 00_0000   | byte      |

**Table 9-1 Control Registers**

- 1. "byte, bit" means that register can be addressed by not only bit but byte manipulation instruction.

- "byte" means that register can be addressed by only byte manipulation instruction. On the other hand, do not use any read-modify-write instruction such as bit manipulation for clearing bit.

below table.

#### Stack Area

The stack provides the area where the return address is saved before a jump is performed during the processing routine at the execution of a subroutine call instruction or the acceptance of an interrupt.

When returning from the processing routine, executing the subroutine return instruction [RET] restores the contents of the program counter from the stack; executing the interrupt return instruction [RETI] restores the contents of the program counter and flags.

The save/restore locations in the stack are determined by the stack pointed (SP). The SP is automatically decreased after the saving, and increased before the restoring. This means the value of the SP indicates the stack location number for the next save.

#### 9.4 Addressing Mode

The HMS87C5216 and GMS81C1408 uses six addressing modes;

- · Register addressing

- · Immediate addressing

- · Direct page addressing

- · Absolute addressing

- · Indexed addressing

- · Register-indirect addressing

# (1) Register Addressing

Register addressing accesses the A, X, Y, C and PSW.

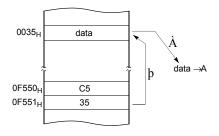

# (2) Immediate Addressing →#imm

In this mode, second byte (operand) is accessed as a data immediately.

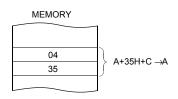

#### Example:

0435 ADC #35H

E45535 LDM 35H, #55H

# (3) Direct Page Addressing →dp

In this mode, a address is specified within direct page.

#### Example;

C535 LDA 35H ;A ←RAM[35H]

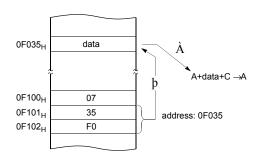

# (4) Absolute Addressing →!abs

Absolute addressing sets corresponding memory data to Data, i.e. second byte(Operand I) of command becomes lower level address and third byte (Operand II) becomes upper level address. With 3 bytes command, it is possible to access to whole memory area.

$\label{eq:add_add_add_add_add_add_add_add} ADC, AND, CMP, CMPX, CMPY, EOR, LDA, LDX, LDY, OR, SBC, STA, STX, STY$

#### Example;

0735F0 ADC !0F035H ;A ←ROM[0F035H]

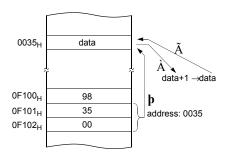

The operation within data memory (RAM) ASL, BIT, DEC, INC, LSR, ROL, ROR

Example; Addressing accesses the address 0135<sub>H</sub>.

983500 INC !0035H ;A ←RAM[035H]

# (5) Indexed Addressing

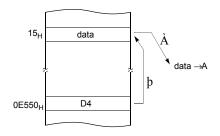

# X indexed direct page (no offset) $\rightarrow$ {X}

In this mode, a address is specified by the X register.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA, XMA

Example; X=15<sub>H</sub>

D4 LDA  $\{X\}$ ; ACC $\leftarrow$ RAM[X].

# X indexed direct page, auto increment→{X}+

In this mode, a address is specified within direct page by the X register and the content of X is increased by 1.

LDA, STA

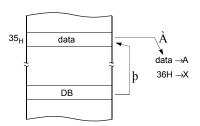

Example; X=35<sub>H</sub>

DB LDA {X}+

# X indexed direct page (8 bit offset) →dp+X

This address value is the second byte (Operand) of command plus the data of X-register. And it assigns the memory in Direct page.

ADC, AND, CMP, EOR, LDA, LDY, OR, SBC, STA STY, XMA, ASL, DEC, INC, LSR, ROL, ROR

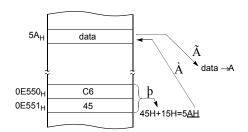

Example; X=015<sub>H</sub>

C645 LDA 45H+X

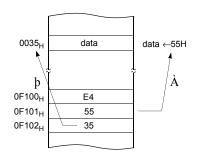

#### Y indexed direct page (8 bit offset) →dp+Y

This address value is the second byte (Operand) of command plus the data of Y-register, which assigns Memory in Direct page.

This is same with above (2). Use Y register instead of X.

#### Y indexed absolute →abs+Y

Sets the value of 16-bit absolute address plus Y-register data as Memory. This addressing mode can specify memory in whole area

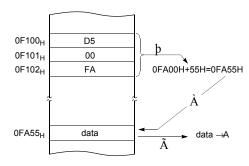

Example; Y=55<sub>H</sub>

D500FA LDA !OFA00H+Y

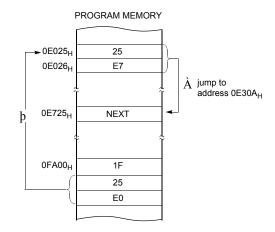

#### (6) Indirect Addressing

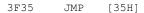

# Direct page indirect →[dp]

Assigns data address to use for accomplishing command which sets memory data(or pair memory) by Operand.

Also index can be used with Index register X,Y.

JMP, CALL

Example;

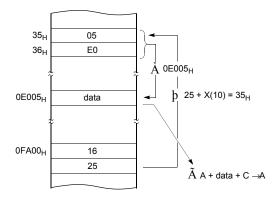

#### X indexed indirect →[dp+X]

Processes memory data as Data, assigned by 16-bit pair memory which is determined by pair data [dp+X+1][dp+X] Operand plus X-register data in Direct page.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; X=10<sub>H</sub>

1625 ADC [25H+X]

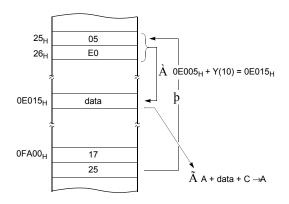

# Y indexed indirect $\rightarrow$ [dp]+Y

Processes memory data as Data, assigned by the data [dp+1][dp] of 16-bit pair memory paired by Operand in Direct page plus Y-register data.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; Y=10<sub>H</sub>

1725 ADC [25H]+Y

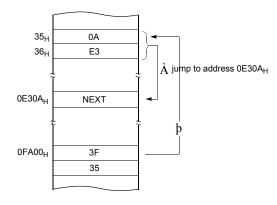

# Absolute indirect →[!abs]

The program jumps to address specified by 16-bit absolute address.

JMP

Example;

1F25E0 JMP [!OC025H]

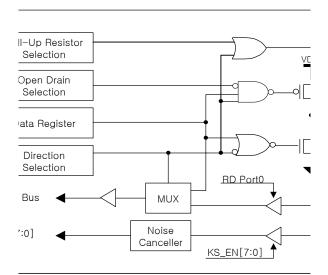

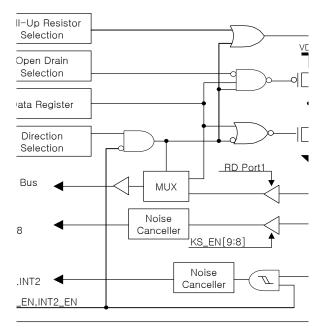

#### 10. I/O PORTS

The GMS87C5216 has 38 I/O ports which are PORT0(8 I/O), PORT1 (8 I/O), PORT2 (8 I/O), PORT3 (8 I/O), PORT4 (6 I/O). Pull-up resistor of each port can be selectable by program. Each port contains data direction register which controls I/O and data register which stores port data

#### 10.1 R0 Ports

R0 is an 8-bit CMOS bidirectional I/O port (address  $0C0_H$ ). Each I/O pin can independently used as an input or an output through the R0DD register (address  $0C1_H$ ).

R0 has internal pull-ups that is independently connected or disconnected by R0PC. The control registers for R0 are shown below.

| R0 Data R  | Register (R/W) R07 R06 R05 R04 | ADDRESS : 0C0 <sub>H</sub><br>RESET VALUE : Undefined<br>R03 R02 R01 R00 |

|------------|--------------------------------|--------------------------------------------------------------------------|

| R0 Directi | ion Register (W)               | ADDRESS : 0C1 <sub>H</sub><br>RESET VALUE : 00 <sub>H</sub>              |

| R0DD       |                                |                                                                          |

|            |                                | Port Direction<br>0: Input<br>1: Output                                  |

| R0 Pull-u  | p Selection Register (V        | V) ADDRESS :0F8 <sub>H</sub><br>RESET VALUE : 00 <sub>H</sub>            |

| R0PC       |                                |                                                                          |

|            |                                | Pull-up select 1: Without pull-up 0: With pull-up                        |

| R0 Open    | drain Assign Register (        | (W) ADDRESS :0E4 <sub>H</sub> RESET VALUE : 00 <sub>H</sub>              |

| R0ODC      |                                |                                                                          |

|            |                                | Open drain select<br>0: Push-pull<br>1: Open drain                       |

|            |                                |                                                                          |

#### (1) R0 I/O Data Direction Register (R0DD)

R0 I/O Data Direction Register (R0DD) is 8-bit register, and can assign input state or output state to each bit. If R0DD is ``1``, port R0 is in the output state, and if ``0``, it is in the input state. R0DD is write-only register. Since R0DD is initialized as ``00 h`` in reset state, the whole port R0 becomes input state.

#### (2) R0 Data Register (R0)

R0 data register (R0) is 8-bit register to store data of port R0. When set as the output state by R0DD, and data is written in R0, data is outputted into R0 pin. When set as the input state, input state of pin is read. The initial value of R0 is unknown in reset state.

#### (3) R0 Open drain Assign Register (R0ODC)

R0 Open Drain Assign Register (R0ODC) is 8bit register, and can assign R0 port as open drain output port each bit, if corresponding port is selected as output. If R0ODC is selected as ``1``, port R0 is open drain output, and if selected as ``0``, it is push-pull output. R0ODC is write-only register and initialized as ``00 h`` in reset state.

# (4) R0 Pull-up Resistor Control Register (R0PC)

R0 pull-up resistor control register (R0PC) is 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R0PC is selected as ``1``, pull-up ia disabled and if selected as ``0``, it is enabled. R0PC is write-only register and initialized as ``00 h`` in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

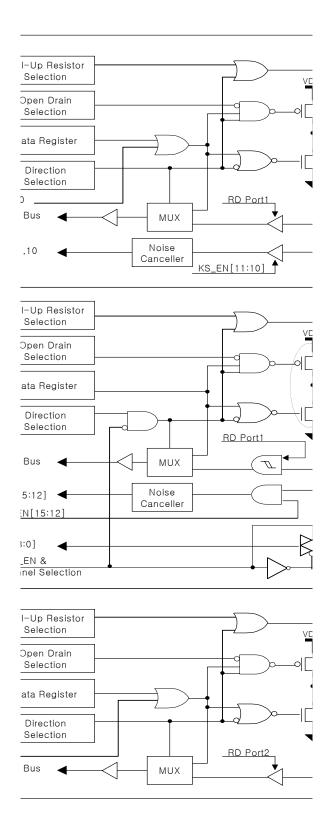

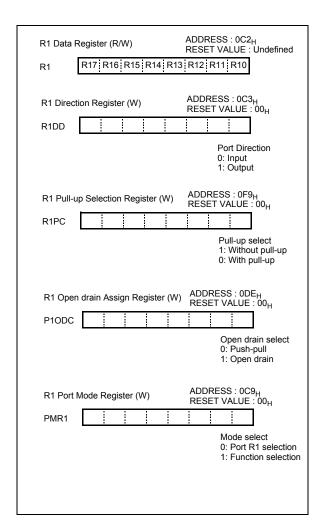

#### 10.2 R1 Ports

R1 is an 8-bit CMOS bidirectional I/O port (address  $0C2_H$ ). Each I/O pin can independently used as an input or an output through the R1DD register (address  $0C3_H$ ).

R1 has internal pull-ups that is independently connected or disconnected by register R1PC. The control registers for R1 are shown below.

#### (1) R1 I/O Data Direction Register (R1DD)

R1 I/O Data Direction Register (R1DD) is 8-bit register, and can assign input state or output state to each bit. If R1DD is ``1``, port R1 is in the output state, and if ``0``, it is in the input state. R1DD is write-only register. Since R1DD is initialized as ``00 h`` in reset state, the whole port R1 becomes input state.

#### (2) R1 Data Register (R1)

R1 data register (R1) is 8-bit register to store data of port R1. When set as the output state by R1DD, and data is written in R1, data is outputted into R1 pin. When set as the input state, input state of pin is read. The initial value of R1 is unknown in reset state.

#### (3) R1 Mode Register (PMR1)

R1 Port Mode Register (PMR1) is 8-bit register, and can assign the selection mode for each bit. When set as "0", corresponding bit of PMR1 acts as port R1 selection mode, and when set as ``1``, it becomes function selection mode.

PMR1 is write-only register and initialized as ``00 h`` in reset state. Therefore, becomes Port selection mode. Port R1 can be I/O port by manipulating each R1DD bit, if corresponding PMR1 bit is selected as ``0``.

| Pin Name | PMR1 | Selection<br>Mode | Remarks      |

|----------|------|-------------------|--------------|

| -        |      |                   |              |

| -        |      |                   |              |

| FC0      | 0    | R25(I/O)          | -            |

| EC0      | 1    | EC0(I)            | EVENT COUNTO |

| то       | 0    | R24(I/O)          | -            |

| T2       | 1    | T2(O)             | TIMER2       |

| T1       | 0    | R13 (I/O)         | -            |

| 11       | 1    | T1(O)             | TIMER1       |

| To       | 0    | R12 (I/O)         | -            |

| ТО       | 1    | T0(O)             | TIMER0       |

| INITO    | 0    | R11 (I/O)         | -            |

| INT2     | 1    | INT2(I)           | EXT INT2     |

| INITA    | 0    | R10(I/O)          | -            |

| INT1     | 1    | INT1(I)           | EXT INT1     |

Table 10-1 Selection mode of PMR1

#### (4) R1 Pull-up Resistor Control Register (R1PC)

R1 pull-up resistor control register (R1PC) is 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R1PC is selected as ``1``, pull-up ia disabled and if selected as ``0``, it is enabled. R1PC is write-only register and initialized as ``00 h`` in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

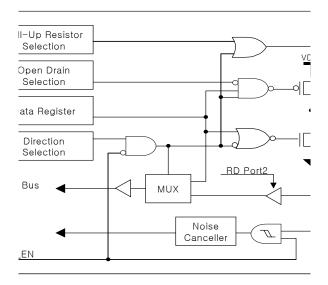

# 10.3 R2 Port

R2 is an 8-bit CMOS bidirectional I/O port (address  $0C4_H$ ). Each I/O pin can independently used as an input or an output through the R2DD register (address  $0C5_H$ ).

R2 has internal pujll-ups that is independently connected or disconnected by R2PC (address  $0FA_H$ ). The control registers for R2 are shown as below.

| R2 Data Register (R/W) R2 R27 R26 R25 R24 R23 | ADDRESS : 0C4 <sub>H</sub><br>RESET VALUE : Undefined                                                  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|

| R2 Direction Register (W)                     | ADDRESS: 0C5 <sub>H</sub> RESET VALUE: 00 <sub>H</sub> Port Direction 0: Input 1: Output               |

| R2 Pull-up Selection Register (W)             | ADDRESS:0FA <sub>H</sub> RESET VALUE:00 <sub>H</sub> Pull-up select 1: Without pull-up 0: With pull-up |

| R2 Open drain Assign Register (W)             | ADDRESS :0DF <sub>H</sub> RESET VALUE : 00 <sub>H</sub> Open drain select 0: Push-pull 1: Open drain   |

# (1) R2 I/O Data Direction Register (R2DD)

$R2\ I/O\ Data\ Direction\ Register\ (R2DD)$  is 8-bit register, and can

assign input state or output state to each bit. If R2DD is ``1``, port R2 is in the output state, and if ``0``, it is in the input state. R2DD is write-only register. Since R2DD is initialized as ``00 h`` in reset state, the whole port R2 becomes input state.

#### (2) R2 Data Register (R2)

R2 data register (R2) is 8-bit register to store data of port R2. When set as the output state by R2DD, and data is written in R2, data is outputted into R2 pin. When set as the input state, input state of pin is read. The initial value of R2 is unknown in reset state.

# (3) R2 Open drain Assign Register (R2ODC)

R2 Open Drain Assign Register (R2ODC) is 8bit register, and can assign R2 port as open drain output port each bit, if corresponding port is selected as output. If R2ODC is selected as ``1``, port R2 is open drain output, and if selected as ``0``, it is push-pull output. R2ODC is write-only register and initialized as ``00 h`` in reset state.

# (4) R2 Pull-up Resistor Control Register (R2PC)

R2 pull-up resistor control register (R2PC) is 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R2PC is selected as ``1``, pull-up is disabled and if selected as ``0``, it is enabled. R2PC is write-only register and initialized as ``00 h`` in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

#### **R3 Port**

R3 is an 8-bit CMOS bidirectional I/O port (address  $0E5_H$ ). Each I/O pin can independently used as an input or an output through the R3DD register (address  $0E6_H$ ).

R3 has internal pull-ups that is independently connected or disconnected by R3PC (address  $0FB_{\rm H}$ ). The control registers for R3 are shown as below.

| R3 Data Register (R/W) R3 R37 R36 R35 R34 R3 | ADDRESS : 0E5 <sub>H</sub><br>RESET VALUE : Undefined<br>33 R32 R31 R30                                   |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| R3 Direction Register (W)                    | ADDRESS: 0E6 <sub>H</sub> RESET VALUE: 00 <sub>H</sub> Port Direction 0: Input 1: Output                  |

| R3 Pull-up Selection Register (W)            | ADDRESS :0FB <sub>H</sub> RESET VALUE : 00 <sub>H</sub> Pull-up select 1: Without pull-up 0: With pull-up |

| R3 Open drain Assign Register (W)            | Open drain select 0: Push-pull 1: Open drain                                                              |

#### (1) R3 I/O Data Direction Register (R3DD)

R3 I/O Data Direction Register (R3DD) is 8-bit register, and can assign input state or output state to each bit. If R3DD is ``1``, port R3 is in the output state, and if ``0``, it is in the input state. R3DD is write-only register. Since R3DD is initialized as ``00 h`` in reset state, the whole port R3 becomes input state.

#### (2) R3 Data Register (R3)

R3 data register (R3) is 8-bit register to store data of port R3. When set as the output state by R3DD, and data is written in R3, data is outputted into R3 pin. When set as the input state, input state of pin is read. The initial value of R3 is unknown in reset state.

# (3) R3 Open drain Assign Register (R3ODC)

R3 Open Drain Assign Register (R3ODC) is 8bit register, and can assign R3 port as open drain output port each bit, if corresponding port is selected as output. If R3ODC is selected as ``1``, port R3 is open drain output, and if selected as ``0``, it is push-pull output. R3ODC is write-only register and initialized as ``00 h`` in reset state.

### (4) R3 Pull-up Resistor Control Register (R3PC)

R3 pull-up resistor control register (R3PC) is 8-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R3PC is selected as "1", pull-up ia disabled and if selected as "0", it is enabled. R3PC is write-only register and initialized as "00 h" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

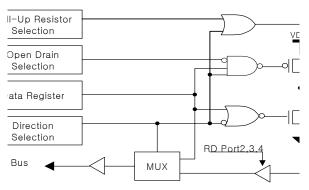

#### **R4 Port**

R4 is an 1-bit CMOS bidirectional I/O port (address  $0E7_H$ ). Each I/O pin can independently used as an input or an output through the R4DD register (address  $0E8_H$ ).

R3 has internal pull-ups that is independently connected or disconnected by R4PC (address  $0FC_{\rm H}$ ). The control registers for R4 are shown as below.

| R4 Data R          | Register (R/W) ADDRESS : 0E7 <sub>H</sub> RESET VALUE : Undefin                                              | ed         |

|--------------------|--------------------------------------------------------------------------------------------------------------|------------|

| R4                 | R44 R43 R42 R41 R40                                                                                          |            |

| R4 Directi<br>R4DD | ion Register (W)  ADDRESS: 0E8 <sub>H</sub> RESET VALUE: 00 <sub>H</sub> Port Direction 0: Input 1: Output   |            |

| R4 Pull-up         | p Selection Register (W)  ADDRESS :0FCH RESET VALUE : 00H  Pull-up select 1: Without pull-up 0: With pull-up | р          |

| R4 Open            | drain Assign Register (W) ADDRESS :0E1 <sub>H</sub> RESET VALUE : 00 <sub>H</sub>                            |            |

| R4ODC              | Open drain color                                                                                             | <b>~</b> + |

|                    | Open drain selec<br>0: Push-pull<br>1: Open drain                                                            | Л          |

#### (1) R4 I/O Data Direction Register (R4DD)

R4 I/O Data Direction Register (R4DD) is 1-bit register, and can assign input state or output state to each bit. If R4DD is ``1``, port R4 is in the output state, and if ``0``, it is in the input state. R4DD is write-only register. Since R4DD is initialized as ``00 h`` in reset state, the whole port R4 becomes input state.

#### (2) R4 Data Register (R4)

R4 data register (R4) is 1-bit register to store data of port R4. When set as the output state by R4DD, and data is written in R4, data is outputted into R4 pin. When set as the input state, input state of pin is read. The initial value of R4 is unknown in reset state.

#### (3) R4 Open drain Assign Register (R4ODC)

R4 Open Drain Assign Register (R4ODC) is 1-bit register, and can assign R4 port as open drain output port each bit, if corresponding port is selected as output. If R4ODC is selected as ``1``, port R4 is open drain output, and if selected as ``0``, it is pushpull output. R4ODC is write-only register and initialized as ``00 h`` in reset state.

#### (4) R4 Pull-up Resistor Control Register (R4PC)

R4 pull-up resistor control register (R4PC) is 1-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If R4PC is selected as ``1``, pull-up ia disabled and if selected as ``0``, it is enabled. R4PC is write-only register and initialized as ``00 h`` in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

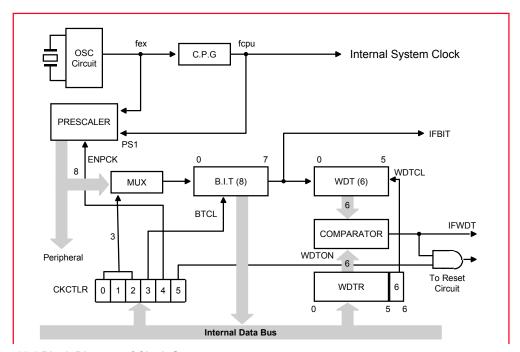

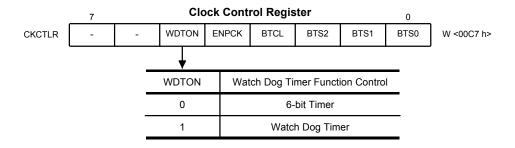

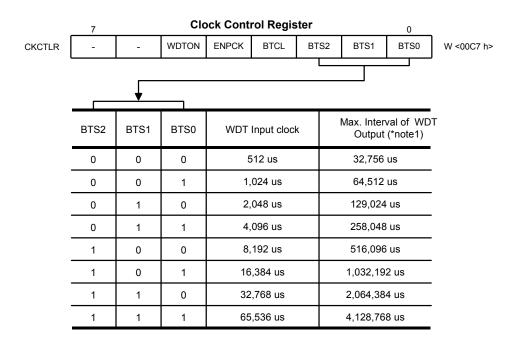

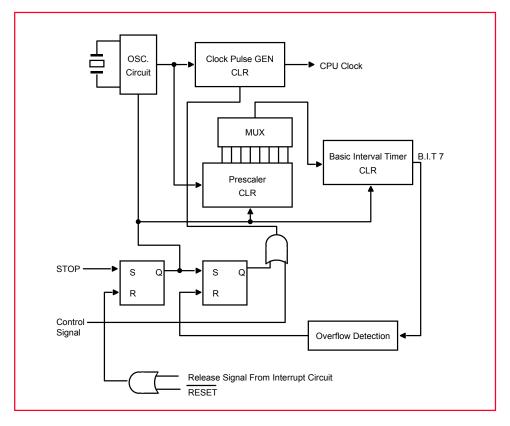

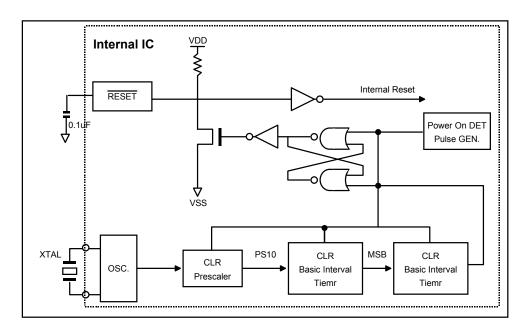

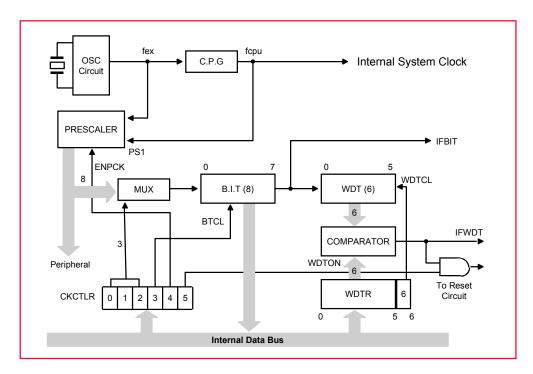

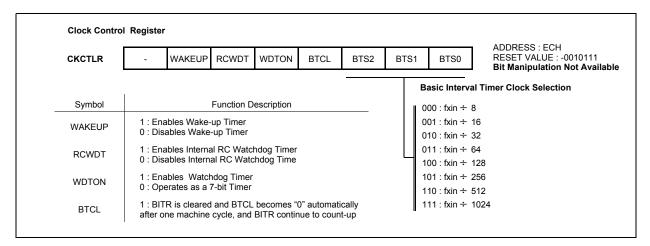

# 11. CLOCK GENERATOR

Clock generating circuit consists of Clock Pulse Generator (C.P.G), Prescaler, Basic Interval Timer (B.I.T) and Watch Dog

Timer. The clock applied to the Xin pin divided by two is used as the internal system clock.

Figure 11-1 Block Diagram of Clock Generator

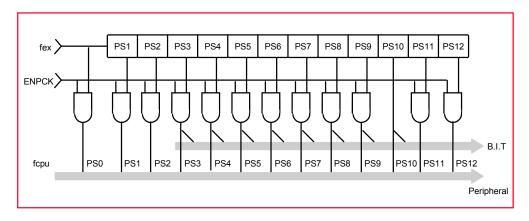

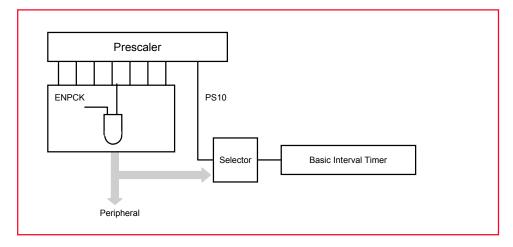

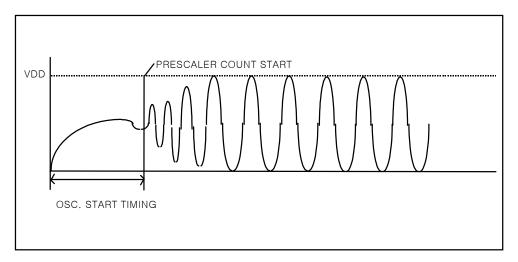

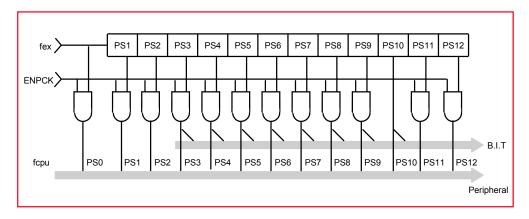

Prescaler consists of 12-bit binary counter. The clock supplied from oscillation circuit is input to prescaler (fex). The divided

output from each bit of prescaler is provided to peripheral hardware.

Figure 11-2 Block diagram of Prescaler

| fex (MHz)                                                                                      | 4 MHz                                                                                                                                 |                                                                                                           | 2 MHz                                                                                                                        |                                                                   |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|                                                                                                | frequency                                                                                                                             | period                                                                                                    | frequency                                                                                                                    | period                                                            |

| ps 0<br>ps 1<br>ps 2<br>ps 3<br>ps 4<br>ps 5<br>ps 6<br>ps 7<br>ps 8<br>ps 9<br>ps 10<br>ps 11 | 4 MHz<br>2 MHz<br>1 MHz<br>500 KHz<br>250 KHz<br>125 KHz<br>62.5 KHz<br>31.25 KHz<br>15.63 KHz<br>7.183 KHz<br>3.906 KHz<br>1.953 KHz | 250 ns<br>500 ns<br>1 us<br>2 us<br>4 us<br>8 us<br>16 us<br>32 us<br>64 us<br>128 us<br>256 us<br>512 us | 2 MHz<br>1 MHz<br>500 KHz<br>250 KHz<br>125 KHz<br>62.5 KHz<br>31.25 KHz<br>15.63 KHz<br>7.183 KHz<br>3.906 KHz<br>1.953 KHz | 500 ns 1 us 2 us 4 us 8 us 16 us 32 us 64 us 128 us 256 us 512 us |

| ps 12                                                                                          | 0.976 KHz                                                                                                                             | 1024 us                                                                                                   | 0.488 KHz                                                                                                                    | 2048 us                                                           |

Table 11-1 ps output period

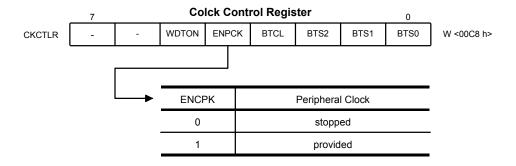

lock to peripheral hardware can be stopped by bit4 (ENPCK) of CKCTLR Register. ENPCK is set to ``1`` in reset state.

# 12. Timer

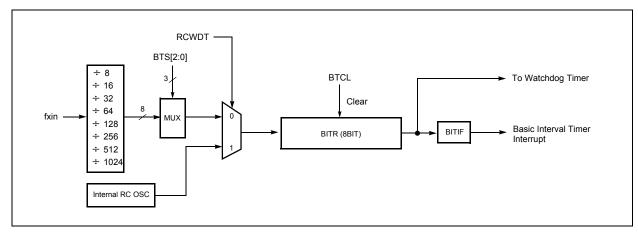

# 12.1 Basic Interval Timer

The GMS81C5016/24/32 has one 8-bit Basic Interval Timer that is free-run and can not stop. Block diagram is shown in Figure 12-1.

The Basic Interval Timer generates the time base for key scanning, watchdog timer counting, and etc. It also provides a Basic interval timer interrupt (IFBIT). As the count overflow from  ${\rm FF}_{\rm H}$  to  $00_{\rm H}$ , this overflow causes the interrupt to be generated.

- -8bit binary counter

- -Use the bit output of prescaler as input to secure the oscillation stabilization time after power-on

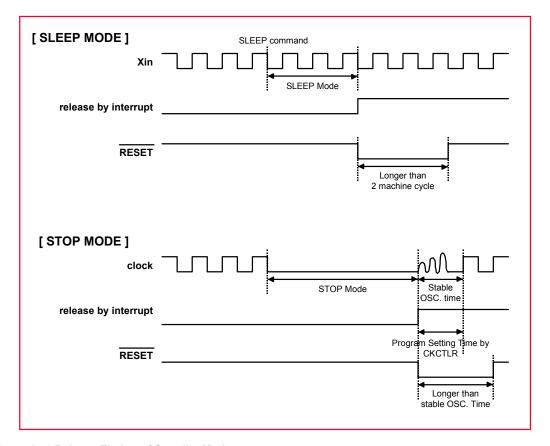

- -Secures the oscillation stabilization time in standby mode (stop mode) release

- -Contents of B.I.T can be read

- -Provides the clock for watch dog timer.

Figure 12-1 Block Diagram of Basic Interval Timer

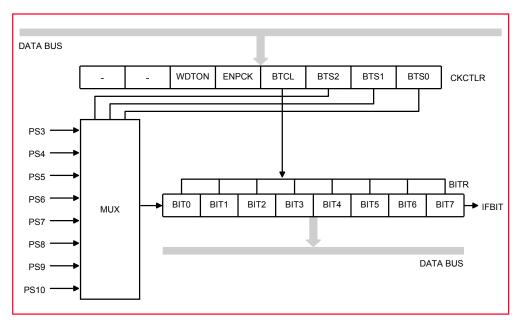

# (1) Control of B.I.T

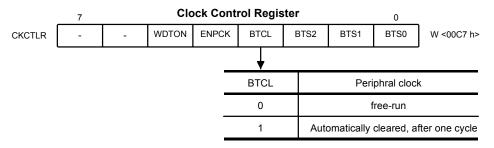

The Basic Interval Timer is controlled by the clock control register (CKCTLR) shown in Figure 12-2. If bit3(BTCL) of CKCTLR is set to ``1``, B.I.T is cleared, and then, after one machine cycle,

BTCL becomes ``0``, and B.I.T starts counting. BTCL is set to ``0`` in reset state.

Figure 12-2 BTCL mode of B.I.T

## (2) Input clock selection of B.I.T

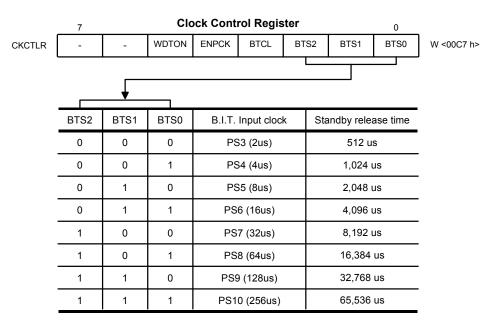

The input clock of B.I.T can be selected from the prescaler within a range of 2us to 256us by clock input selection bits (BTS2~BTS0). (at fex = 4MHz). In reset state, or power on reset, BTS2="1", BTS1="1", BTS0="1" to secure the longest oscillation stabilization time. B.I.T can generate the wide range of ba-

sic interval time interrupt request (IFBIT) by selecting prescaler output. Interrupt interval can be selected to kinds of interval time as shown in

Figure 12-3.

Figure 12-3 Basic Interval Timer Interrupt Time

#### (3) Reading Basic Interval Timer

By reading of the Basic Interval Timer Register (BITR), we can read counter value of B.I.T. Because B.I.T can be cleared or read, the spending time up to maximum 65.5ms can be available. B.I.T

is read-only register. If B.I.T register is written, then CKCTLR register with same address is written.

|      | 7    | 0    |      |      |      |      |      |      |            |

|------|------|------|------|------|------|------|------|------|------------|

| BITR | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 | R <00C7 h> |

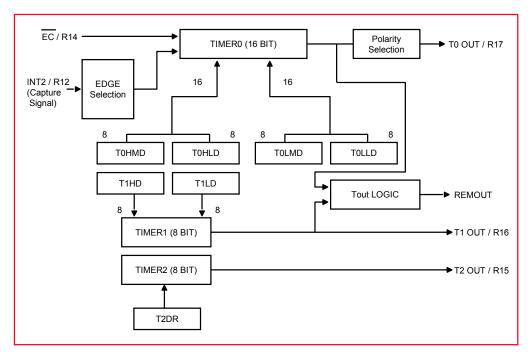

## 12.2 Timer0, Timer1, Timer2

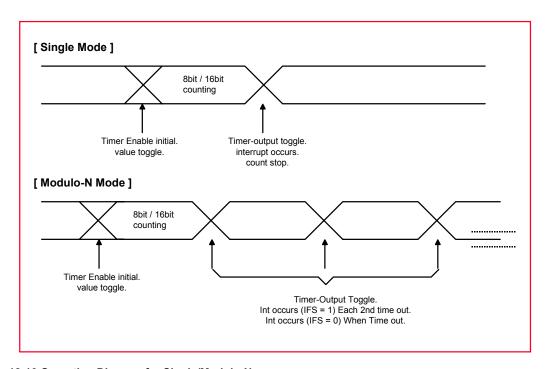

### (1) Timer Operation Mode

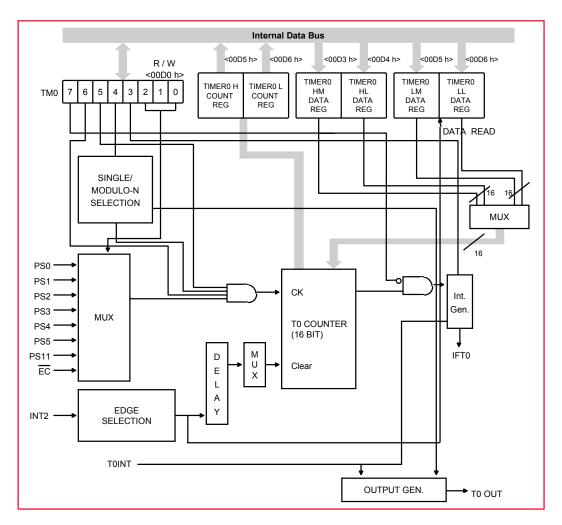

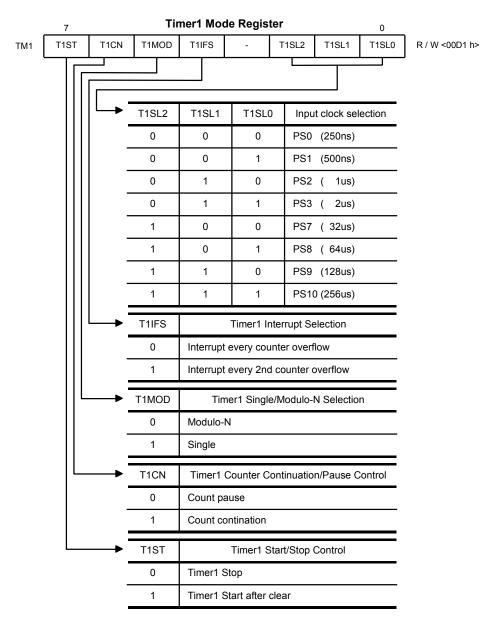

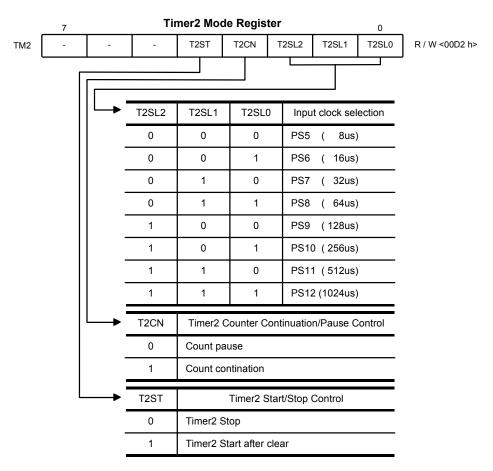

Timer consists of 16bit binary counter Timer0 (T0), 8bit binary Timer1 (T1), Timer2 (T2), Timer Data Register, Timer Mode Register (TM01, TM0, TM1, TM2) and control circuit. Timer Data Register Consists of Timer0 High-MSB Data Register (T0HMD), Timer0 High-LSB Data Register (T0HLD), Timer0 Low-MSB Data Register (T0LMD), Timer0 Low-LSB Data Register (T0LLD), Timer1 High Data Register (T1HD), Timer1 Low

Data Register (T1LD), Timer2 Data Register (T2DR). Any of the PS0  $\sim$  PS5, PS11 and external event input EC can be selected as clock source for T0. Any of the PS0  $\sim$  PS3, PS7  $\sim$  PS10 can be selected as clock T1. Any of the PS5  $\sim$  PS12 can be selected as clock source for T2.

\* Relevant Port Mode Register (PMR1: 00C9 h) value should be assigned for event counter,

| Timer0 | - 16-bit Interval Timer<br>- 16-bit Event Counter<br>- 16-bit Input Capture<br>- 16-bit rectangular-wave output | - Single/Modulo-N Mode - Timer Output Initial Value Setting - Timer0~Timer1 combination Logic Output - One Interrupt Generating Every 2nd |

|--------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Timer1 | - 8-bit Interval Timer<br>- 8-bit rectangular-wave output                                                       | Counter Overflow                                                                                                                          |

| Timer2 | - 8-bit Interval Timer<br>- 8-bit rectangular-wave output<br>- Modulo-N Mode                                    |                                                                                                                                           |

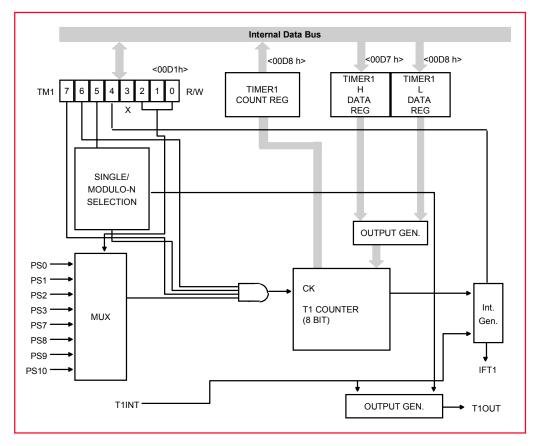

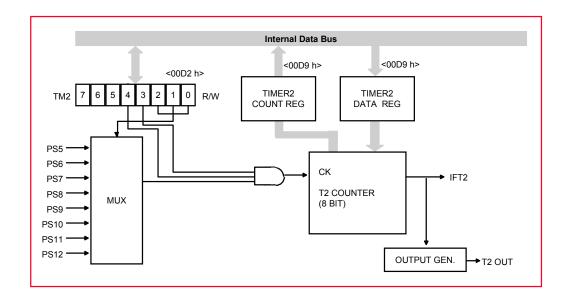

Figure 12-4 Timer / Counter Block diagram

## (2) Function of Timer & Counter

fex = 4MHz

| 16bit Tim       | er (T0)       | 8bit Time       | r (T1)     | 8bit Timer (T2) |            |

|-----------------|---------------|-----------------|------------|-----------------|------------|

| Resolution (CK) | Max. Count    | Resolution (CK) | Max. Count | Resolution (CK) | Max. Count |

| PS0 ( 0.25 us)  | 16,384 us     | PS0 ( 0.25 us)  | 64 us      | PS5 ( 8 us)     | 2.048 us   |

| PS1 ( 0.5 us)   | 32,768 us     | PS1 ( 0.5 us)   | 128 us     | PS6 ( 16 us)    | 4,096 us   |

| PS2 ( 1 us)     | 65,536 us     | PS2 ( 1 us)     | 256 us     | PS7 ( 32 us)    | 8,192 us   |

| PS3 ( 2 us)     | 131,072 us    | PS3 ( 2 us)     | 512us      | PS8 ( 64 us)    | 16,384 us  |

| PS4 ( 4 us)     | 262,144 us    | PS7 ( 32 us)    | 8,192 us   | PS9 ( 128 us)   | 32,768 us  |

| PS5 ( 8 us)     | 524,288 us    | PS8 ( 64 us)    | 16,384 us  | PS10 ( 256 us)  | 65,536 us  |

| PS11 ( 512 us)  | 33,554,432 us | PS9 ( 128 us)   | 32,768 us  | PS11 ( 512 us)  | 131,072 us |

| EC              | -             | PS10 ( 256 us)  | 65,536 us  | PS12 (1,024 us) | 262,144 us |

Figure 12-5 Block Diagram of Timer0

Figure 12-6 Block Diagram of Timer1

Figure 12-7 Block Diagram of Timer2

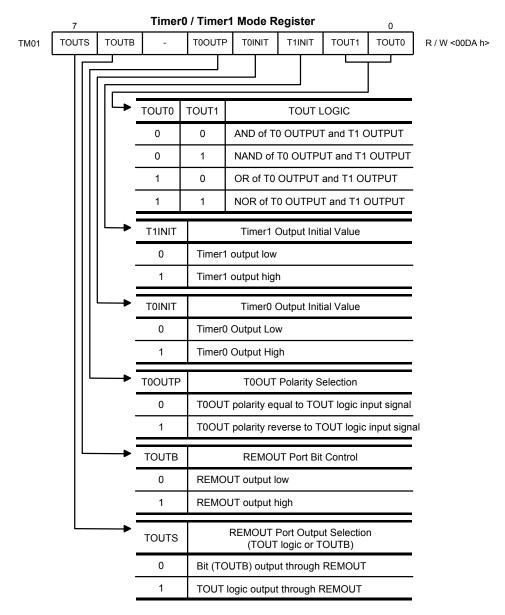

Figure 12-8 Timer0 / Timer1 Mode Register

<sup>\*</sup> PS1 : not supporting input capture.

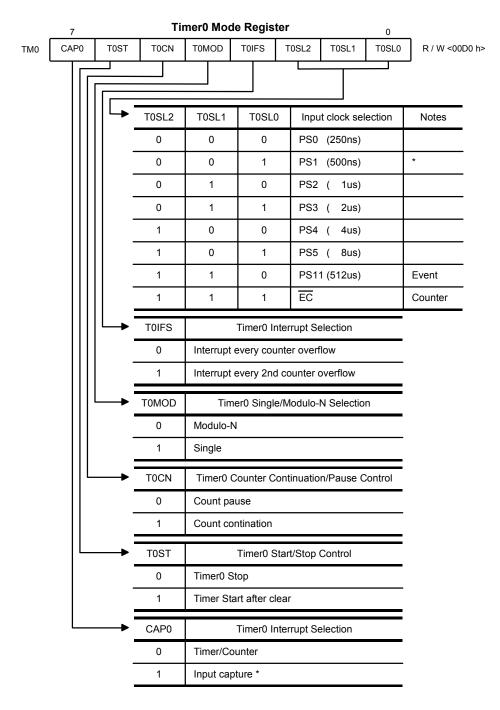

Figure 12-9 Timer0 Mode Register

Figure 12-10 Timer1 Mode Register

Figure 12-11 Timer2 Mode Register

|      | 7  | Externa | l Interru | ot Signal | Edge S | election I             | Register | 0 |            |

|------|----|---------|-----------|-----------|--------|------------------------|----------|---|------------|

| IEDS | -  | -       | IED2H     | IED2L     | IED1H  | IED1L                  | -        | - | W <00CB h> |

|      |    |         |           |           |        |                        |          |   |            |

|      | IE | D*H     |           | IED*L     |        | !                      | NT*      |   |            |

|      |    | 0       |           | 0         |        |                        | -        |   |            |

|      |    | 0       |           | 1         |        | Falling Edge Selection |          |   | •          |

|      |    | 1       |           | 0         |        | Rising Edge Selection  |          |   |            |

|      |    | 1       |           | 1         | Both   | Edge Sel               | ection   |   | •          |

Figure 12-12 External Interrupt Signal Edge Selection

Register

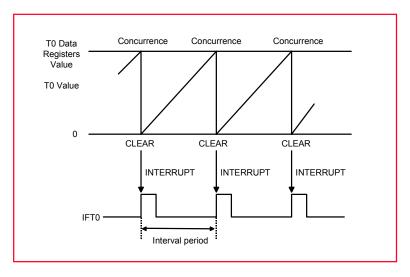

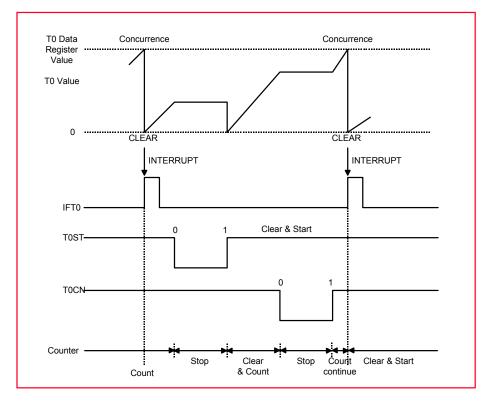

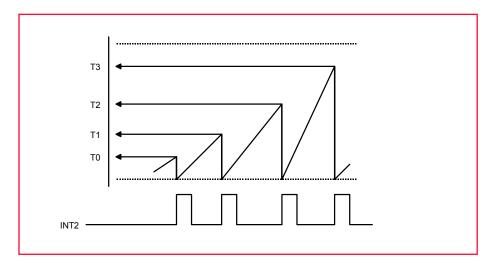

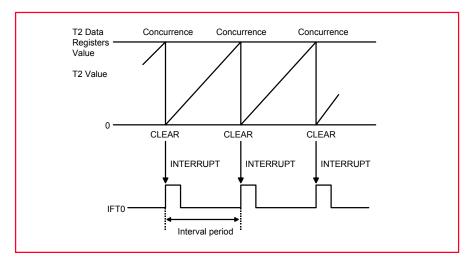

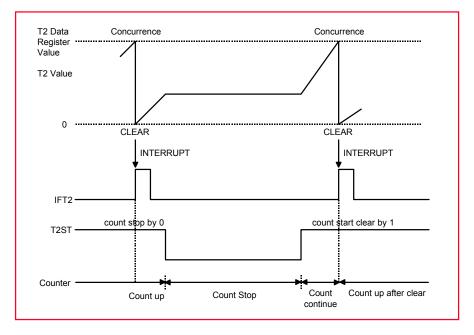

#### (3) Timer0, Timer1

TIMER0 and TIMER1 have an up-counter. When value of the up-counter reaches the content of Timer Data Register (TDR),

the up-counter is cleared to ``00 h``, and interrupt (IFT0, IFT1) is occured at the next clock.

Figure 12-13 Operatiion of Timer0