#### **Not Intended For New Designs**

T-46-07-08

# 11C70 Master-Slave D-Type Flip-Flop

## **General Description**

The 11C70 is a high-speed ECL D-Type Master-Slave Flip-Flop capable of toggle rates over 650 MHz. Designed primarily for communications and instrumentation, it can also be used in other digital applications and is fully compatible with 10K ECL. Asynchronous Direct Set and Direct Clear inputs are provided which override the clock.

The circuit is voltage-compensated, which makes output levels and input thresholds insensitive to  $V_{\mbox{\footnotesize{EE}}}$  variations.

This also allows operation with ECL supply voltage  $V_{EE}$  of -5.2V or with TTL supply  $V_{CC}$  of +5.0V. Each input has an internal 50 k $\Omega$  pull-down resistor, which allows unused inputs to be left open. Open emitter-follower outputs accommodate a variety of loading and terminating schemes. The 11C70 is pin-compatible with the Motorola MC1670 but is a higher-frequency replacement.

# Ordering Code: See Section 6

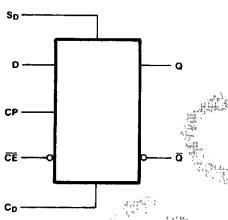

# **Logic Symbol**

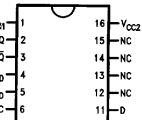

# Connection Diagram

16-Pin DIP

NC 6 11 D CP 7 10 NC VE 8 9 CE

TL/F/9891-1

TL/F/9891-

| Pin Names                | Description               |

|--------------------------|---------------------------|

| CE                       | Clock Enable (Active LOW) |

| CP                       | Clock Pulse               |

| D                        | Deta Input                |

| Q, <b>⊼</b> <sup>™</sup> | Outputs                   |

| S <sub>D</sub>           | Direct Set                |

| C <sub>D</sub>           | Direct Clear              |

#### **Truth Table**

| Inputs |    |   |     |    | 0      | Operation     |  |

|--------|----|---|-----|----|--------|---------------|--|

| SD     | CD | D | CE  | СР | Qt + 1 | Operation     |  |

| Н      | L  | Х | Х   | Х  | Н      | Direct Set    |  |

| L      | Н  | Х | X   | X  | L      | Direct Clear  |  |

| Н      | Н  | Х | Χ   | X  | _      | intermediate  |  |

| L      | L  | Х | Н   | _  | Qt     | Disable Clock |  |

| L      | L  | Н | L   |    | Н      | Clocked Set   |  |

| L      | _L | L | _ L |    | L      | Clocked Clear |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

= LOW to HIGH Transition

t, t+1 = Time Before and After Clock Positive Transition

### **Absolute Maximum Ratings**

Above which the useful life may be impaired

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

-65°C to +150°C Storage Temperature +150°C

Maximum Junction Temperature (T<sub>J</sub>) -7.0V to GND Supply Voltage Range

VEE to GND Input Voltage (DC) -50 mA Output Current (DC Output HIGH)

-5.7V to -4.7V **Operating Range** 300°C

Lead Temperature (Soldering, 10 sec.)

## **Recommended Operating Conditions**

Max -4.7VSupply Voltage (VEE) -5.700°C Ambient Temperature (TA)

#### **DC Electrical Characteristics**

$V_{EE} = -5.2V$ ,  $V_{CC} = GND$

| Symbol           | Parameter                                           | Min                     | Тур | Max                        | Units          | ⊕ T <sub>A</sub>        | Conditions                                                                      |

|------------------|-----------------------------------------------------|-------------------------|-----|----------------------------|----------------|-------------------------|---------------------------------------------------------------------------------|

| Voн              | Output Voltage HIGH                                 | -1000<br>-960<br>-900   |     | -840<br>-810<br>-720       | mV<br>mV<br>mV | ტე<br>+25°0<br>+75°0    | $V_{IN} = V_{IHA}$ or $V_{ILB}$ per Truth<br>Table Loading 50 $\Omega$ to $-2V$ |

| V <sub>OL</sub>  | Output Voltage LOW                                  | -1870<br>-1850<br>-1850 |     | -1665<br>-1620<br>-1595    | mV<br>mV<br>mV | 9°C<br>+25°C<br>+75°C   |                                                                                 |

| V <sub>OHC</sub> | Output Voltage HIGH                                 | -1020<br>-980<br>-920   |     |                            | mV<br>mV<br>mV | 0°C<br>                 | $V_{IN} = V_{IHB}$ or $V_{ILA}$ for D input Loading $50\Omega$ to $-2V$         |

| V <sub>OLC</sub> | Output Voltage LOW                                  |                         | /6  | - 1615<br>- 1600<br>- 1575 | m > 0<br>m > 0 | 0°C<br>+25°C<br>+75°C   |                                                                                 |

| V <sub>IH</sub>  | Input Voltage HIGH                                  | -1135<br>-1095<br>-1035 |     | -840<br>-810<br>-720       | mV<br>mV<br>mV | 0°C<br>+ 25°C<br>+ 75°C | Guaranteed input Voltage HIGH<br>for All inputs                                 |

| V <sub>IL</sub>  | Input Voltage LOW                                   | -1870<br>-1850<br>-1830 |     | -1500<br>-1485<br>-1460    | mV<br>mV<br>mV | 0°C<br>+ 25°C<br>+ 75°C | Guaranteed Input Voltage LOW for All Inputs                                     |

| liH              | Input Current HIGH Clock Input Data Input Sp and Cp |                         |     | 250<br>270<br>550          | μΑ<br>μΑ<br>μΑ | +25°C                   | V <sub>IN</sub> = V <sub>IHA</sub>                                              |

| IįL              | Input Current LOW                                   | 0.5                     |     |                            | μА             | +25°C                   | V <sub>IN</sub> = V <sub>IHB</sub>                                              |

| IEE              | Power Supply Current                                | -48                     |     |                            | mA             | + 25°C                  | All Inputs Open                                                                 |

# AC Electrical Characteristics

$V_{EE} = -5.2V$ ,  $V_{CC} = GND$ ,  $T_A = +25^{\circ}C$

| Symbol                          | Parameter                                                | Min | Тур | Max | Units | Conditions          |

|---------------------------------|----------------------------------------------------------|-----|-----|-----|-------|---------------------|

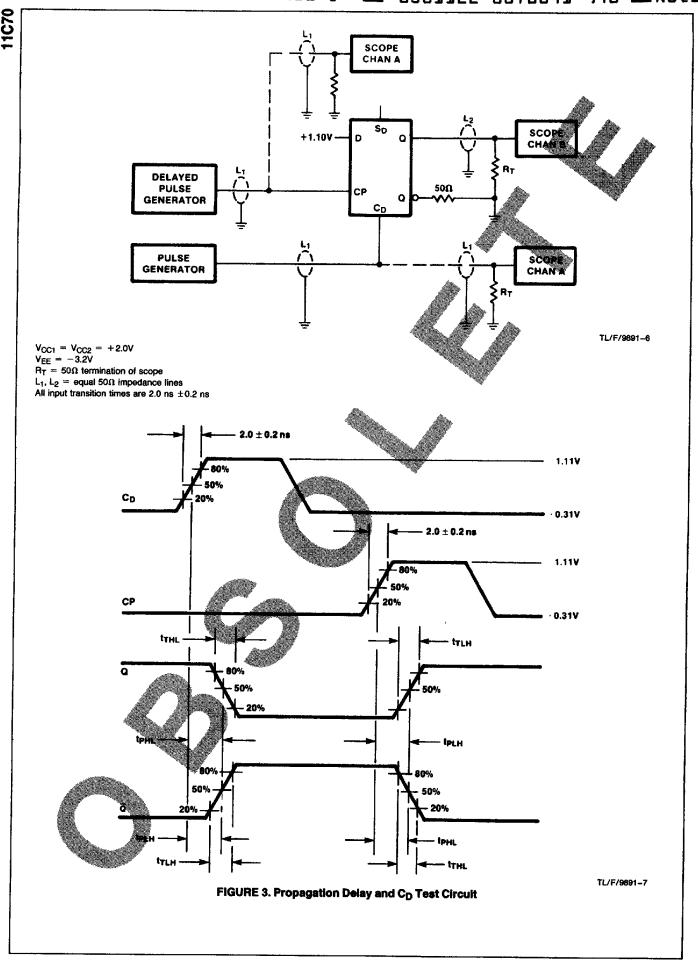

| t <sub>PLH</sub> , t <b>pHL</b> | Propagation Delay (CP-Q)                                 |     | 1.1 | 1.4 | ns    | See Figures 3 and 4 |

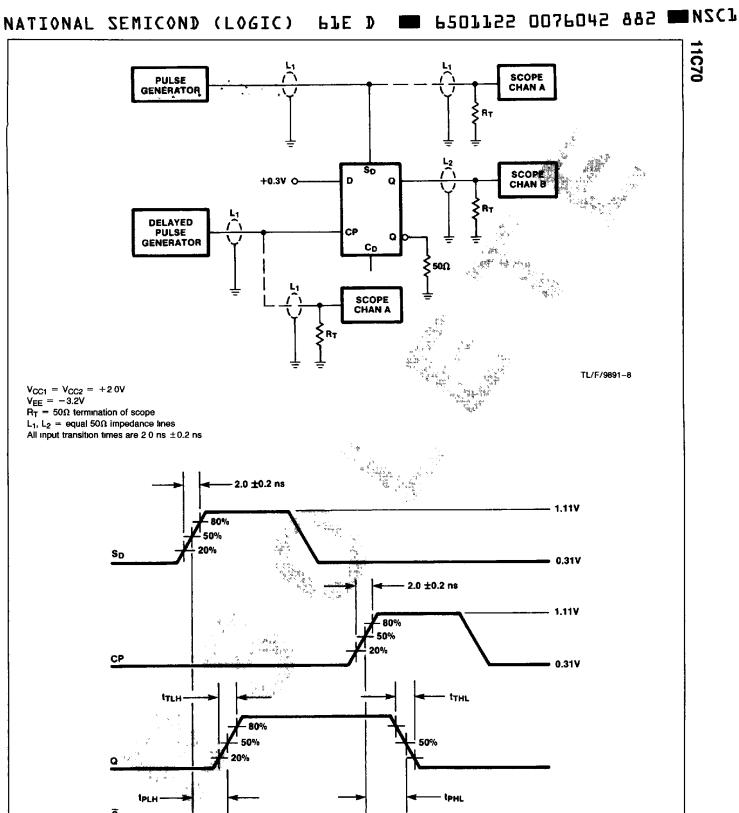

| tplH. <b>(PH</b> L              | Propagation Delay (S <sub>D</sub> -Q, C <sub>D</sub> -Q) |     | 1.3 | 1.7 | ns    |                     |

| tTLH                            | Transition Time 20% to 80%                               |     | 0.9 | 1.3 | ns    |                     |

| t <sub>THL</sub>                | Transition Time 80% to 20%                               |     | 0.9 | 1.3 | ns    |                     |

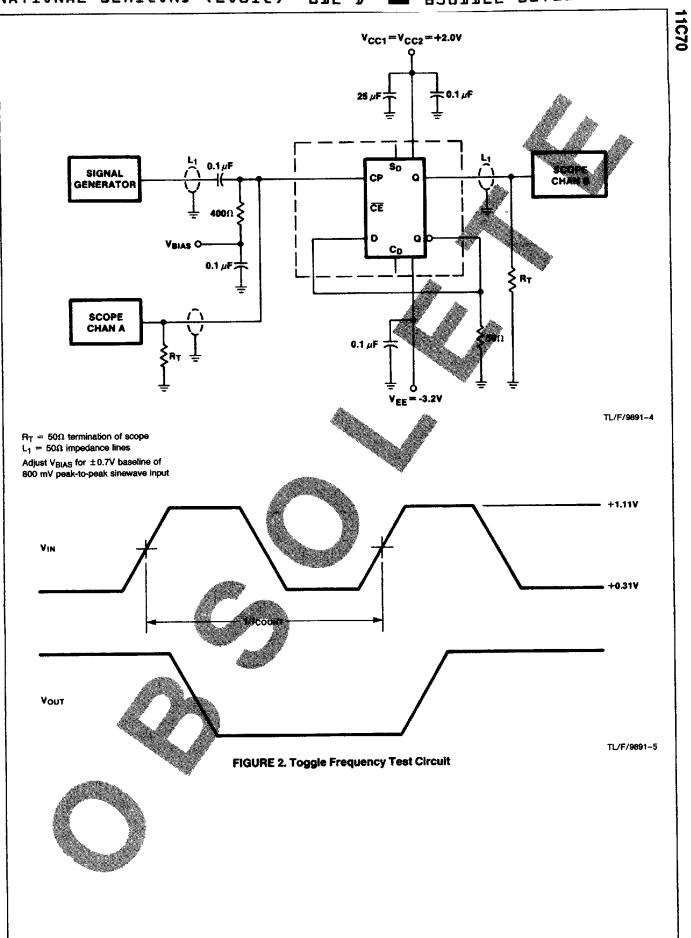

| fTOG (MAX)                      | Toggle Frequency (CP)                                    | 550 | 650 |     | MHz   | See Figure 2        |

Note: This device is guaranteed for  $f_{TOG(max)} \ge 500$  MHz over the 0°C to +75°C temperature range.

## **Functional Description**

Master and slave clock thresholds are internally offset in opposite directions to avoid race conditions or simultaneous master-slave changes when the clock has slow rise or fall times. While the clock is LOW, the slave is in a HOLD condition and information present on the D input is gated into the master. When the clock goes HIGH, it locks the master into its present state, making it insensitive to the D input, causing the new information to appear on the outputs.

The CP and CE inputs are logically identical, but physical constraints associated with the Dual In-Line package make the CE input slower at the upper end of the toggle range. To prevent new data from entering the master on the next CP LOW cycle, CE should be HIGH while CP is still HIGH.

A HIGH signal on SD or CD will override the clocked inputs and force Q or Q, respectively, to go HIGH. If both CD and SD are HIGH, the two output voltages will be somewhere between the HIGH and LOW levels and thus, cannot be usefully defined.

When the input signals for the 11C70 come from other ECL circuits, either 11CXX series or 10K types, these circuits will automatically provide appropriate signal swings, provided, of course, that these circuits are operated within their ratings and that due consideration is given to terminations appropriate to the particular application, as discussed in the F100K ECL Design Guide (Section 5 of Databook).

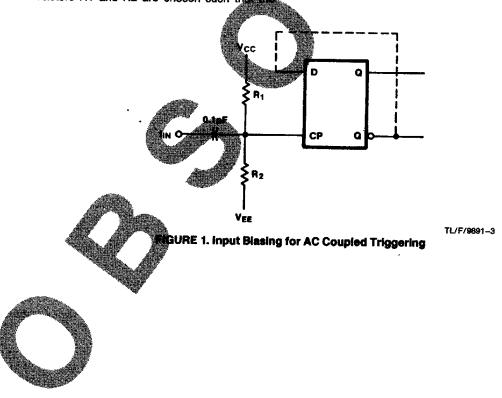

For applications where the clock signal comes from a circuit type other than ECL (in high frequency prescaling, for example) it is generally necessary to use external components to shift the signal levels and center them about the 11C70 input threshold region. A typical biasing scheme is shown in Figure 1. Resistors R1 and R2 are chosen such that it

quiescent voltage at the CP input is -1.3V with respect to the V<sub>CC</sub> terminal of the 11C70. Also indicated is the coupling from Q back to the D input to make a simple toggle. The clock source should be designed to provide a signal swing in the range of 400 mV to 1200 mV, peak-to-peak, over the specified frequency and temperature range. To avoid saturating the input transister and the limiting the frequency capability, the positive peak of the clock should not be more positive than -0.4V with respect to the contraction.

The 11C70 outputs have no internal pull cour resistors. When driving a microstrip line terminated at the tar end by a resistor returned to -2V w.t.  $V_{CC}$ ), the quiescent  $I_{OH}$  current in the line performs the pull-down function when the output starts to go LQM. For series termination or for short unterminated lines, a  $270\Omega$  resistor to  $V_{EE}$  will provide adequate pull-down current. The outputs switch slightly faster when both outputs are equally loaded than if only one output is loaded and and opposite changes in Q and Q load currents tend to cancel the effects of the small inductance of the Voterin.

The test arrangements illustrate the use of split power supplies, with a 27 V<sub>CC</sub> and -3.2V V<sub>EE</sub>. This is done as a matter of instrumentation convenience, since it allows the outputs to be connected via  $50\Omega$  cables directly to the sampling scope inputs, which have  $50\Omega$  internal terminations. By thus avoiding the use of probes, test correlation problems between supplier and user are minimized. In actual polications only a single power supply is needed, and ground can be assigned to V<sub>CC</sub>, as in ECL systems or to V<sub>EE</sub> side as in TTL systems. RF bypass capacitors are recommended in either case.

FIGURE 4. Propagation Delay and S<sub>D</sub> Test Circuit

4-19

TL/F/9891-9

**t**THL