# HD68P01V07, HD68P01V07-1-HD68P01M0, HD68P01M0-1MCU (Microcomputer Unit)

The HD68P01 is an 8-bit single chip microcomputer unit (MCU) which significantly enhances the capabilities of the HMCS6800 family of parts. It can be used in production systems to allow for easy firmware changes with minimum delay or it can be used to emulate the HD6801 for software development It includes 128 bytes of RAM, Serial Communications Interface (SCI), parallel I/O and a three function Programmable Timer on chip, and 2048 bytes, 4096 bytes or 8192 bytes of EPROM on package. It includes an upgrade HD6800 microprocessing unit (MPU) while retaining upward source and object code compatibility. Execution times of key instructions have been improved and several new instructions have been added including an unsigned 8 by 8 multiply with 16-bit result. The HD68P01 can function as a monolithic microcomputer or can be expanded to a 65k byte address space. It is TTL compatible and requires one +5 volt power supply. A summary of HD68P01 features includes:

### FEATURES

- Expanded HMCS6800 Instruction Set

- 8 x 8 Multiply Instruction

- Serial Communications Interface (SCI)

- Upward Source and Object Code Compatible with HD6800

- 16-bit Three-function Programmable Timer

- Applicable to All Type of EPROM 4096 bytes; HN482732A

8192 bytes; HN482764

- 128 Bytes of RAM (64 bytes Retainable on Powerdown)

- 29 Parallel I/O and Two Handshake Control Line

- Internal Clock Generator with Divide-by-Four Output

- Full TTL Compatibility

- Full Interrupt Capability

- Single-Chip or Expandable to 65k Bytes Address Space

- Bus compatible with HMCS6800 Family

### TYPE OF PRODUCTS

| Type No.     | Bus Timing | EPROM Type No. |

|--------------|------------|----------------|

| HD68P01V07   | 1 MHz      | HN482732A-30   |

| HD68P01V07-1 | 1.25MHz    | HN482732A-30   |

| HD68P01M0    | 1 MHz      | HN482764-3     |

| HD68P01M0-1  | 1.25MHz    | HN482764-3     |

Note) EPROM is not attached to the MCU.

# ■ PROGRAM DEVELOPMENT SUPPORT TOOLS

- Cross assembler software for use with IBM PCs and compatibles

- In circuit emulator for use with IBM PCs and compatibles

# ■ PIN ARRANGEMENT (Top View)

# HD68P01V07, HD68P01V07-1

| P23   11   |

|------------|

| Vcc Standb |

# HD68P01M0, HD68P01M0-1

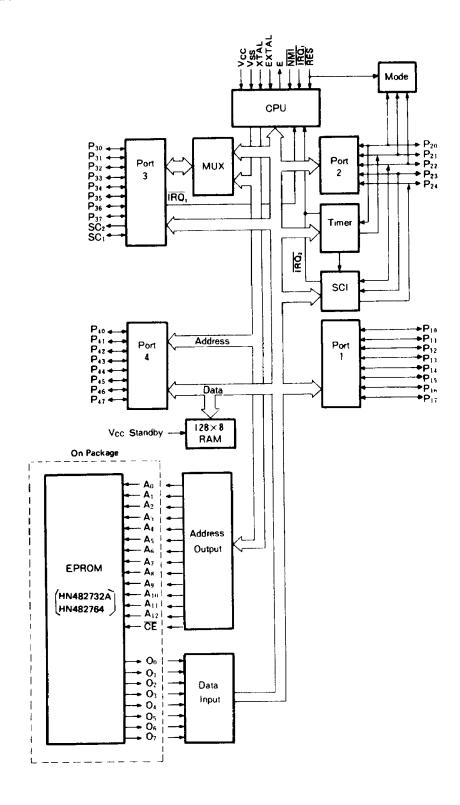

# BLOCK DIAGRAM

# **ABSOLUTE MAXIMUM RATINGS**

| Item                  | Symbol            | Value       | Unit |

|-----------------------|-------------------|-------------|------|

| Supply Voltage        | V <sub>cc</sub> * | -0.3 ~ +7.0 | V    |

| Input Voltage         | V <sub>in</sub> * | -0.3 ~ +7.0 | V    |

| Operating Temperature | Topr              | 0 ~+70      | °c   |

| Storage Temperature   | T <sub>stg</sub>  | -55 ~ +150  | °c   |

<sup>\*</sup> With respect to VSS (SYSTEM GND)

[NOTE] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

# ■ ELECTRICAL CHARACTERISTICS

# • DC CHARACTERISTICS ( $V_{CC}$ =5.0V±5%, $V_{SS}$ = 0V, Ta = 0 $\sim$ +70°C, unless otherwise noted.)

| Ite                      | m                                              | Symbol           | Test Condition                        | min      | typ          | max             | Unit |

|--------------------------|------------------------------------------------|------------------|---------------------------------------|----------|--------------|-----------------|------|

| Innua "High" Valence     | RES                                            |                  |                                       | 4.0      | _            | V <sub>cc</sub> |      |

| Input "High" Voltage     | Other Inputs*                                  | ViH              | ;<br>!                                | 2.0      |              | Vcc             | V    |

| Input "Low" Voltage      | All Inputs*                                    | VIL              | i                                     | -0.3     | _            | 0.8             | V    |

|                          | P <sub>40</sub> ~ P <sub>47</sub>              |                  | 1 0 - 244                             | - 1      | _            | 0.5             |      |

| Input Load Current       | SC <sub>1</sub>                                | [lin]            | Vin = 0 ~ 2.4V                        |          | <del>-</del> | 0.8             | mA   |

|                          | EXTAL                                          |                  | V <sub>in</sub> = 0 ~ V <sub>CC</sub> |          | _            | 1.2             |      |

| Input Leakage Current    | NMI, IRQ <sub>1</sub> , RES                    | t <sub>in</sub>  | V <sub>in</sub> = 0 ~ 5.25V           | <u> </u> | _            | 2,5             | μΑ   |

| Three State (Offset)     | $P_{10} \sim P_{17}, P_{30} \sim P_{37}$       | 11 1             | V <sub>in</sub> = 0.5 ~ 2.4V          | [ - [    | _            | 10              |      |

| Leakage Current          | P <sub>20</sub> ~ P <sub>24</sub>              | I <sub>TSI</sub> | V <sub>in</sub> = 0.5 - 2.4V          |          |              | 100             | μΑ   |

|                          | $P_{30} \sim P_{37}$                           |                  | I <sub>LOAD</sub> = -205 μA           | 2.4      |              |                 |      |

| Output "High" Voltage    | $P_{40} \sim P_{47}$ , E, $SC_1$ , $SC_2$      | VoH              | I <sub>LOAD</sub> = -145 μA           | 2.4      | _            |                 | V    |

|                          | Other Outputs                                  |                  | I <sub>LOAD</sub> = -100 μA           | 2.4      | _            | _               |      |

| Output "Low" Voltage     | All Outputs                                    | Vol              | I <sub>LOAD</sub> = 1.6 mA            |          | _            | 0.5             | V    |

| Darlington Drive Current | P <sub>10</sub> ~ P <sub>17</sub>              | -Іон             | V <sub>out</sub> = 1.5V               | 1.0      | _            | 10.0            | mA   |

| Power Dissipation        |                                                | PD               |                                       | -        |              | 1200            | mW   |

| Janua Canadiana          | $P_{30} \sim P_{37}, P_{40} \sim P_{47}, SC_1$ |                  | V <sub>in</sub> = 0V, Ta = 25°C,      | -        | -            | 12.5            |      |

| Input Capacitance        | Other Inputs                                   | Cin              | f = 1.0 MHz                           | _        |              | 12.5            | pF   |

| Vcc Standby              | Powerdown                                      | V <sub>SBB</sub> |                                       | 4.0      | _            | 5.25            | V    |

| ACC grandoly             | Operating                                      | V <sub>SB</sub>  |                                       | 4.75     | _            | 5.25            | V    |

| Standby Current          | Powerdown                                      | I <sub>SBB</sub> | V <sub>SBB</sub> = 4.0V               | _        | _            | 8.0             | mA   |

<sup>\*</sup>Except Mode Programming Levels: See Figure 8.

# • AC CHARACTERISTICS BUS TIMING $\{V_{CC}=5.0V\pm5\%,\,V_{SS}=0V,\,T_a=0\sim+70^{\circ}C,\,unless\,otherwise\,noted.\}$

|                      |                            |                      | 1              | HD68 | P01V0        | 7/M0     | HD68P       | 01V07-   | 1/M0-1         | Unit     |

|----------------------|----------------------------|----------------------|----------------|------|--------------|----------|-------------|----------|----------------|----------|

|                      | Item                       | Symbol               | Test Condition | min  | typ          | max      | min         | typ      | max            | 0        |

| Cycle Time           |                            | t <sub>cyc</sub>     |                | 1    | -            | 10       | 8.0         |          | 10             | μs       |

| Address Strobe Pul   | se width "High"*           | PWASH                | ]              | 200  | -            |          | 150         |          | _              | ns       |

| Address Strobe Ris   |                            | <sup>t</sup> ASr     |                | 5    |              | 50       | 5           |          | 50             | ns       |

| Address Strobe Fal   | l Time                     | tASf                 |                | 5    |              | 50       | 5           |          | 50             | ns       |

| Address Strobe De    | lay Time*                  | t <sub>ASD</sub>     | 7              | 60   |              |          | 30          |          |                | n:       |

| Enable Rise Time     |                            | t <sub>Er</sub> _    | ]              | 5    |              | 50       | 5           |          | 50             | n:       |

| Enable Fall Time     |                            | t <sub>Ef</sub>      |                | 5    |              | 50       | 5           |          | 50             | n:       |

| Enable Pulse Width   | "High" Time "              | PWEH                 |                | 450  | <b>.</b> – . |          | 340         |          |                | n        |

| Enable Pulse Width   |                            | PWEL                 |                | 450  |              |          | 350         |          |                | n        |

|                      | Enable Delay Time          | tASED                |                | 60   |              |          | 30          |          |                | n        |

| Address Delay Tim    |                            | t AD                 | Fig. 1         | _    |              | 260      |             |          | 260            | _ n      |

| Address Delay Tim    | ne for Latch (f = 1.0MHz)* | t ADL                | Fig. 2         | _    | _            | 270      |             | -        | 260            | n        |

| Data Set-up Write    |                            | t DSW                |                | 225  |              |          | 115         | <u> </u> |                | ļ n      |

| Data Set-up Read     |                            | t <sub>DSR</sub>     |                | 80   | <u> </u>     |          | 70          |          |                | n        |

|                      | Read                       | t HR                 |                | 10   |              | _        | 10          |          |                | ٦,       |

| Data Hold Time       | Write                      | t HW                 |                | 20   |              | <u> </u> | 20          |          | <u> </u>       | <u> </u> |

| Address Set-up Tir   | ne for Latch *             | t ASL                |                | 60   | <u> </u>     | -        | 50          |          |                | n        |

| Address Hold Tim     |                            | t AHL                | 7              | 20   | -            | <u> </u> | 20          |          |                | r        |

| Address Hold Tim     |                            | t <sub>AH</sub>      |                | 20   |              |          | 20          | _        | <u> </u>       | r        |

| Peripheral Read      | Non-Multiplexed Bus *      | (t <sub>ACCN</sub> ) | 7              | _    |              | (610)    | <u> </u>    |          | (420)          | ٦,       |

| Access Time          | Multiplexed Bus *          | (t <sub>ACCM</sub> ) |                | _    |              | (600)    | <del></del> | L        | (420)          | <u> </u> |

| Oscillator stabiliza |                            | t <sub>RC</sub>      | Fig. 11        | 100  | <u> </u>     | <u> </u> | 100         |          | <del>  -</del> | <u></u>  |

| Processor Control    |                            | tpcs                 | Fig. 12        | 200  |              |          | 200         |          | <u> </u>       |          |

These timings change in approximate proportion to toyc. The figures in this characteristics represent those when toyc is minimum (= in the highest speed operation).

# PERIPHERAL PORT TIMING (V<sub>CC</sub> = 5.0V $\pm 5\%$ , V<sub>SS</sub> = 0V, Ta = 0 $\sim$ +70°C, unless otherwise noted.)

| ltem                                                                       |                  | Symbol            | Test Condition | min | typ | max | Unit |

|----------------------------------------------------------------------------|------------------|-------------------|----------------|-----|-----|-----|------|

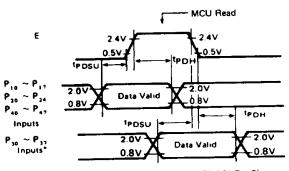

| Peripheral Data Setup Time                                                 | Port 1, 2, 3, 4  | 1 <sub>PDSU</sub> | Fig. 3         | 200 |     | _   | ns   |

| Peripheral Data Hold Time                                                  | Port 1, 2, 3, 4  | t <sub>PDH</sub>  | Fig. 3         | 200 |     |     | ns   |

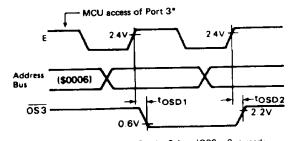

| Delay Time, Enable Positive T<br>to OS3 Negative Transition                | ransition        | t <sub>OSD1</sub> | Fig. 5         | _   | _   | 350 | ns   |

| Delay Time, Enable Positive T<br>to OS3 Positive Transition                | ransition        | t <sub>OSD2</sub> | Fig. 5         | _   | _   | 350 | ns   |

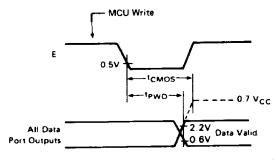

| Delay Time, Enable Negative<br>Transition to Peripheral Data<br>Valid      | Port 1, 2*, 3, 4 | t <sub>PWD</sub>  | Fig. 4         | _   | _   | 400 | ns   |

| Delay Time, Enable Negative<br>Transition to Peripheral<br>CMOS Data Valid | Port 2**, 4      | t <sub>CMOS</sub> | Fig. 4         | _   | _   | 2.0 | μs   |

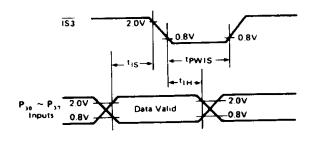

| Input Strobe Pulse Width                                                   | L                | tpwis             | Fig. 6         | 200 |     |     | ns   |

| Input Data Hold Time                                                       | port 3           | t <sub>iH</sub>   | Fig. 6         | 50  |     |     | ns   |

| Input Data Set-up Time                                                     | Port 3           | t <sub>IS</sub>   | Fig. 6         | 20  | _   |     | ns   |

<sup>\*</sup>Except P21 \*\*10k\O pull up register required for Port 2

TIMER, SCI TIMING (V<sub>CC</sub> = 5.0V  $\pm$ 5%, V<sub>SS</sub> = 0V, Ta = 0  $\sim$  +70°C, unless otherwise noted.)

| ltem                                                | Symbol            | Test Condition | min                     | typ | max | Unit              |

|-----------------------------------------------------|-------------------|----------------|-------------------------|-----|-----|-------------------|

| Timer Input Pulse Width                             | tpwT              |                | 2 t <sub>cvc</sub> +200 | _   | -   | ns                |

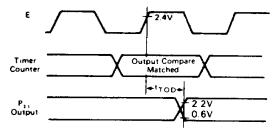

| Delay Time, Enable Positive Transition to Timer Out | t <sub>TOD</sub>  | Fig. 7         | -                       | _   | 600 | ns                |

| SCI Input Clock Cycle                               | t <sub>Scyc</sub> |                | 1                       |     | _   | t <sub>cyc</sub>  |

| SCI Input Clock Pulse Width                         | tpwsck            |                | 0.4                     |     | 0.6 | t <sub>Scyc</sub> |

# MODE PROGRAMMING $\{V_{CC} = 5.0V \pm 5\%, V_{SS} = 0V, T_a = 0 \sim +70^{\circ}C, unless otherwise noted.\}$

| Item                  |                      | Symbol           | Test Condition | min | typ      | max | Unit                                             |

|-----------------------|----------------------|------------------|----------------|-----|----------|-----|--------------------------------------------------|

| Mode Programming Inpu | it "Low" Voltage     | V <sub>MPL</sub> |                | _   | _        | 1.7 | V                                                |

| Mode Programming Inpu |                      | V <sub>MPH</sub> |                | 4.0 | <u> </u> | _   | V                                                |

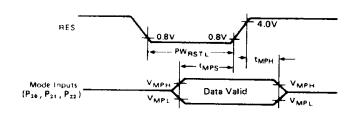

| RES "Low" Pulse Width |                      | PWRSTL           | Fig. 8         | 3.0 | †        |     | t <sub>cyc</sub>                                 |

| Mode Programming Set- | up Time              | TMPS             |                | 2.0 |          |     | t <sub>cyc</sub>                                 |

| Mode Programming      | RES Rise Time ≥ 1 µs |                  |                | 0   | _        | _   | <del>                                     </del> |

| Hold Time             | RES Rise Time < 1μs  | <sup>t</sup> MPH |                | 100 | <b>†</b> |     | ns                                               |

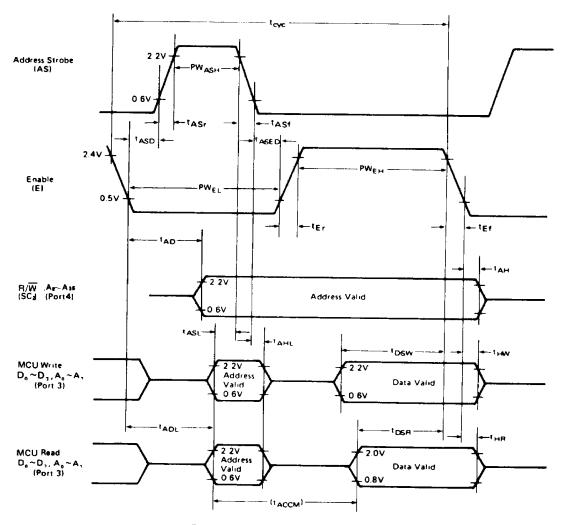

Figure 1 Expanded Multiplexed Bus Timing

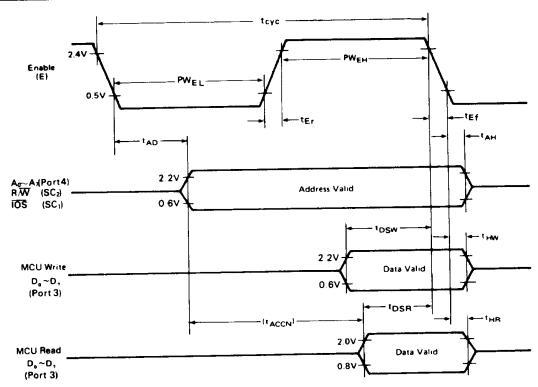

Figure 2 Expanded Non-Multiplexed Bus Timing

\*Port 3 Non-Latched Operation (LATCH ENABLE = 0)

Figure 3 Data Set-up and Hold Times (MCU Read)

\*Access matches Output Strobe Select (OSS = 0, a read, OSS = 1, a write)

Figure 5 Port 3 Output Strobe Timing (Single Chip Mode)

(NOTE) 1. 10 k $\Omega$  Pullup resistor required for Port 2 to reach 0.7 V<sub>CC</sub> 2. Not applicable to P<sub>21</sub> 3. Port 4 cannot be pulled above V<sub>CC</sub>

Figure 4 Port Data Delay Timing (MCU Write)

Figure 6 Port 3 Latch Timing (Single Chip Mode)

Figure 7 Timer Output Timing

Figure 8 Mode Programming Timing

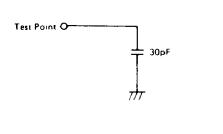

(a) CMOS Load

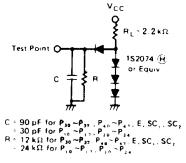

(b) TTL Load

Figure 9 Bus Timing Test Loads

# INTRODUCTION

The HD68P01 is an 8-bit monolithic microcomputer which can be configured to function in a wide variety of applications. The facility which provides this extraordinary flexibility is its ability to be hardware programmed into eight different operating modes. The operating mode controls the configuration of 18 of the MCU's 40 pins, available on-chip resources, memory map, location (internal or external) of interrupt vectors, and type of external bus. The configuration of the remaining 22 pins is not dependent on the operating mode.

Twenty-nine pins are organized as three 8-bit ports and one 5-bit port. Each port consists of at least a Data Register and a write-only Data Direction Register. The Data Direction Register is used to define whether corresponding bits in the Data Register are configured as an input (clear) or output (set).

The term "port", by itself, refers to all of its associated hardware. When the port is used as a "data port" or "I/O port", it is controlled by its Data Direction Register and the programmer has direct access to its pins using the port's Data Register. Port pins are labled as Pij where i identifies one of four ports and j indicates the particular bit.

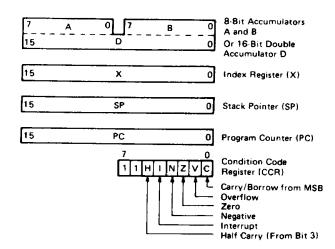

The Microprocessor Unit (MPU) is an enhanced HD6800 MPU with additional capabilities and greater throughput. It is upward source and object code compatible with the HD6800. The programming model is depicted in Figure 10 where Accumulator D is a concatenation of Accumulators A and B. A list of new operations added to the HMCS6800 instruction set are shown in Table 8.

The basic difference between the HD6801 and the HD68P01 is that the HD6801 has an on-chip ROM while the HD68P01 has

an on the package EPROM. The HD68P01 is pin and code compatible with the HD6801 and can be used to emulate the HD6801, allowing easy software development using the onpackage EPROM. Software developed using the HD68P01 can then be masked into the HD6801 ROM.

Figure 10 HD68P01 Programming Model

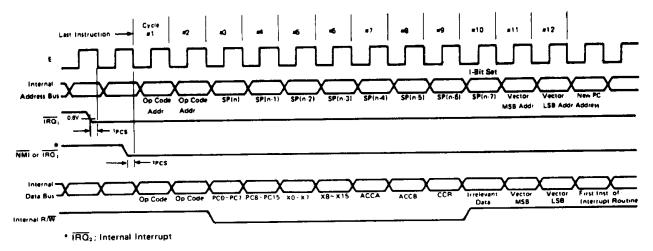

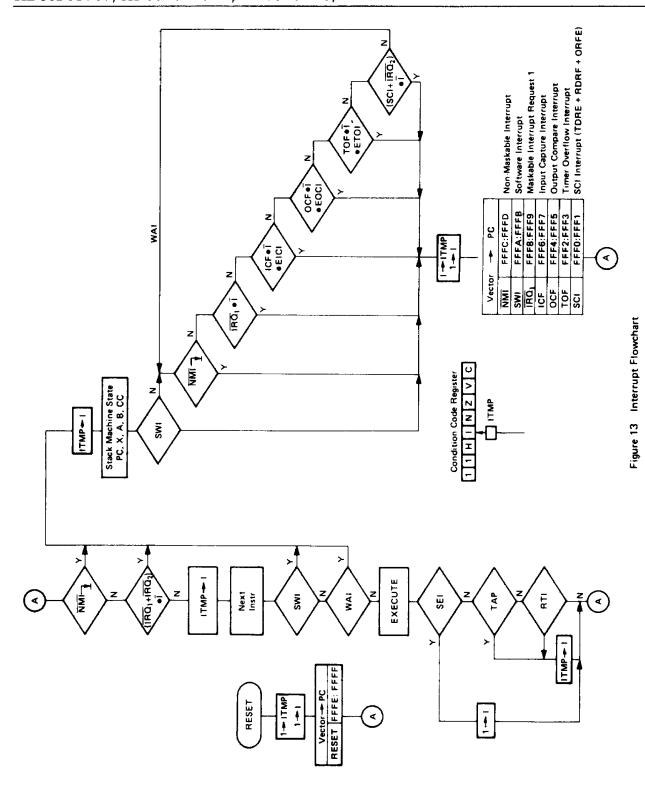

### ■ INTERRUPTS

The MCU supports two types of interrupt requests: maskable and non-maskable. A Non-Maskable Interrupt ( $\overline{NMI}$ ) is always recognized and acted upon at the completion of the current instruction. Maskable interrupts are controlled by the Condition Code Register's I-bit and by individual enable bits. The I-bit controls all maskable interrupts. Of the maskable interrupts, there are two types:  $\overline{IRQ_1}$  and  $\overline{IRQ_2}$ . The Programmable Timer and Serial Communications Interface use an internal  $\overline{IRQ_2}$  interrupt line, as shown in BLOCK DIAGRAM. External devices (and  $\overline{IS3}$ ) use  $\overline{IRQ_1}$ . An  $\overline{IRQ_1}$  interrupt is serviced before  $\overline{IRQ_2}$  if both are pending.

All IRQ<sub>2</sub> interrupts use hardware prioritized vectors. The single SCI interrupt and three timer interrupts are serviced in a prioritized order where each is vectored to a separate location. All MCU interrupt vector locations are shown in Table 1.

The Interrupt flowchart is depicted in Figure 13 and is common to every MCU interrupt excluding Reset. The Program Counter, Index Register, A Accumulator, B Accumulator, and Condition Code Register are pushed to the stack. The I-bit is

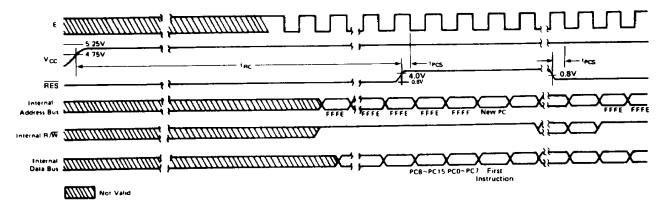

set to inhibit maskable interrupts and a vector is fetched corresponding to the current highest priority interrupt. The vector is transferred to the Program Counter and instruction execution is resumed. Interrupt and RES timing is illustrated in Figure 11 and 12

Table 1 Interrupt Vector Locations

| MSB  | LSB  | Interrupt                 |

|------|------|---------------------------|

| FFFE | FFFF | RES                       |

| FFFC | FFFD | NMI                       |

| FFFA | FFFB | Software Interrupt (SWI)  |

| FFF8 | FFF9 | IRQ <sub>1</sub> (or IS3) |

| FFF6 | FFF7 | ICF (Input Capture)       |

| FFF4 | FFF5 | OCF (Output Compare)      |

| FFF2 | FFF3 | TOF (Timer Overflow)      |

| FFF0 | FFF1 | SCI (RDRF + ORFE + TDRE)  |

Figure 11 Interrupt Sequence

Figure 12 Reset Timing

# FUNCTIONAL PIN DESCRIPTIONS

V<sub>CC</sub> and V<sub>SS</sub> provide power to a large portion of the MCU. The power supply should provide +5 volts (±5%) to V<sub>CC</sub>, and VSS should be tied to ground. Total power dissipation (including  $V_{CC}$  Standby), will not exceed  $P_D$  milliwatts.

# V<sub>CC</sub> Standby

VCC Standby provides power to the standby portion (\$80 through \$BF) of the RAM and the STBY PWR and RAME bits of the RAM Control Register. Voltage requirements depend on whether the MCU is in a powerup or powerdown state. In the powerup state, the power supply should provide +5 volts (±5%) and must reach VSB volts before RES reaches 4.0 volts. During powerdown, VCC Standby must remain above VSBB (min) to sustain the standby RAM and STBY PWR bit. While in powerdown operation, the standby current will not exceed ISBB.

It is typical to power both V<sub>CC</sub> and V<sub>CC</sub> Standby from the same source during normal operation. A diode must be used between them to prevent supplying power to V<sub>CC</sub> during powerdown operation. VCC Standby should be tied to either ground or V<sub>CC</sub> in Mode 3.

Figure 14 Battery Backup for V<sub>CC</sub> Standby

# RAM Control Register (\$14)

The RAM Control Register includes two bits which can be used to control RAM accesses and determine the adequacy of the standby power source during powerdown operation. It is intended that RAME be cleared and STBY PWR be set as part of a powerdown procedure.

|      |      | RA | M Contr | ol Regis | ter |   |   |

|------|------|----|---------|----------|-----|---|---|

| 7    | 6    | 5  | 4       | 3        | 2   | 1 | 0 |

| STBY | RAME | х  | х       | х        | х   | х | х |

Bit 0~5 Not Used Bit 6 RAME

RAM Enable. This Read/Write bit can be used to remove the entire RAM from the internal memory map. RAME is set (enabled) during Reset provided standby power is available on the positive edge of RES. If RAME is clear, any access to a RAM address is external. If RAME is set and not in Mode 3, the RAM is included in the internal map.

Bit 7 STBY PWR

Standby Power. This bit is a Read/Write status bit which is cleared whenever VCC Standby decreases below VSBB (min). It can be set only by software and is not affected by RES.

# XTAL and EXTAL

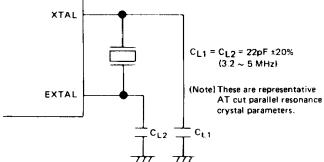

These two input pins interface either a crystal or TTL com-

patible clock to the MCU's internal clock generator. Divide-byfour circuitry is included which allows use of the inexpensive 3.58 MHz Color Burst TV crystals. A 22 pF capacitor is required from each crystal pin to ground to ensure reliable startup and operation. Alternatively, EXTAL may be driven with an external TTL compatible clock with a duty cycle of 45% ~ 55% with XTAL connected to ground.

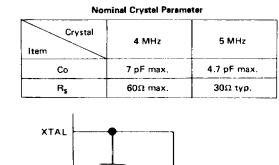

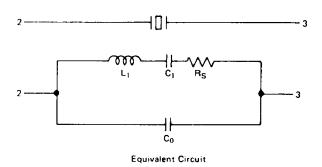

The internal oscillator is designed to interface with an AT-cut quartz crystal resonator or a ceramic resonator operated in parallel resonance mode in the frequency range specified for 3.2 ~ 4 MHz. The crystal should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time. The MCU is compatible with most commercially available crystals and ceramic resonators and nominal crystal parameters are shown in Figure 15.

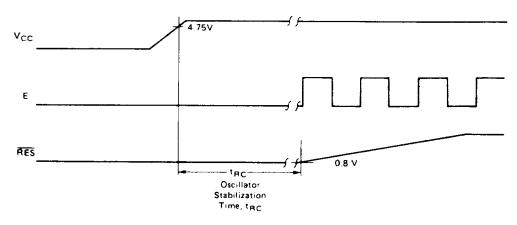

### • RES

This input is used to reset the MCU's internal state and provide an orderly startup procedure. During powerup, RES must be held below 0.8 volts: (1) at least tRC after VCC reaches 4.75 volts in order to provide sufficient time for the clock generator to stabilize, and (2) until V<sub>CC</sub> Standby reaches 4.75 volts. RES must be held low at least three E-cycles if asserted during pow-

When a "High" level is detected, the MCU does the following:

- 1) All the higher order address lines will be forced "High".

- 2) I/O Port 2 bits, 2, 1, and 0 are latched into programmed control bits PC2, PC1 and PC0.

- 3) The last two (\$FFFE, \$FFFF) locations in memory will be used to load the program addressed by the program

- 4) The interrupt mask bit is set; must be cleared before the CPU can recognize maskable interrupts.

### ● E (Enable)

This is an output clock used primarily for bus synchronization. It is TTL compatible and is the slightly skewed divide-byfour result of the MCU input frequency. It will drive one Schottky TTL load and 90 pF, and all data given in cycles is referenced to this clock unless otherwise noted.

# • NMI (Non-Maskable Interrupt)

An NMI negative edge request an CPU interrupt sequence, but the current instruction will be completed before it responds to the request. The CPU will then begin an interrupt sequence. Finally, a vector is fetched from \$FFFC and \$FFFD, transferred to the Program Counter and instruction execution resumes.  $\overline{\text{NMI}}$  typically requires a 3.3 k $\Omega$  (nominal) resistor to V<sub>CC</sub>. There is no internal NMI pullup resistor. NMI must be held low for at least one E-cycle to be recognized under all conditions.

# IRQ1 (Maskable Interrupt Request 1)

IRQ1 is a level-sensitive input which can be used to request an interrupt sequence. The CPU will complete the current instruction before it responds to the request. If the interrupt mask bit (I-bit) in the Condition Code Register is clear, the CPU will begin an interrupt sequence. Finally, a vector is fetched from \$FFF8 and \$FFF9, transferred to the Program Counter, and instruction execution is resumed.

$1R\overline{Q}_1$  typically requires an external 3.3 k $\Omega$  (nominal) resistor to  $V_{CC}$  for wire-OR application.  $\overline{IRQ}_i$  has no internal pullup resistor.

# • SC1 and SC2 (Strobe Control 1 and 2)

The function of  $SC_1$  and  $SC_2$  depends on the operating mode.  $SC_1$  is configured as an output in all modes except single chip mode, whereas  $SC_2$  is always an output.  $SC_1$  and  $SC_2$  can drive one Schottky load and 90 pF.

# SC<sub>1</sub> and SC<sub>2</sub> in Single Chip Mode

In Single Chip Modes,  $SC_1$  and  $SC_2$  are configured as an input and output, respectively, and both function as Port 3 control lines.  $SC_1$  functions as  $\overline{IS3}$  and can be used to indicate that Port 3 input data is ready or output data has been accepted. Three options associated with  $\overline{IS3}$  are controlled by Port 3's Control and Status Register and are discussed in Port 3's description. If unused,  $\overline{IS3}$  can remain unconnected.

$SC_2$  is configured as  $\overline{OS3}$  and can be used to strobe output data or acknowledge input data. It is controlled by Output Strobe Select (OSS) in Port 3's Control and Status Register. The strobe is generated by a read (OSS= 0) or write (OSS= 1) to Port 3's Data Register.  $\overline{OS3}$  timing is shown in Figure 5.

# SC1 and SC2 in Expanded Non-Multiplexed Mode

In the Expanded Non-Multiplexed Mode, both  $SC_1$  and  $SC_2$  are configured as outputs.  $SC_1$  functions as Input/Output Select ( $\overline{IOS}$ ) and is asserted only when \$0100 through \$01FF is sensed on the internal address bus.

$SC_2$  is configured as Read/Write and is used to control the direction of data bus transfers. An CPU read is enabled when Read/Write and E are high.

# SC<sub>1</sub> and SC<sub>2</sub> in Expanded Multiplexed Mode

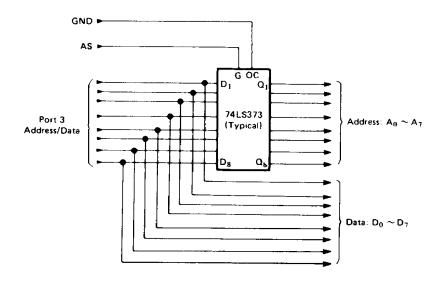

In the Expanded Multiplexed Modes, both  $SC_1$  and  $SC_2$  are configured as outputs.  $SC_1$  functions as Address Strobe and can be used to demultiplex the eight least significant addresses and the data bus. A latch controlled by Address Strobe captures address on the negative edge, as shown in Figure 20.

$SC_2$  is configured as Read/Write and is used to control the direction of data bus transfers. An CPU read is enabled when Read/Write and E are high.

(a) Nominal Recommended Crystal Parameters

(b) Oscillator Stabilization Time (tRC)

Figure 15 Oscillator Characteristics

# PORTS

There are four I/O ports on the MCU; three 8-bit ports and one 5-bit port. There are two control lines associated with one of the 8-bit ports. Each port has an associated write only Data Direction Register which allows each I/O line to be programmed to act as an input or an output. A "1" in the corresponding Data Direction Register bit will cause that I/O line to be an output. A "0" in the corresponding Data Direction Register bit will cause the I/O line to be an input. There are four ports: Port 1, Port 2, Port 3, and Port 4. Their addresses and the addresses of their Data Direction registers are given in Table 2.

Table 2 Port and Data Direction Register Addresses

| Ports      | Port Address | Data Direction<br>Register Address |

|------------|--------------|------------------------------------|

| I/O Port 1 | \$0002       | \$0000                             |

| I/O Port 2 | \$0003       | \$0001                             |

| I/O Port 3 | \$0006       | \$0004                             |

| 1/O Port 4 | \$0007       | \$0005                             |

P10~P17 (Port 1)

Port 1 is a mode independent 8-bit I/O port where each line is an input or output as defined by its Data Direction Register. The TTL compatible three-state output buffers can drive one Schottky TTL load and 30 pF, Darlington transistors, or CMOS devices using external pullup resistors. It is configured as a data input port by RES. Unused lines can remain unconnected.

# P<sub>20</sub>~P<sub>24</sub> (Port 2)

Port 2 is a mode independent 5-bit I/O port where each line is configured by its Data Direction Register. During RES, all lines are configured as inputs. The TTL compatible three-state output buffers can drive one Schottky TTL load and 30 pF or CMOS devices using external pullup resistors. P<sub>20</sub>, P<sub>21</sub> and P<sub>22</sub> must always be connected to provide the operating mode. If lines P<sub>23</sub> and P<sub>24</sub> are unused, they can remain unconnected.

P<sub>20</sub>, P<sub>21</sub>, and P<sub>22</sub> provide the operating mode which is latched into the Program Control Register on the positive edge of RES. The mode may be read from Port 2 Data Register as shown where PC2 is latched from pin 10.

Port 2 also provides an interface for the Serial Communications Interface and Timer. Bit 1, if configured as an output, is dedicated to the timer's Output Compare function and cannot be used to provide output from Port 2 Data Register.

Port 2 Data Register

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |                |

|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| PC2 | PC1 | PCO | P24 | P23 | P22 | P21 | P20 | <b>\$000</b> 3 |

# • P<sub>30</sub> ~P<sub>37</sub> (Port 3)

Port 3 can be configured as an I/O port, a bidirectional 8-bit data bus, or a multiplexed address/data bus depending on the operating mode. The TTL compatible three-state output buffers can drive one Schottky TTL load and 90 pF. Unused lines can remain unconnected.

# Port 3 in Single-Chip Mode

Port 3 is an 8-bit I/O port in Single-Chip Mode where each line is configured by its Data Direction Register. There are also

two lines, 183 and 083, which can be used to control Port 3 data transfers.

Three Port 3 options are controlled by the Port 3 Control and Status Register and available only in Single-Chip Mode: (1) Port 3 input data can be latched using  $\overline{1S3}$  as a control signal, (2)  $\overline{OS3}$  can be generated by either an CPU read or write to Port 3's Data Register, and (3) an  $\overline{1RQ_1}$  interrupt can be enabled by an  $\overline{1S3}$  negative edge. Port 3 latch timing is shown in Figure 6.

Port 3 Control and Status Register

| 7           | 6                                 | 5 | 4   | 3               | 2 | 1 | 0 |        |

|-------------|-----------------------------------|---|-----|-----------------|---|---|---|--------|

| īS3<br>Flag | IS3<br>IRQ <sub>1</sub><br>Enable | х | oss | Latch<br>Enable | × | × | × | \$000F |

| Dis 0 0      | Not used.                                    |

|--------------|----------------------------------------------|

| Bit 0~2      |                                              |

| Bit 3        | LATCH ENABLE. This bit controls the in-      |

|              | put latch for Port 3. If set, input data is  |

|              | latched by an IS3 negative edge. The latch   |

|              | is transparent after a read of Port 3's Data |

|              | Register. LATCH ENABLE is cleared by         |

|              | RES.                                         |

| Bit 4        | OSS (Output Strobe Select). This bit deter-  |

| <b>211</b> , | mines whether OS3 will be generated by a     |

|              | read or write of Port 3's Data Register.     |

|              | When clear, the strobe is generated by a     |

|              | when clear, the strope is generated by       |

|              | read; when set, it is generated by a write.  |

|              | OSS is cleared by RES.                       |

| Bit 5        | Not used.                                    |

| Bit 6        | IS3 IRQ, ENABLE. When set, an IRQ,           |

| <b>2</b> 0   | interrupt will be enabled whenever IS3       |

|              | FLAG is set; when clear, the interrupt is    |

|              | inhibited. This bit is cleared by RES.       |

| Bit 7        | IS3 FLAG. This read-only status bit is set   |

|              | by an IS3 negative edge. It is cleared by a  |

|              | read of the Port 3 Control and Status        |

|              | Register (with 153 FLAG set) followed by     |

|              | a read or write to Port 3's Data Register or |

|              |                                              |

|              | by RES.                                      |

# Port 3 in Expanded Non-Multiplexed Mode

Port 3 is configured as a bidirectional data bus  $(D_0 \sim D_7)$  in the Expanded Non-Multiplexed Mode. The direction of data transfers is controlled by Read/Write  $(SC_2)$  and clocked by E (Enable).

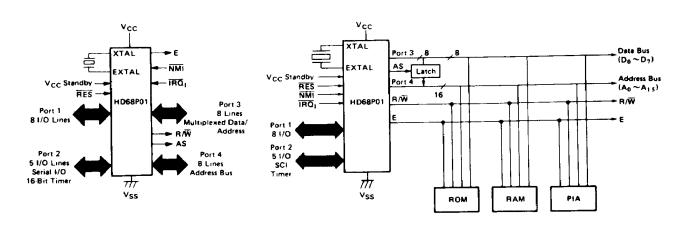

# Port 3 in Expanded Multiplexed Mode

Port 3 is configured as a time multiplexed address  $(A_0 \sim A_7)$  and data bus  $(D_0 \sim D_7)$  in Expanded Multiplexed Mode where Address Strobe (AS) can be used to demultiplex the two buses. Port 3 is held in a high impedance state between valid address and data to prevent potential bus conflicts.

# • P<sub>40</sub>~P<sub>47</sub> (Port 4)

Port 4 is configured as an 8-bit I/O port, address outputs, or data inputs depending on the operating mode. Port 4 can drive one Schottky TTL load and 90 pF and is the only port with internal pullup resistors. Unused lines can remain unconnected.

# Port 4 in Single Chip Mode

In Single Chip Mode, Port 4 functions as an 8-bit I/O port where each line is configured by its Data Direction Register.

Internal pullup resistors allow the port to directly interface with CMOS at 5 volt levels. External pullup resistors to more than 5 volts, however, cannot be used.

# Port 4 in Expanded Non-Multiplexed Mode

Port 4 is configured from RES as an 8-bit input port where its Data Direction Register can be written to provide any or all of address lines, A<sub>0</sub> to A<sub>7</sub>. Internal pullup resistors are intended to pull the lines high until its Data Direction Register is configured.

### Port 4 in Expanded Multiplexed Mode

In all Expanded Multiplexed modes except Mode 6, Port 4 functions as half of the address bus and provides  $A_8$  to  $A_{15}$ . In Mode 6, the port is configured from RES as an 8-bit parallel input port where its Data Direction Register can be written to provide any or all of address lines,  $A_8$  to  $A_{15}$ . Internal pullup resistors are intended to pull the lines high until its Data Direction Register is configured where bit 0 controls  $A_8$ .

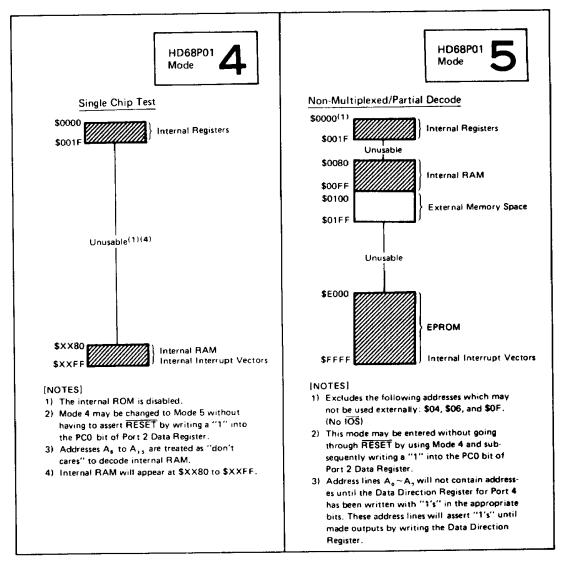

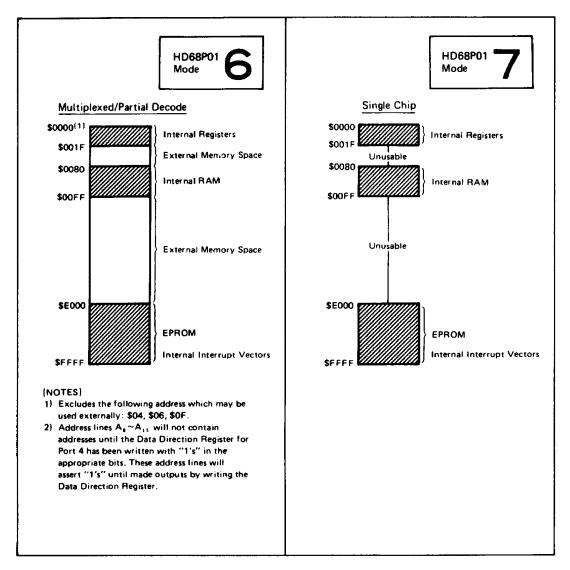

### OPERATING MODES

The MCU provides eight different operating modes which are selectable by hardware programming and referred to as Mode 0 through Mode 7. The operating mode controls the memory map, configuration of Port 3, Port 4,  $SC_1$ ,  $SC_2$ , and the physical location of interrupt vectors.

### Fundamental Modes

The MCU's eight modes can be grouped into three fundamental modes which refer to the type of bus it supports: Single Chip, Expanded Non-Multiplexed, and Expanded Multiplexed. Single chip modes include 4 and 7, Expanded Non-Multiplexed is Mode 5 and the remaining five are Expanded Multiplexed modes. Table 3 summarizes the characteristics of the operating modes.

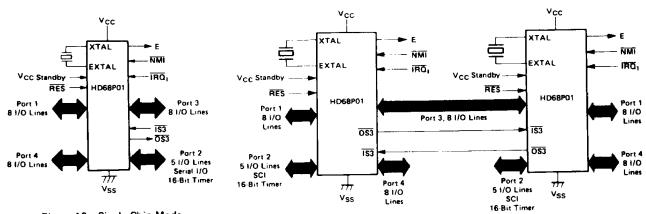

# Single Chip Modes (4, 7)

In Single-Chip Mode, the MCU's four ports are configured as parallel input/output data ports, as shown in Figure 16. The MCU functions as a monolithic microcomputer in these two modes without external address or data buses. A maximum of 29 I/O lines and two Port 3 control lines are provided. In addition to other peripherals, another MCU can be interfaced to Port 3 in a loosely coupled dual processor configuration, as shown in Figure 17.

In Single-Chip Test Mode (4), the RAM responds to \$xx80 through \$xxFF and the ROM is removed from the internal address map. A test program must first be loaded into the RAM using modes 0, 1, 2, or 6. If the MCU is Reset and then programmed into Mode 4, execution will begin at \$xxFE: xxFF. Mode 5 can be irreversibly entered from Mode 4 without going through Reset by setting bit 5 of Port 2's Data Register. This mode is used primarily to test Ports 3 and 4 in the Single-Chip and Non-Multiplexed Modes.

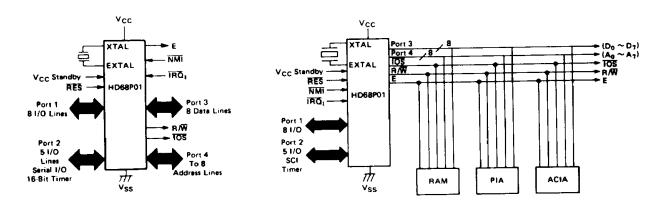

# **Expanded Non-Multiplexed Mode (5)**

A modest amount of external memory space is provided in the Expanded Non-Multiplexed Mode while retaining significant on-chip resources. Port 3 functions as an 8-bit bidirectional data bus and Port 4 is configured as an input data port. Any combination of the eight least-significant address lines may be obtained by writing to Port 4's Data Direction Register. Stated alternatively, any combination of  $A_0$  to  $A_2$  may be provided while retaining the remainder as input data lines. Internal pull-

up resistors are intended to pull Port 4's lines high until it is configured.

Figure 18 illustrates a typical system configuration in the Expanded Non-Multiplexed Mode. The MCU interfaces directly with HMCS6800 family parts and can access 256 bytes of external address space at \$100 through \$1FF. IOS provides an address decode of external memory (\$100-\$1FF) and can be used similarly to an address or chip select line.

Table 3 Summary of HD6800 Operating Modes

# Common to all Modes: Reserved Register Area Port 1 Port 2 Programmable Timer

Serial Communication Interface

| Single Chip Mode 7                                   |

|------------------------------------------------------|

| 128 bytes of RAM; 2048 bytes of ROM                  |

| Port 3 is a parallel I/O port with two control lines |

| Port 4 is a parallel I/O port                        |

|                                                      |

SC<sub>1</sub> is Input Strobe 3 (IS3) SC<sub>2</sub> is Output Strobe 3 (OS3)

# Expanded Non-Multiplexed Mode 5 128 bytes of RAM; 2048 bytes of ROM 256 bytes of external memory space Port 3 is an 8-bit data bus Port 4 is an input port/address bus SC<sub>1</sub> is (nput/Output Select (IOS)

# Expanded Multiplexed Modes 1, 2, 3, 6

Four memory space options (65k address space):

- (1) No internal RAM or ROM (Mode 3)

- (2) Internal RAM, no ROM (Mode 2)

- (3) Internal RAM and ROM (Mode 1)

- (4) Internal RAM, ROM with partial address bus (Mode 6)

Port 3 is a multiplexed address/data bus

Port 4 is an address bus (inputs/address in Mode 6) SC<sub>1</sub> is Address Strobe (AS)

SC<sub>2</sub> is Read/Write (R/W)

SC<sub>2</sub> is read/write (R/W)

### Test Modes 0 and 4

Expanded Multiplexed Test Mode 0

May be used to test RAM and ROM

Single Chip and Non-Multiplexed Test Mode 4

- (1) May be changed to Mode 5 without going through Reset

- (2) May be used to test Ports 3 and 4 as I/O ports

# Expanded-Multiplexed Modes (0, 1, 2, 3, 6)

In the Expanded-Multiplexed Modes, the MCU has the ability to access a 65k bytes memory space. Port 3 functions as a time multiplexed address/data bus with address valid on the negative edge of Address Strobe (AS) and the data bus valid while E is high. In Modes 0 to 3, Port 4 provides address lines  $\underline{A_8}$  to  $\underline{A_{15}}$ . In Mode 6, however, Port 4 is configured during RES as data port inputs and the Data Direction Register can be changed to provide any combination of address lines,  $\underline{A_8}$  to  $\underline{A_{15}}$ . Stated alternatively, any subset of  $\underline{A_8}$  to  $\underline{A_{15}}$  can be provided while retaining the remainder as input data lines. Internal pullup resistors are intended to pull Port 4's lines high until software configures the port.

Figure 19 depicts a typical configuration for the Expanded-Multiplexed Modes. Address Strobe can be used to control a transparent D-type latch to capture addresses  $A_0$  to  $A_7$ , as shown in Figure 20. This allows Port 3 to function as a Data Bus when E is high.

In Mode 0, the Reset vector is external for the first two Ecycles after the positive edge of RES and internal thereafter. In

addition, the internal and external data buses are connected and there must be no memory map overlap to avoid potential bus conflicts. Mode 0 is used primarily to verify the ROM pattern

and monitor the internal data bus with the automated test equipment.

Figure 16 Single Chip Mode

Figure 17 Single Chip Dual Processor Configuration

Figure 18 Expanded Non-Multiplexed Configuration

Figure 19 Expanded Multiplexed Configuration

**Function Table** Output Enable Output D Control G Q н н н Ł L 1 L L X  $Q_0$

Figure 20 Typical Latch Arrangement

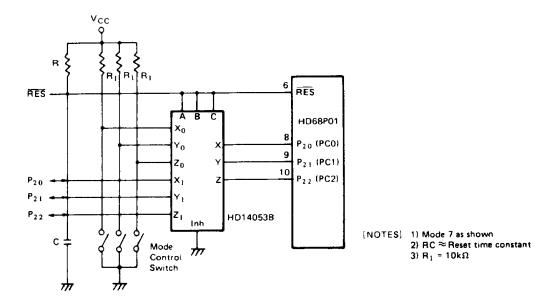

# Programming The Mode

The operating mode is programmed by the levels asserted on  $P_{22}$ ,  $P_{21}$ , and  $P_{20}$  which are latched into PC2, PC1, and PC0 of the program control register on the positive edge of  $\overline{RES}$ . The operating mode may be read from Port 2 Data Register as shown below, and programming levels and timing must be met as shown in Figure 8. A brief outline of the operating modes is shown in Table 4.

Circuitry to provide the programming levels is dependent primarily on the normal system usage of the three pins. If configured as outputs, the circuit shown in Figure 21 may be used; otherwise, three-state buffers can be used to provide isolation while programming the mode.

Port 2 Data Register

| _ | _7  | -6  | 5   | 4   | 3   | 2   | 1   | 0   |                |

|---|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

|   | PC2 | PC1 | PC0 | P24 | P23 | P22 | P21 | P20 | <b>\$000</b> 3 |

Table 4 Mode Selection Summary

| Mode | P <sub>22</sub><br>(PC2) | P <sub>21</sub><br>(PC1) | P <sub>20</sub> (PC0) | ROM  | RAM  | Interrupt<br>Vectors | Bus<br>Mode        | Operating Mode                 |

|------|--------------------------|--------------------------|-----------------------|------|------|----------------------|--------------------|--------------------------------|

| 7    | н                        | Н                        | Н                     | 1    | ı    | ı                    | 1                  | Single Chip                    |

| 6    | Н                        | Н                        | L                     | ī —  | 1    | ı                    | MUX(5, 6)          | Multiplexed/Partial Decode     |

| 5    | н                        | L                        | Н                     | ı    | ı    | 1                    | NMUX(5, 6)         | Non-Multiplexed/Partial Decode |

| 4    | н                        | L                        | L                     | 1(2) | J(1) | I                    | 1                  | Single Chip Test               |

| 3    | L                        | Н                        | н                     | E    | E    | E                    | MUX(4)             | Multiplexed /No RAM or ROM     |

| 2    | L                        | Н                        | L                     | E    | ı    | E                    | MUX(4)             | Multiplexed /RAM               |

| 1    | L                        | L                        | Н                     | ı    | ī    | E                    | MUX <sup>(4)</sup> | Multiplexed/RAM & ROM          |

| 0    | L                        | L                        | L                     | Ī    | 1    | [(3)                 | MUX(4)             | Multiplexed Test               |

# Legend:

- 1 Internal

- E External

- MUX Multiplexed NMUX — Non-Multiplexed

- L -- Logic "0"

- H Logic "1"

### Notes

- (1) Internal RAM is addressed at \$XX80

- (2) Internal ROM is disabled

- (3) RES vector is external for 2 cycles after RES goes high

- (4) Addresses associated with Ports 3 and 4 are considered external in Modes 0, 1, 2, and 3

- (5) Addresses associated with Port 3 are considered external in Modes 5 and 6

- (6) Port 4 default is user data input; address output is optional by writing to Port 4 Data Direction Register

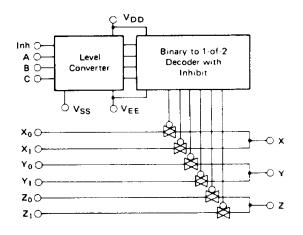

Figure 21 Recommended Circuit for Mode Selection

| Truth Table |      |      |    |                |      |                  |  |  |  |  |  |

|-------------|------|------|----|----------------|------|------------------|--|--|--|--|--|

| Cantr       | ol I | npu  | t  | 00             | Swit | ch               |  |  |  |  |  |

|             | s    | elec | ;t | 011            | JWII |                  |  |  |  |  |  |

| Inhibit     | С    | В    | Α  | HD140538       |      |                  |  |  |  |  |  |

| 0           | 0    | 0    | 0  | Z <sub>0</sub> | ٧0   | Χo               |  |  |  |  |  |

| 0           | 0    | 0    | 1  | Z <sub>0</sub> | Yo   | Xi               |  |  |  |  |  |

| 0           | 0    | 1    | 0  | Zo             | Υı   | Χo               |  |  |  |  |  |

| 0           | 0    | 1    | 1  | Zo             | Yı   | Χı               |  |  |  |  |  |

| 0           | 1    | 0    | 0  | Z <sub>1</sub> | Yo   | Χo               |  |  |  |  |  |

| 0           | 1    | 0    | 1  | Zı             | Yo   | $\mathbf{x}_{1}$ |  |  |  |  |  |

| 0           | 1    | 1    | 0  | Zi             | Yı   | Χo               |  |  |  |  |  |

| 0           | 1    | 1    | 1  | Zı             | Yi   | ×ι               |  |  |  |  |  |

| 1           | ×    | ×    | x  |                | _    |                  |  |  |  |  |  |

Figure 22 HD14053B Multiplexers/Demultiplexers

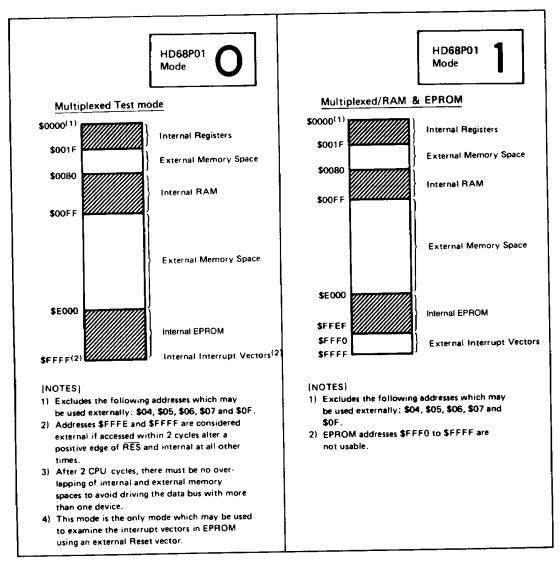

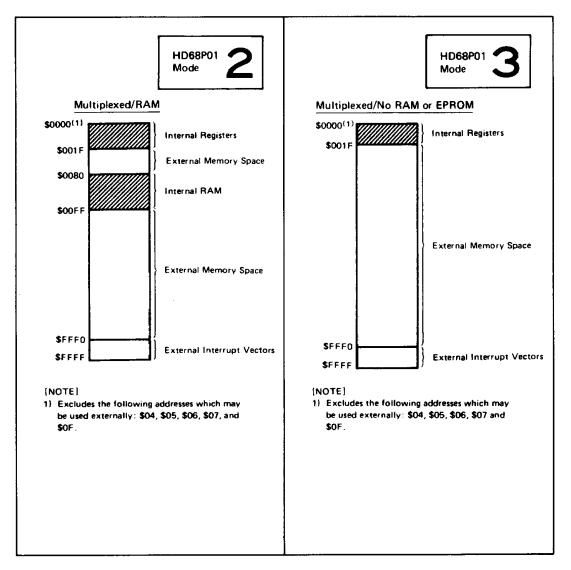

### **MEMORY MAPS**

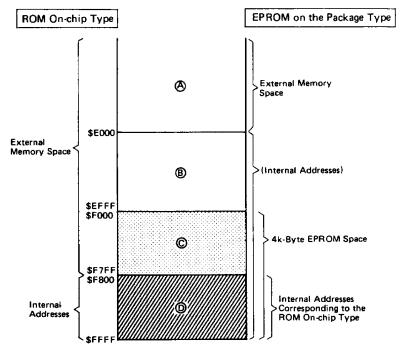

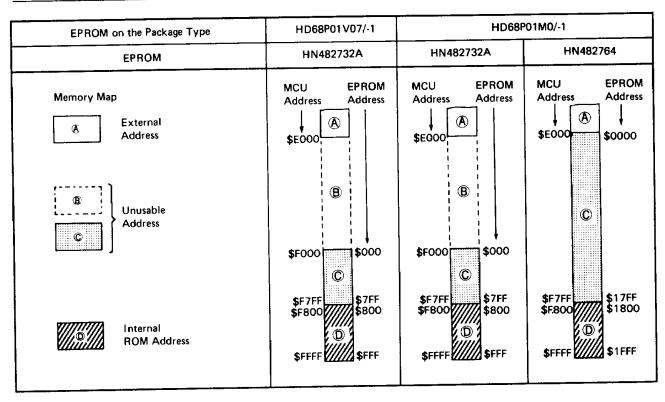

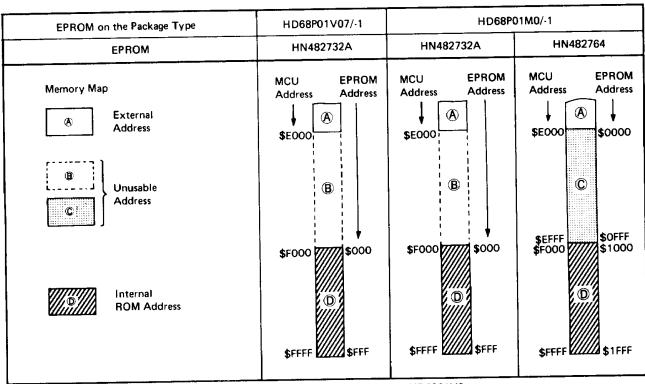

The MCU can provide up to 65k bytes address space depending on the operating mode. The HD68P01 provides 8k bytes address space for EPROM, but the maps differ in EPROM types as follows

1) HN482732A (a 4k-byte EPROM)

In order to support the HD6801V0, EPROM of the HD68P01V07/HD68P01V07-1 must be located at \$F000-\$FFFF.

2) HN482764 (a 8k-byte EPROM)

The HD68P01M0/HD68P01M0-1 can provide up to 8k bytes address space using HN482764 instead of HN482732A. In this case, EPROM of the HD68P01M0/HD68P01M0-1 is located at \$E000-\$FFFF.

A memory map for each operating mode is shown in Figure 23. The first 32 locations of each map are reserved for the MCU's internal register area, as shown in Table 5, with exceptions as indicated.

Refer to "Precaution when emulating the HD6801 Family".

Table 5 Internal Register Area

| Register                                     | Address |

|----------------------------------------------|---------|

| Port 1 Data Direction Register***            | 00      |

| Port 2 Data Direction Register***            | 01      |

| Port 1 Data Register                         | 02      |

| Port 2 Data Register                         | 03      |

| Port 3 Data Direction Register***            | 04*     |

| Port 4 Data Direction Register***            | 05**    |

| Port 3 Data Register                         | 06*     |

| Port 4 Data Register                         | 07**    |

| Timer Control and Status Register            | 08      |

| Counter (High Byte)                          | 09      |

| Counter (Low Byte)                           | OA.     |

| Output Compare Register (High Byte)          | ОВ      |

| Output Compare Register (Low Byte)           | oc      |

| Input Capture Register (High Byte)           | OD      |

| Input Capture Register (Low Byte)            | 0E      |

| Port 3 control and Status Register           | OF*     |

| Rate and Mode Control Register               | 10      |

| Transmit/Receive Control and Status Register | 11      |

| Receive Data Register                        | 12      |

| Transmit Data Register                       | 13      |

| RAM Control Register                         | 14      |

| Reserved                                     | 15-1F   |

<sup>\*</sup> External address in Modes 0, 1, 2, 3, 5, 6; cannot be accessed in Mode 5 (No IOS)

<sup>\*\*</sup> External addresses in Modes 0, 1, 2, 3

<sup>\*\*\* 1 =</sup> Output, 0 = Input

Figure 23 HD68P01 Memory Maps

Figure 23 HD68P01 Memory Maps (Continued)

Figure 23 HD68P01 Memory Maps (Continued)

Figure 23 HD68P01 Memory Maps (Continued)

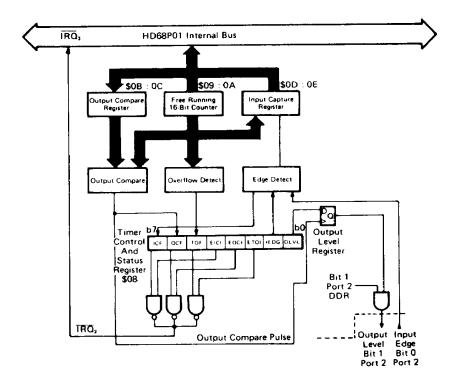

# ■ PROGRAMMABLE TIME

The Programmable Timer can be used to perform input waveform measurements while independently generating an output waveform. Pulse widths can vary from several microseconds to many seconds. A block diagram of the Timer is shown in Figure 24.

### Counter (\$09:0A)

The key timer element is a 16-bit free-running counter which is incremented by E (Enable). It is cleared during RES and is read-only with one exception: a write to the counter (\$09) will preset it to \$FFF8. This feature, intended for testing, can disturb serial operations because the counter provides the SCI's internal bit rate clock. TOF is set whenever the counter contains all 1's

# • Output Compare Register (\$0B:0C)

The Output Compare Register is a 16-bit Read/Write register used to control an output waveform or provide an arbitrary timeout flag. It is compared with the free-running counter on each E-cycle. When a match is found, OCF is set and OLVL is clocked to an output level register. If Port 2, bit 1, is configured as an output, OLVL will appear at P21 and the Output Compare Register and OLVL can then be changed for the next compare. The function is inhibited for one cycle after a write to its high byte of the Compare Resister (\$0B) to ensure a valid compare.

The Output Compare Register is set to \$FFFF by RES.

# • Input Capture Register (\$0D: 0E)

The Input Capture Register is a 16-bit read-only register used to store the free-running counter when a "proper" input transition occurs as defined by IEDG. Port 2, bit 0 should be configured as an input, but the edge detect circuit always senses P20 even when configured as an output. An input capture can occur independently of ICF: the register always contains the most current value. Counter transfer is inhibited, however, between accesses of a double byte CPU read. The input pulse width must be at least two E-cycles to ensure an input capture under all conditions.

### Timer Control and Status Register (\$08)

The Timer Control and Status Register (TCSR) is an 8-bit register of which all bits are readable while bits 0~4 can be written. The three most significant bits provide the timer's status and indicate if:

- · a proper level transition has been dtected,

- a match has been found between the free-running counter and the output compare register, and

- the free-running counter has overflowed.

Each of the three events can generate an  $\overline{IRQ}_2$  interrupt and is controlled by an individual enable bit in the TCSR.

Figure 24 Block Diagram of Programmable Timer

Timer Control and Status Register (TCSR)

| 7   | 6   | 5   | 4    | 3    | 2    | 1    | 0    |        |

|-----|-----|-----|------|------|------|------|------|--------|

| ICF | OCF | TOF | EICI | EOCI | ЕТОІ | IEDG | OLVL | \$0008 |

Bit 0 OLVL Output level. OLVL is clocked to the output level register by a successful output compare and will appear at  $P_{21}$  if Bit 1 of Port 2's Data Direction Register is set. It is cleared by  $\overline{RES}$ .

Bit 1 IEDG

Input Edge. IEDG is cleared by RES and controls which level transition will trigger a counter transfer to the Input Capture Register:

IEDG = 0 Transfer on a negative-edge

Bit 2 ETOI

Enable Timer Overflow Interrupt. When set, an IRQ<sub>2</sub> interrupt is enabled for a timer overflow; when clear, the interrupt is inhibited. It is cleared by RES.

IEDG = 1 Transfer on a positive-edge.

Bit 3 EOCI Enable Output Compare Interrupt. When set, an IRQ<sub>2</sub> interrupt is enabled for an output compare; when clear, the interrupt is inhibited. It is cleared by RES.

Bit 4 EICI Enable Input Capture Interrupt. When set, an IRQ<sub>2</sub> interrupt is enabled for an input capture; when clear, the interrupt is inhibited. It is cleared by RES.

Bit 5 TOF Timer Overflow Flag. TOF is set when the counter contains \$FFFF. It is cleared by reading the TCSR (with TOF set) followed by the counter's high byte (\$09), or by RES.

Bit 6 OFC

Output Compare Flag. OCF is set when the Output Compare Register matches the free-running counter. It is cleared by reading the TCSR (with OCF set) and then writing to the Output Compare Register (\$0B or \$0C), or by RES.

Bit 7 ICF Input Capture Flag. ICF is set to indicate a proper level transition; it is cleared by reading the TCSR (with ICF set) and then the Input Capture Register High Byte (\$0D), or by RES.

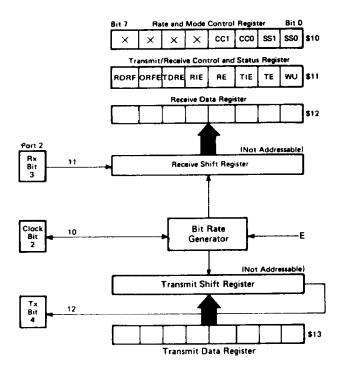

# ■ SERIAL COMMUNICATIONS INTERFACE (SCI)

A full-duplex asynchronous Serial Communications Interface (SCI) is provided with a data format and a variety of rates. The SCI transmitter and receiver are functionally independent, but use the same data format and bit rate. Serial data format is standard mark/space (NRZ) and provides one start bit, eight data bits, and one stop bit. "Baud" and "bit rate" are used synonymously in the following description.

# Wake-Up Feature

In a typical serial loop multi-processor configuration, the software protocol will usually identify the addresse(s) at the beginning of the message. In order to permit uninterested MCU's to ignore the remainder of the message, a wake-up feature is included whereby all further SCI receiver flag (and interrupt) processing can be inhibited until its data line goes idle. An SCI receiver is re-enabled by an idle string of ten consecutive 1's or by RES. Software must provide for the required idle string between consecutive messages and prevent it within messages.

# Programmable Options

The following features of the SCI are programmable: format: Standard mark/space (NRZ)

- · clock: external or internal bit rate clock

- Baud (or bit rate): one of 4 per E-clock frequency, or external bit rate (×8) input

- · wake-up feature: enabled or disabled

- interrupt requests: enabled individually for transmitter and receiver

- clock output: internal bit rate clock enabled or disabled to P<sub>22</sub>

- Port 2 (bit 3, 4): dedicated or not dedicated to serial I/O individually for transmitter and receiver.

### Serial Communications Registers

The Serial Communications Interface includes four addressable registers as depicted in Figure 25. It is controlled by the Rate and Mode Control Register and the Transmit/Receive Control and Status Register. Data is transmitted and received utilizing a write-only Transmit Register and a read-only Receive Register. The shift registers are not accessible to software.

Figure 25 SCI Registers

# Rate and Mode Control Register (RMCR) (\$10)

The Rate and Mode Control Register controls the SCI bit rate, format, clock source, and under certain conditions, the configuration of P<sub>22</sub>. The register consists of four write-only bits which are cleared by RES. The two least significant bits control the bit rate of the internal clock and the remaining two bits control the format and clock source.

# Rate and Mode Control Register (RMCR)

| 7 | 6 | 5 | 4 | 3   | 2   | _ 1 | 0   | _      |

|---|---|---|---|-----|-----|-----|-----|--------|

| × | × | х | x | CC1 | CCO | 551 | SSO | \$0010 |

SS1: SS0 Speed Select. These two bits select the Baud when using the internal clock. Four rates may be selected which are a function of the MCU input frequency. Table 6 lists bit time and rates

for three selected MCU frequencies.

Bit 3: Bit 2 CC1:CC0 Clock Control Select. These two bits select the serial clock source. If CC1 is set, the DDR value for P<sub>22</sub> is forced to the complement of CCO and cannot be altered until CC1 is cleared. If CC1 is cleared after having been set, its DDR value is unchanged. Table 7 defines the clock source, and use of P22.

If both CC1 and CC0 are set, an external TTL compatible clock must be connected to P22 at eight times (8×) the desired bit rate, but not greater than E, with a duty cycle of 50% (± 10%). If CC1:CC0 = 10, the internal bit rate clock is provided at  $P_{22}$  regardless of the values for TE or RE.

(Note) The source of SCI internal bit rate clock is the timer's free running counter. An CPU write to the counter can disturb serial operations.

# Transmit/Receive Control and Status Register (TRCSR) (\$11)

The Transmit/Receive Control and Status Register controls the transmitter, receiver, wake-up feature, and two individual interrupts and monitors the status of serial operations. All eight bits are readable while bits 0 to 4 are also writable. The register is initialized to \$20 by RES.

Transmit/Receive Control and Status Register (TRCSR)

| 7    | 6    | 5    | 4   | 3  | 2   | 1  | 0  |        |

|------|------|------|-----|----|-----|----|----|--------|

| RDRF | ORFE | TDRE | RIE | RE | TIE | ΤE | wu | \$0011 |

"Wake-up" on Idle Line. When set, WU enables Bit 0 WU the wake-up function; it is cleared by ten consecutive 1's or by RES. WU will not set if the line

Bit 1 TE Transmit Enable, When set, P24 DDR bit is set, cannot be changed, and will remain set if TE is subsequently cleared. When TE is changed from clear to set, the transmitter is connected to P24

and a preamble of nine consecutive 1's is transmitted. TE is cleared by RES.

Transmit Interrupt Enable. When set, an IRQ2 Bit 2 TIE interrupt is enabled when TDRE is set; when clear, the interrupt is inhibited. TE is cleared by

Bit 3 RE

Receive Enable. When set, P23's DDR bit is cleared, cannot be changed, and will remain clear if RE is subsequently cleared. While RE is set, the SCI receiver is enabled. RE is cleared by

Bit 4 RIE Receiver Interrupt Enable. When set, an IRQ2 interrupt is enabled when RDRF and/or ORFE is set; when clear, the interrupt is inhibited. RIE is

cleared by RES. Bit 5 TDRE

Transmit Data Register Empty. TDRE is set when the Transmit Data Register is transferred to the output serial shift register or by RES. It is cleared by reading the TRCSR (with TDRE set) and then writing to the Transmit Data Register. Additional data will be transmitted only if TDRE has been cleared,

Bit 6 ORFE Overrun Framing Error. If set, ORFE indicates either an overrun or framing error. An overrun is a new byte ready to transfer to the Receiver Data Register with RDRF still set. A receiver framing error has occurred when the byte boundaries of the bit stream are not synchronized to the bit counter. An overrun can be distinguished from a framing error by the value of RDRF: if RDRF is set, then an overrun has occurred; otherwise a framing error has been detected. Data is not transferred to the Receive Data Register in an overrun or framing error condition. ORFE is cleared by reading the TRCSR (with ORFE set) then the Receive Data Register, or by RES.

Bit 7 RDRF Receive Data Register Full. RDRF is set when the input serial shift register is transferred to the Receive Data Register. It is cleared by reading the TRCSR (with RDRF set), and then the Re-

ceive Data Register, or by RES.

Table 6 SCI Bit Times and Rates

|     |       | XTAL     | 2.4576 MHz        | 4.0 MHz            | 4.9152 MHz*         |

|-----|-------|----------|-------------------|--------------------|---------------------|

| SS1 | : SS0 | E        | 614.4 kHz         | 1.0 MHz            | 1.2288 MHz          |

| 0   | 0     | E ÷ 16   | 26 μs/38,400 Baud | 16 μs/62,500 Baud  | 13 μs/76,800 Baud   |

| 0   | 1     | E ÷ 128  | 208µs/4,800 Baud  | 128µs/7812.5 Baud  | 104.2 μs/9,600 Baud |

| 1   | 0     | E ÷ 1024 | 1.67ms/600 Baud   | 1.024ms/976.6 Baud | 833.3 μs/1,200 Baud |

| 1   | 1     | E ÷ 4096 | 6.67ms/150 Baud   | 4.096ms/244.1 Baud | 3.33 ms/300 Baud    |

<sup>\*</sup> HD68P01V07-1, HD68P01M0-1 only

Table 7 SCI Format and Clock Source Control

| CC1: CC0 | Format | Clock Source | Port 2 Bit 2 | Port 2 Bit 3 | Port 2 Bit 4 |

|----------|--------|--------------|--------------|--------------|--------------|

| 0 0      | _      | _            | _            |              | _            |

| 0 1      | NRZ    | Internal     | Not Used     | **           | **           |

| 1 0      | NRZ    | Internal     | Output*      | **           | ••           |

| 1 1      | NRZ    | External     | Input        | **           | **           |

<sup>\*</sup> Clock output is available regardless of values for bits RE and TE.

\*\* Bit 3 is used for serial input if RE = "1" in TRCS; bit 4 is used for serial output if TE = "1" in TRCS.

# Internally Generated Clcok

If the user wishes for the serial I/O to furnish a clock, the following requirements are applicable:

- · the values of RE and TE are immaterial.

- · CC1, CC0 must be set to 10

- the maximum clock rate will be E ÷ 16.

- the clock will be at 1X the bit rate and will have a rising edge at mid-bit.

### Externally Generated Clock

If the user wishes to provide an external clock for the serial I/O, the following requirements are applicable:

- the CC1, CC0, field in the Rate and Mode Control Register must be set to 11,

- the external clock must be set to 8 times (X8) the desired band rate and

- the maximum external clock frequency is 1.0 MHz.

### Serial Operations

The SCI is initialized by writing control bytes first to the Rate and Mode Control Register and then to the Transmit/Receive Control and Status Register.

The Transmitter Enable (TE) and Receiver Enable (RE) bits may be left set for dedicated operations.

### Transmit operations

The transmit operation is enabled by TE in the Transmit/Receive Control and Status Register. When TE is set, the output of the transmit serial shift register is connected to P<sub>24</sub> and the serial output by first transmitting to a ten-bit preamble of 1's. Following the preamble, internal synchronization is established and the transmitter section is ready for operation.

At this point one of two situation exist:

- if the Transmit Data Register is empty (TDRE = 1), a continuous string of ones will be sent indicating an idle line, or,

- if a byte has been written to the Transmit Data Register (TDRE = 0), it is transferred to the output serial shift register and transmission will begin.

During the transfer itself, the start bit (0) is first transmitted.

Then the 8 data bits (beginning with bit 0) followed by the stop bit (1), are transmitted. When the Transmitter Data Register has been emptied, the TDRE flag bit is set.

If the MCU fails to respond to the flag within the proper time, (TDRE is still set when the next normal transfer from the parallel data register to the serial output register should occur) then a 1 will be sent (instead of a 0) at "Start" bit time, followed by more 1's until more data is supplied to the data register. No 0's will be sent while TDRE remains a 1.

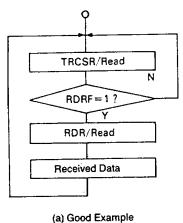

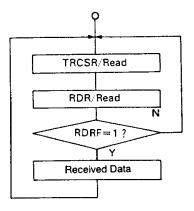

### **Receive Operations**

The receive operation is enabled by RE which configures  $P_{23}$ . The receive operation is controled by the contents of the Transmit/Receive Control and Status Register and the Rate and Mode Control Register.

The receiver bit interval is divided into 8 sub-intervals for internal synchronization. In the NRZ Mode, the received bit stream is synchronized by the first 0 (space) encountered.

The approximate center of each bit time is strobed during the next 10 bits. If the tenth bit is not a 1 (stop bit) a framing error is assumed, and ORFE is set. If the tenth bit is a 1, the data is transferred to the Receive Data Register, and interrupt flag RDRF is set. If RDRF is still set at the next tenth bit time, ORFE will be set, indicating an over-run has occurred. When the MCU responds to either flag (RDRF or ORFE) by reading the status register followed by reading the Data Register, RDRF (or ORFE) will be cleared.

## INSTRUCTION SET

The HD68P01 is upward source and object code compatible with the HD6800. Execution times of key instructions have been reduced and several new instructions have been added, including hardware multiply. A list of new operations added to the HD6800 instruction set is shown in Table 8.

In addition, two new special opcodes, 4E and 5E, are provided for test purposes. These opcodes force the Program Counter to increment like a 16-bit counter, causing address lines used in the expanded modes to increment until the device is reset. These opcodes have no mnemonics.

Table 8 New Instructions

| Instruction | Description                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------|

| ABX         | Unsigned addition of Accumulator B to Index Register                                                               |

| ADDD        | Adds (without carry ) the double accumulator to memory and leaves the sum in the double accumulator                |

| ASLD        | Shifts the double accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C-bit |

| BRN         | Branch Never                                                                                                       |

| LDD         | Loads double accumulator from memory                                                                               |

| LSRD        | Shifts the double accumulator right (towards LSB) one bit; the MSB is cleared and the LSB is shifted into the C-bi |

| MUL         | Unsigned multiply; multiplies the two accumulators and leaves the product in the double accumulator                |

| PSHX        | Pushes the Index Register to stack                                                                                 |

| PULX        | Pulls the Index Register from stack                                                                                |

| STD         | Stores the double accumulator to memory                                                                            |

| SUBD        | Subtracts memory from the double accumulator and leaves the difference in the double accumulator                   |

### Programming Model

A programming model for the HD68P01 is shown in Figure 10. Accumulator A can be concatenated with accumulator B and jointly referred to as accumulator D where A is the most significant byte. Any operation which modifies the double accumulator will also modify accumulator A and/or B. Other registers are defined as follows:

### **Program Counter**

The program counter is a 16-bit register which always points to the next instruction.

### Stack Pointer

The stack pointer is a 16-bit register which contains the address of the next available location in a pushdown/pullup (LIFO) queue. The stack resides in random access memory at a location defined by the programmer.

# Index Register

The Index Register is a 16-bit register which can be used to store data or provide an address for the indexed mode of addressing.

### **Accumulators**

The CPU contains two 8-bit accumulators, A and B, which are used to store operands and results from the arithmetic logic unit (ALU). They can also be concatenated and referred to as the D (double) accumulator.

# **Condition Code Registers**

The condition code register indicates the results of an instruction and includes the following five condition bits: Negative (N), Zero (Z), Overflow (V), Carry/Borrow from MSB (C), and Half Carry from bit 3 (H). These bits are testable by the conditional branch instruction. Bit 4 is the interrupt mask (I-bit) and inhibits all maskable interrupts when set. The two unused bits, b6 and b7 are read as ones.

# Addressing Modes

The CPU provides six addressing modes which can be used to reference memory. A summary of addressing modes for all instructions is presented in Table 9, 10, 11, and 12 where execution times are provided in E-cycles. Instruction execution times are summarized in Table 13. With an input frequency of 4 MHz, E-cycles are equivalent to microseconds. A cycle-by-cycle description of bus activity for each instruction is provided in Table 14 and a description of selected instructions is shown in Figure 26.

### **Immediate Addressing**

The operand or "immediate byte(s)" is contained in the following byte(s) of the instruction where the number of bytes matches the size of the register. These are two or three byte instructions.

# **Direct Addressing**

The least significant byte of the operand address is contained in the second byte of the instruction and the most significant byte is assumed to be \$00. Direct addressing allows the user to access \$00 through \$FF using two byte instructions and execution time is reduced by eliminating the additional memory access. In most applications, the 256-byte area is reserved for frequently referenced data.

# **Extended Addressing**

The second and third bytes of the instruction contain the absolute address of the operand. These are three byte instructions.

### Indexed Addressing

The unsigned offset contained in the second byte of the instruction is added with carry to the Index Register and used to reference memory without changing the Index Register. These are two byte instructions.

Table 9 Index Register and Stack Manipulation Instructions

|                        |          | T            |          |          |              |      |              |    |     |   |     |                                                  |          |    |      |    | Boolean/                                                                                       | C | ond | . Co | de | Re | <b>)</b> . |

|------------------------|----------|--------------|----------|----------|--------------|------|--------------|----|-----|---|-----|--------------------------------------------------|----------|----|------|----|------------------------------------------------------------------------------------------------|---|-----|------|----|----|------------|

| Pointer Operations     | Mnemonic | In           | me       | d        | D            | irec | t            | ir | nde | • | E×  | ten                                              | d        | lm | plie | d  | Arithmetic Operation                                                                           | 5 | 4   | 3    | 2  | 1  | 0          |

|                        |          | OP           | ~        | #        | OP           | ~    | #            | OP | ~   | # | OP  | ~                                                | #        | OР | ~    | #  |                                                                                                | × | _   | N    | Z  | Y  | _          |

| Compare Index Reg      | СРХ      | 8C           | 4        | 3        | 9C           | 5    | 2            | AC | 6   | 2 | вс  | 6                                                | 3        |    |      |    | X - M: M + 1                                                                                   | • | •   | 1    | ‡  | ‡  | ‡          |

| Decrement Index Reg    | DEX      | † <u> </u>   |          |          |              |      |              |    | Ι.  |   |     | <u> </u>                                         |          | 09 | 3    | 1  | X 1 -→ X                                                                                       | • | •   | •    | 1  | •  | -          |

| Decrement Stack Potr   | DES      |              | 1        |          |              |      | Γ            |    |     |   |     | l                                                |          | 34 | 3    | L. | SP - 1 → SP                                                                                    | • | •   | •    | •  | •  | •          |

| Increment Index Reg    | INX      | †            |          | 1        |              |      |              |    |     |   |     |                                                  |          | 80 | 3    | 1  | X + 1 → X                                                                                      | • | •   | •    | ;  | •  | •          |

| Increment Stack Potr   | INS      | 1            |          | t-       |              | 1    |              | 1  |     |   |     |                                                  |          | 31 | 3    | 1  | SP + 1 → SP                                                                                    | • | •   | •    | •  | •  | ·          |

| Load Index Reg         | LDX      | CE           | 3        | 3        | DE           | 4    | 2            | EE | 5   | 2 | FE  | 5                                                | 3        |    |      |    | $M \rightarrow X_H$ , $(M+1) \rightarrow X_L$                                                  | • | _   | :    | ‡  | R  | ┡-         |

| Load Stack Pntr        | LDS      | 8E           | 3        | 3        | 9E           | 4    | 2            | AE | 5   | 2 | BE  | 5                                                | 3        |    |      |    | M → SPH, (M+1) → SPL                                                                           | • | •   | ‡    | ‡  | R  | ·          |

| Store Index Reg        | STX      | +-           |          |          | DF           | 4    | 2            | EF | 5   | 2 | FF  | 5                                                | 3        |    |      |    | $X_H \rightarrow M, X_L \rightarrow (M+1)$                                                     | • | •   | 1    | ‡  | A  | •          |

| Store Stack Pntr       | STS      | +            | ✝        | †        | 9F           | 4    | 2            | AF | 5   | 2 | BF  | 5                                                | 3        |    |      |    | $SP_H \rightarrow M, SP_L \rightarrow (M+1)$                                                   | • | •   | 1    | ‡  | R  | •          |

| Index Reg → Stack Pntr |          | <del> </del> | <u> </u> | †        | -            | +-   | 1            | -  | 1   | 1 | t - |                                                  | $\vdash$ | 35 | 3    | 1  | X - 1 → SP                                                                                     | • | •   | •    | •  | •  | •          |

| Stack Pntr → Index Reg |          | +            | $\vdash$ | +-       | <del> </del> | +    | <del> </del> | †  | +-  | † | -   | 1                                                | 1        | 30 | 3    | 1  | SP + 1 → X                                                                                     | • | •   | •    | •  | •  | •          |