# HD6801S0, HD6801S5 MCU (Microcomputer Unit)

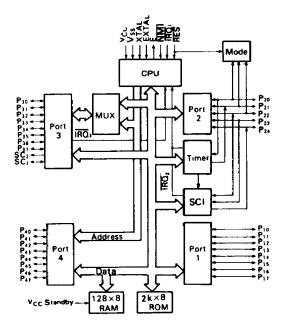

The HD6801S MCU is an 8-bit microcomputer unit which is compatible with the HMCS6800 family of parts. The HD6801S MCU is object code compatible with the HD6800 with improved execution times of key instructions plus several new 16-bit and 8-bit instructions including an 8x8 unsigned multiply with 16-bit result. The HD6801S MCU can operate as a single—chip microcomputer or be expanded to 65k bytes. The HD6801S MCU is TTL compatible and requires one +5.0 volt power supply. The HD6801S MCU has 2k bytes of ROM and 128 bytes of RAM on chip. Serial Communication interface (S.C.I.), and parallel I/O as well as a three function 16-bit timer. Features and Block diagram of the HD6801S include the following:

- Expanded HMCS6800 Instruction Set

- 8 x 8 Multiply

- On-Chip Serial Communication Interface (S.C.I.)

- Object Code Compatible With The HD6800 MPU

- 16-Bit Timer

- Single Chip Or Expandable To 65k Bytes

- 2k Bytes Of ROM

- 128 Bytes Of RAM (64 Bytes Retainable On Power Down)

- 29 Parallel I/O Lines And 2 Handshake Control Lines

- Internal Clock/Divided-By-Four Circuitry

- TTL Compatible Inputs And Outputs

- Interrupt Capability

- Compatible with MC6801 and MC6801-1

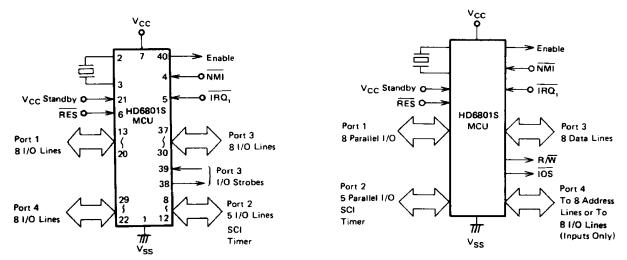

#### BLOCK DIAGRAM

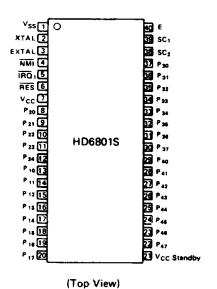

#### ■ PIN ARRANGEMENT

TYPE OF PRODUCTS

| MCU      | Bus Timing |

|----------|------------|

| HD6801S0 | 1 MHz      |

| HD6801S5 | 1.25 MHz   |

#### ■ PROGRAM DEVELOPMENT SUPPORT TOOLS

- Cross assembler software for use with IBM PCs and compatibles

- In circuit emulator for use with IBM PCs and compatibles

#### ■ ABSOLUTE MAXIMUM RATINGS

|                       |                   | Value                     | Unit |

|-----------------------|-------------------|---------------------------|------|

| ltem                  | Symbol            |                           |      |

| Supply Voltage        | V <sub>cc</sub> * | <b>-0.3</b> ∼ <b>+7.0</b> | V    |

|                       | V <sub>in</sub> * | -0.3 ~ +7.0               | V    |

| Input Voltage         | т                 | 0 ~+70                    | °C   |

| Operating Temperature | ' opr             | - 55 ~ +150               | °C   |

| Storage Temperature   | T <sub>stg</sub>  | - 55 - 7150               |      |

With respect to V<sub>SS</sub> (SYSTEM GND)

[NOTE] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

#### ■ ELECTRICAL CHARACTERISTICS

## • DC CHARACTERISTICS ( $V_{CC}$ =5.0V±5%, $V_{SS}$ = 0V, Ta = 0 $\sim$ +70°C, unless otherwise noted.)

| İten                     | 1                                                           | Symbol                                           | Test Condition                   | min  | typ | max             | Unit     |

|--------------------------|-------------------------------------------------------------|--------------------------------------------------|----------------------------------|------|-----|-----------------|----------|

|                          | RES                                                         | .,                                               |                                  | 4.0  |     | V <sub>cc</sub> | V        |

| Input "High" Voltage     | Other Inputs*                                               | V <sub>IH</sub>                                  |                                  | 2.0  | _   | V <sub>cc</sub> |          |

| Input "Low" Voltage      | All inputs*                                                 | VIL                                              |                                  | -0.3 | _   | 0.8             | V        |

| mpat con totage          | P <sub>40</sub> ~ P <sub>47</sub>                           |                                                  |                                  | -    | _   | 0.5             |          |

| Laurent Land Commons     | SC <sub>1</sub>                                             | lin                                              | Vin = 0 ~ 2.4V                   | -    |     | 0.8             | mΑ       |

| Input Load Current       | EXTAL                                                       |                                                  | $V_{in} = 0 \sim V_{CC}$         | -    |     | 0.8             |          |

| Input Leakage Current    | NMI, IRQ1, RES                                              | I II in I                                        | $V_{in} = 0 \sim 5.25V$          | _    | _   | 2.5             | μΑ       |

| Three State (Offset)     | $P_{10} \sim P_{17}, P_{30} \sim P_{37}$                    |                                                  |                                  | -    | _   | 10              |          |

| Leakage Current          | $P_{20} \sim P_{24}$                                        | I <sub>TSI</sub>                                 | $V_{in} = 0.5 \sim 2.4 V$        |      |     | 100             | μΑ       |

| Leakage Current          | $P_{30} \sim P_{37}$                                        | V <sub>OH</sub>                                  | I <sub>LOAD</sub> = -205 μA      | 2.4  |     |                 |          |

| Output "High" Voltage    | $P_{40} \sim P_{47}$ , E, SC <sub>1</sub> , SC <sub>2</sub> |                                                  | $I_{LOAD} = -145 \mu\text{A}$    | 2.4  |     |                 | v        |

| Output Mg. 15.55         | Other Outputs                                               |                                                  | $I_{LOAD} = -100 \mu\text{A}$    | 2.4  |     |                 |          |

| Output "Low" Voltage     | All Outputs                                                 | VoL                                              | I <sub>LOAD</sub> = 1.6 mA       |      |     | 0.5             | <u> </u> |

| Darlington Drive Current | P <sub>10</sub> ~ P <sub>17</sub>                           | -Іон                                             | V <sub>out</sub> = 1.5V          | 1.0  |     | 10.0            | mA       |

| Power Dissipation        | 10 11                                                       | PD                                               |                                  |      |     | 1200            | mW       |

| rower Dissipation        | $P_{30} \sim P_{37}, P_{40} \sim P_{47}, SC_1$              | <del>                                     </del> | V <sub>in</sub> = 0V, Ta = 25°C, |      | _   | 12.5            | pF       |

| Input Capacitance        | Other inputs                                                | Cin                                              | f = 1.0 MHz                      | _    | _   | 10.0            |          |

|                          | Powerdown                                                   | V <sub>SBB</sub>                                 |                                  | 4.0  | _   | 5.25            | V        |

| V <sub>CC</sub> Standby  | Operating                                                   | V <sub>SB</sub>                                  |                                  | 4.75 | _   | 5.25            | <b>'</b> |

| Standby Current          | Powerdown                                                   | I <sub>SBB</sub>                                 | V <sub>SBB</sub> = 4.0V          |      |     | 8.0             | mA       |

<sup>\*</sup>Except Mode Programming Levels.

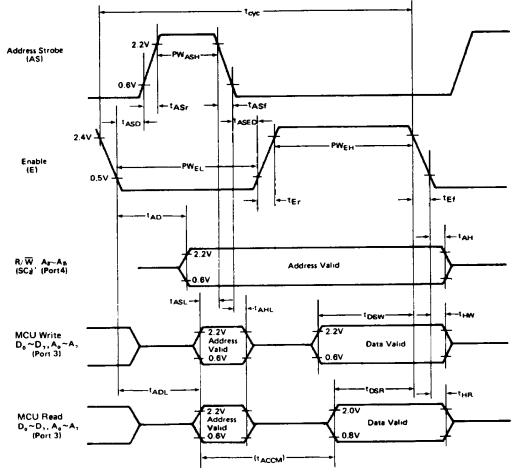

#### • AC CHARACTERISTICS

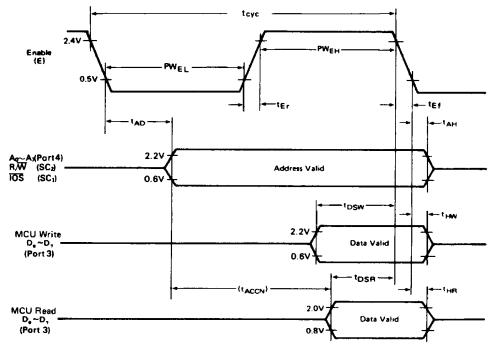

BUS TIMING (V<sub>CC</sub> =  $5.0V\pm5\%$ , V<sub>SS</sub> = 0V, Ta =  $0\sim+70^{\circ}$ C, unless otherwise noted.)

|                                       | Item                       | Symbol               | Test Condition | Н   | D6801 | SO    | H   | D6801        | <b>S</b> 5   | Uni   |

|---------------------------------------|----------------------------|----------------------|----------------|-----|-------|-------|-----|--------------|--------------|-------|

| Cycle Time                            |                            |                      | rest demartion | min | typ   | max   | min | typ          | max          | 1 000 |

| Cycle Time                            | Cycle Time                 |                      |                | 1   | -     | 10    | 0.8 | -            | 10           | μs    |

| Address Strobe Pu                     | Ise Width "High"*          | PWASH                |                | 200 | -     | T -   | 150 | -            | _            | ns    |

| Address Strobe Ri                     | se Time                    | tASr                 | }              | 5   | _     | 50    | 5   | <u> </u>     | 50           | ns    |

| Address Strobe Fa                     | II Time                    | tasf                 | 1              | 5   | 1_    | 50    | 5   | T -          | 50           | ns    |

| Address Strobe De                     | ay Time*                   | tasd                 | 1              | 60  | -     | _     | 30  | <u> </u>     | -            | ns    |

| Enable Rise Time                      |                            | ter                  |                | 5   | ! =   | 50    | 5   | _            | 50           | ns    |

| Enable Fall Time                      |                            | ter                  |                | 5   | _     | 50    | 5   | -            | 50           | ns    |

| Enable Pulse Widtl                    | h "High" Time*             | PWEH                 |                | 450 | _     |       | 340 |              | _            | ns    |

| Enable Pulse Width "Low" Time*        |                            | PWEL                 |                | 450 |       | _     | 350 |              | <u> </u>     | ns    |

| Address Strobe to Enable, Delay Time* |                            | tASED                |                | 60  |       | _     | 30  | <b>†</b>     |              | ns    |

| Address Delay Time                    |                            | t <sub>AD</sub>      | Fig. 1         | -   | T     | 260   | -   | <del> </del> | 260          | ns    |

| Address Delay Tim                     | ne for Latch (f = 1.0MHz)* | t <sub>ADL</sub>     | Fig. 2         | _   | -     | 270   |     | † <u>-</u>   | 260          | ns    |

| Data Set-up Write                     | Time                       | t <sub>DSW</sub>     |                | 225 |       | _     | 115 | _            | _            | ns    |

| Data Şet-up Read                      | Time                       | t <sub>DSR</sub>     |                | 80  | -     | T -   | 70  | _            | _            | ns    |

| Data Hold Time                        | Read                       | t <sub>HR</sub>      |                | 10  |       | _     | 10  | _            | <del>-</del> |       |

| Dota Hold Time                        | Write                      | t <sub>HW</sub>      |                | 20  |       | 20    | -   | _            | ns           |       |

| Address Set-up Tir                    | ne for Latch*              | tasL                 |                | 60  | _     | _     | 50  | _            | _            | ns    |

| Address Hold Time                     | e for Latch                | t <sub>AHL</sub>     |                | 20  | _     | _     | 20  |              | _            | ns    |

| Address Hold Time                     |                            | t <sub>AH</sub>      |                | 20  |       | _     | 20  | _            | _            | ns    |

| Peripheral Read                       | Non-Multiplexed Bus*       | (taccn)              |                |     | _     | (610) |     | _            | (420)        |       |

| Access Time                           | Multiplexed Bus*           | (t <sub>ACCM</sub> ) |                | _   | -     | (600) | _   | _            | (420)        | ns    |

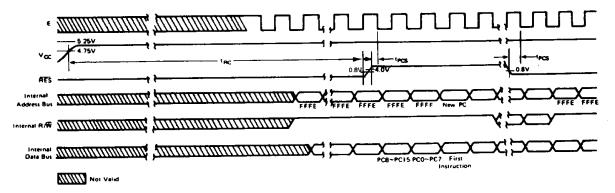

| Oscillator stabilizat                 | tion Time                  | tRC                  | Fig. 10        | 100 | _     | _     | 100 | _            | _            | ms    |

| Processor Control S                   | Set-up Time                | tecs                 | Fig. 11        | 200 | _     | -     | 200 | _            | _            | ns    |

<sup>\*</sup>These timings change in approximate proportion to tcyc. The figures in this characteristics represent those when tcyc is minimum (= in the highest speed operation).

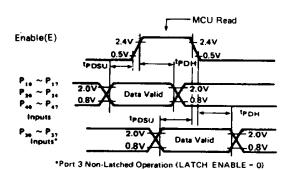

## PERIPHERAL PORT TIMING ( $V_{CC}$ = 5.0V ±5%, $V_{SS}$ = 0V, Ta = 0 $\sim$ +70°C, unless otherwise noted.)

| Item                                                                  | Item             |                   | Test Condition | min          | typ      | max | Unit |

|-----------------------------------------------------------------------|------------------|-------------------|----------------|--------------|----------|-----|------|

| Peripheral Data Setup Time                                            | Port 1, 2, 3, 4  | t <sub>PDSU</sub> | Fig. 3         | 200          | _        |     | ns   |

| Peripheral Data Hold Time                                             | Port 1, 2, 3, 4  | t <sub>PDH</sub>  | Fig. 3         | 200          | <u> </u> | _   | ns   |

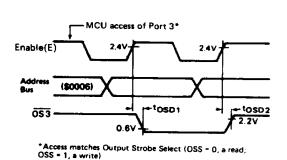

| Delay Time, Enable Positive Transition to OS3 Negative Transition     |                  | t <sub>OSD1</sub> | Fig. 5         | _            | -        | 350 | ns   |

| Delay Time, Enable Positive 1 to OS3 Positive Transition              | ransition        | t <sub>OSD2</sub> | Fig. 5         | _            |          | 350 | ns   |

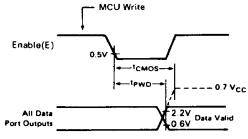

| Delay Time, Enable Negative<br>Transition to Peripheral Data<br>Valid | Port 1, 2*, 3, 4 | t <sub>PWD</sub>  | Fig. 4         | _            | _        | 400 | ns   |

| Delay Time, Enable Negative Transition to Peripheral CMOS Data Valid  |                  | tcmos             | Fig. 4         | <del>-</del> | _        | 2.0 | μς   |

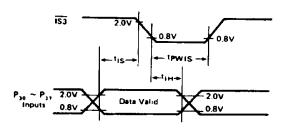

| Input Strobe Pulse Width                                              |                  | tewis             | Fig. 6         | 200          | _        | _   | ns   |

| Input Data Hold Time                                                  | port 3           | t <sub>iH</sub>   | Fig. 6         | 50           | _        | _   | ns   |

| Input Data Set-up Time                                                | Port 3           | t <sub>IS</sub>   | Fig. 6         | 20           | <u> </u> | _   | ns   |

<sup>\*</sup>Except P<sub>21</sub> \*\*10kΩ pull up register required for Port 2

TIMER, SCI TIMING (V<sub>CC</sub> = 5.0V  $\pm$ 5%, V<sub>SS</sub> = 0V, Ta = 0  $^{\sim}$  +70°C, unless otherwise noted.)

| Item                                                   | Symbol             | Test Condition | min       | typ | max | Unit              |

|--------------------------------------------------------|--------------------|----------------|-----------|-----|-----|-------------------|

| Timer Input Pulse Width                                | t <sub>PWT</sub>   |                | 2tcyc+200 |     |     | ns                |

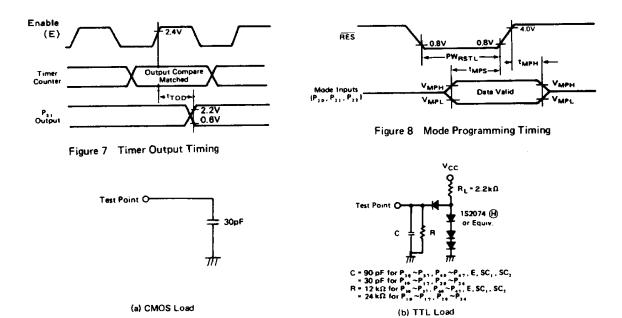

| Delay Time, Enable Positive Transition to<br>Timer Out | trop               | Fig. 7         | _         | _   | 600 | ns                |

| SCI Input Clock Cycle                                  | t <sub>Scyc</sub>  |                | 1         | _   | -   | t <sub>cyc</sub>  |

| SCI Input Clock Pulse Width                            | t <sub>PWSCK</sub> |                | 0.4       |     | 0.6 | t <sub>Scyc</sub> |

## MODE PROGRAMMING ( $V_{CC}$ = 5.0V ±5%, $V_{SS}$ = 0V, Ta = 0 $\sim$ +70°C, unless otherwise noted.)

| ltem                                  | Item                |                  | Test Condition | min | typ          | max | Unit             |

|---------------------------------------|---------------------|------------------|----------------|-----|--------------|-----|------------------|

| Mode Programming Input "Low" Voltage  |                     | V <sub>MPL</sub> |                | _   | _            | 1.7 | V                |

| Mode Programming Input "High" Voltage |                     | V <sub>MPH</sub> | 1              | 4.0 | _            | _   | V                |

| RES "Low" Pulse Width                 |                     | PWRSTL           | Fig. 8         | 3.0 | <del>-</del> | -   | t <sub>cyc</sub> |

| Mode Programming Set-up Time          |                     | t <sub>MPS</sub> | 1              | 2.0 | _            |     | t <sub>cyc</sub> |

| Mode Programming                      | RES Rise Time ≥ 1μs |                  | 1              | 0   |              | _   | ns               |

| Hold Time                             | RES Rise Time < 1μs | TMPH             |                | 100 | _            |     | 11.3             |

Figure 1 Expanded Multiplexed Bus Timing

Figure 2 Expanded Non-Multiplexed Bus Timing

Figure 3 Data Set-up and Hold Times (MCU Read)

Figure 5 Port 3 Output Strobe Timing (Single Chip Mode)

(NOTE)

- 1. 10 k $\Omega$  Pullup resistor required for Port 2 to reach 0.7 V<sub>CC</sub>

- 2. Not applicable to P<sub>31</sub>

3. Port 4 cannot be pulled above V<sub>CC</sub>

Figure 4 Port Data Delay Timing (MCU Write)

Figure 6 Port 3 Latch Timing (Single Chip Mode)

Figure 9 Bus Timing Test Loads

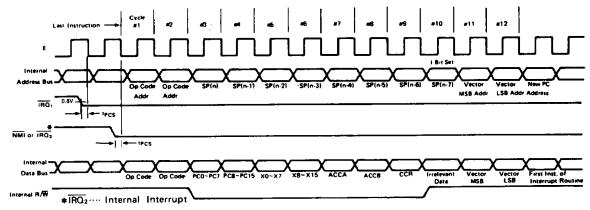

Figure 10 Interrupt Sequence

Figure 11 Reset Timing

#### **SIGNAL DESCRIPTIONS**

#### Vcc and Vss

These two pins are used to supply power and ground to the chip. The voltage supplied will be +5 volts ±5%.

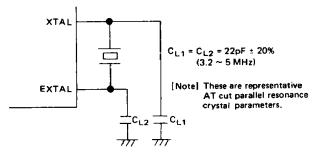

#### XTAL and EXTAL

These connections are for a parallel resonant fundamental crystal, AT cut. Divide-by-4 circuitry is included with the internal clock, so a 4 MHz crystal may be used to run the system at 1 MHz. The divide-by-4 circuitry allows for use of the inexpensive 3.58 MHz Color TV crystal for non-time critical applications. Two 22pF capacitors are needed from the two crystal pins to ground to insure reliable operation. An example of the crystal interface is shown in Fig. 12. EXTAL may be driven by an external clock source at a 4 MHz rate to run at 1 MHz with 45% to 55% duty cycle. It is not restricted to 4 MHz, as it will divide by 4 any frequency less than or equal to 5 MHz. XTAL must be grounded if an external clock is used.

Nominal Crystal Parameter

| Crystal<br>Item | 4 MHz           | 5 MHz           |

|-----------------|-----------------|-----------------|

| Co              | 7 pF max.       | 4.7 pF max.     |

| Rs              | $60\Omega$ max. | $30\Omega$ typ. |

Figure 12 Crystal Interface

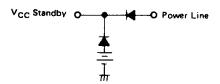

#### Vcc Standby

This pin will supply +5 volts  $\pm 5\%$  to the standby RAM on the chip. The first 64 bytes of RAM will be maintained in the power down mode with 8 mA current max. The circuit of figure 13 can be utilized to assure that  $V_{CC}$  Standby does not go below  $V_{SBB}$  during power down.

To retain information in the RAM during power down the following procedure is necessary:

- Write "0" into the RAM enable bit, RAME. RAME is bit 6 of the RAM Control Register at location \$0014. This disables the standby RAM, thereby protecting it at power down

- 2) Keep V<sub>CC</sub> Standby greater than V<sub>SBB</sub>.

Figure 13 Battery Backup for V<sub>CC</sub> Standby

#### Reset (RES)

This input is used to reset and start the MCU from a power down condition, resulting from a power failure or an initial startup of the processor. On power up, the reset must be held "Low" for at least 100 ms. When reset during operation,  $\overline{RES}$  must be held "Low" at least 3 clock cycles.

When a "High" level is detected, the MCU does the following:

- 1) All the higher order address lines will be forced "High".

- 2) I/O Port 2 bits 2, 1, and 0 are latched into programmed control bits PC2, PC1 and PC0.

- The last two (\$FFFE, \$FFFF) locations in memory will be used to load the program addressed by the program counter.

- 4) The interrupt mask bit is set. Clear before the CPU can recognize maskable interrupts.

#### • Enable (E)

This supplies the external clock for the rest of the system when the internal oscillator is used. It is a single phase, TTL compatible clock, and will be the divide-by-4 result of the crystal oscillator frequency. It will drive one TTL load and 90 pF capacitance.

## Non-Maskable Interrupt (NMI)

A low-going edge on this input requests that a non-maskable-interrupt sequence be generated within the processor. As with interrupt Request signal, the processor will complete the current instruction that is being executed before it recognizes the NMI signal. The interrupt mask bit in the Condition Code Register has no effect on NMI.

In response to an NMI interrupt, the Index Register, Program Counter, Accumulators, and Condition Code Register are stored on the stack. At the end of the sequence, a 16-bit address will be loaded that points to a vectoring address located in memory locations \$FFFC and \$FFFD. An address loaded at these locations causes the CPU to branch to a non-maskable interrupt service routine in memory.

A 3.3  $k\Omega$  external resistor to VCC should be used for wire-OR and optimum control of interrupts.

Inputs  $\overline{IRQ}_1$  and  $\overline{NMI}$  are hardware interrupt lines that are sampled during E and will start the interrupt routine on the  $\overline{E}$  following the completion of an instruction.

#### Interrupt Request (IRQ, )

This level sensitive input requests that an interrupt sequence be generated within the machine. The processor will complete the current instruction before it recognizes the request. At that time, if the interrupt mask bit in the Condition Code Register is not set, the machine will begin an interrupt sequence. The Index Register, Program Counter, Accumulators, and Condition Code Register are stored on the stack. Next the CPU will respond to the interrupt request by setting the interrupt mask bit "High" so that no further maskable interrupts may occur. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations SFFF8 and SFFF9. An address loaded at these locations causes the CPU to branch to an interrupt routine in memory.

The  $IR\overline{Q}_1$  requires a 3.3 k $\Omega$  external resistor to  $V_{CC}$  which should be used for wire-OR and optimum control of interrupts. Internal Interrupts will use an internal interrupt line  $(\overline{IRQ}_2)$ . This interrupt will operate the same as  $\overline{IRQ}_1$  except that it will use the vector address of \$FFF0 through \$FFF7.  $\overline{IRQ}_1$  will have priority over  $\overline{IRQ}_2$  if both occur at the same time. The Interrupt Mask Bit in the condition code register masks both interrupts (See Table 1).

Table 1 Interrupt Vector Location

Highest Priority

| Vec  | tor  | Interrupt                |

|------|------|--------------------------|

| MSB  | LSB  |                          |

| FFFE | FFFF | RES                      |

| FFFC | FFFD | NMI                      |

| FFFA | FFFB | Software Interrupt (SWI) |

| FFF8 | FFF9 | ĪRQ, (or IS3)            |

| FFF6 | FFF7 | ICF (Input Capture)      |

| FFF4 | FFF5 | OCF (Output Compare)     |

| FFF2 | FFF3 | TOF (Timer Overflow)     |

| FFF0 | FFF1 | SC, (RDRF + ORFE + TDRE) |

Lowest Priority

The following pins are available in the Single Chip Mode, and are associated with Port 3 only.

#### input Strobe (IS3) (SC<sub>1</sub>)

This sets an interrupt for the processor when the IS3 Enable bit is set. As shown in Figure 6 Input Strobe Timing, IS3 will fall tls minimum after data is valid on Port 3. If IS3 Enable is set in the I/O Port 3 Control/Status Register, an interrupt will occur. If the latch enable bit in the I/O Port 3 Control/Status Register is set, this strobe will latch the input data from another device when that device has indicated that it has valid data.

#### Output Strobe (OS3) (SC<sub>2</sub>)

This signal is used by the processor to strobe an external device, indicating valid data is on the I/O pins. The timing for the Output Strobe is shown in Figure 5. I/O Port 3 Control/Status Register is discussed in the following section.

The following pins are available in the Expanded Modes.

#### Read/Write (R/W) (SC<sub>2</sub>)

This TTL compatible output signals the peripherals and memory devices whether the CPU is in a Read ("High") or a Write ("Low") state. The normal standby state of this signal is Read ("High"). This output can drive one TTL load and 90 pF capacitance.

#### • I/O Strobe (IOS) (SC<sub>1</sub>)

In the expanded non-multiplexed mode of operation,  $\overline{IOS}$  internally decodes  $A_9$  through  $A_{15}$  as "0"s and  $A_8$  as a "1". This allows external access of the 256 locations from \$0100 to \$01FF. The timing diagrams are shown as figure 2.

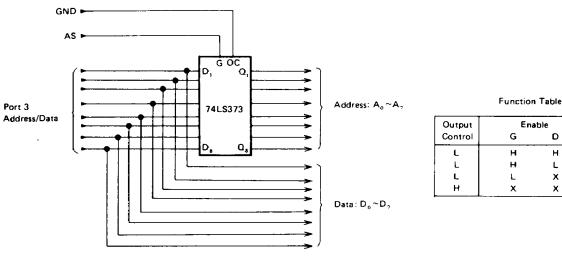

#### Address Strobe (AS) (SC<sub>1</sub>)

In the expanded multiplexed mode of operation, address strobe is output on this pin. This signal is used to latch the 8 LSB's of address which are multiplexed with data on Port 3. An 8-bit latch is utilized in conjunction with Address Strobe, as shown in figure 19. So 1/O Port 3 can become data bus during the E pulse. The timing for this signal is shown in Figure 1 of Bus Timing. This signal is also used to disable the address from the multiplexed bus allowing a deselect time. tASD before the data is enabled to the bus.

#### **■ PORTS**

There are four I/O ports on the HD6801S MCU; three 8-bit ports and one 5-bit port. There are two control lines associated with one of the 8-bit ports. Each port has an associated write only Data Direction Register which allows each I/O line to be programmed to act as an input or an output\*. A "1" in the corresponding Data Direction Register bit will cause that I/O line to be an output. A "0" in the corresponding Data Direction Register bit will cause that I/O line to be an input. There are four ports: Port 1, Port 2, Port 3, and Port 4. Their addresses and the addresses of their Data Direction registers are given in Table 2.

The only exception is bit 1 of Port 2, which can either be data input or Timer output.

Table 2 Port and Data Direction Register Addresses

| Ports      | Port Address | Data Direction<br>Register Address |

|------------|--------------|------------------------------------|

| I/O Port 1 | \$0002       | \$0000                             |

| I/O Port 2 | \$0003       | \$0001                             |

| I/O Port 3 | \$0006       | \$0004                             |

| I/O Port 4 | \$0007       | \$0005                             |

#### I/O Port 1

This is an 8-bit port whose individual bits may be defined as inputs or outputs by the corresponding bit in its data direction register. The 8 output buffers have three-state capability, allowing them to enter a high impedance state when the peripheral data lines are used as inputs. In order to be read properly, the voltage on the input lines must be greater than 2.0 V for a logic "1" and less than 0.8 V for a logic "0". As outputs, these lines are TTL compatible and may also be used as a source of up to 1 mA at 1.5 V to directly drive a Darlington base. After Reset, the I/O lines are configured as inputs. In all three modes, Port 1 is always parallel I/O.

#### I/O Port 2

This port has five lines that may be defined as inputs or outputs by its data direction register. The 5 output buffers have three-state capability, allowing them to enter a high impedance state when used as an input. In order to be read properly, the voltage on the input lines must be greater than 2.0 V for a logic "1" and less than 0.8 V for a logic "0". As outputs, this port has no internal pullup resistors but will drive TTL inputs directly. For driving CMOS inputs, external pullup resistors are required. After Reset, the I/O lines are configured as inputs. Three pins on Port 2 (pins 10, 9, and 8 of the chip) are used to program the mode of operation during reset. The values of these pins at reset are latched into the three MSB's (bits 7, 6, and 5) of Port 2 which are read-only. This is explained in the Mode Selection Section.

In all three modes, Port 2 can be configured as I/O and provides access to the Serial Communications Interface and the Timer. Bit 1 is the only pin restricted to data input or Timer output.

#### I/O Port 3

This is an 8-bit port that can be configured as I/O, a data bus, or an address bus multiplexed with the data bus — depending on the mode of operation hardware programmed by the user at reset. As a data bus, Port 3 is bi-directional. As an input for peripherals, it must be supplied regular TTL levels, that is, greater than 2.0 V for a logic "1" and less than 0.8 V for a logic "0".

Its TTL compatible three-state output buffers can drive one TTL load and 90 pF capacitance. In the Expanded Modes, after reset, the data direction register is inhibited and data flow depends on the state of the  $R/\overline{W}$  line. The input strobe ( $\overline{IS3}$ ) and the output strobe ( $\overline{OS3}$ ) used for handshaking are explained later.

In the three modes, Port 3 assumes the following characteristics:

Single Chip Mode: Parallel Inputs/Outputs as programmed by its associated Data Direction Register. There are two control lines associated with this port in this mode, an input strobe and an output strobe, that can be used for handshaking. They are controlled by the I/O Port 3 Control/Status Register explained at the end of this section. Three options of Port 3 operations are sumarized as follows: (1) Port 3 input data can be latched using  $\overline{1S3}$  (SC<sub>1</sub>) as a control signal, (2)  $\overline{OS3}$  can be generated by either an CPU read or write to Port 3's Data Register, and (3) and  $\overline{1RQ1}$  interrupt can be enabled by an IS3 negative edge. Port 3 latch and strobe timing is shown in Fig. 5 and Fig. 6.

Expanded Non-Multiplexed Mode: In this mode, Port 3 becomes the data bus  $(D_0 \sim D_7)$ .

Expanded Multiplexed Mode: In this mode, Port 3 becomes both the data bus  $(D_0 \sim D_7)$  and lower bits of the address bus  $(A_0 \sim A_7)$ . An address strobe output is true when the address is on the port.

#### I/O PORT 3 CONTROL/STATUS REGISTER

|        | 7        | 6               | 5 | 4   | 3      | 2 | 1 | 0    |   |

|--------|----------|-----------------|---|-----|--------|---|---|------|---|

| :      | IS3      | 183             | × | oss | LATCH  | х | × | ×    | ] |

| \$000F | <b>!</b> | IRQ 1<br>ENABLE |   |     | ENABLE |   |   | <br> | l |

- Bit 0; Not used.

- Bit 1; Not used.

- Bit 2; Not used.

- Bit 3; LATCH ENABLE. This controls the input latch for I/O Port 3. If this bit is set "High" the input data will be latched with the falling edge of the Input Strobe, 183. This bit is cleared by reset, and the latch is "re-opened" with CPU read Port 3.

- Bit 4; OSS. (Output Strobe Select) This bit will select if the Output Strobe should be generated at  $\overline{OS3}$  (SC<sub>2</sub>) by a write to I/O Port 3 or a read of I/O Port 3. When this bit is cleared the strobe is generated by a read Port 3. When this bit is set the strobe is generated by a write to Port 3.

- Bit 5; Not used.

- Bit 6; IS3 IRQ<sub>1</sub> ENABLE. When set, interrupt will be enabled whenever IS3 FLAG is set; when clear, interrupt is inhibited. This bit is cleared by reset.

- Bit 7; IS3 FLAG. This is a read-only status bit that is set by the falling edge of the input strobe, IS3 (SC<sub>1</sub>). It is cleared by a read of the Control/Status Register followed by a read or write of I/O Port 3. Reset will clear this bit.

#### • I/O Port 4

This is an 8-bit port that can be configured as I/O or as address output lines depending on the mode of operation. In order to be read properly, the voltage on the input lines must be greater than 2.0 V for a logic "1" and less than 0.8 V for a logic "0"

As outputs, each line is TTL compatible and can drive 1 TTL

load and 90 pF capacitance. After reset, the lines are configured as inputs. To use the pins as addresses, therefore, they should be programmed as outputs. In the three modes, Port 4 assumes the following characteristics:

Single Chip Mode: Parallel Inputs/Outputs as programmed by its associated Data Direction Register.

Expanded Non-Multiplexed Mode: Port 4 is configured as the lower order address lines  $(A_0 \sim A_7)$  by writing "1"s to the data direction register. When all eight address lines are not needed, the remaining lines, starting with the most significant bit, may be used as I/O (inputs only).

Expanded Multiplexed Mode: Port 4 is configured as the higher order address lines ( $A_8 \sim A_{15}$ ) by writing "1"s to the data direction register. When all eight address lines are not needed, the remaining lines, starting with the most significant bit, may be used as I/O (Inputs only).

#### OPERATION MODES

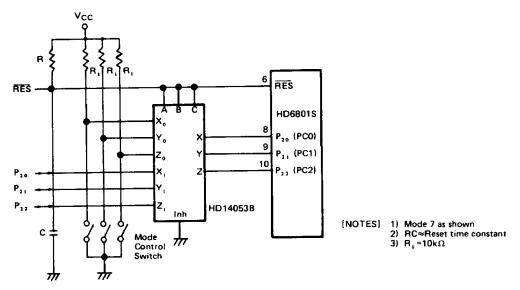

The operation modes that HD6801S will operate after reset is determined by hardware that the user must wire on pins 10, 9, and 8 of the chip. These pins are the three LSB's (I/O 2, I/O 1, and I/O 0 respectively) of Port 2. They are latched into programmed control bits PC2, PC1, and PC0 when reset goes high. I/O Port 2 Register is shown below.

#### PORT 2 DATA REGISTER

| ****   | 7 | 6   | 5   | 4     | 3     | 2     | 1     | 0     |  |

|--------|---|-----|-----|-------|-------|-------|-------|-------|--|

| \$0003 |   | PC1 | PCO | 1/0 4 | I/O 3 | 1/0 2 | 1/0 1 | 1/0 0 |  |

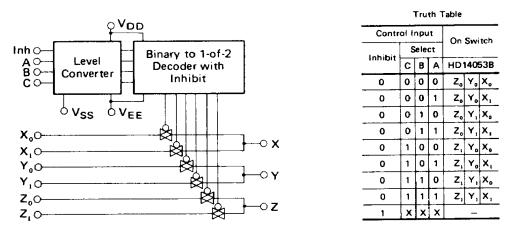

An example of external hardware that could be used for Mode Selection is shown in Fig. 14. The HD14053B provides the isolation between the peripheral device and MCU during reset, which is necessary if data conflict can occur between peripheral device and Mode generation circuit.

As bits 5, 6 and 7 of Port 2 are read-only, the mode cannot be changed through software. The mode selections are shown in Table 3.

The HD6801S can operate in three basic modes; (1) Single Chip Mode, (2) Expanded Multiplexed Mode (com-

(1) Single Chip Mode, (2) Expanded Multiplexed Mode (compatible with HMCS6800 peripheral family) (3) Expanded Non-Multiplexed Mode.

#### Single Chip Mode

In the Single Chip Mode the Ports are configured as I/O.

This is shown in Figure 16 the single Chip Mode. In this mode, Port 3 will have two associated control lines, an input strobe and an output strobe for handshaking data.

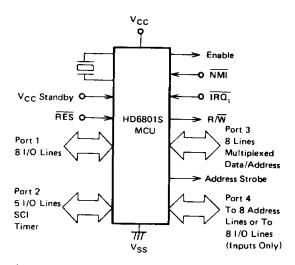

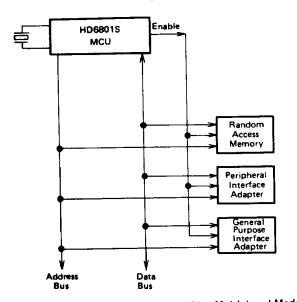

#### Expanded Non-Multiplexed Mode

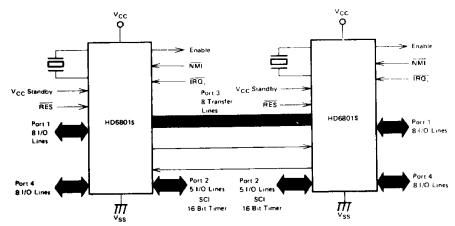

In this mode the HD6801S will directly address HMCS6800 peripherals with no external logic. In this mode Port 3 becomes the data bus. Port 4 becomes the  $A_0 \sim A_7$  address bus or partial address and I/O (inputs only). Port 2 can be parallel I/O, serial I/O, Timer, or any combination of them. Port 1 is parallel I/O only. In this mode the HD6801S is expandable to 256 locations. The eight address lines associated with Port 4 may be substituted for I/O (inputs only) if a fewer number of address lines will satisfy the application (See Figure 17).

834

Figure 14 Recommended Circuit for Mode Selection

Figure 15 HD14053B Multiplexers/Demultiplexers

Figure 16 HD6801S MCU Single-Chip Mode

Figure 17 HD6801S MCU Expanded Non-Multiplexed Mode

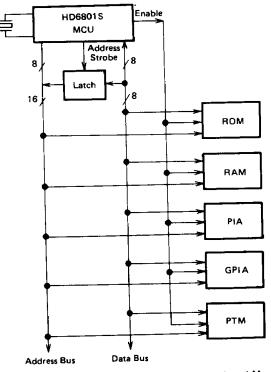

#### Expanded Multiplexed Mode

In this mode Port 4 becomes higher order address lines with an alternative of substituting some of the address lines for I/O (inputs only). Port 3 is the data bus multiplexed with the lower order address lines differentiated by an output called Address Strobe. Port 2 is 5 lines of Parallel I/O, SCI, Timer, or any combination of them. Port 1 is 8 Parallel 1/O lines. In this mode it is expandable to 65k bytes. (See Figure 18).

#### Lower order Address Bus Latches

Since the data bus is multiplexed with the lower order address bus in Port 3, latches are required to latch those address bits. The 74LS373 Transparent octal D-type latch can be used with the HD6801S to latch the least significant address byte. Figure 19 shows how to connect the latch to the HD6801S. The output control to the 74LS373 may be connected to ground.

Figure 18 HD6801S MCU Expanded Multiplexed Mode

Enable Output D Q н н Ł х a, Z

Figure 19 Latch Connection

#### Mode and Port Summary MCU Signal Description

This section gives a description of the MCU signals for the various modes. SC1 and SC2 are signals which vary with the mode that the chip is in.

| MODE             | PORT 1<br>Eight Lines | PORT 2 Five Lines | PORT 3 Eight Lines                                     | PORT 4 Eight Lines                              | SC1     | SC <sub>2</sub> |

|------------------|-----------------------|-------------------|--------------------------------------------------------|-------------------------------------------------|---------|-----------------|

| SINGLE CHIP      | 1/0                   | 1/0               | 1/0                                                    | 1/0                                             | ĪŠ3 (I) | ŌS3 (O)         |

| EXPANDED MUX     | 1/0                   | 1/0               | ADDRESS BUS $(A_0 \sim A_7)$ DATA BUS $(D_0 \sim D_7)$ | ADDRESS BUS* (A <sub>8</sub> ~A <sub>15</sub> ) | AS(O)   | R/W(O)          |

| EXPANDED NON-MUX | 1/0                   | 1/0               | DATA BUS (D <sub>0</sub> ~D <sub>7</sub> )             | ADDRESS BUS* (A <sub>0</sub> ~A <sub>7</sub> )  | ios(o)  | R/W(O)          |

<sup>\*</sup>These lines can be substituted for I/O (Input Only) starting with the most significant address line.

I = Input

O = Output

R/W = Read/Write

IS3 = Input Strobe OS3 = Output Strobe IOS = I/O Select

SC = Strobe Control AS = Address Strobe

Table 3 Mode Selection Summary

| Mode           | P <sub>22</sub><br>(PC2) | P <sub>21</sub><br>(PC1) | P. (PC0) | ROM      | RAM  | Interrupt<br>Vectors | Bus<br>Mode | Operating<br>Mode              |

|----------------|--------------------------|--------------------------|----------|----------|------|----------------------|-------------|--------------------------------|

| 7              | Н                        | н                        | н        | ı        | 1    | İ                    | ı           | Single Chip                    |

| 6              | Н.                       | Н—                       | L        | <u>-</u> |      | 1                    | MUX(6)      | Multiplexed/Partial Decode     |

| 5              | Н                        |                          | н        | 1        | ī    | 1                    | NMUX(6)     | Non-Multiplexed/Partial Decode |

| _ <del>_</del> | Н                        | <del></del> -            | L        | Į(2)     | j(1) | ı                    | 1           | Single Chip Test               |

| 3              | L                        | Н                        | Н        | E        | E    | E                    | MUX         | Multiplexed/No RAM & ROM       |

| 2              | <u> </u>                 | Н                        | L        | E        | 1    | E                    | Mux         | Multiplexed/RAM                |

| _ <del>-</del> |                          |                          | н        | ,        | 1    | E                    | MUX         | Multiplexed/RAM & ROM          |

| 0              | <del> </del>             | 1                        | <u> </u> | 1        |      | J(3)                 | MUX         | Multiplexed Test               |

#### LEGEND:

I - Internal

E - External

MUX - Multiplexed

NMUX - Non-Multiplexed

L -- Logic "0"

H - Logic "1"

#### [NOTES]

- 1) Internal RAM is addressed at \$XX80

- 2) Internal ROM is disabled

- 3) RES vector is external for 2 cycles after RES goes "High"

- 4) Addresses associated with Ports 3 and 4 are considered external in Modes 0, 1, 2, and 3

- 5) Addresses associated with Port 3 are considered external in Modes 5 and 6

- 6) Port 4 default is user data input; address output is optional by writing to Port 4

Data Direction Register

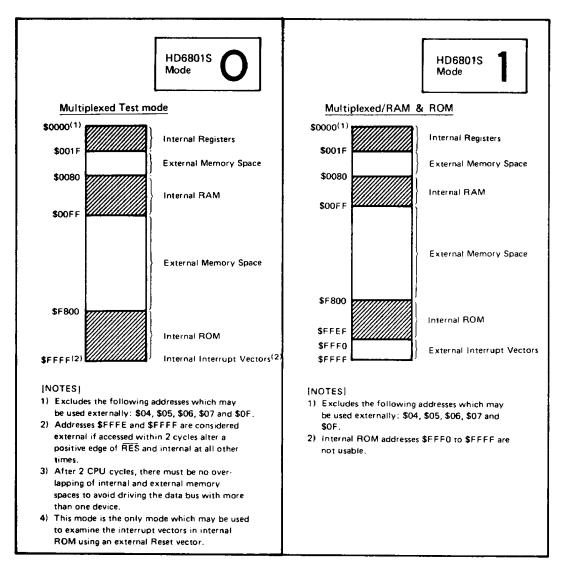

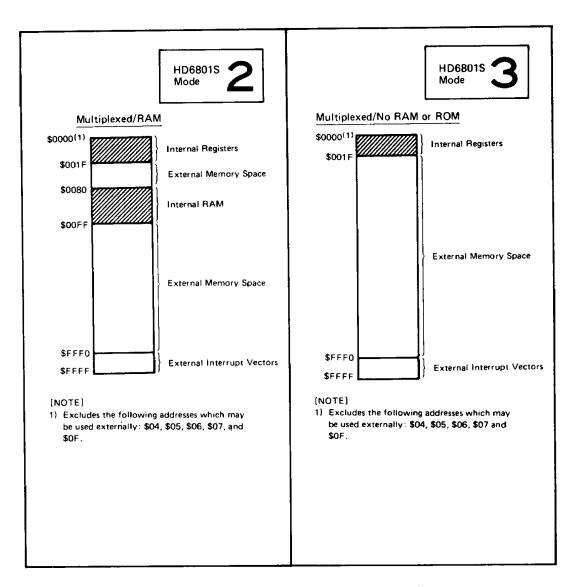

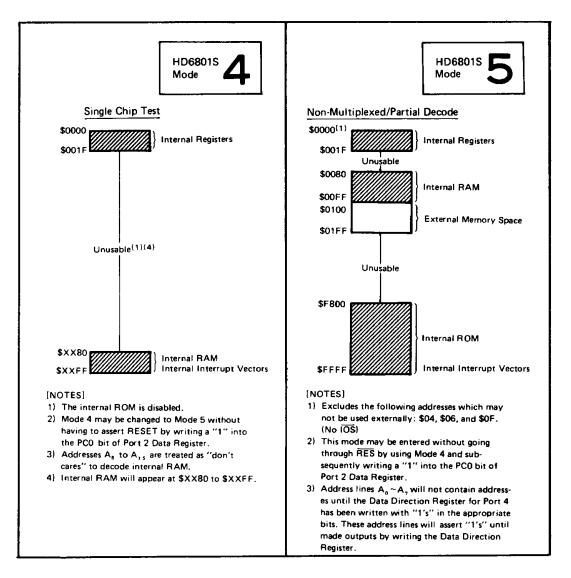

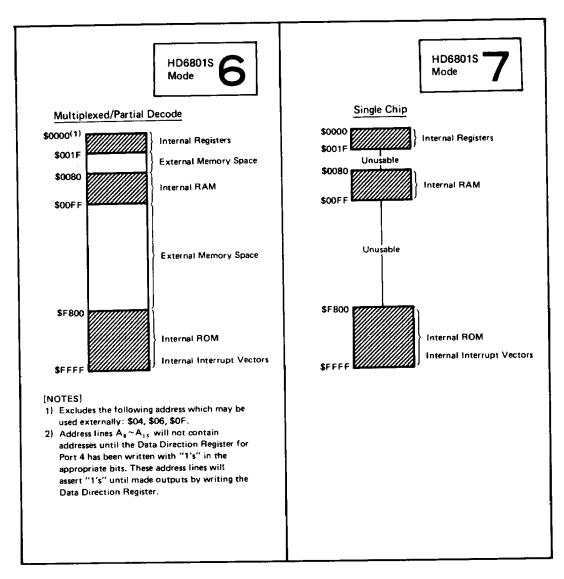

## ■ MEMORY MAPS

The MCU can provide up to 65k bytes address space depending on the operating mode. A memory map for each operating mode is shown in Figure 20. The first 32 locations of each map are reserved for the MCU's internal register area, as shown in Table 4. With exceptions as indicated.

Table 4 Internal Register Area

| Register                                     | Address |

|----------------------------------------------|---------|

| Port 1 Data Direction Register***            | 00      |

| Port 2 Data Direction Register***            | 01      |

| Port 1 Data Register                         | 02      |

| Port 2 Data Register                         | 03      |

| Port 3 Data Direction Register ***           | 04*     |

| Port 4 Data Direction Register ***           | 05**    |

| Port 3 Data Register                         | 06*     |

| Port 4 Data Register                         | 07**    |

| Timer Control and Status Register            | 08      |

| Counter (High Byte)                          | 09      |

| Counter (Low Byte)                           | 0A      |

| Output Compare Register (High Byte)          | ОВ      |

| Output Compare Register (Low Byte)           | oc      |

| Input Capture Register (High Byte)           | , OD    |

| Input Capture Register (Low Byte)            | 0E      |

| Port 3 Control and Status Register           | OF*     |

| Rate and Mode Control Register               | 10      |

| Transmit/Receive Control and Status Register | 11      |

| Receive Data Register                        | 12      |

| Transmit Data Register                       | 13      |

| RAM Control Register                         | 14      |

| Reserved                                     | 15-1F   |

External address in Modes 0, 1, 2, 3, 5, 6; cannot be accessed in Mode 5 (No. IOS)

\*\*\* 1=Output, 0=Input

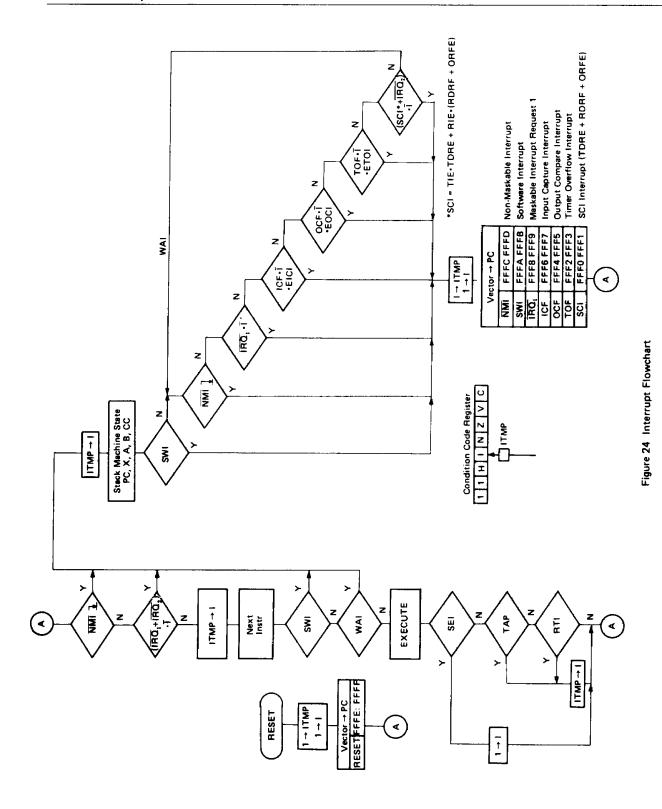

#### ■ INTERRUPT FLOWCHART

The Interrupt flow chart is depicted in Figure 24 and is common to every interrupt excluding reset.

<sup>\*\*</sup> External addresses in Modes 0, 1, 2, 3

Figure 20 HD6801S Memory Maps

Figure 20 HD6801S Memory Maps (Continued)

Figure 20 HD6801S Memory Maps (Continued)

Figure 20 HD6801S Memory Maps (Continued)

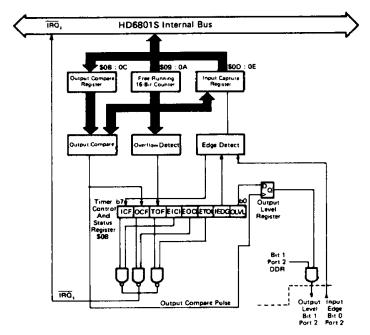

#### ■ PROGRAMMABLE TIMER

The HD6801S contains an on-chip 16-bit programmable timer which may be used to perform measurements on an input waveform while independently generating an output waveform. Pulse widths for both input and output signals may vary from a few microseconds to many seconds. The timer hardware consists of

- an 8-bit control and status register,

- a 16-bit free running counter,

- · a 16-bit output compare register, and

- · a 16-bit input capture register

A block diagram of the timer registers is shown in Figure 21.

#### • Free Running Counter (\$0009:\$000A)

The key element in the programmable timer is a 16-bit free running counter which is driven to increasing values by E (Enable). The counter value may be read by the CPU software at any time. The counter is cleared to zero by reset and may be considered a read-only register with one exception. Any CPU write to the counter's address (\$09) will always result in preset value of \$FFF8 being loaded into the counter regardless of the value involved in the write. This preset figure is intended for testing operation of the part, but may be of value in some applications.

#### Output Compare Register (\$000B:\$000C)

The Output Compare Register is a 16-bit read/write register which is used to control an output waveform. The contents of this register are constantly compared with the current value of the free running counter. When a match is found, a flag is set (OCF) in the Timer Control and Status Register (TCSR) and the current value of the Output Level bit (OLVL) in the TCSR is clocked to the Output Level Register. Providing the Data Direction Register for Port 2, Bit 1 contains a "1" (Output), the output level register value will appear on the pin for Port 2

Bit 1. The values in the Output Compare Register and Output level bit may then be changed to control the output level on the next compare value. The Output Compare Register is set to \$FFFF during RES. The Compare function is inhibited for one cycle following a write to the high byte of the Output Compare Register to insure a valid 16-bit value is in the register before a compare is made.

#### Input Capture Register (\$000D:\$000E)

The Input Capture Register is a 16-bit read-only register used to store the current value of the free running counter when the proper transition of an external input signal occurs. The input transition change required to trigger the counter transfer is controlled by the input Edge bit (IEDG) in the TCSR. The Data Direction Register bit for Port 2 Bit 0, should\* be clear (zero) in order to gate in the external input signal to the edge detect unit in the timer.

The input pulse width must be at least two E-cycles to ensure an input capture under all conditions.

\* With Port 2 Bit 0 configured as an output and set to "1", the external input will still be seen by the edge detect unit.

#### • Timer Control and Status Register (TCSR) (\$0008)

The Timer Control and Status Register consists of an 8-bit register of which all 8 bits are readable but only the low order 5 bits may be written. The upper three bits contain read-only timer status information and indicate the followings.

- a proper transition has taken place on the input pin with a subsequent transfer of the current counter value to the input capture register.

- a match has been found between the value in the free running counter and the output compare register, and

- when \$0000 is in the free running counter.

Each of the flags may be enabled onto the HD6801 internal bus  $(\overline{RQ}_2)$  with an individual Enable bit in the TCSR. If the

Figure 21 Block Diagram of Programmable Timer

Timer Control and Status Register

| 7   | 6   | 5   | 4    | 3    | 2    | 1    | 0    |        |

|-----|-----|-----|------|------|------|------|------|--------|

| ICF | OCF | TOF | EICI | EOCI | ETOI | I€DG | OLVL | \$0008 |

I-bit in the HD6801S Condition Code Register has been cleared, a priority vectored interrupt will occur corresponding to the flag bit(s) set. A description for each bit follows:

Bit 0 OLVL Output Level This value is clocked to the output level register on a successful output compare. If the DDR for Port 2 bit 1 is set, the value will appear on the output pin.

Bit 1 IEDG Input Edge — This bit controls which transition of an input will trigger a transfer of the counter to the input capture register. The DDR for Port 2 Bit 0 must be clear for this function to operate. IEDG = 0 Transfer takes place on a negative edge ("High"-to-"Low" transition).

IEDG = 1 Transfer takes place on a positive edge

IEDG = 1 Transfer takes place on a positive edge ("Low"-to-"High" transition).

Bit 2 ETO1 Enable Timer Overflow Interrupt — When set, this bit enables IRQ<sub>2</sub> to occur on the internal bus for a TOF interrupt; when clear the interrupt is inhibited.

Bit 3 EOCI Enable Output Compare Interrupt — When set, this bit enables IRQ<sub>2</sub> to appear on the internal bus for an output compare interrupt; when clear the interrupt is inhibited.

Bit 4 EICI Enable Input Capture Interrupt – When set, this bit enables IRQ<sub>2</sub> to occur on the internal bus for an input capture interrupt; when clear the interrupt is inhibited.

Bit 5 TOF Timer Overflow Flag — This read-only bit is set when the counter contains \$FFFF. It is cleared by a read of the TCSR (with TOF set) followed by an CPU read of the Counter (\$09).

Bit 6 OCF Output Compare Flag – This read-only bit is set when a match is found between the output compare register and the free running counter. It is cleared by a read of the TCSR (with OCF set) followed by an CPU write to the output compare register (\$OB or \$OC).

Bit 7 ICF Input Capture Flag — This read-only status bit is set by a proper transition on the input; it is cleared by a read of the TCSR (with ICF set) followed by an CPU read of the Input Capture Register (\$0D).

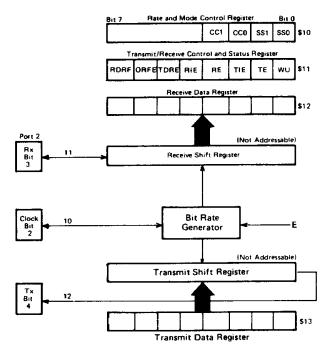

## ■ SERIAL COMMUNICATION INTERFACE

The HD6801S contains a full-duplex asynchronous serial communication interface (SCI) on chip. The controller comprises a transmitter and a receiver which operate independently or each other but in the same data format and at the same data rate. Both transmitter and receiver communicate with the

CPU via the data bus and with the outside world via pins 2, 3, and 4 of Port 2. The hardware, software, and registers are explained in the following paragraphs.

#### Wake-Up Feature

In a typical multi-processor application, the software protocol will usually contain a destination address in the initial byte(s) of the message. In order to permit non-selected MCU's to ignore the remainder of the message, a wake-up feature is included whereby all further interrupt processing may be optionally inhibited until the beginning of the next message. When the next message appears, the hardware re-enables (or "wakes-up") the for the next message. The "wake-up" is automatically triggered by a string of ten consecutive 1's which indicates an idle transmit line. The software protocol must provide for the short idle period between any two consecutive messages.

#### • Programmable Options

The following features of the HD6801S serial I/O section are programmable:

- · format standard mark/space (NRZ)

- · Clock external or internal

- baud rate one of 4 per given CPU \$\phi\_2\$ clock frequency or external clock \$\times 8\$ input

- wake-up feature enabled or disabled

- Interrupt requests enabled or masked individually for transmitter and receiver data registers

- clock output internal clock enabled or disabled to Port 2 (Bit 2)

- Port 2 (bits 3 and 4) dedicated or not dedicated to serial I/O individually for transmitter and receiver.

#### Serial Communication Hardware

The serial communication hardware is controlled by 4 registers as shown in Figure 22. The registers include:

- · an 8-bit control and status register

- · a 4-bit rate and mode control register (write-only)

- · an 8-bit read-only receive data register and

- · an 8-bit write-only transmit data register.

In addition to the four registers, the serial I/O section utilizes bit 3 (serial input) and bit 4 (serial output) of Port 2. Bit 2 of Port 2 is utilized if the internal-clock-out or external-clock-in options are selected.

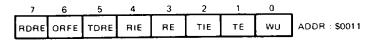

#### Transmit/Receive Control and Status (TRCS) Register

The TRCS register consists of an 8-bit register of which all 8 bits may be read while only bits  $0\sim4$  may be written. The register is initialized to \$20 by reset. The bits in the TRCS register are defined as follows:

Transmit/Receive Control and Status Register

**(1)** HITACHI

Figure 22 Serial I/O Registers

Bit 0 WU "Wake-up" on Next Message — set by HD6801S software and cleared by hardware on receipt of ten consecutive 1's or reset of RE flag. It should be noted that RE flag should be set in advance of

CPU set of WU flag.

Bit 1 TE Transmit Enable — set by HD6801S to produce preamble of nine consecutive 1's and to enable gating of transmitter output to Port 2, bit 4 regardless of the DDR value corresponding to this bit; when clear, serial I/O has no effect on Port 2

bit 4.

TE set should be after at least one bit time of data transmit rate from the set-up of transmit data rate and mode.

Bit 2 TIE

Transmit Interrupt Enable — when set, will permit an IRQ2 interrupt to occur when bit 5 (TDRE) is set; when clear, the TDRE value is masked from

the bus.

Bit 3 RE

Receiver Enable — when set, gates Port 2 bit 3 to input of receiver regardless of DDR value for this bit; when clear, serial I/O has no effect on Port 2 bit 3.

Bit 4 RIE

Receiver Interrupt Enable — when set, will permit an IRQ2 interrupt to occur when bit 7 (RDRF) or bit 6 (ORFE) is set; when clear, the interrupt is masked.

Bit 5 TDRE Transmit Data Register Empty — set by hardware when a transfer is made from the transmit data register to the output shift register. The TDRE bit is cleared by reading the status register, then

writing a new byte into the transmit data register, TDRE is initialized to 1 by reset.

Bit 6 ORFE Over-Run-Framing Error — set by hardware when an overrun or framing error occurs (receive only). An overrun is defined as a new byte received with last byte still in Data Register/Buffer. A framing error has occurred when the byte boundaries in bit stream are not synchronized to bit counter. The ORFE bit is cleared by reading the status register, then reading the Receive Data Register, or by reset.

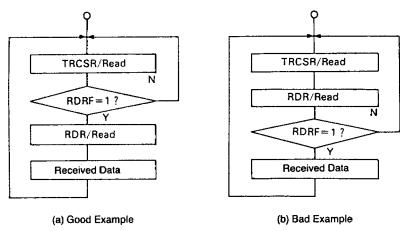

Bit 7 RDRF Receiver Data Register Full — Set by hardware when a transfer from the input shift register to the receiver data register is made. The RDRF bit is cleared by reading the status register, then reading the Receive Data Register, or by reset.

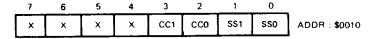

#### Rate and Mode Control Register

The Rate and Mode Control register controls the following serial I/O variables:

- Baud rate

- format

- · clocking source, and

- Port 2 bit 2 configuration

The register consists of 4 bits all of which are write-only and cleared by reset. The 4 bits in the register may be considered as a pair of 2-bit fields. The two low order bits control the bit rate for internal clocking and the remaining two bits control the format and clock select logic. The register definition is as follows:

#### Rate and Mode Control Register

Bit 0 SSO | Speed Select - These bits select the Baud rate for Bit 1 SS1 f the internal clock. The four rates which may be selected are a function of the CPU  $\phi_2$  clock frequency. Table 5 lists the available Baud rates.

Bit 2 CCO | Clock Control and Format Select - this 2-bit field Bit 3 CC1 controls the format and clock select logic. Table 6 defines the bit field.

Table 5 SCI Bit Times and Rates

|       |     | XTAL     | 2.4576 MHz        | 4.0 MHz             | 4.9152 MHz*         |

|-------|-----|----------|-------------------|---------------------|---------------------|

| SS1 : | SS0 | E        | 614.4 kHz         | 1.0 MHz             | 1.2288 MHz          |

| 0     | 0   | E ÷ 16   | 26 μs/38,400 Baud | 16 μs/62,500 Baud   | 13 μs/76,800 Baud   |

| 0     | 1   | E ÷ 128  | 208 μs/4,800 Baud | 128 μs/7812.5 Baud  | 104.2 μs/9,600 Baud |

| 1     | o   | E ÷ 1024 | 1.67 ms/600 Baud  | 1,024 ms/976.6 Baud | 833.3 μs/1,200 Baud |

| 1     | 1   | E ÷ 4096 | 6.67 ms/150 Baud  | 4.096 ms/244.1 Baud | 3.33 ms/300 Baud    |

<sup>\*</sup> HD6801S5 Only

Table 6 SCI Format and Clock Source Control

| CC1: CC0 | Format | Clock Source | Port 2 Bit 2 | Port 2 Bit 3 | Port 2 Bit 4 |

|----------|--------|--------------|--------------|--------------|--------------|

| 0 0      | _      | _            | _            | **           | **           |

| 0 1      | NRZ    | Internal     | Not Used     | **           | ••           |

| 1 0      | NRZ    | Internal     | Output*      | **           | **           |

| 1 1      | NRZ    | External     | Input        | **           | **           |

#### Internally Generated Clock

If the user wishes for the serial I/O to furnish a clock, the following requirements are applicable:

- · the values of RE and TE are immaterial.

- · CC1, CC0 must be set to 10

- the maximum clock rate will be E ÷ 16.

- the clock will be at 1× the bit rate and will have a rising edge at mid-bit.

#### **Externally Generated Clock**

If the user wishes to provide an external clock for the serial I/O, the following requirements are applicable:

- · the CC1, CC0, field in the Rate and Mode Control Register must be set to 11,

- · the external clock must be set to 8 times (x8) the desired baud rate and

- the maximum external clock frequency is 1.0 MHz.

#### Serial Operations

The serial I/O hardware should be initialized by the HD6801S software prior to operation. This sequence will normally consist of;

- · writing the desired operation control bits to the Rate and Mode Control Register and

- writing the desired operational control bits in the Transmit/ Receive Control and Status Register.

The Transmitter Enable (TE) and Receiver Enable (RE) bits may be left set for dedicated operations.

#### **Transmit Operations**

The transmit operation is enabled by the TE bit in the Transmit/Receive Control and Status Register. This bit when set, gates the output of the serial transmit shift register to Port 2 Bit 4 and takes unconditional control over the Data Direction Register value for Port 2, Bit 4.

Following a RES the user should configure both the Rate and Mode Control Register and the Transmit/Receive Control and Status Register for desired operation. Setting the TE bit during this procedure initiates the serial output by first transmitting a nine-bit preamble of 1's. Following the preamble, internal synchronization is established and the transmitter section is ready for operation.

At this point one of two situation exist:

- 1) if the Transmit Data Register is empty (TDRE = 1), a continuous string of ones will be sent indicating an idle line, or,

- 2) if data has been loaded into the Transmit Data Register (TDRE = 0), the word is transferred to the output shift register and transmission of the data word will begin.

During the data transmit, the 0 start bit is first transmitted. Then the 8 data bits (beginning with bit 0) followed by the stop bit, are transmitted. When the Transmitter Data Register has been emptied, the hardware sets the TDRE flag bit.

If the HD6801S fails to respond to the flag within the proper time, (TDRE is still set when the next normal transfer from the parallel data register to the serial output register should occur) then a 1 will be sent (instead of a 0) at "Start" bit time, followed by more I's until more data is supplied to the data register. No 0's will be sent while TDRE remains a 1.

Clock output is available regardless of values for bits RE and TE. Bit 3 is used for serial input if RE = "1" in TRCS; bit 4 is used for serial output if TE = "1" in TRCS.

#### Receive Operation

The receive operation is enabled by the RE bit which gates in the serial input through Port 2 Bit 3. The receiver section operation is conditioned by the contents of the Transmit/ Receive Control and Status Register and the Rate and Mode Control Register.

The receiver bit interval is divided into 8 sub-intervals for internal synchronization. In the NRZ Mode, the received bit stream is synchronized by the first 0 (space) encountered.

The approximate center of each bit time is strobed during the next 10 bits. If the tenth bit is not a 1 (stop bit) a framing error is assumed, and bit ORFE is set. If the tenth bit as a 1, the data is transferred to the Receive Data Register, and interrupt flag RDRF is set. If RDRF is still set at the next tenth bit time, ORFE will be set, indicating an over-run has occurred. When the HD6801S responds to either flag (RDRF or ORFE) by reading the status register followed by reading the Data Register, RDRF (or ORFE) will be cleared.

#### ■ RAM CONTROL REGISTER

This register, which is addressed at \$0014, gives status information about the standby RAM. A "0" in the RAM enable bit (RAME) will disable the standby RAM, thereby protecting it at power down if V<sub>CC</sub> Standby is held greater than V<sub>SBB</sub> volts, as explained previously in the signal description for V<sub>CC</sub> Standby.

**RAM Control Register** STBY х RAME х х X \$0014 X **PWR**

Bit 0 Not used.

Bit 1 Not used.

Bit 2 Not used.

Bit 3 Not used.

Bit 4 Not used.

Bit 5 Not used.

Bit 6 RAME The RAM Enable control bit allows the user the ability to disable the standby RAM. This bit is set to a logic "1" by RES which enables the standby RAM and can be written to one or zero under program control. When the RAM is disabled, data is read from external memory.

Big 7 STBY The Standby Power bit is cleared when the standby voltage is removed. This bit is a read/write status flag that the user can read which indicates that the standby RAM voltage has been applied, and the data in the standby RAM is valid.

#### ■ GENERAL DESCRIPTION OF INSTRUCTION SET

The HD6801S is upward object code compatible with the HD6800 as it implements the full HMCS6800 instruction set. The execution times of key instructions have been reduced to increase throughout. In addition, new instructions have been added; these include 16-bit operations and a hardware multiply.

Included in the instruction set section are the following:

- CPU Programming Model (Figure 23)

- Addressing modes

- Accumulator and memory instructions Table 7

- New instructions

- Index register and stack manipulations instructions Table

- Jump and branch instructions Table 9

- Condition code register manipulation instructions Table 10

- Instructions Execution times in machine cycles Table

- Summary of cycle by cycle operation Table 12

- · Op codes Map Table 13

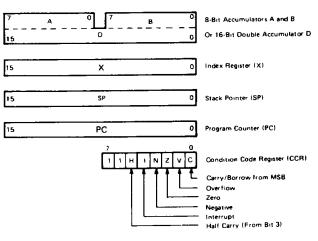

#### • CPU Programming Model

The programming model for the HD6801S is shown in Figure 23. The double (D) accumulator is physically the same as the Accumulator A concatenated with the Accumulator B so that any operation using accumulator D will destroy information in A and B.

Figure 23 CPU Programming Model

#### **CPU Addressing Modes**

The HD6801S eight-bit microcomputer unit has seven address modes that can be used by a programmer, with the addressing mode a function of both the type of instruction and the coding within the instruction. A summary of the addressing modes for a particular instruction can be found in Table 11 along with the associated instruction execution time that is given in machine cycles. With a clock frequency of 4 MHz, these times would be microseconds.

#### Accumulator (ACCX) Addressing

In accumulator only addressing, either accumulator A or accumulator B is specified. These are one-byte instructions.

#### Immediate Addressing

In immediate addressing, the operand is contained in the second byte of the instruction except LDS and LDX which have the operand in the second and third bytes of the instruction. The CPU addresses this location when it fetches the immediate instruction for execution. These are two or three-byte instruc-

Table 7 Accumulator & Memory Instructions

|                            |          |          |           |        |        |        | Add                                                 | ressir        | ng M   | lod | es      |         |         |            |     |     |                                                       | C          |             |                  | on I<br>Iiste |                  | ie         |

|----------------------------|----------|----------|-----------|--------|--------|--------|-----------------------------------------------------|---------------|--------|-----|---------|---------|---------|------------|-----|-----|-------------------------------------------------------|------------|-------------|------------------|---------------|------------------|------------|

| Operations                 | Mnemonic | IMI      | иFſ       | , 1    | DIF    | FC     | τī                                                  | INI           | DEX    |     | EXT     | EN      | D       | IMP        | LIE | Б   | Boolean/<br>Arithmetic Operation                      | 5          | 4           | 3                | 2             | 1                | 0          |

|                            |          | OP       | ~         | #      | OP     | ~      | #                                                   | ОР            | ~      | #   | ОР      | ~       | #       | ОР         | ~   | #   | Argument Operation                                    | Н          | 1           | Ν                | z             | V                | ᆚ          |

| Add                        | ADDA     | 8B       | 2         | 2      | 9В     | 3      | 2                                                   | AB            | 4      | 2   | 88      | 4       | 3       |            |     |     | A + M → A                                             | ‡          | •           | \$               | \$            | ‡                | -          |

|                            | ADDB     | СВ       | 2         | 2      | DB     | 3      | 2                                                   | ĒВ            | 4      | 2   | FB      | 4       | 3       |            |     |     | B + M → B                                             | 1          | •           | ‡                | 1             | ‡                | 1:         |

| Add Double                 | ADDD     | СЗ       | 4         | 3      | D3     | 5      | 2                                                   | E3            | 6      | 2   | F3      | 6       | 3       |            |     |     | A:B+M:M+1→A:B                                         | •          | ٠           | \$               | \$            | 1                |            |

| Add Accumulators           | ABA      | 1        | ╁─        | Н      |        | _      |                                                     |               | $\neg$ | _   |         |         |         | 1B         | 2   | 1   | A + B → A                                             | 1          | •           | ‡                | 1             | 1                | +          |

| Add With Carry             | ADCA     | 89       | 2         | 2      | 99     | 3      | 2                                                   | Α9            | 4      | 2   | 89      | 4       | 3       |            |     |     | A + M + C → A                                         | \$         | •           | :                | ‡             | 1                | +          |

| add Williams               | ADCB     | C9       | 2         | 2      | D9     | 3      | 2                                                   | E9            | 4      | 2   | F9      | 4       | 3       |            |     |     | B + M + C → B                                         | ‡          | •           | 1                | 1             | 1                | -          |

| AND                        | ANDA     | 84       | 2         | 2      | 94     | 3      | 2                                                   | Α4            | 4      | 2   | В4      | 4       | 3       |            |     |     | A·M → A                                               | •          | •           | ‡                | 1             | R                | +          |

|                            | ANDB     | C4       | 2         | 2      | D4     | 3      | 2                                                   | E4            | 4      | 2   | F4      | 4       | 3       |            |     |     | B·M → B                                               | •          | •           | 1                | ‡             | R                | _          |

| Bit Test                   | BITA     | 85       | 2         | 2      | 95     | 3      | 2                                                   | A5            | 4      | 2   | В5      | 4       | 3       |            |     |     | A·M                                                   | •          | •           | ‡                | 1             | R                | -          |

| 51. 1. 55.                 | BIT B    | C5       | 2         | 2      | D5     | 3      | 2                                                   | E5            | 4      | 2   | F5      | 4       | 3       |            |     |     | В∙М                                                   | •          | •           | ‡                | 1             | R                | -          |

| Clear                      | CLR      | t        | 1         |        | T      |        |                                                     | 6F            | 6      | 2   | 7F      | 6       | 3       | Ī          |     |     | 00 → M                                                | •          | •           | R                | s             | P                | -          |

|                            | CLRA     | † –      | T         | $\Box$ | _      |        |                                                     |               |        |     |         | L       |         | 4F         | 2   | 1   | 00 → A                                                | •          | •           | R                | -             | +                | +          |

|                            | CLRB     |          | †         |        | T      |        |                                                     |               |        | _   |         | Ţ       |         | 5F         | 2   | 1   | 00 → B                                                | •          | •           | R                | +-            | +-               | -          |

| Compare                    | CMPA     | 81       | 2         | 2      | 91     | 3      | 2                                                   | Α1            | 4      | 2   | В1      | 4       | 3       |            |     |     | A - M                                                 | •          | •           | ‡                | t             | <del></del>      |            |

| 00                         | СМРВ     | C1       | 2         | 2      | D1     | 3      | 2                                                   | ٤١            | 4      | 2   | F1      | 4       | 3       |            |     | Ī   | B - M                                                 | •          | •           | \$               | ‡             | 1                | 1          |

| Compare<br>Accumulators    | CBA      | T        | T         |        |        | Г      | <u> </u>                                            |               |        |     |         |         |         | 11         | 2   | 1   | A – B                                                 | •          | •           | 1                | 4             | 1                | +          |

| Complement, 1's            | COM      | $T^{-}$  |           |        |        |        | Г                                                   | 63            | 6      | 2   | 73      | 6       | 3       |            |     |     | M → M                                                 | •          | •           | 1                | ┵             | _                | _          |

|                            | COMA     | <b>†</b> | T         | 十一     | 1      | _      | 1                                                   |               |        |     |         | 1 -     |         | 43         | 2   | 1   | Ā → A                                                 | •          | •           | 1                | +             | +                | -+-        |

|                            | сомв     | 1        | $\top$    |        |        |        |                                                     |               |        |     |         |         |         | 53         | 2   | 1   | B → B                                                 | •          | •           | <b>‡</b>         | <u> </u>      | -                | -          |

| Complement, 2's            | NEG      | +        | +-        | T      | 1      | Τ      |                                                     | 60            | 6      | 2   | 70      | 6       | 3       |            |     |     | 00 - M → M                                            | •          | •           | +-               | +             | +                | D id       |

| (Negate)                   | NEGA     | 1        |           |        |        |        |                                                     |               |        |     |         |         |         | 40         | 2   | 1   | 00 - A → A                                            | •          | •           | 1                | +             | -                | C C        |

| ,,,,,                      | NEGB     |          | 1         |        |        |        |                                                     |               |        |     |         | 1       | L       | 50         | 2   | 1   | 00 - B → B                                            | •          | •           | 1                | _‡։           | 16               | L S        |

| Decimal Adjust, A          | DAA      |          | 1         |        |        |        |                                                     |               |        |     |         |         |         | 19         | 2   | 1   | Converts binary add of BCD characters into BCD format | •          | •           | ţ                | $\perp$       | 1                | ; (3       |

| Decrement                  | DEC      |          |           |        |        |        |                                                     | 6A            | 6      | 2   | 7A      | 6       | 3       |            |     | L   | M – 1 → M                                             | •          | •           | Ψ.               | -             | -                | 0          |

|                            | DECA     |          |           | T      |        |        |                                                     |               |        | L   | L       |         |         | 4A         | 2   | 1   | A – 1 → A                                             | •          | •           | +-               | +             | <del>-   '</del> | <b>4</b> ) |

|                            | DECB     |          | Т         |        |        | Γ      |                                                     |               |        | [   |         |         |         | 5 <b>A</b> | 2   | 1   | B - 1 → B                                             | •          | •           | -                | -             | -                | 4          |

| Exclusive OR               | EORA     | 88       | 2         | 2      | 98     | 3      | 2                                                   | A8            | 4      | 2   | 88      | 4       | 3       |            |     | _   | A ⊕ M → A                                             | •          | •           | <u> </u>         | -             | -                | R          |

|                            | EORB     | СВ       | 2         | 2      | D8     | 3      | 2                                                   | E8            | 4      | 2   | F8      | 4       | 3       |            | Ι   |     | B ⊕ M→ B                                              | •          | •           | 4                | -             |                  | R          |

| Increment                  | INC      | 1        | ┪         | 1      |        |        |                                                     | 6C            | 6      | 2   | 7C      | 6       | 3       |            | Ţ   |     | M + 1 → M                                             | •          | •           | <del>-  </del> - | -             | -4               | 5          |

|                            | INCA     |          | 1         | 1      |        | 1      | $\top$                                              | 1             |        | Ī   |         |         | Г       | 4C         | 2   | 1   | A + 1 → A                                             | •          | •           |                  | _             | +                | 5          |

|                            | INCB     | $\top$   | 1         | 1      |        |        | 7                                                   | 1             |        |     |         |         | Γ       | 5C         | 2   | 1   | B + 1 → B                                             | •          | •           | -                | -+-           | $\rightarrow$    | 5.         |

| Load                       | LDAA     | 86       | 2         | 2      | 96     | 3      | 2                                                   | A6            | 4      | 2   | В6      | 4       | 3       |            |     | Ĺ   | M → A                                                 | •          | •           | -                | -             | -+-              | R          |

| Accumulator                | LDAB     | C6       | 2         | 2      | D6     | 3      | 2                                                   | E6            | 4      | 2   | F6      | 4       | 3       |            |     |     | M → B                                                 | •          | •           | 1                | 1             |                  | R          |

| Load Double<br>Accumulator | LDD      | cc       | : 3       | 3      | DC     | 4      | 2                                                   | EC            | 5      | 2   | FC      | 5       | 3       |            |     |     | M + 1 → B, M → A                                      | •          | 4           | 1                | 1             | 1                | R          |

| Multiply Unsigned          | MUL      |          | Ţ         |        |        |        | $oldsymbol{oldsymbol{oldsymbol{oldsymbol{\Gamma}}}$ |               |        |     |         | $\perp$ | $\perp$ | 30         | 10  | ) 1 | ·                                                     | •          | -+-         | +                | . +           | . +              | •          |